A method and cmos device for adjusting the threshold of high-k metal gate cmos device

A metal gate and device technology, which is applied in the manufacturing of semiconductor devices, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of poor controllability, channel process damage, and small thickness distinction range, and achieves a large thickness controllable range. , the effect of reducing process damage and integrating process is simple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

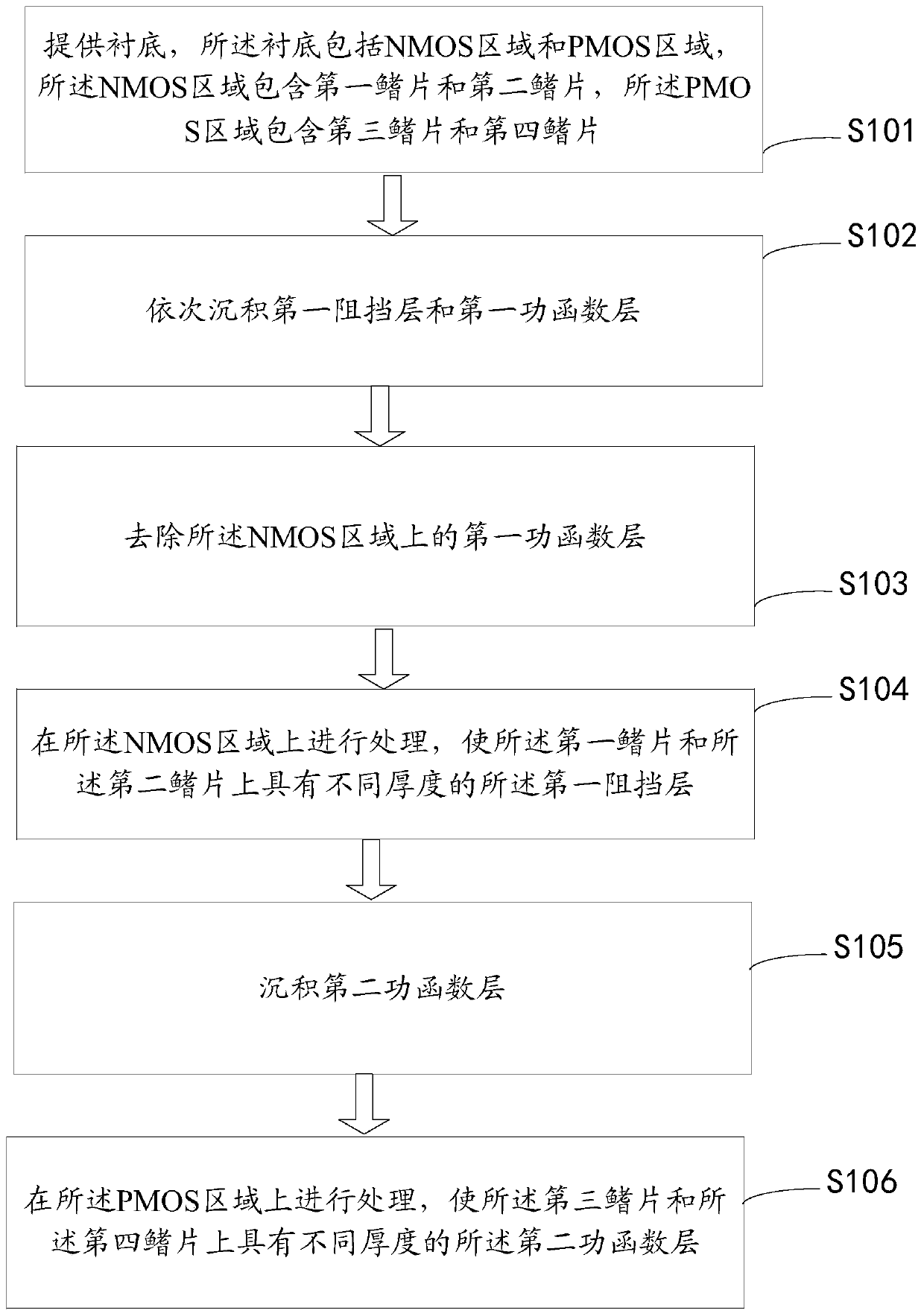

[0048] In this embodiment, a method for adjusting the threshold of a high-K metal gate CMOS device is provided, such as figure 1 shown, including:

[0049] S101, providing a substrate, where the substrate includes an NMOS region and a PMOS region, the NMOS region includes a first fin and a second fin, and the PMOS region includes a third fin and a fourth fin;

[0050] S102, sequentially depositing a first barrier layer and a first work function layer;

[0051] S103, removing the first work function layer on the NMOS region;

[0052] S104, performing processing on the NMOS region, so that the first barrier layer has different thicknesses on the first fin and the second fin;

[0053] S105, depositing a second work function layer;

[0054] S106. Perform processing on the PMOS region, so that the third fin and the fourth fin have the second work function layer with different thicknesses.

[0055] Below, combine Figure 1-7 To introduce in detail the detailed steps of the method...

Embodiment 2

[0092] In this embodiment, a CMOS device is provided, such as Figure 6 shown, including:

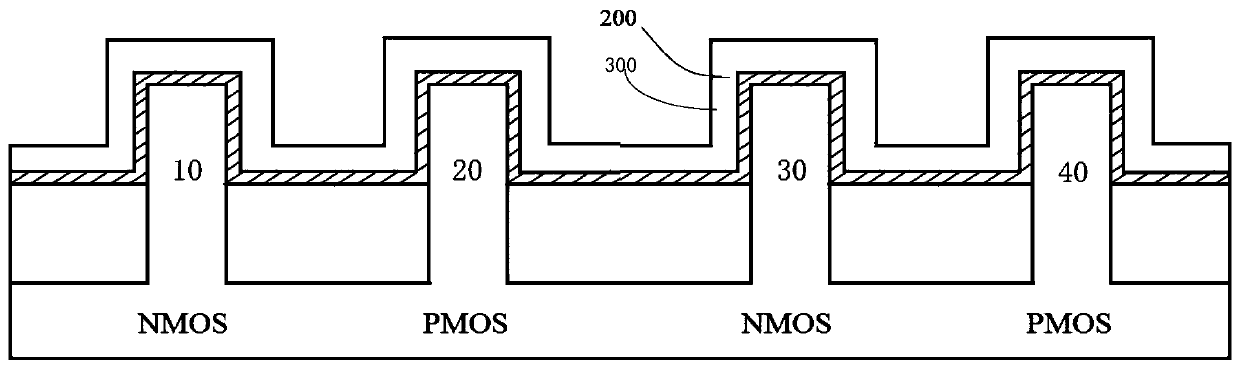

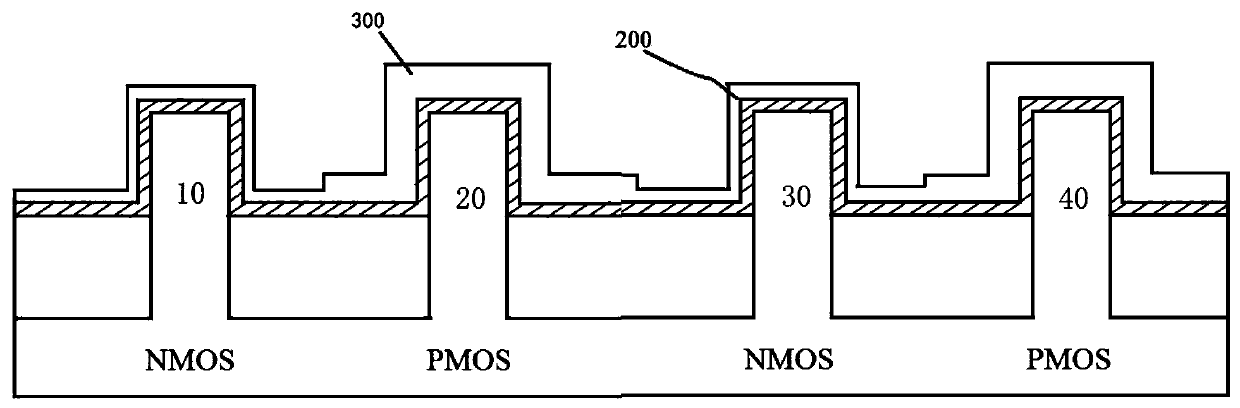

[0093] A substrate 100, the substrate 100 includes an NMOS area and a PMOS area, the NMOS area includes the first fin 10 and the second fin 30, and the PMOS area includes the third fin 20 and the fourth fin 40;

[0094] The first barrier layer 200 is located on the NMOS region and the PMOS region, and the first barrier layer 200 has different thicknesses on the first fin 10 and the second fin 30;

[0095] A first work function layer 300, the first work function layer 300 is located on the first barrier layer 200 of the PMOS region;

[0096] The second work function layer 400, the second work function layer 400 is located on the first barrier layer 200 in the NMOS region and on the first work function layer 300 in the PMOS region, wherein the second work function layer 400 The third fin 20 and the fourth fin 40 have the second work function layer 400 with different thicknesses.

[009...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More