Method for adjusting threshold of high-K metal gate CMOS device and CMOS device

A metal gate and device technology, applied in the field of semiconductor integration, can solve the problems of channel process damage, poor controllability, inaccurate corrosion thickness of barrier layer and work function layer materials, etc., to reduce process damage, large controllable range, Integrate the effect of a simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

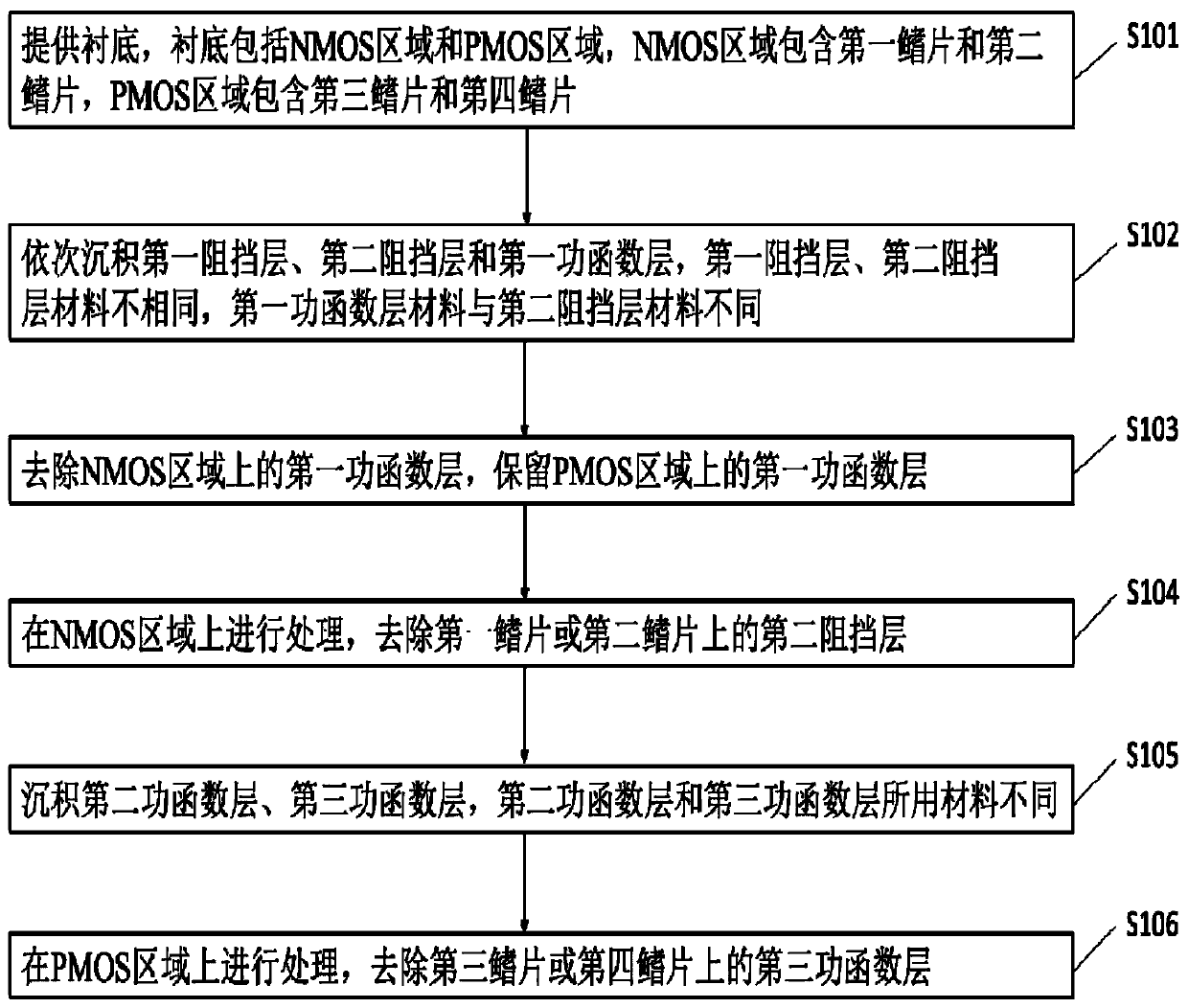

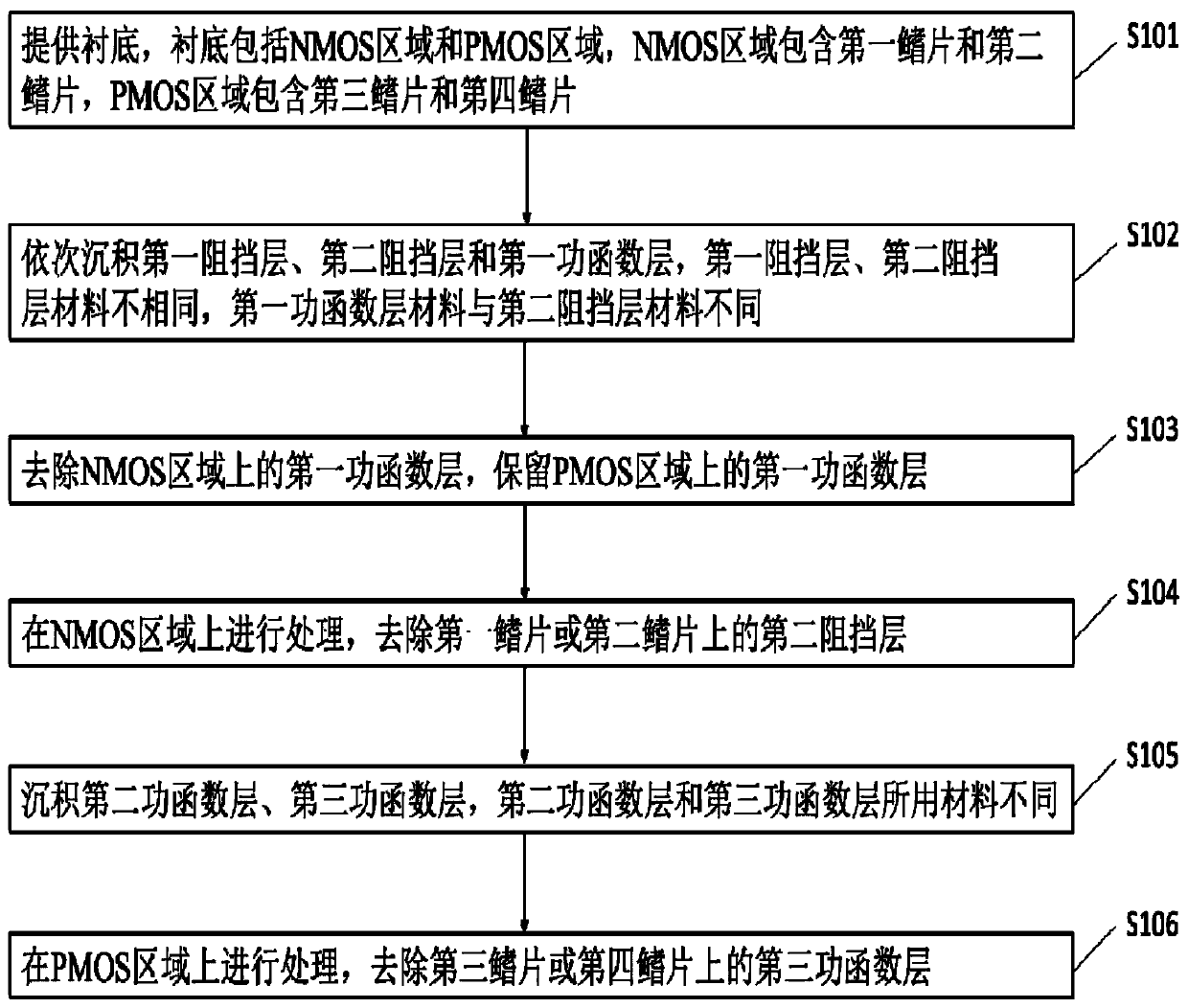

[0042] In this embodiment, a method for adjusting the threshold of a high-K metal gate CMOS device is provided, such as figure 1 shown, including:

[0043] Step S101, providing a substrate.

[0044] The substrate includes an NMOS area and a PMOS area, the NMOS area includes a first fin and a second fin, and the PMOS area includes a third fin and a fourth fin.

[0045] In the embodiment of the present application, an isolation layer / high-k dielectric layer may be disposed on the fin of the substrate.

[0046] Step S102, depositing a first barrier layer, a second barrier layer and a first work function layer in sequence.

[0047] The materials of the first barrier layer and the second barrier layer are different, and respectively include one of the following materials: TiN, TaN, TiNSi.

[0048] The first work function layer includes at least one or a combination of the following materials: TiN, TaN, TiNx, TaNx, TiNSi, and the material of the first work function layer is diffe...

Embodiment 2

[0074] In this embodiment, a CMOS device is provided, including:

[0075] a substrate, the substrate includes an NMOS region and a PMOS region, the NMOS region includes a first fin and a second fin, and the PMOS region includes a third fin and a fourth fin;

[0076] a first barrier layer located on the NMOS region and the PMOS region;

[0077] The second barrier layer is located only on the first fin region of the NMOS region and on the first barrier layer of the PMOS region, and the materials used for the first barrier layer and the second barrier layer are different;

[0078] a first work function layer, the first work function layer is located on the second barrier layer in the PMOS region, and the material of the first work function layer is different from the material of the second barrier layer;

[0079] a second work function layer located on the first barrier layer in the NMOS region, the second barrier layer and the first work function layer in the PMOS region;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More