A high and low channel sampling rate distribution method for EEG signal acquisition

A method of distribution, EEG signal technology, applied in the direction of diagnostic signal processing, electrical digital data processing, medical science, etc., to achieve the effect of equal sampling intervals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

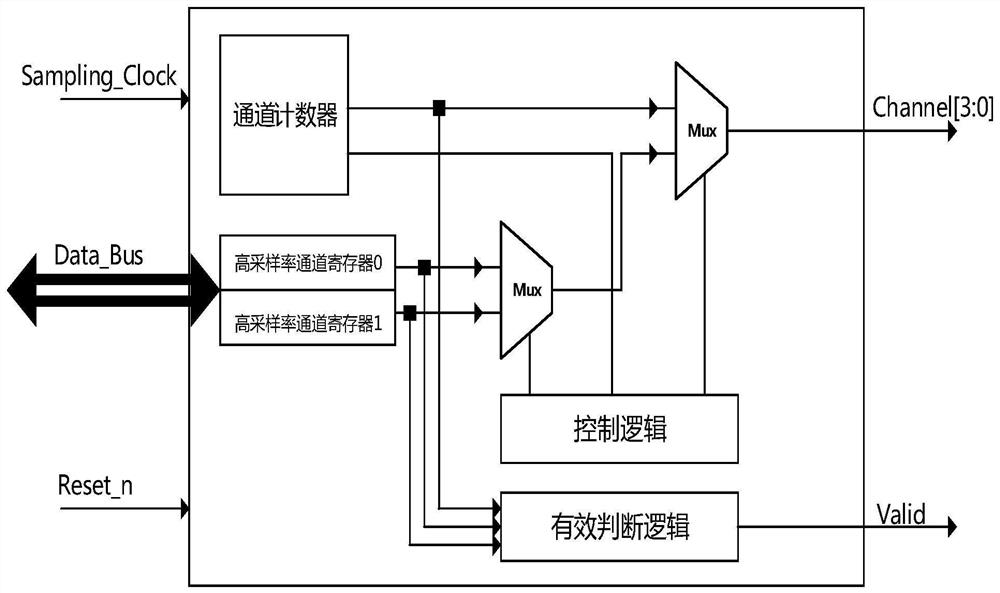

Method used

Image

Examples

example 1

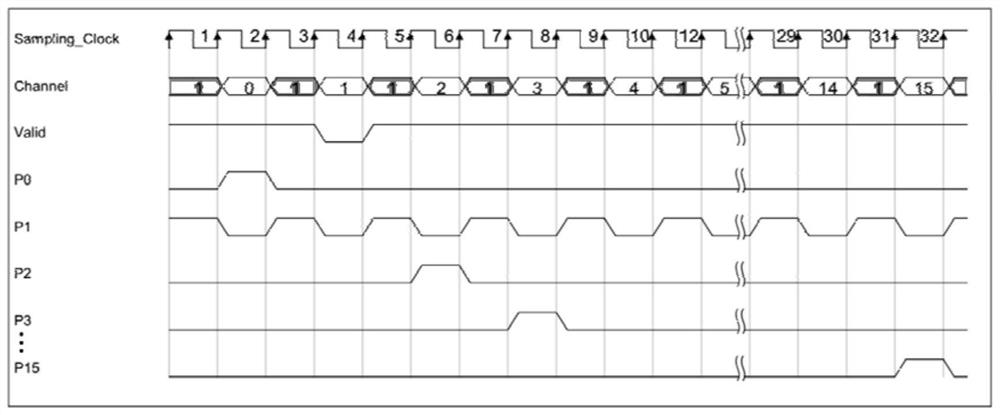

[0026]In this example, only channel 1 is allocated as a high sampling rate channel, and both high sampling rate channel registers are written with 1. Timing diagram such asfigure 2 Shown. In the figure, the Sampling_Clock labeled 1, 3, 5,..., 31 is the odd sampling clock, which corresponds to the shaded part of the Channel, and the Sampling_Clock labeled 2, 4, 6, ..., 32 in the figure is the even sampling clock. Corresponds to the non-shaded part of the Channel. At the odd-numbered sampling clocks labeled 1, 5, 9,..., 29, read the high sampling rate channel register 0 and output the value 1 to Channel, and at the odd-numbered sampling clocks labeled 3, 7, 11,..., 31 Sampling clock, read high sampling rate channel register 1 and output the value 1 to Channel. At the even-numbered sampling clock, the channel counter is incremented by 1, and if it reaches the maximum value (15 in this example), the counting is restarted, and the value of the channel counter is output to the Channel. In...

example 2

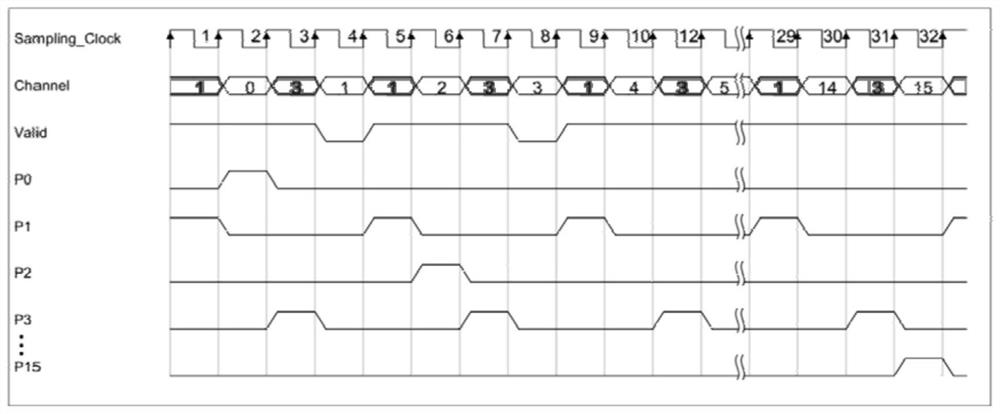

[0028]In this example, channel 1 and channel 3 are allocated as high-sampling-rate channels, high-sampling-rate channel register 0 is written with 1, and high-sampling-rate channel register 1 is written with 3. Timing diagram such asimage 3Shown. At the odd-numbered sampling clocks labeled 1, 5, 9,..., 29, read the high sampling rate channel register 0 and output the value 1 to Channel, and at the odd-numbered sampling clocks labeled 3, 7, 11,..., 31 Sampling clock, read high sampling rate channel register 1 and output value 3 to Channel. At the even-numbered sampling clock, the channel counter is incremented by 1, and if it reaches the maximum value (15 in this example), the counting is restarted, and the value of the channel counter is output to the Channel. In the even-numbered sampling clock labeled 4, the output channel counter is 1 at this time, and the valid judgment logic circuit judges that the value has been stored in the high sampling rate channel register group, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More