Method, system and related device for parallel execution of multi-algorithms of cryptographic cards

A cryptographic card and multi-algorithm technology, applied in the protection of internal/peripheral computer components, can solve the problems of wasting logic computing resources and reducing computing efficiency, and achieve the effect of improving computing efficiency and high utilization of hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

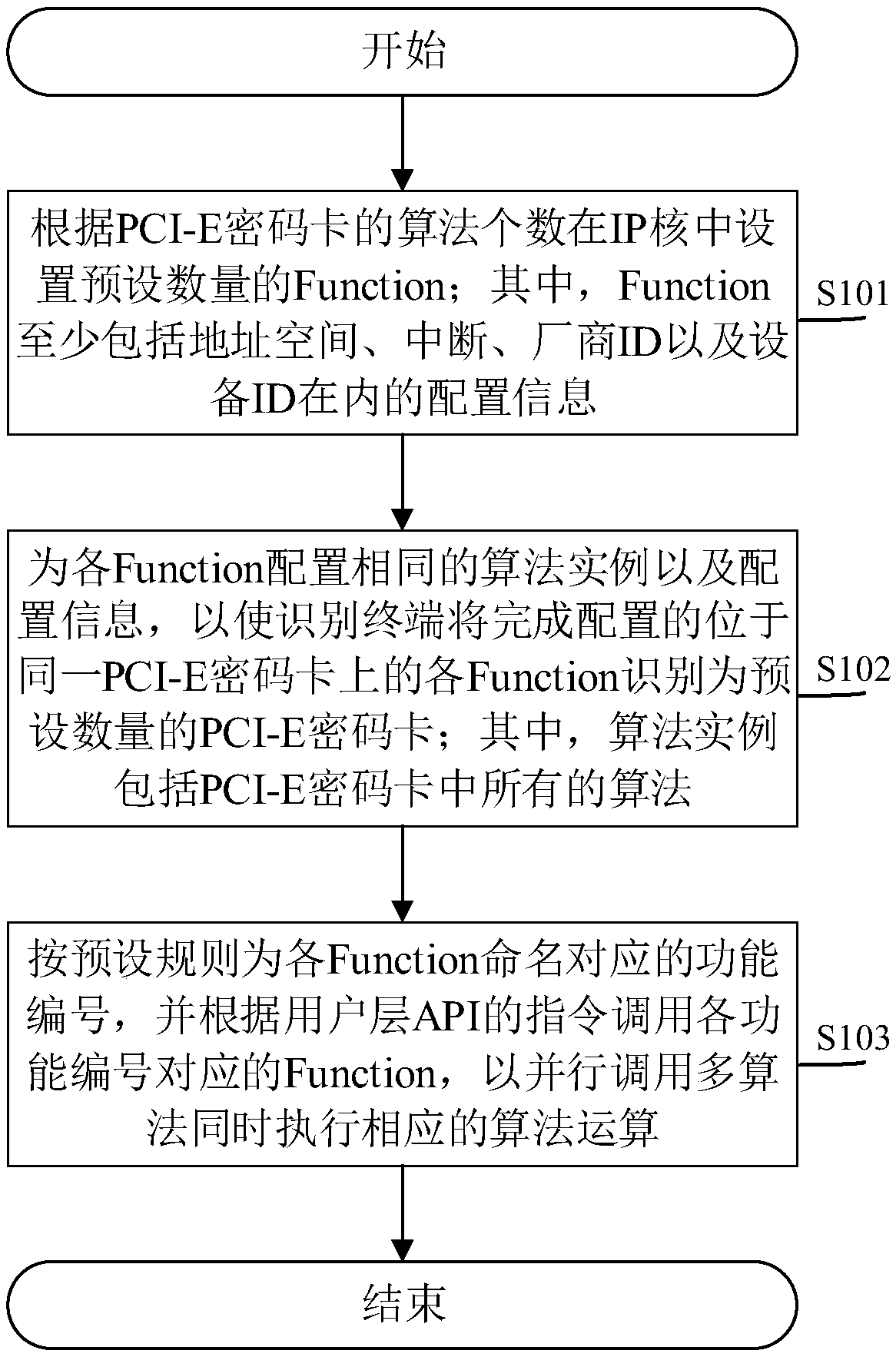

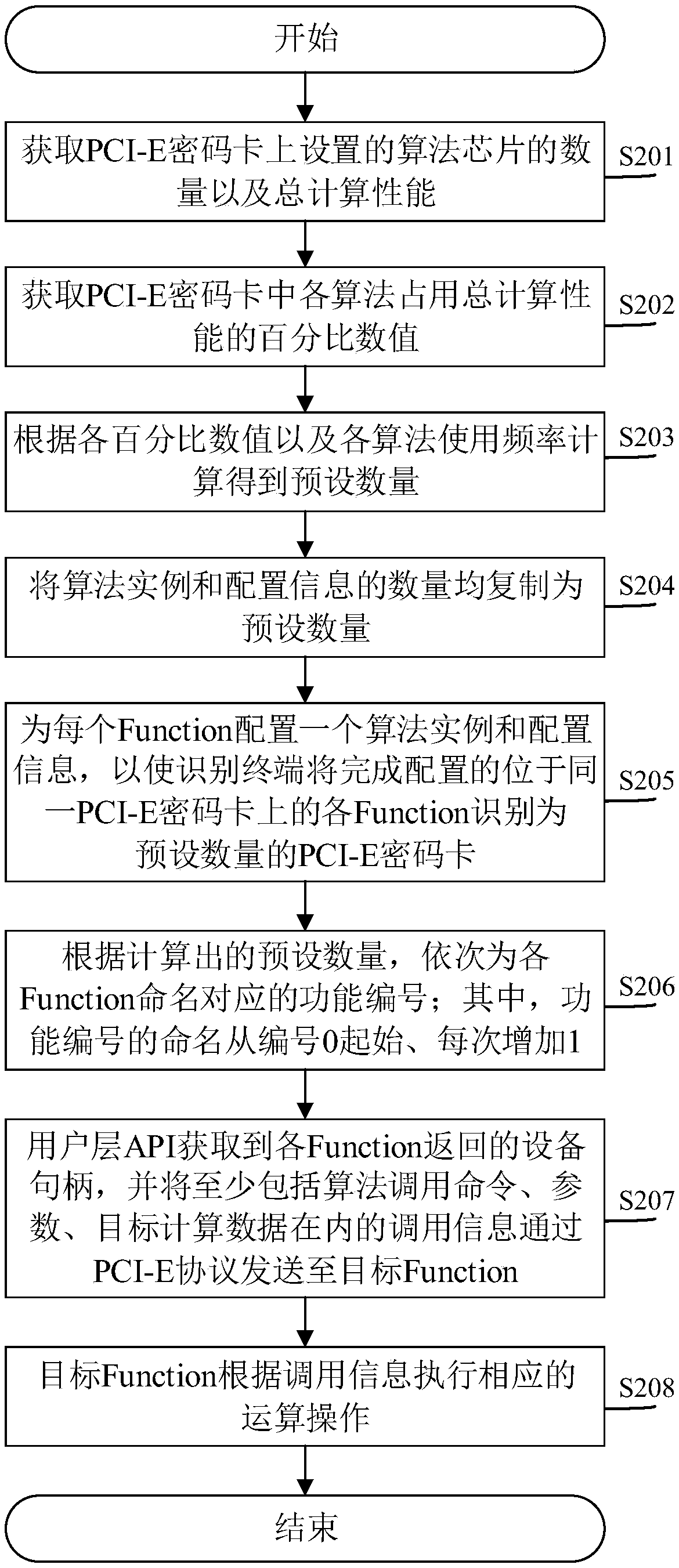

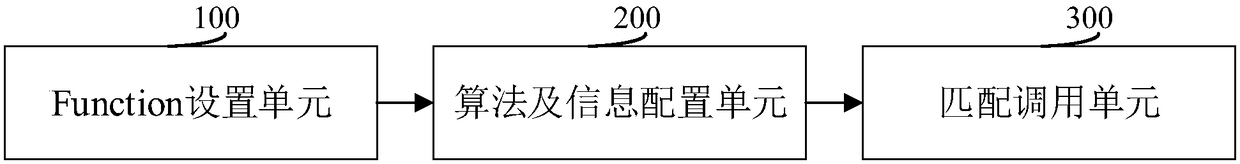

[0044] The core of this application is to provide a method for parallel execution of multiple algorithms of a cipher card, which is applied to a PCI-E cipher card based on FPGA, and can more scientifically and rationally use the logical computing resources and hardware provided by the inherent hardware of the PCI-E cipher card The resource utilization rate is higher, so that multiple algorithms are in the operation state at the same time or at the same time interval, which significantly improves the operation efficiency.

[0045] In order to make the purposes, technical solutions and advantages of the embodiments of the present application clearer, the technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Obviously, the described embodiments It is a part of the embodiments of this application, not all of them. Based on the embodiments in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com