Array substrate and display panel

一种阵列基板、薄膜晶体管的技术,应用在静态指示器、光学、仪器等方向,能够解决显示不均、影响像素单元像素电压等问题,达到显示画面质量高、显示效果均匀的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

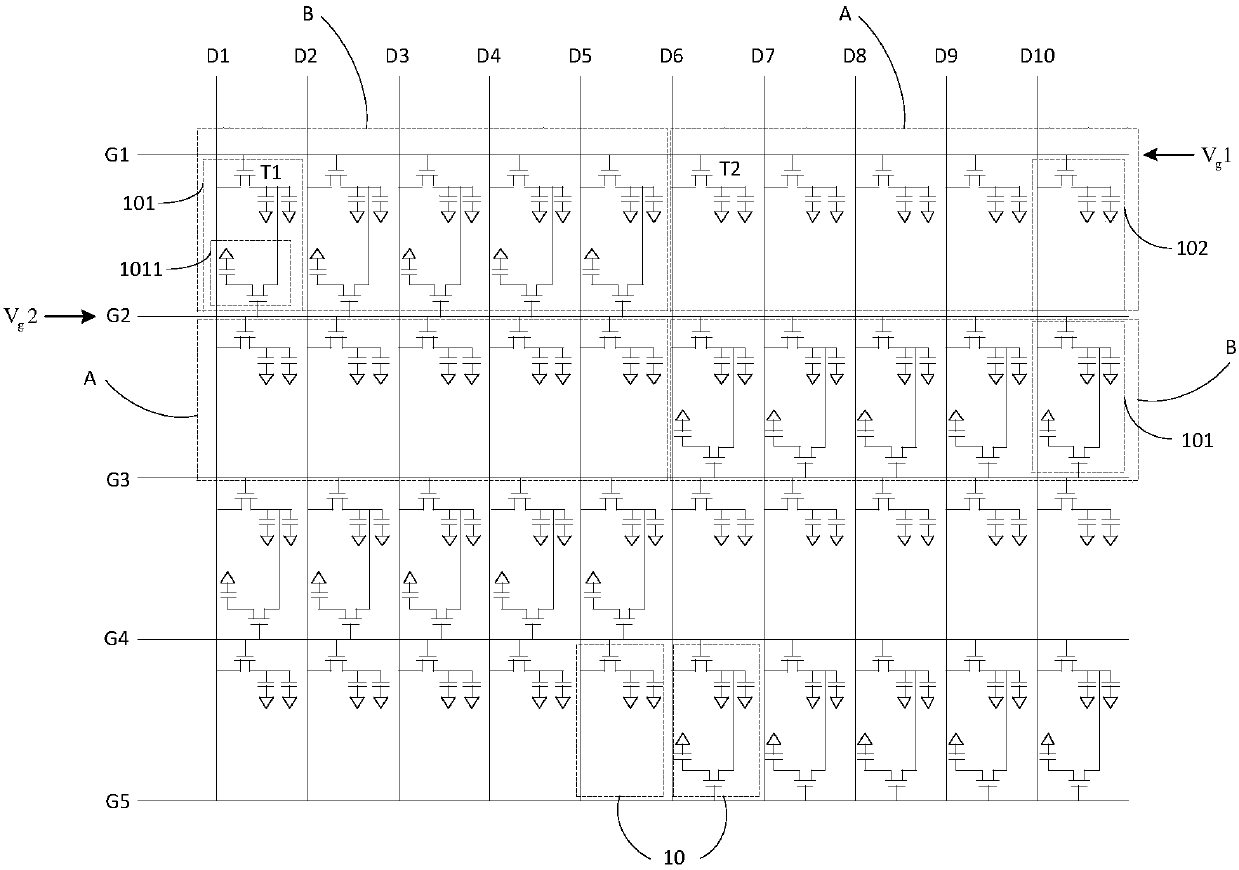

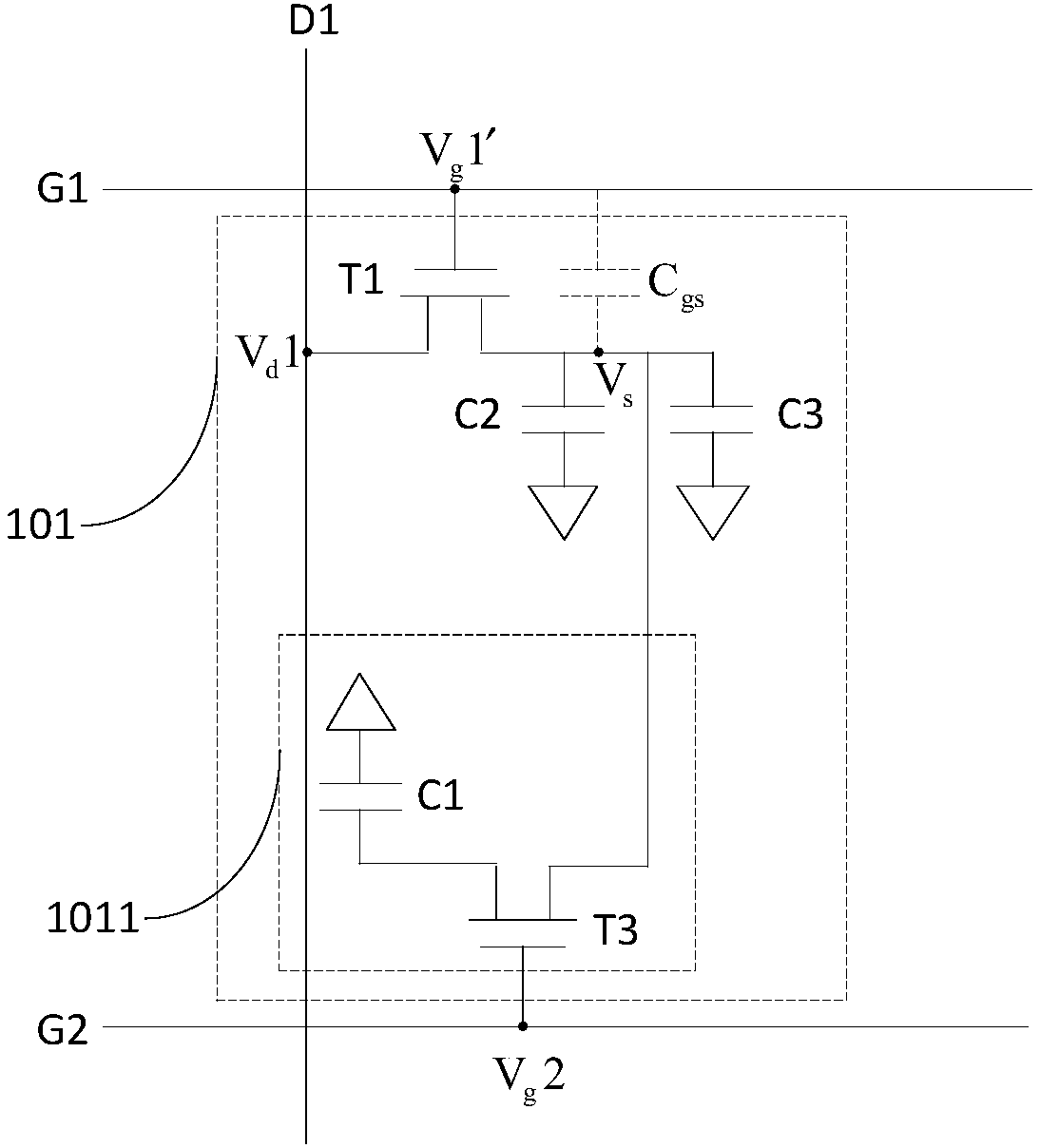

[0019] The present invention provides the array substrate of the first embodiment. See figure 1 , the array substrate disclosed in this embodiment includes:

[0020] A plurality of scanning lines Gn, this embodiment takes the scanning lines G1 to G5 as an example for illustration;

[0021] A plurality of data lines Dn, this embodiment is described by taking the data lines D1 to D10 as an example, and are arranged to intersect with a plurality of scanning lines Gn to form a plurality of pixel units 10;

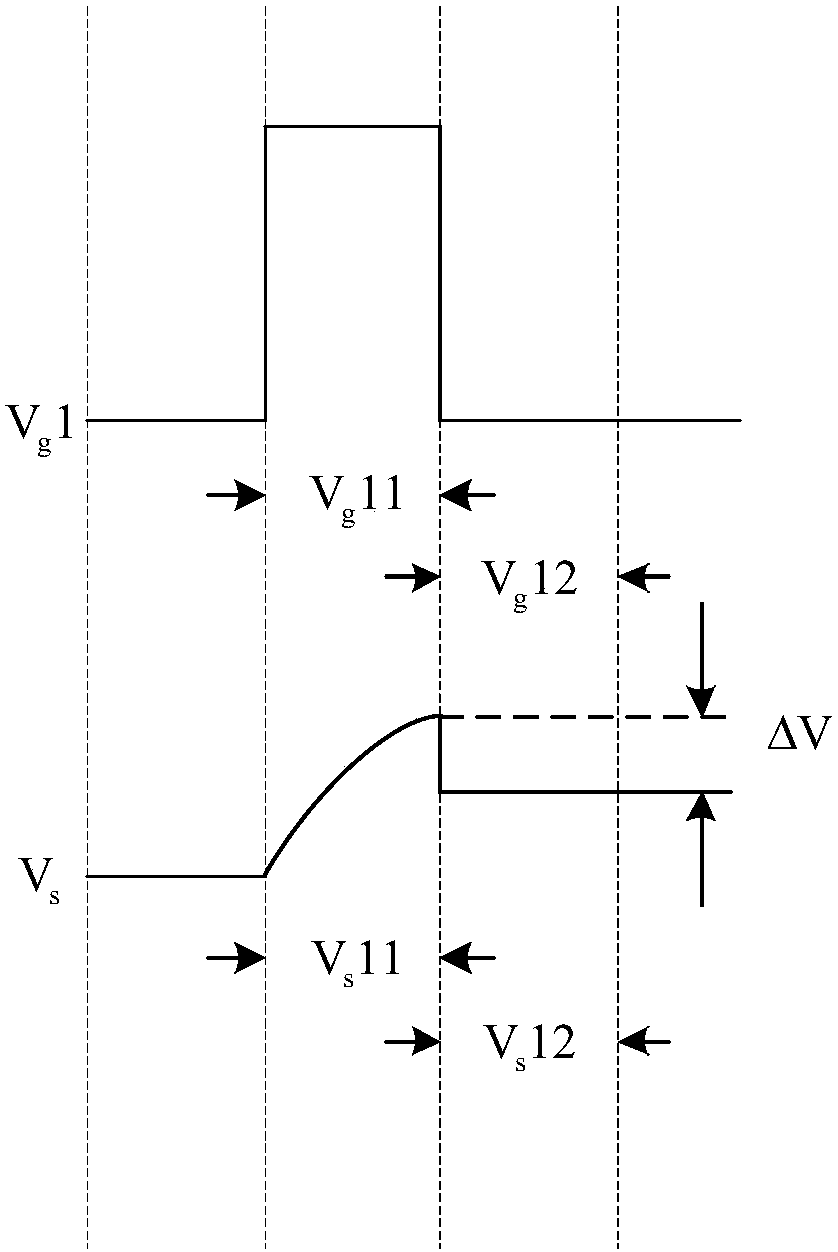

[0022] Wherein, the plurality of pixel units 10 are divided into a first area A and a second area B along the direction of the scanning line Gn, the first area A is close to the scanning signal input end, and the second area B is far away from the scanning signal input end. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More