A SRAM memory cell circuit with low bit line leakage current

A technology of memory cell circuit and leakage current, applied in the field of memory array and SRAM memory cell circuit, can solve the problems of easy failure of write operation, limited read and write ability, read interference, etc., and achieve high write margin, save area and power consumption , the effect of low static power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in detail below in conjunction with the accompanying drawings and application examples.

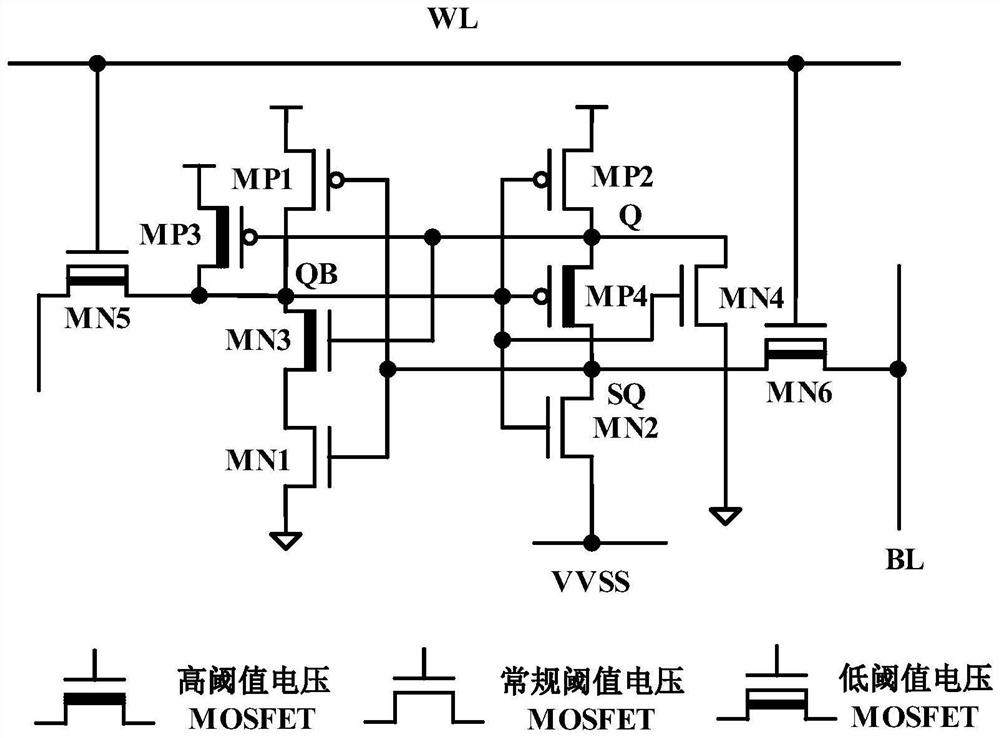

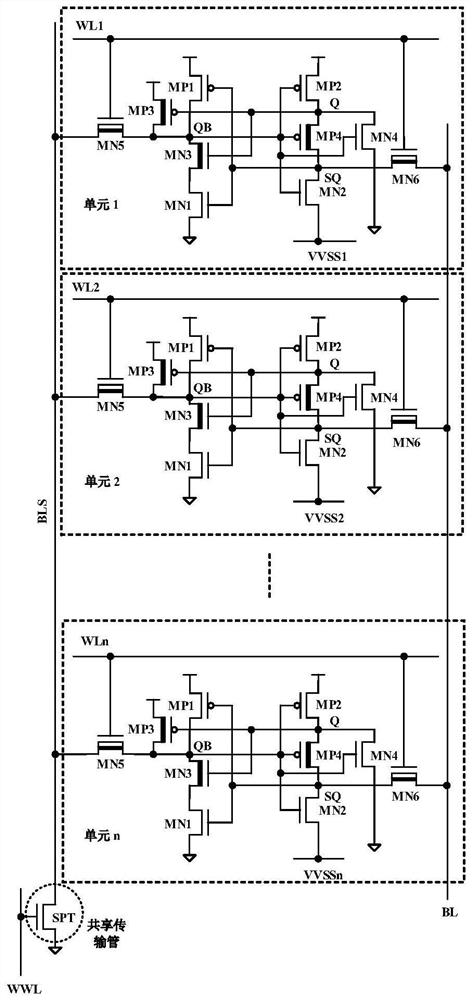

[0027] The SRAM storage unit circuit of the low bit line leakage current proposed by the present invention is a 10T structure, and its specific circuit structure is as follows figure 2 As shown, it includes the first NMOS transistor MN1, the second NMOS transistor MN2, the third NMOS transistor MN3, the fourth NMOS transistor MN4, the fifth NMOS transistor MN5, the sixth NMOS transistor MN6, the first PMOS transistor MP1, the second PMOS transistor MP2, the third PMOS transistor MP3 and the fourth PMOS transistor MP4, wherein in order to improve the read and write performance of the SRAM storage unit circuit, the third NMOS transistor MN3, the third PMOS transistor MP3 and the fourth PMOS transistor MP4 can be set as high threshold MOS The fifth NMOS transistor MN5 and the sixth NMOS transistor MN6 are set as low-threshold MOS transistors; t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More