Testing device and method for FPGA chip function

A technology of functional testing and chip testing, which is applied in measuring devices, digital circuit testing, electronic circuit testing, etc. It can solve the problems of no automatic comparison function between test results and simulation results, limited test input timing signals, and impossibility of execution.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

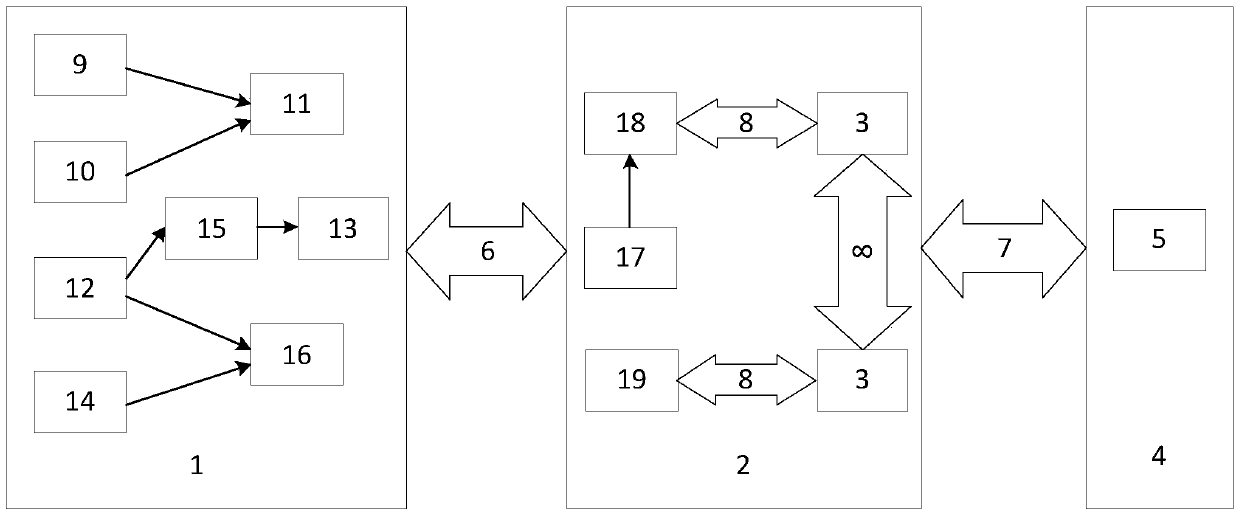

[0028] Such as figure 1 As shown, the FPGA chip functional testing device of the present invention comprises host computer 1, PXIe chassis 2, high-speed digital I / O card 3, PCB board 4, FPGA chip 5 to be tested, and host computer 1 passes Ethernet line 6 and PXIe chassis 2 The PXIe chassis 2 is inserted with a high-speed digital I / O card 3, the high-speed digital I / O card 3 communicates with each other through the PXIe bus 8, and the high-speed digital I / O card 3 communicates with the PCB board 4 through the I / O cable 7 The PCB board 4 is provided with a chip packaging socket, and the FPGA chip 5 to be tested is placed on the PCB board 4 chip socket.

[0029] The host computer 1 is provided with a pin parameter setting module 9 for setting the number of pins of the chip to be tested and the properties of the pins; for setting the configurati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More