Patents

Literature

56 results about "Chip and PIN" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Chip and PIN is a brand name adopted by the banking industries in the United Kingdom and Ireland for the EMV smart card payment system for credit, debit, and ATM cards. "Chip" refers to a computer chip embedded in the smartcard, and "PIN" refers to a personal identification number that the customer must supply. "Chip and PIN" is also used in a generic sense to mean any EMV smart card technology that relies on an embedded chip and a PIN. Chip and signature, which as the name implies, is an alternative implementation that requires the cardholder to verify identity by signing a printed receipt rather than entering a PIN.

Dynamic Account Selection

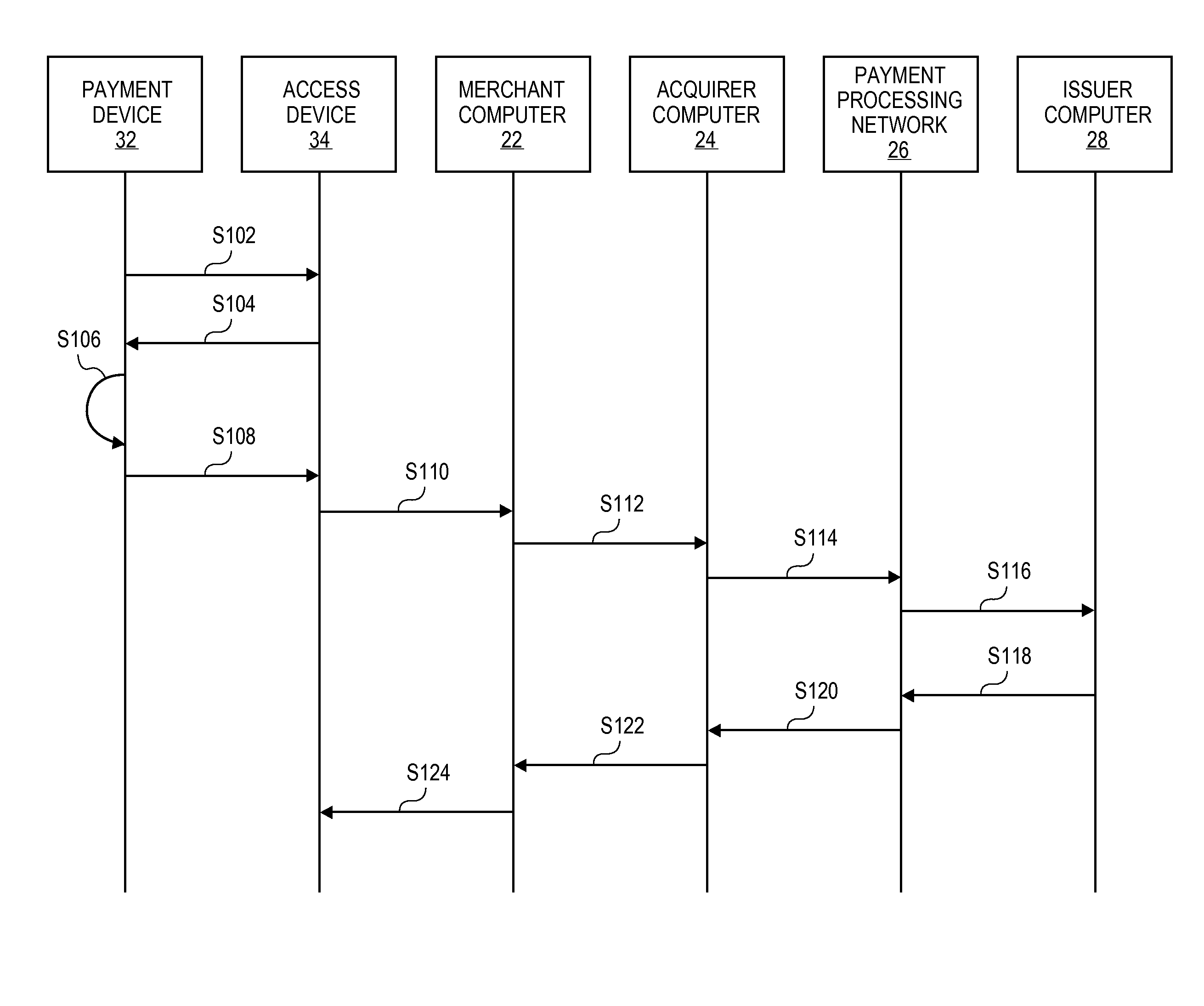

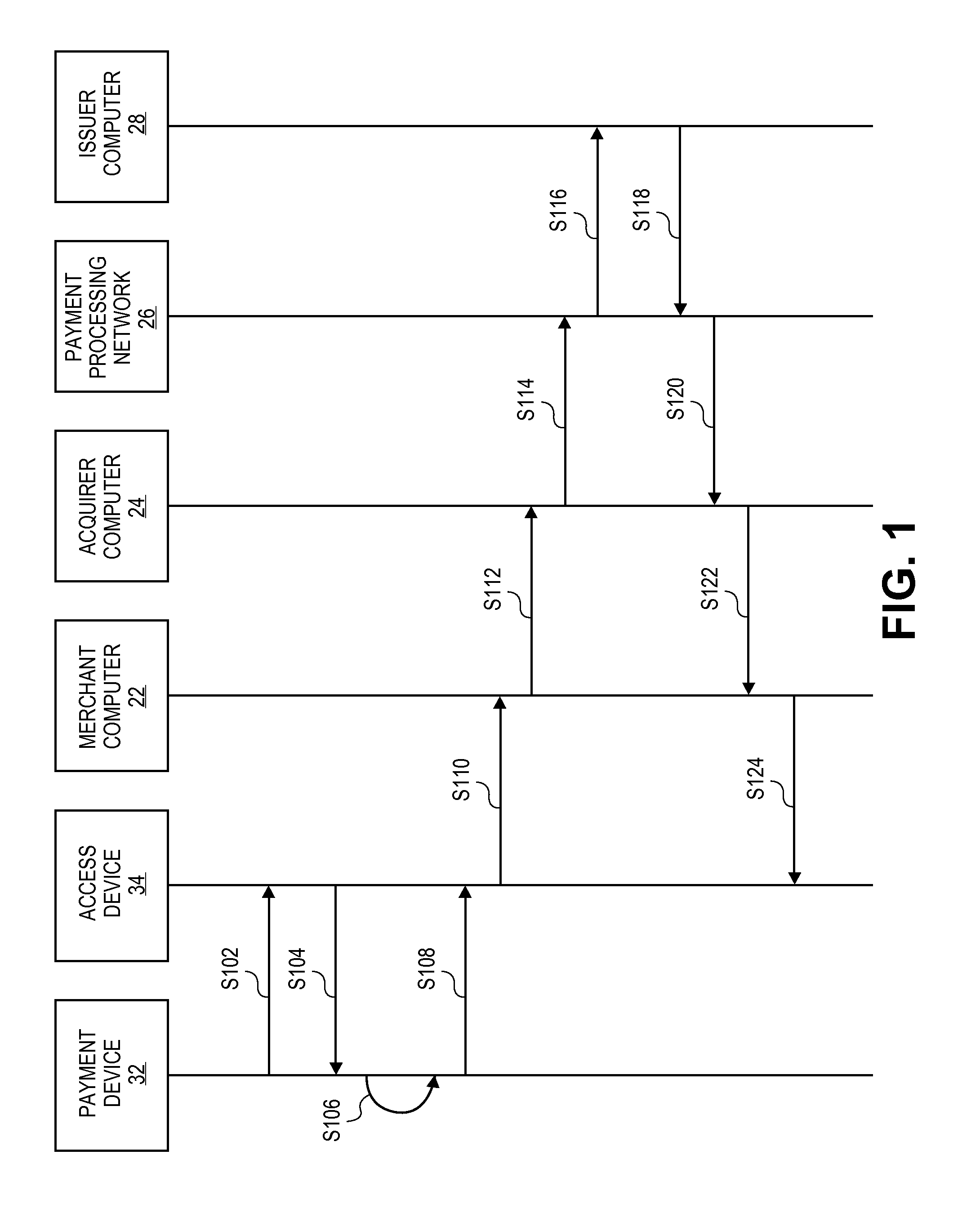

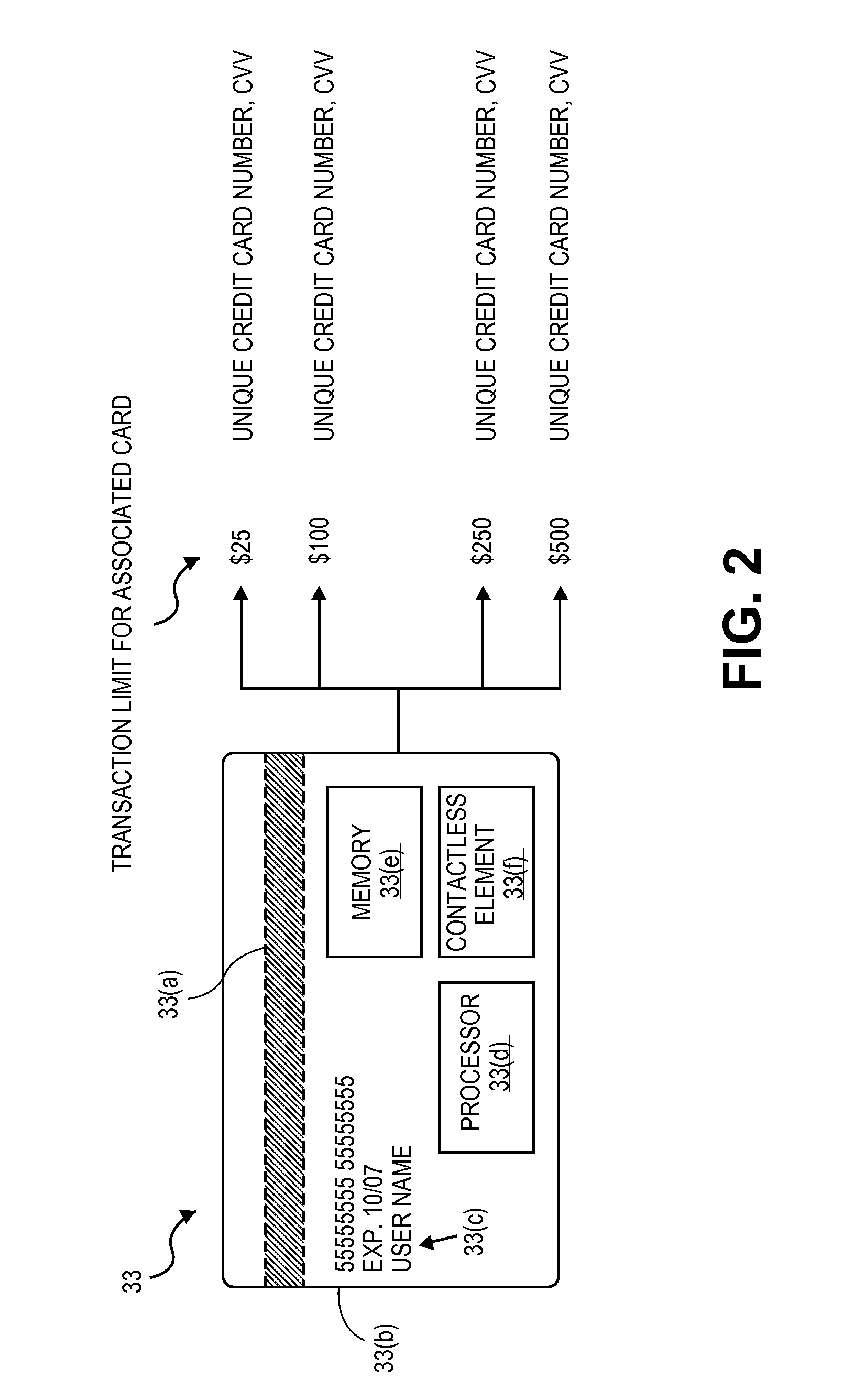

Embodiments automatically select one of the multiple pre-generated payment cards provisioned on a mobile device. The multiple pre-generated payment cards (real or virtual) may each have a different credit limit. The mobile device may automatically select one of the multiple payment cards based on a transaction value of a transaction that is being conducted. An available credit limit of the selected payment card may be equal to or slightly greater than the transaction value. In some embodiments, the available credit limit of the selected payment card may be closer to the transaction value than the available credit limits of the remaining payment cards. In some embodiments, the different payment cards may be provisioned in a chip-and-pin based smart credit card or mobile wallet.

Owner:VISA INT SERVICE ASSOC

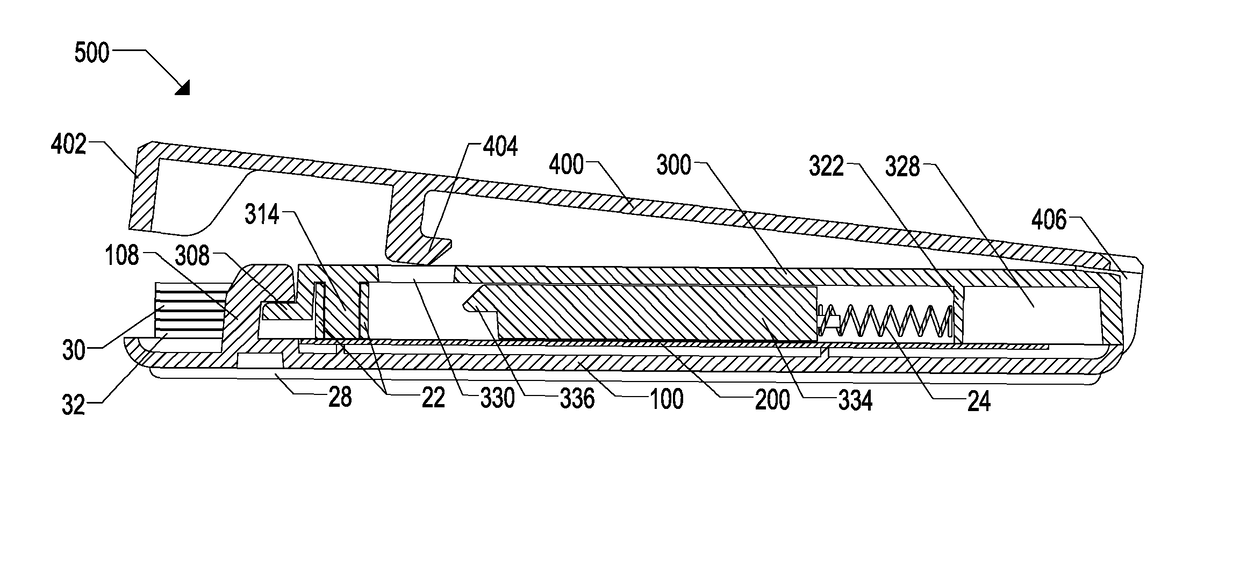

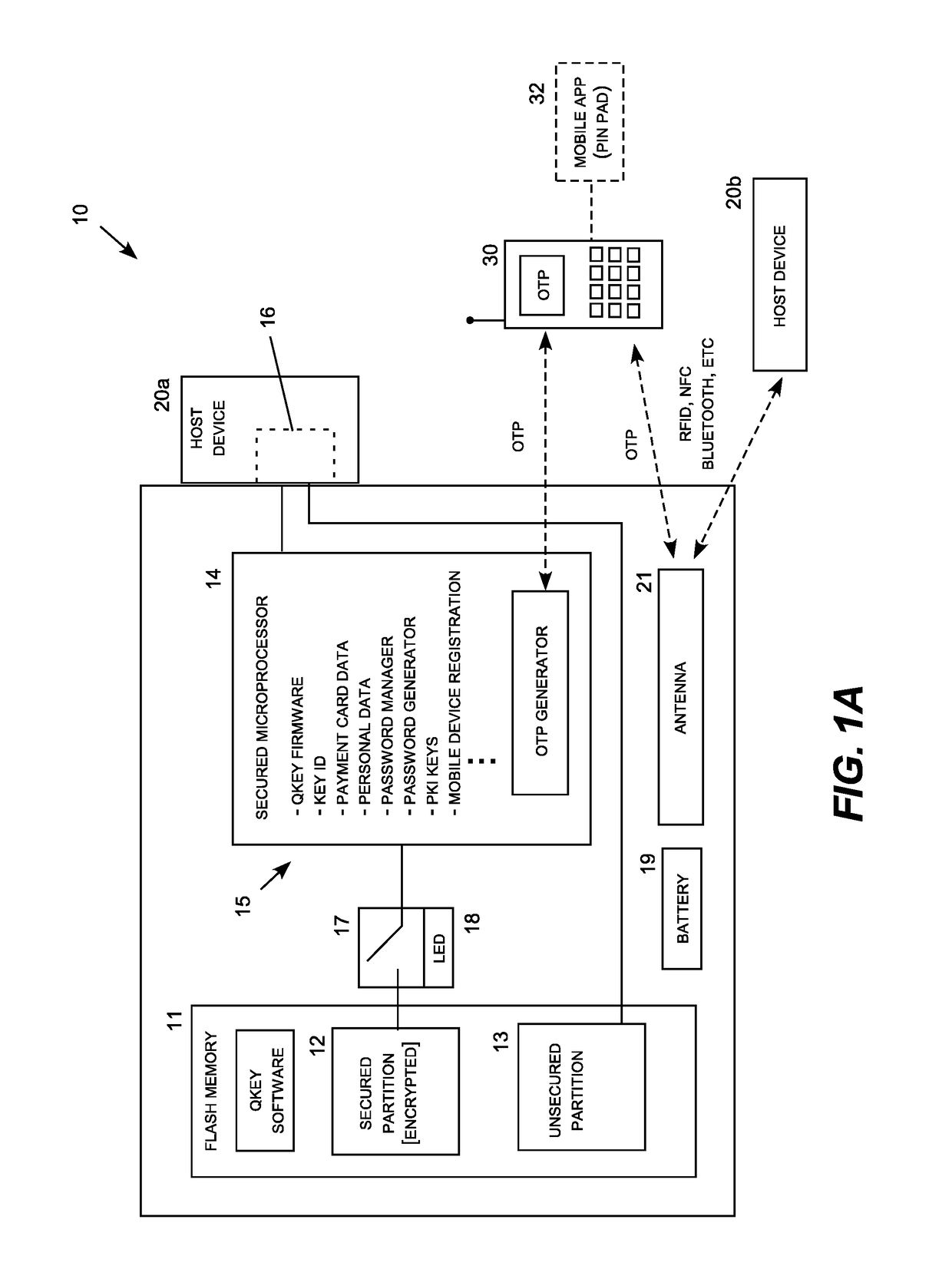

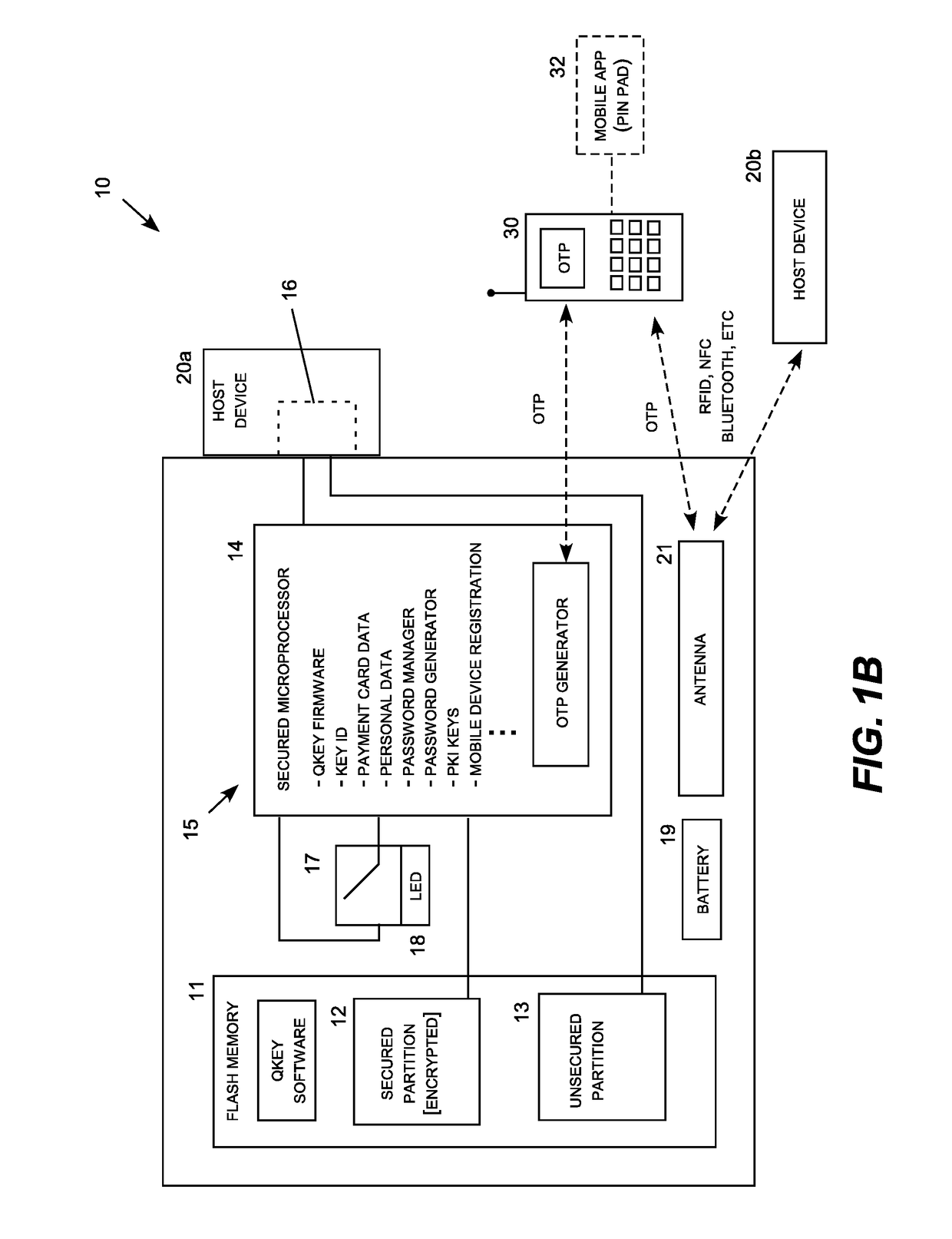

Data storage key for secure online transactions

ActiveUS20150199684A1Reduce usagePayment protocolsInternal/peripheral component protectionSecure Electronic TransactionPhysical shape

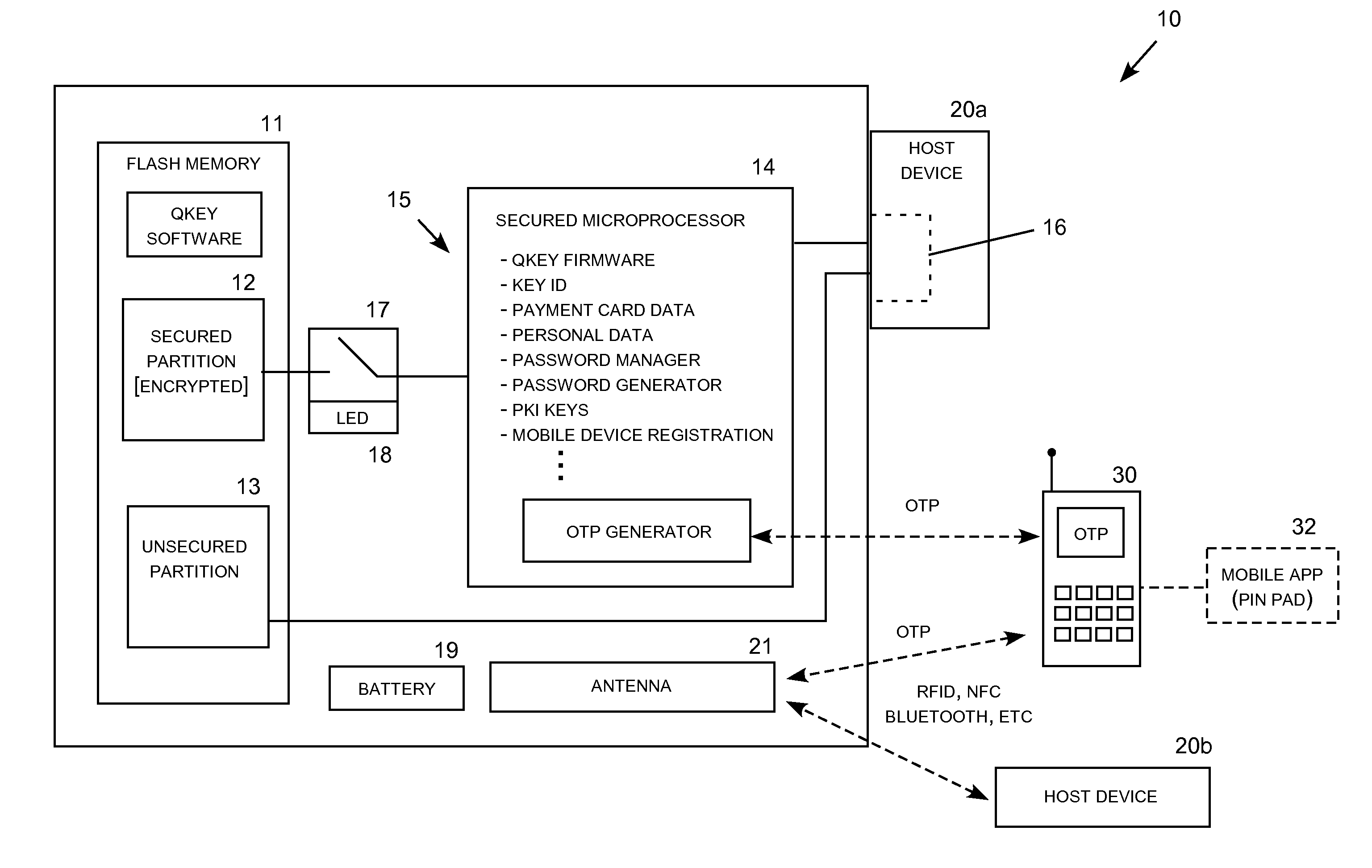

A secure non-volatile solid state memory data key appears similar to a conventional USB flash drive modified to have a physical shape resembling a door key with an eyelet for attaching the data key to a key ring or lanyard. The data key includes a USB port, a microprocessor (effectively serving as the “chip” in the chip-and-pin configuration), and a secure memory for holding secure transaction information, such as credit and debit card numbers, verified personal identification (federated ID), and other secure data. A biometric sensor (e.g., touch sensor or “capcha”) verifies that a person is in physical possession of the data key before permitting access to the secure memory. The touch sensor may be limited to use by a unique individual person through a biometric reader, such as a finger print reader, where the verification finger print is stored on the key rather than the connected host device.

Owner:UQONTROL

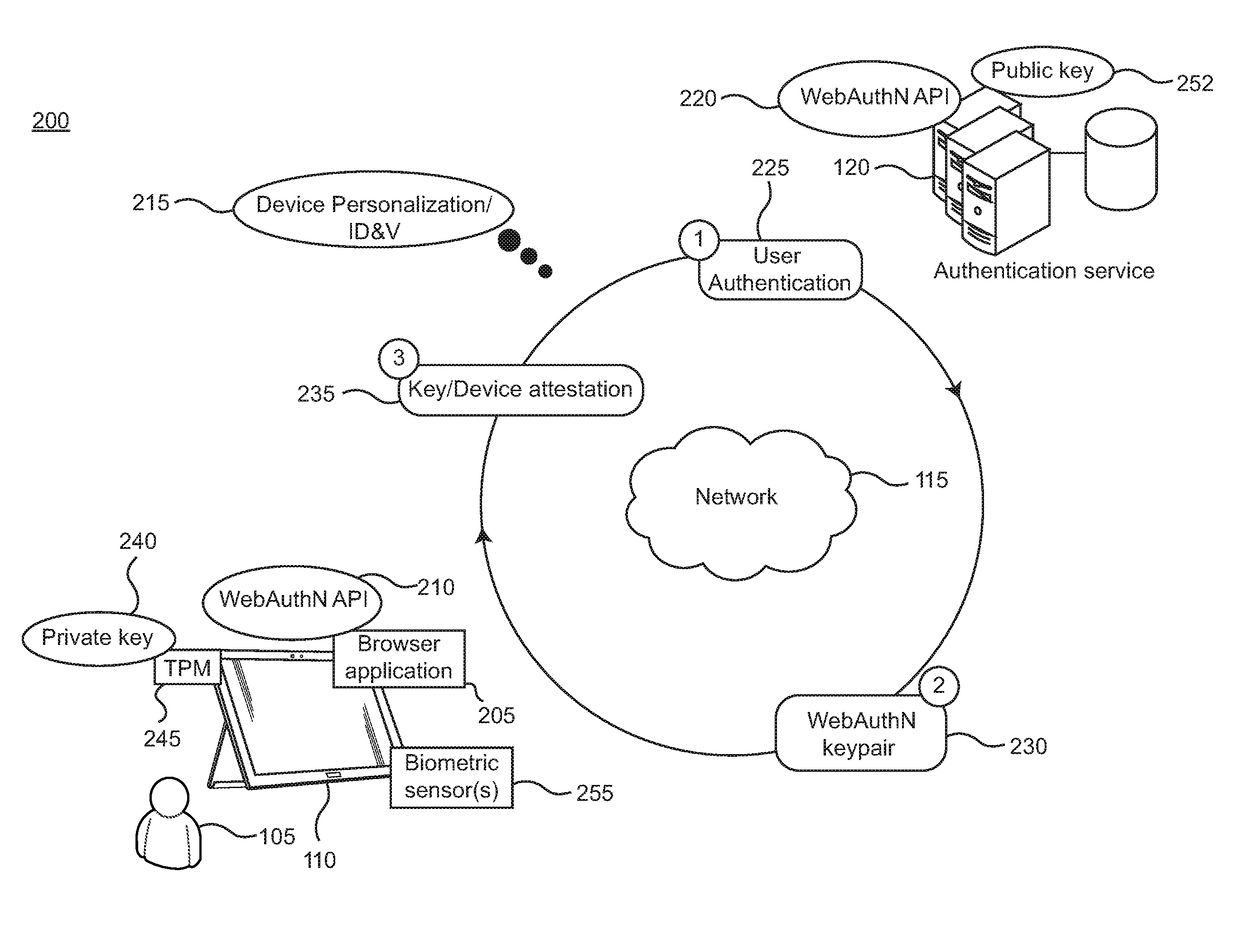

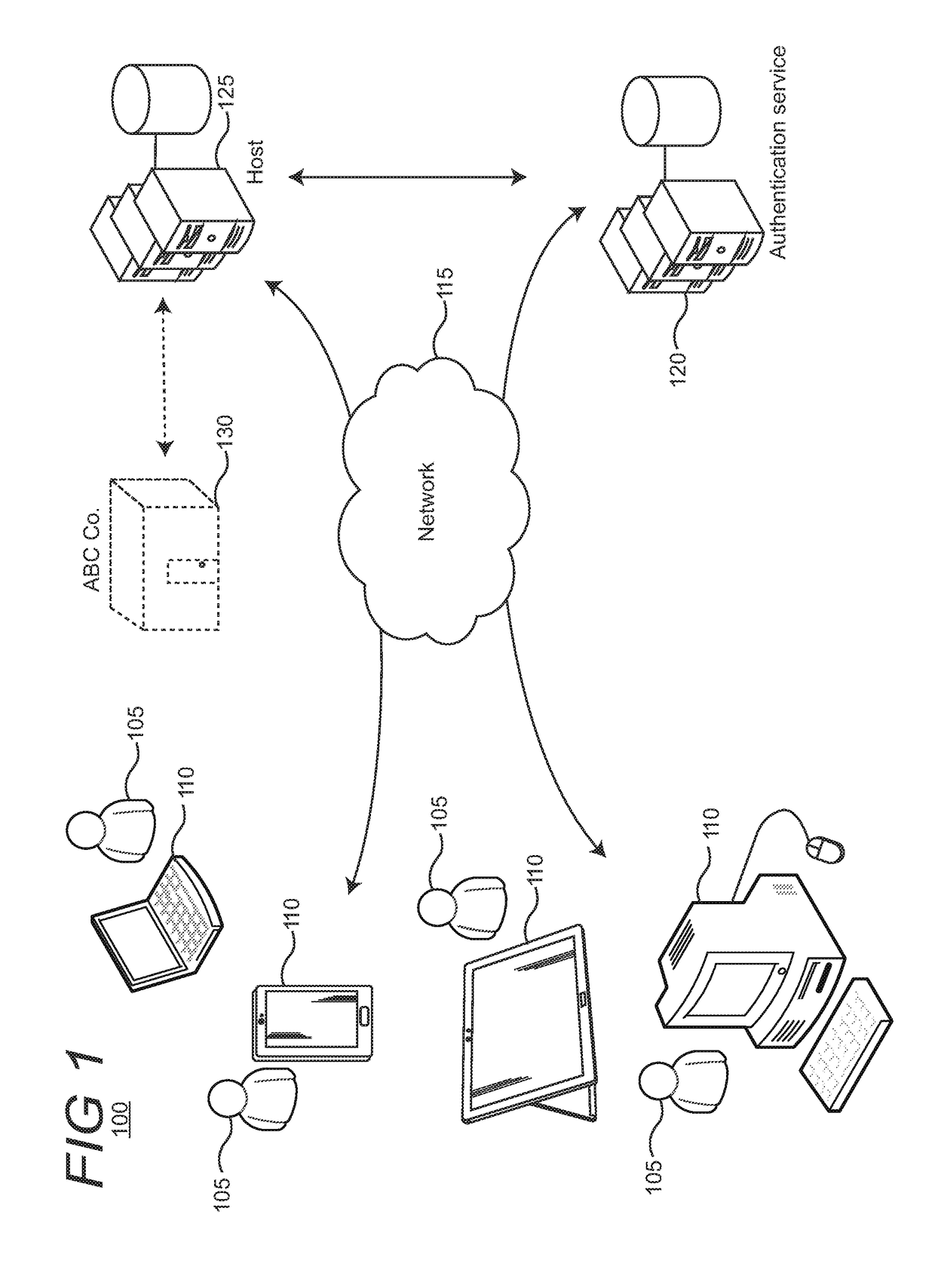

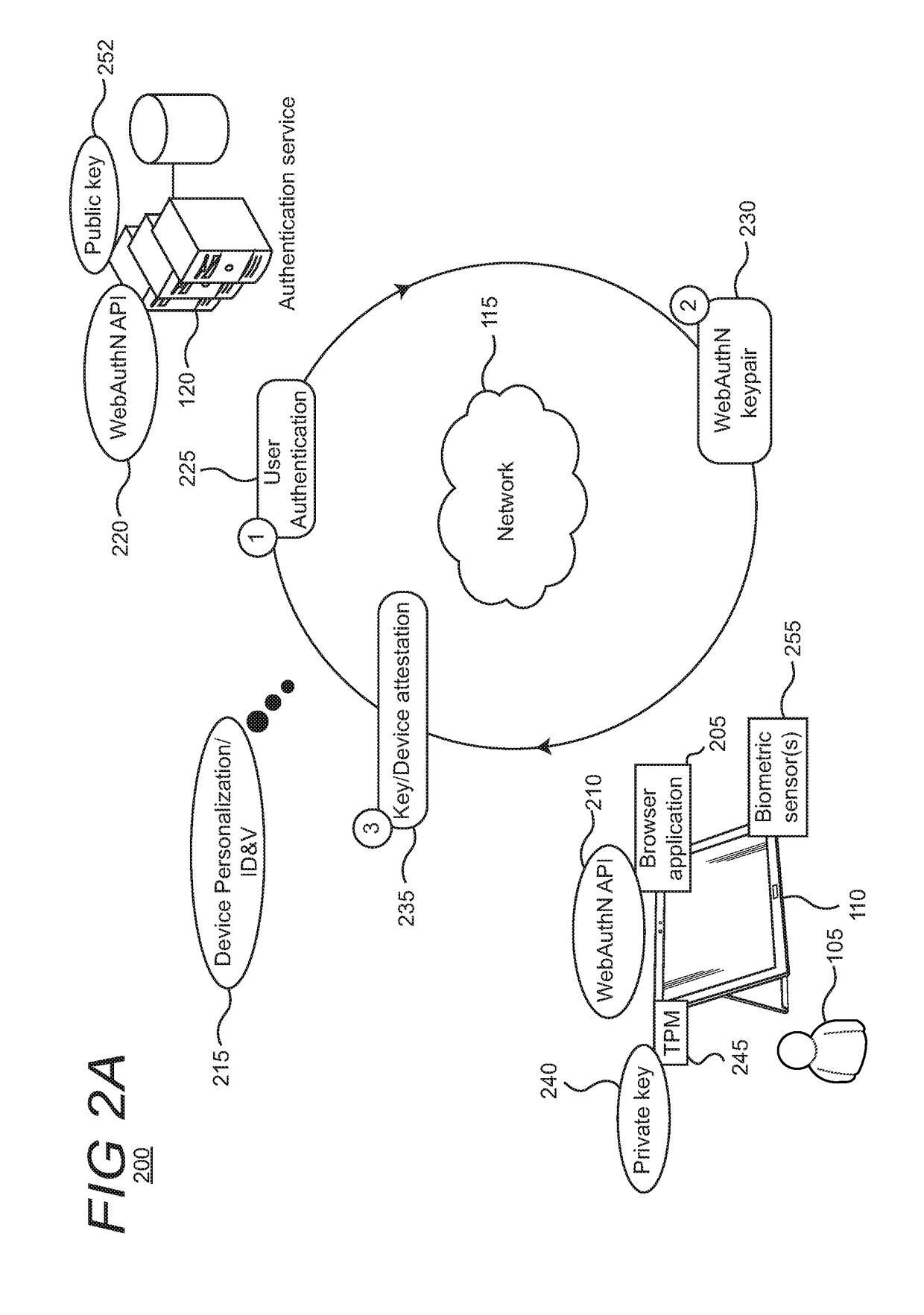

User and device authentication for web applications

InactiveUS20180101850A1Improve bindingImprove securityDigital data authenticationTransmissionComputer hardwareWeb application

A computing device supports a Web Authentication (WebAuthN) application program interface (API) that is configured to exposes functionalities that may substitute for those utilized in the EMV (Europay, Mastercard, and Visa) standard for transactions using smart payment instruments like debit and credit cards that include embedded computer chips. The functionality of the WebAuthN-compliant computing device is analogous to a physical card in the conventional chip and PIN (personal identification number) where the chip serves as proof of payment device and the PIN as proof of payment account holder.

Owner:MICROSOFT TECH LICENSING LLC

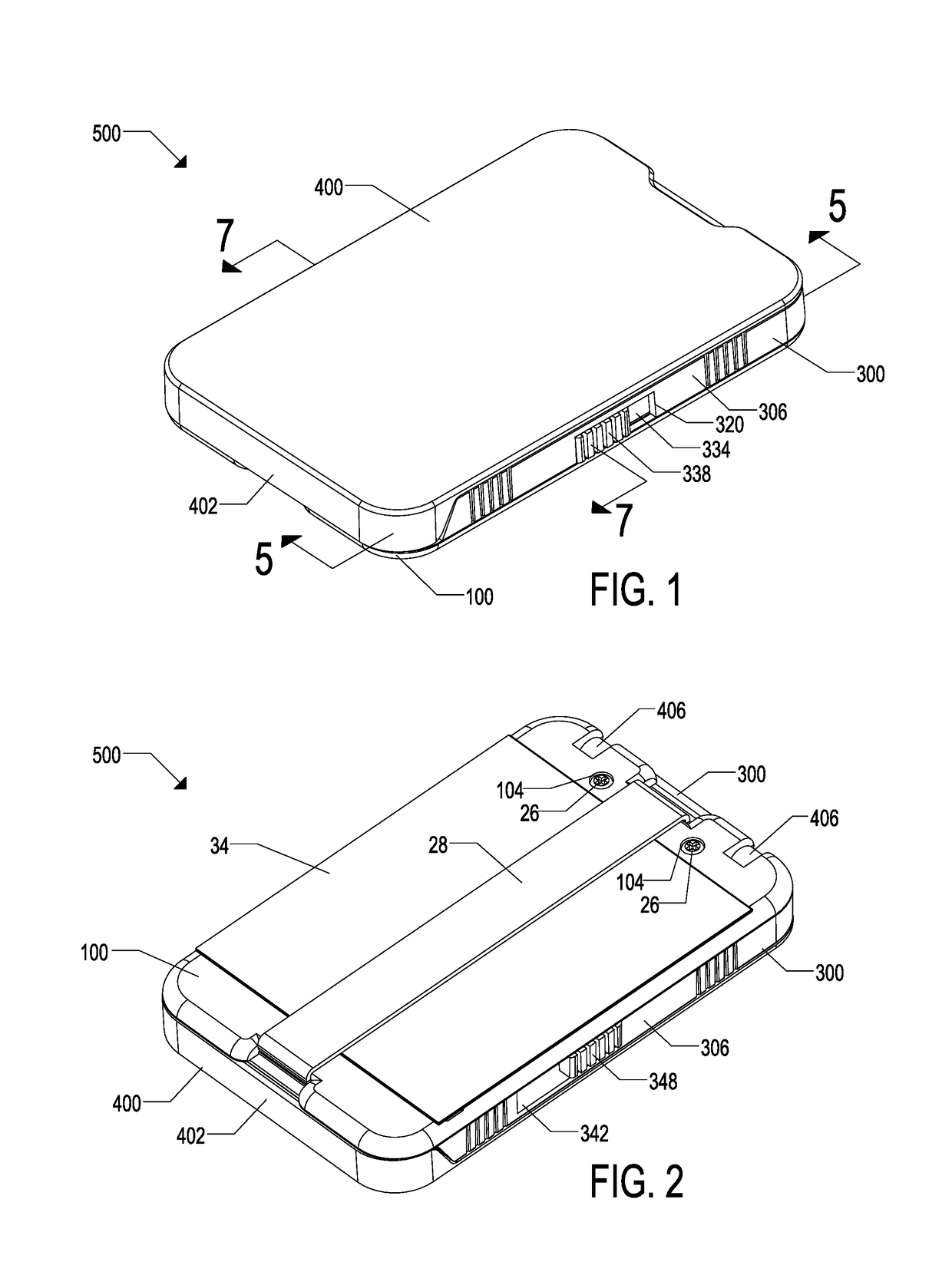

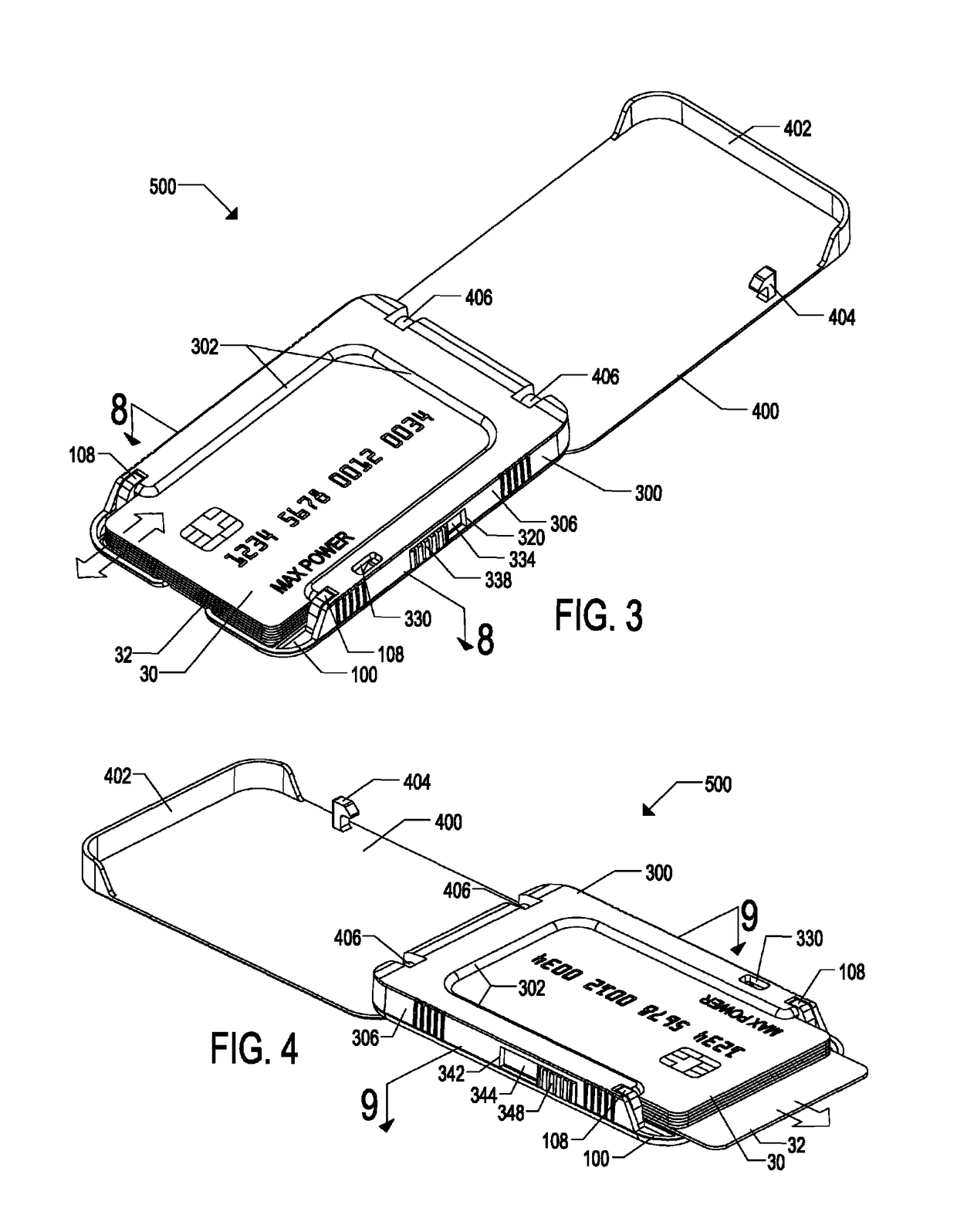

Electromagnetic shielding card case for contactless and chip and pin cards

InactiveUS9907375B1Easy to seeQuickly and easily inserted verticallyPursesMagnetic/electric field screeningEngineeringElectromagnetic shielding

An improved electromagnetic shielding card case comprising a front panel hingedly connected to a U-shaped member and a base member which sandwich an electromagnetic shielding member between them. A card slot is defined on its top by U-shaped member, its bottom by the shielding member, and its left, right and rear sides by a continuous inner wall extending downwards from the U-shaped member, whereby cards are able to be slidably inserted and removed at the front end of the case and shields cards inside the slot from RFID scanning. A resilient means frictionally engages the edges of cards in the slot so a user can shuffle through cards without any falling out, and allows the topmost card to be pushed forward and easily inserted into a chip and pin card reader. A soft rubber strap affixed to the back of the base member allows paper currency to be held securely.

Owner:KITCHEN MICHAEL WILLIAM

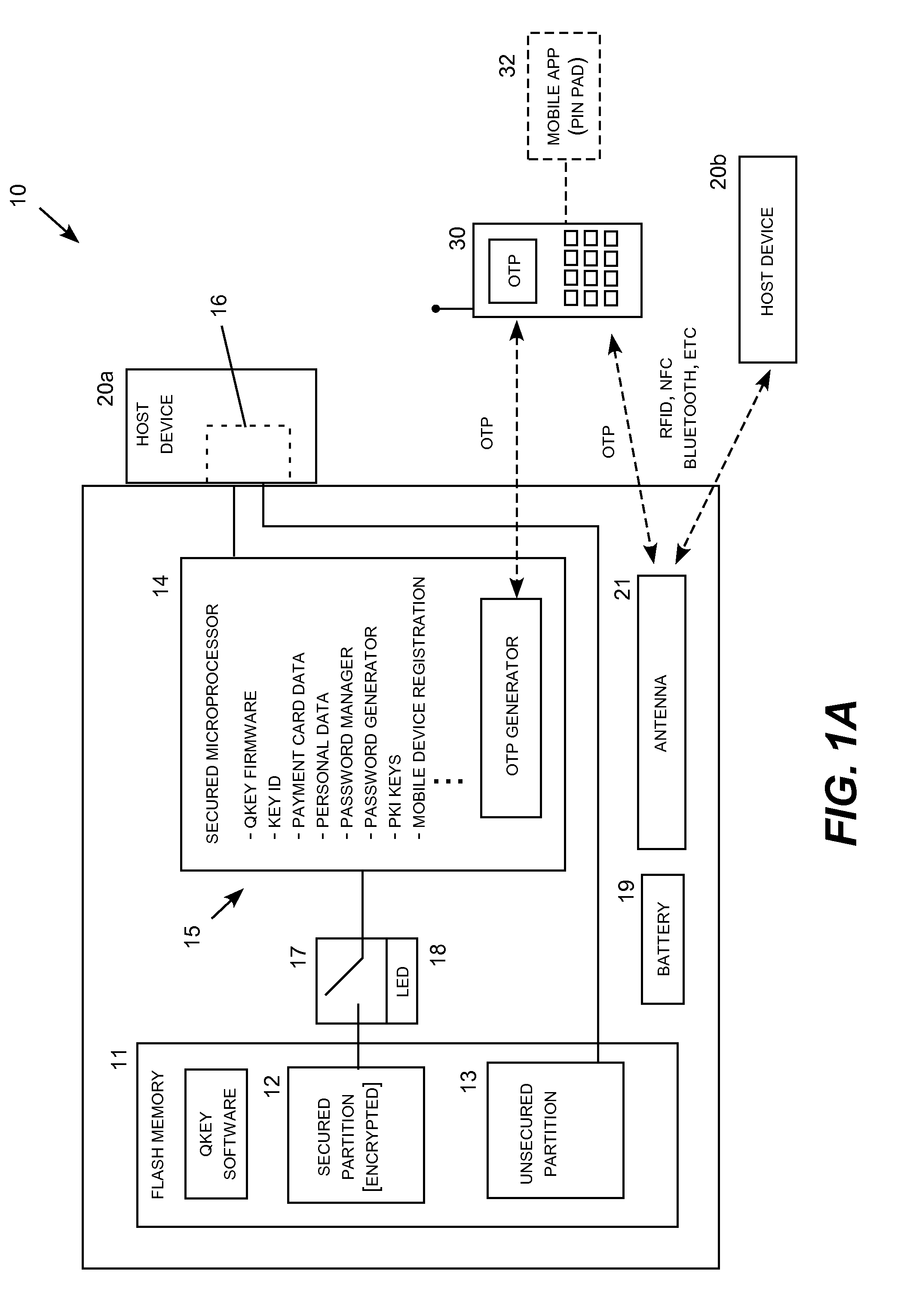

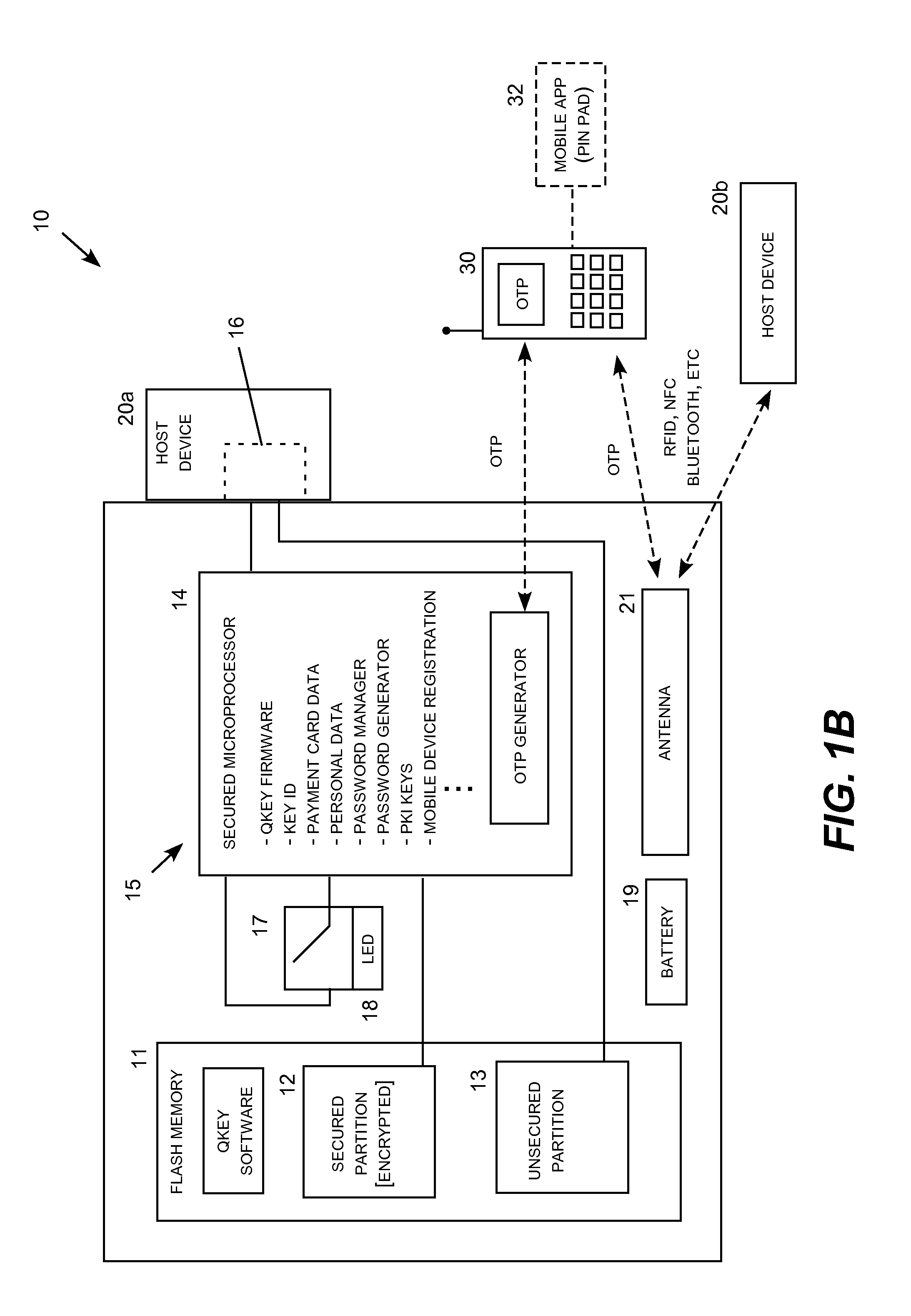

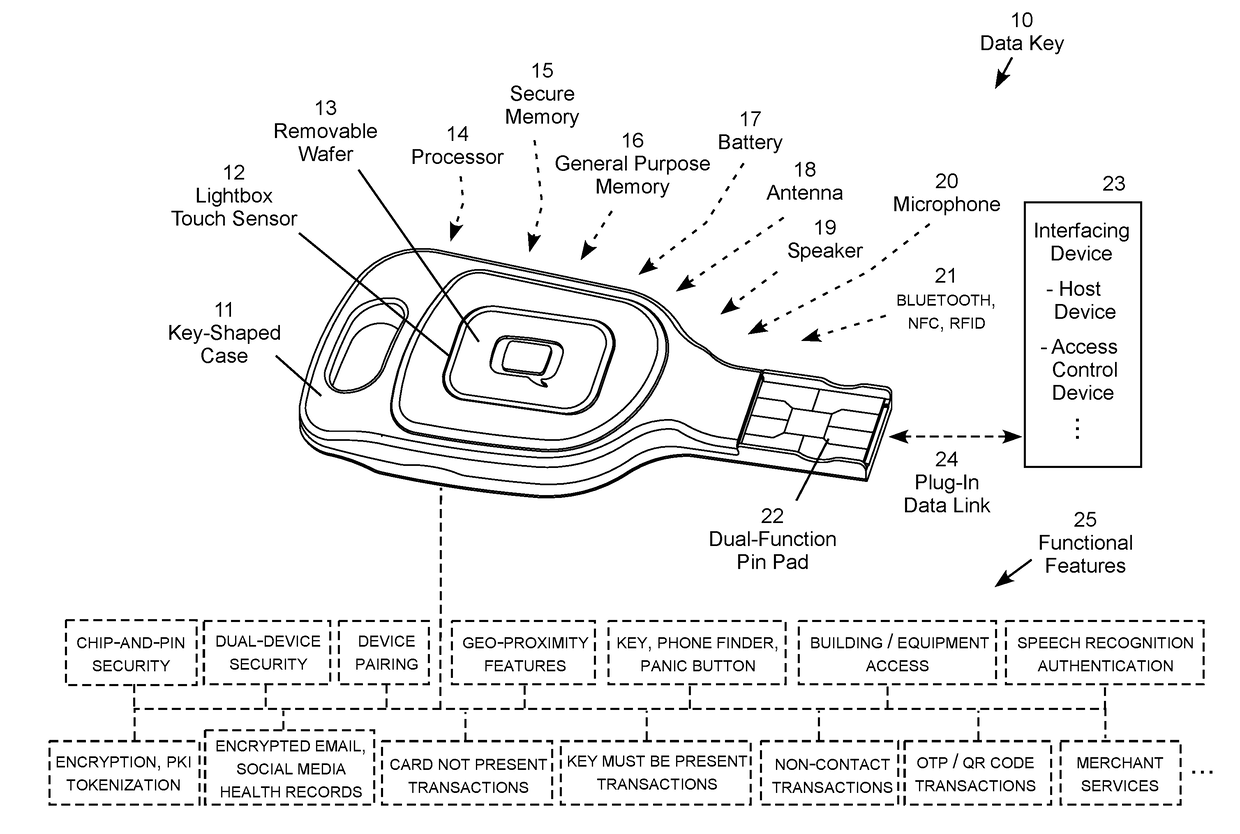

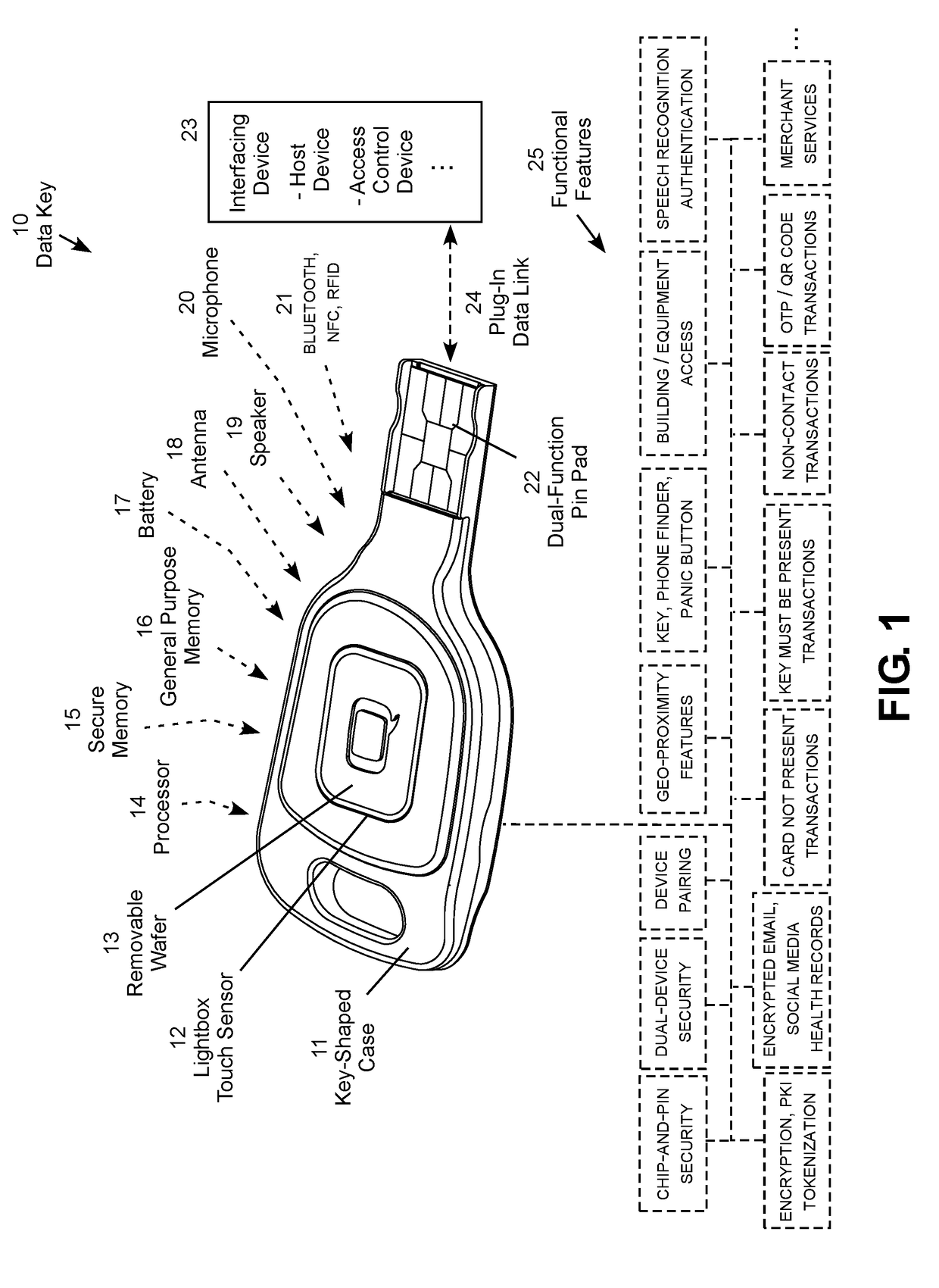

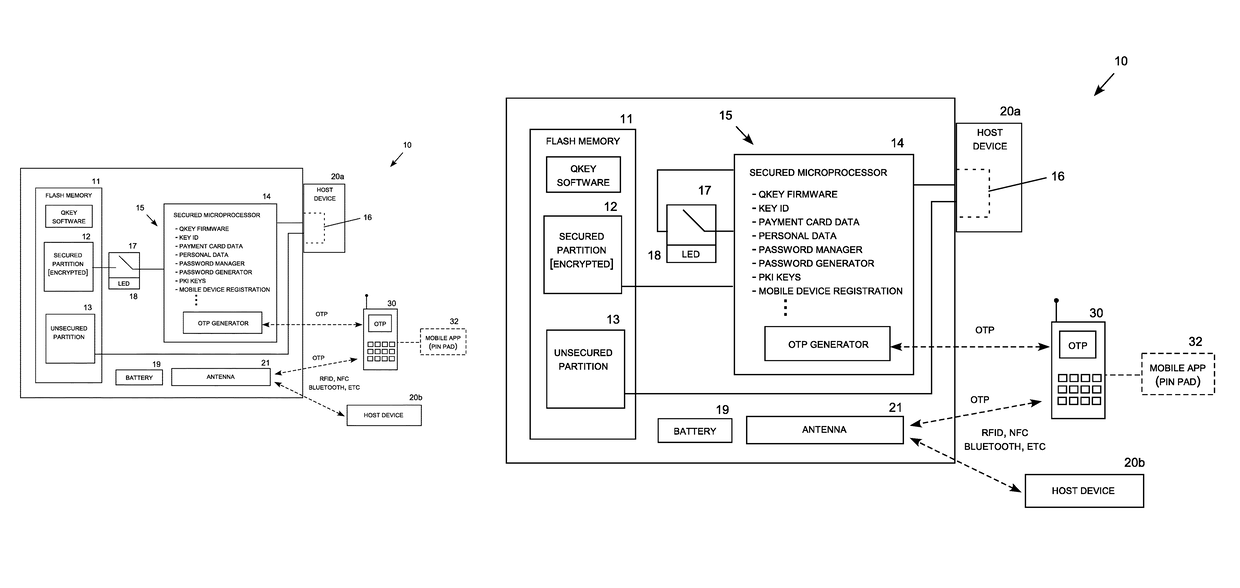

Multi-Function Data Key

A data key for secure financial and other types of data transactions with a key-shaped case, lightbox touch sensor carrying a removable wafer, processor, secure memory, general-purpose memory, battery, antenna, speaker, microphone, and a dual-purpose USB and chip pin pad. Bluetooth, NFC and / or RFID provides the ability to pair the data key through a wireless channel with another device, such as a smartphone, using a pairing button on the back of the data key. The data key provides chip-and-pin type security to online financial transactions. Dual-device security requires both the data key and another communication device registered to an authorized user to be present to activate the data key for secure operations. Device pairing enables geo-proximity features, such as dual-device security with a paired device, key finder, phone finder, and panic button. The data key may provide secure, remotely programmable security for building and equipment access.

Owner:UQONTROL

Logic drive based on multichip package comprising standard commodity FPGA IC chip with cryptography circuits

ActiveUS20210005592A1Lower the barrierReduce expensesSemiconductor/solid-state device detailsSolid-state devicesData setSemiconductor chip

A multichip package comprising: a first chip package comprising a first semiconductor IC chip, a first polymer layer in a space beyond and extending from a sidewall of the first semiconductor IC chip, a first through package via in the first polymer layer, and a first interconnection scheme under the first semiconductor IC chip, first polymer layer and first through package via, wherein the first semiconductor IC chip comprises a plurality of volatile memory cells configured to store first data associated with a plurality of resulting values for a look-up table (LUT) and a selection circuit configured to select, in accordance with a first input data set thereof, a data from a second input data set thereof as an output data for the logic operation; a first metal bump under the first chip package; and a non-volatile memory IC chip over the first chip package, wherein the non-volatile memory IC chip comprises a plurality of first non-volatile memory cells configured to store second data associated with the plurality of resulting values for the look-up table (LUT), wherein the first data are associated with the second data.

Owner:ICOMETRUE CO LTD

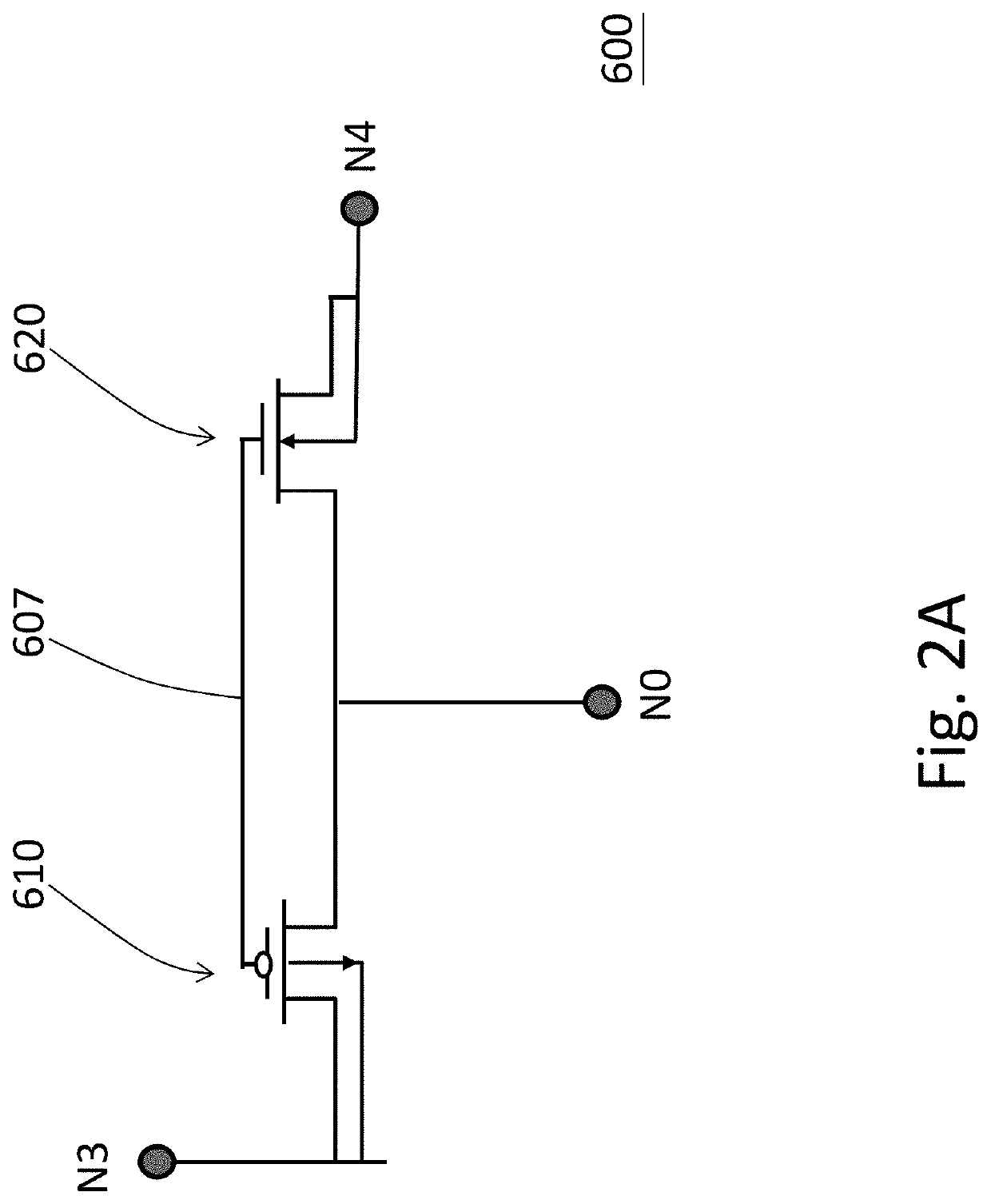

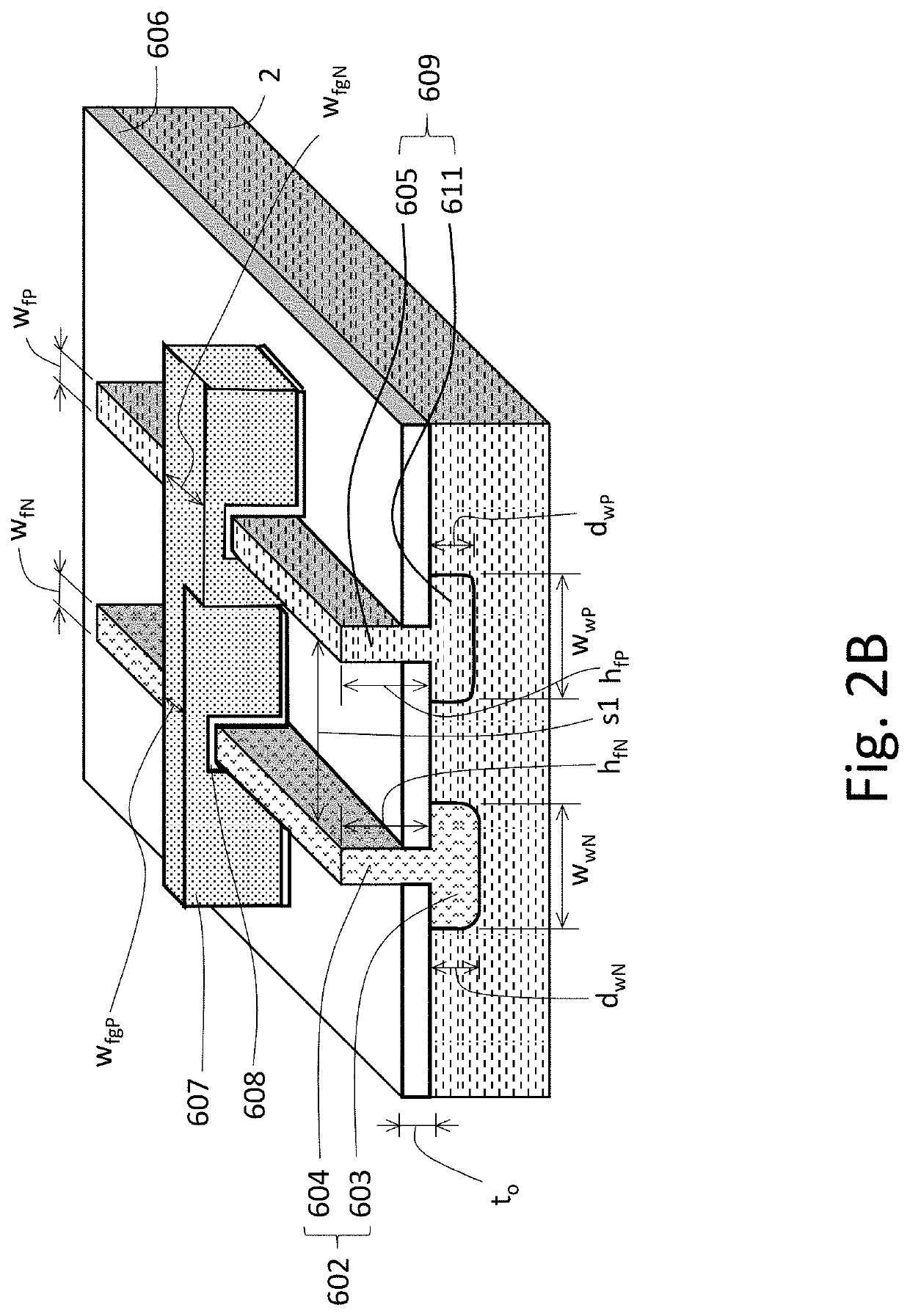

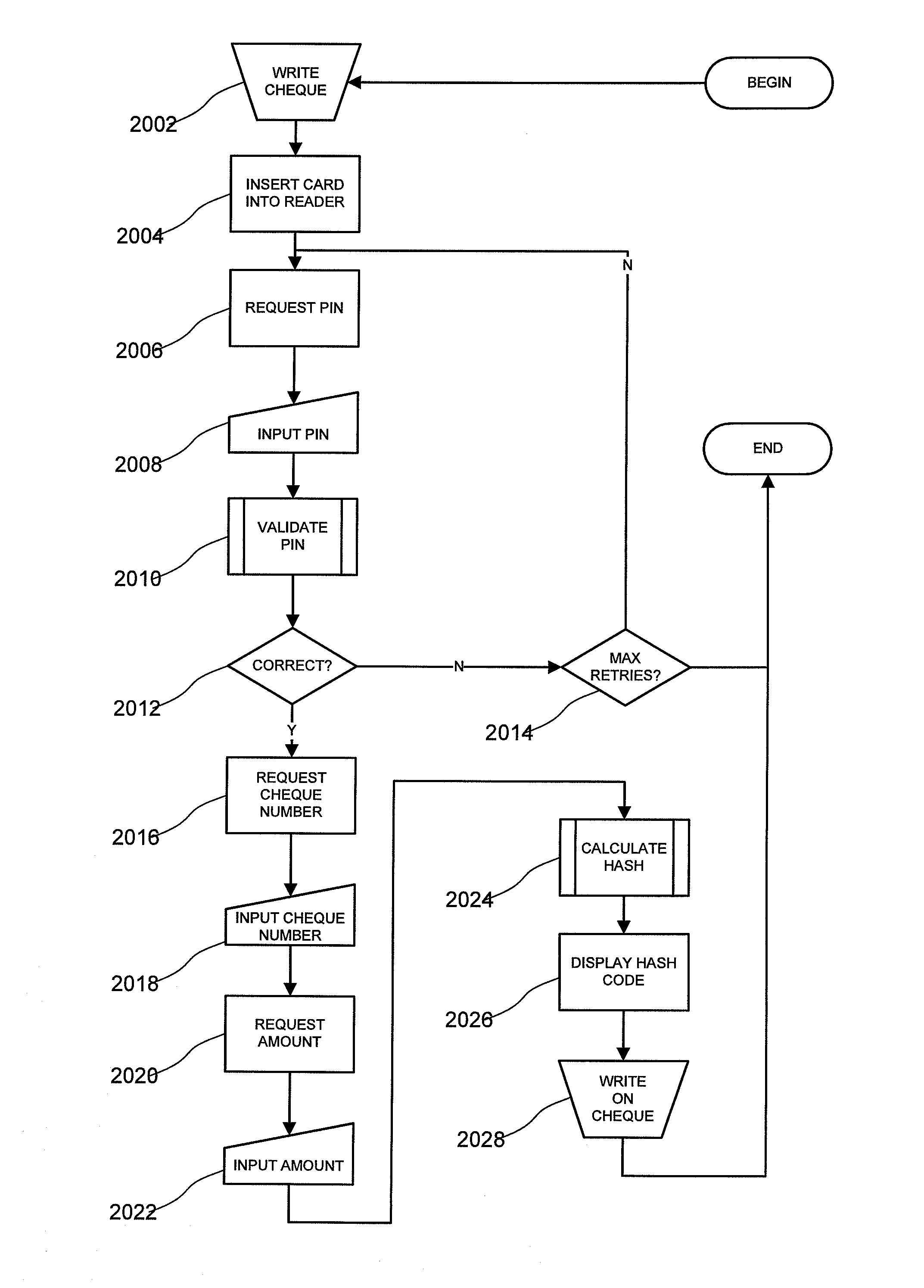

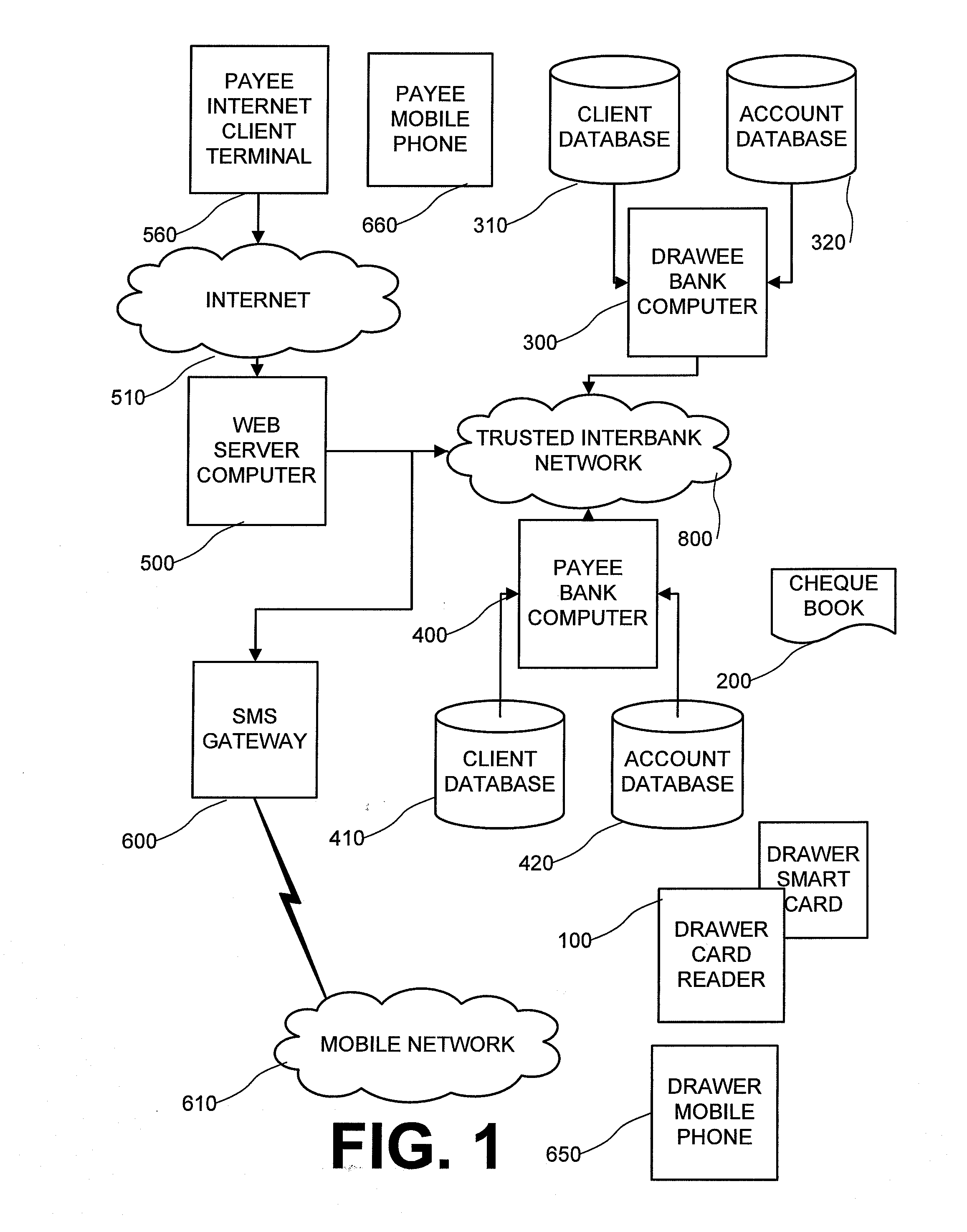

Computer system and method for initiating payments based on cheques

InactiveUS20130173476A1Rapid and secureComplete banking machinesFinanceThe InternetComputerized system

A system and method for initiating electronic payments based on paper cheques, including a paying party chip-and-PIN terminal arranged to input cleartext data including a cheque number and an amount from a cheque issued by a first bank, at which the paying party has an account, and generating from it encoded data using a key, for the user to write on the cheque; and a computer associated with the first bank, arranged to accept, from a paid party via the internet, data defining a second bank and an account at the second bank, associated with the paid party; accepting, from the paid party, the cleartext data and the encoded data from the cheque, and validating the cleartext data from the cheque using the encoded data and the key; and initiating an electronic funds transfer from the first bank to the second bank of the amount specified on the cheque.

Owner:BARCLAYS BANK

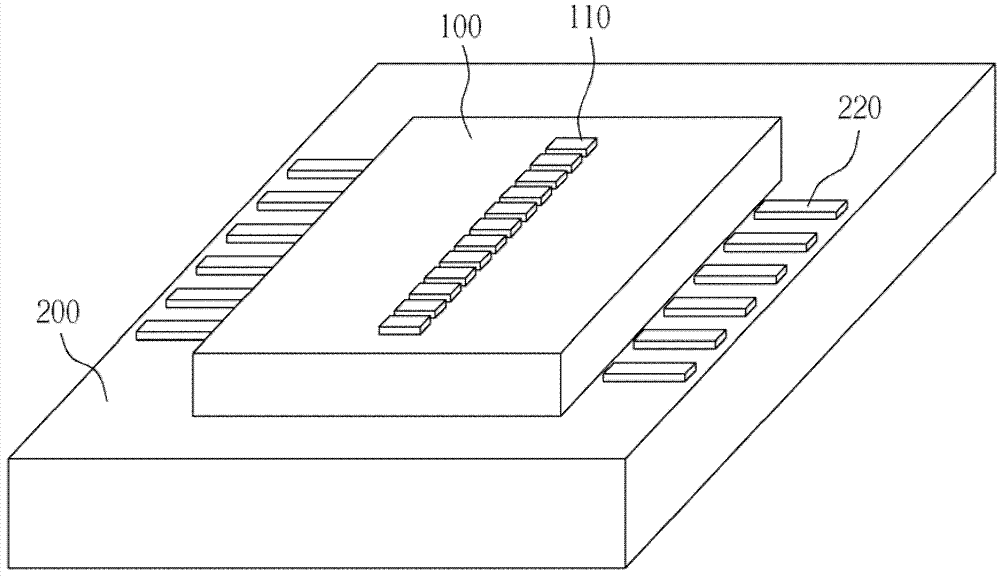

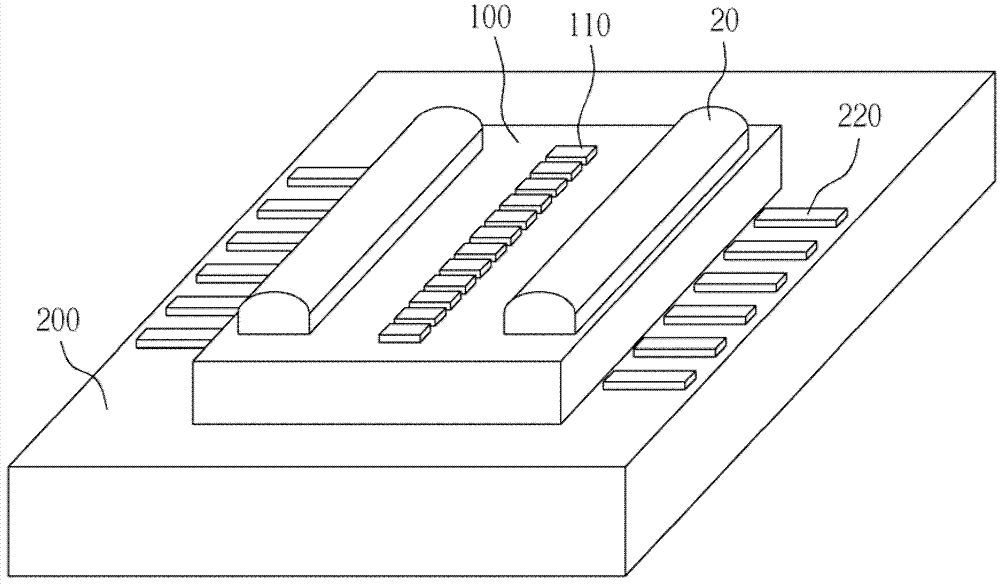

Parallel optical array assembly with standard MPO interface

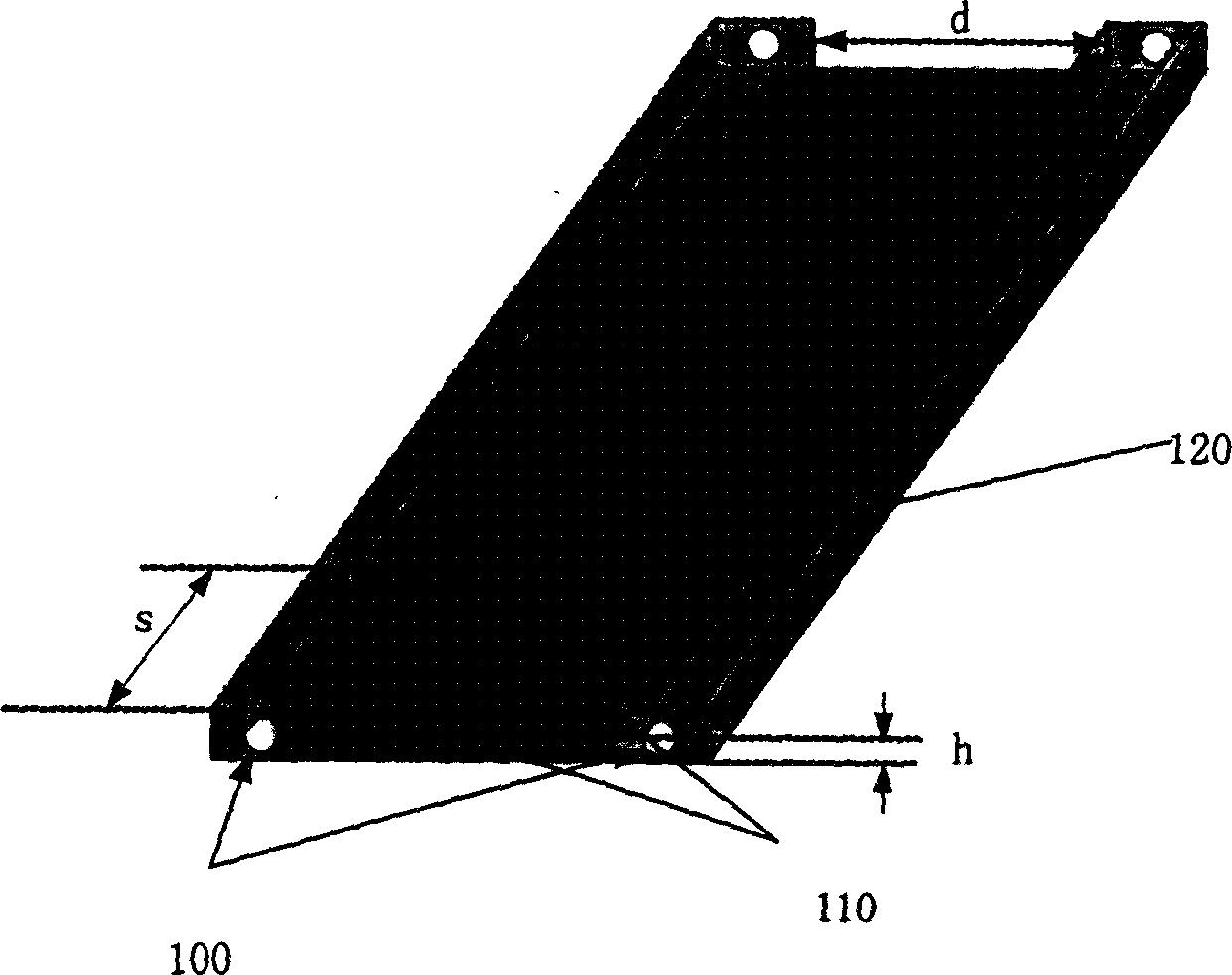

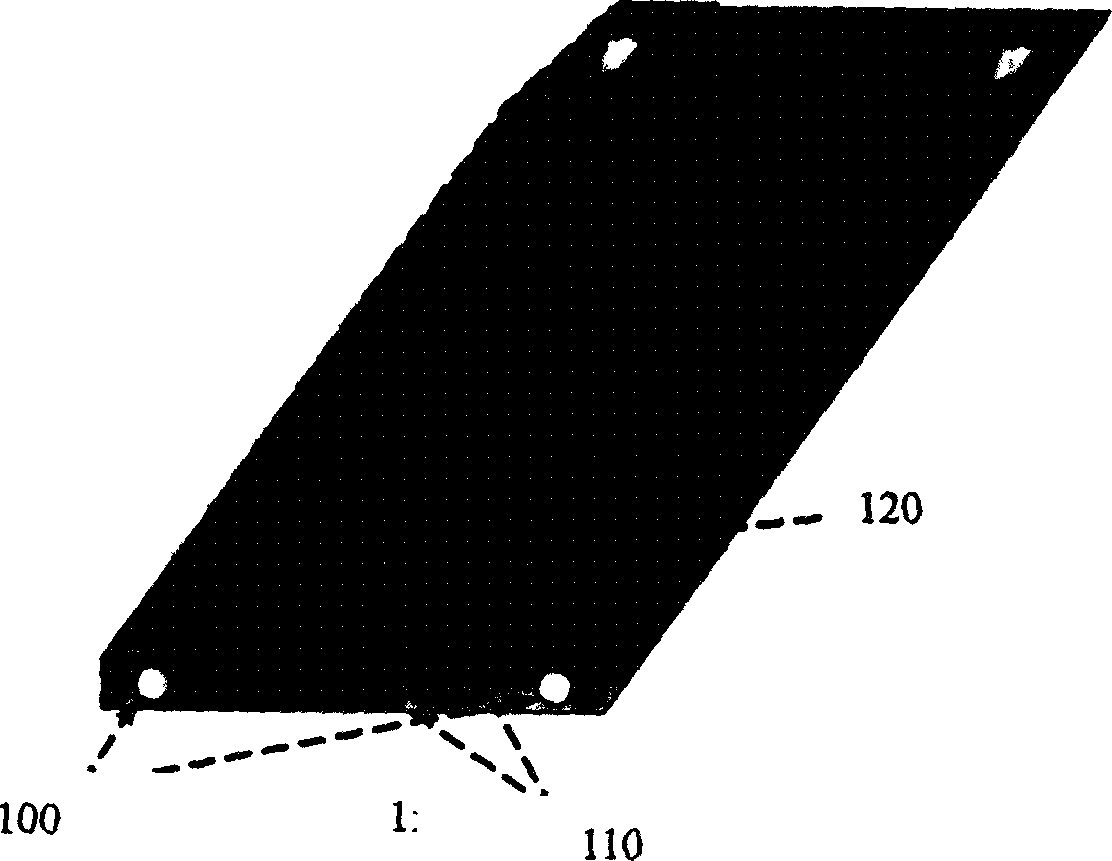

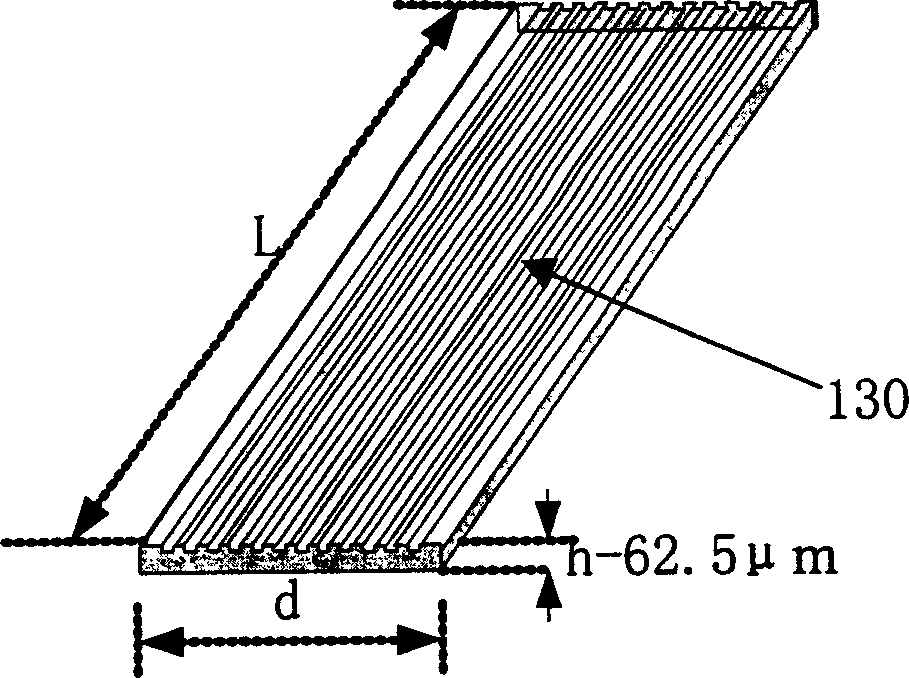

InactiveCN1564039AMaintain consistencyHigh positioning accuracyCoupling light guidesLaser arrayFiber array

The subassembly includes standard MPO connector, groove substrate, and top cover substrate and optical fiber. One end of the subassembly is traditional standard 1XN MPO connector in order to keep compatibility, and the other end is coupled to VCSEL chip of face emission laser array and light receiving PIN chip. Grooves are etched on a substrate, and lines on two sides of grooves are utilized to posit each optical fiber so as to fabricate fiber array module. Both VCSEL chip and PIN chip is made through photo etching providing high positioning accuracy, which guarantees coupling efficiency. Positioning accuracy for each optical fiber is 0.2-0.5 micro.

Owner:武汉海博光技术有限公司

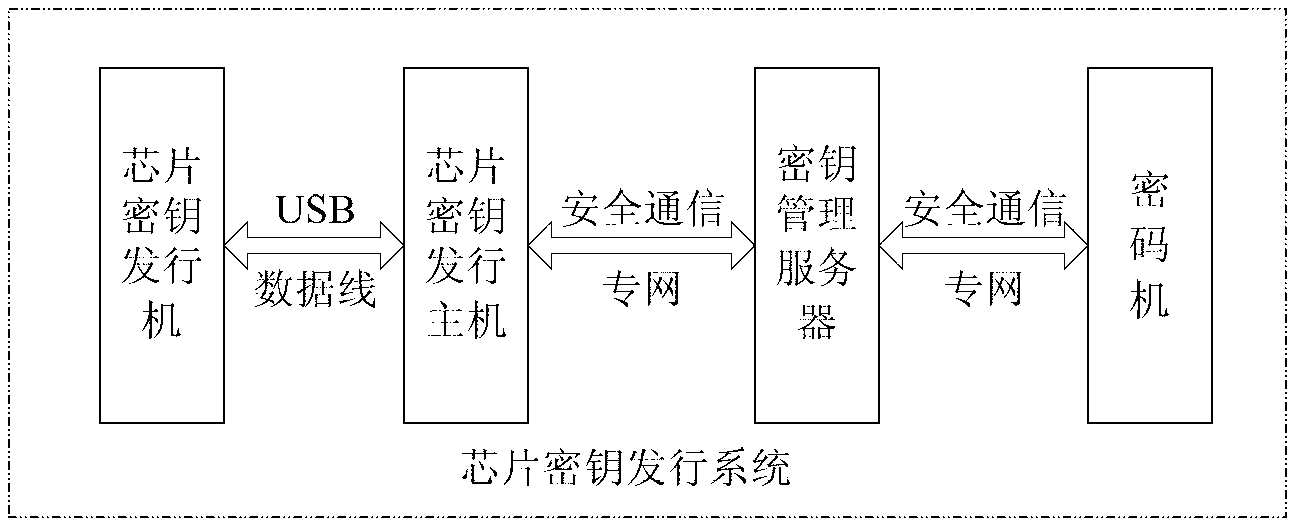

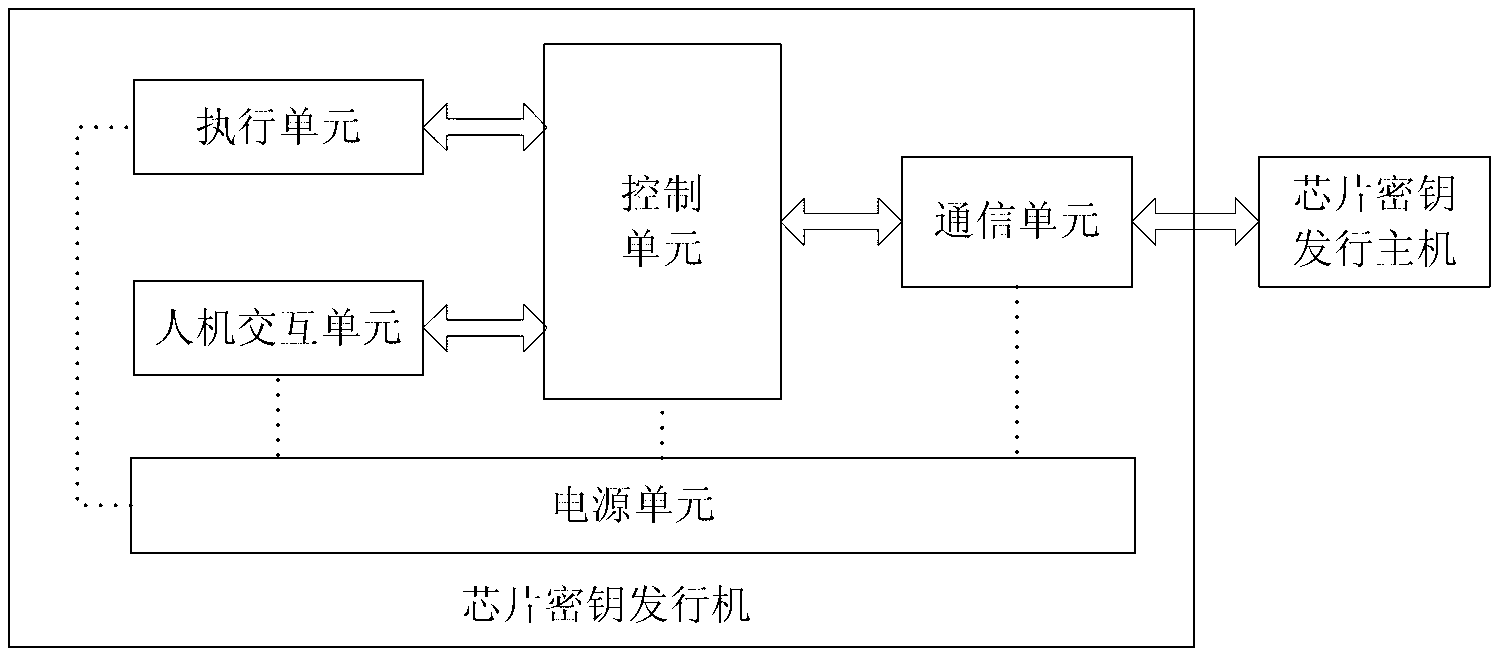

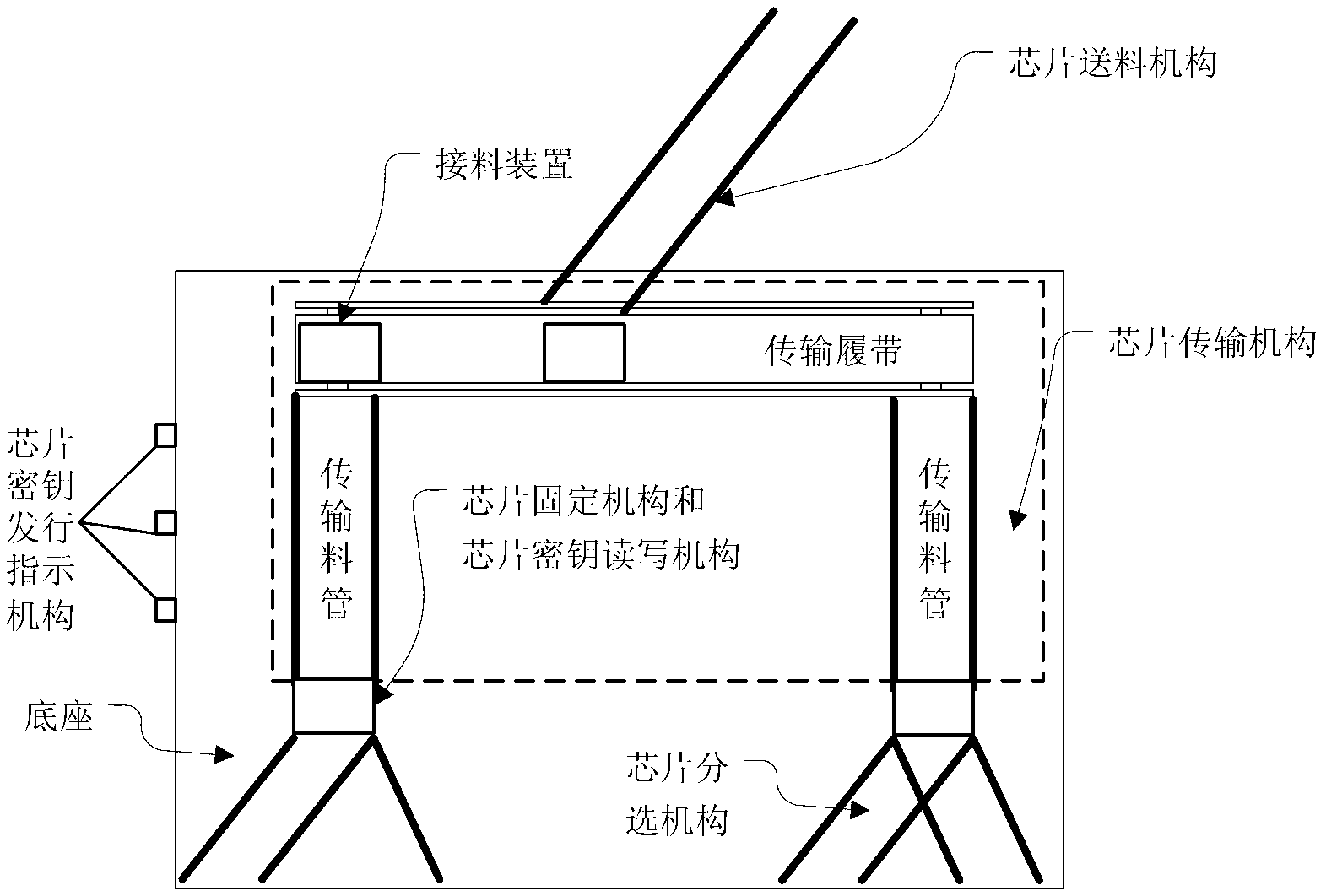

Secure chip key issuing system and secure chip key issuing method

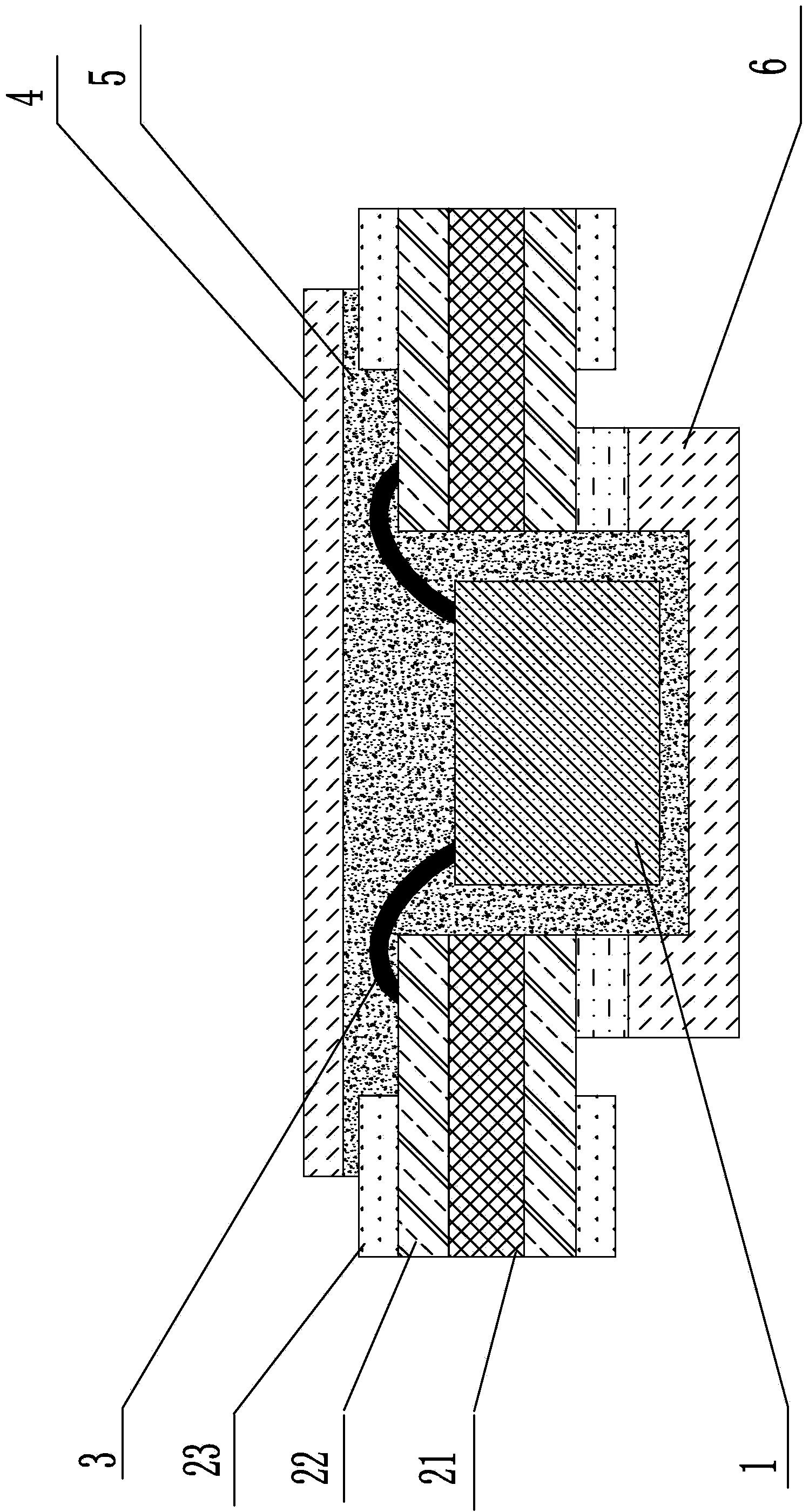

ActiveCN103178953ASimple structureEasy to operateKey distribution for secure communicationTelecommunications linkKey issues

The invention provides a secure chip key issuing system and a secure chip key issuing method. The system comprises a chip key issuer, a chip key issuing mainframe, a key management server and a cipher machine. A certain improvement is made to the chip key issuer and the cipher machine, namely, in the chip key issuer, a chip key reading-writing mechanism is directly fixed on the chip key issuer, and a chip fixing device is embedded in the chip reading-writing mechanism to enable the chip fixing device to be directly in physical connection with a pin of an issued chip so as to effectively prevent information monitoring and key interception of the chip key issuer from the outside. In the system and the method, a secure chip and the cipher machine of the chip key issuer are supportive of the symmetric encryption technology and the asymmetric encryption technology and have a data encryption and decryption operation function, an SSL (safety session link) is established between the chip key issuer and a server cipher machine by performing session key negotiation through the symmetric encryption technology and the asymmetric encryption technology, and safety of a chip key issuing system is effectively improved.

Owner:CHINA ELECTRIC POWER RES INST +1

Testing device and method for FPGA chip function

The invention belongs to the technical field of FPGA chip function testing, in particular to a testing device and a method for an FPGA chip function capable of reflecting whether the timing simulationresult of the FPGA function is consistent on the logic function of a real FPGA chip. The device comprises a host computer, a PXIe chassis, high-speed digital I / O cards, a PCB, and a to-be-tested FPGAchip. The host computer is connected to the PXIe chassis which has high-speed digital I / O cards inserted therein. The high-speed digital I / O cards communicate with each other through a PXIe bus and are connected to the PCB. A chip package socket is provided in the PCB. The to-be-tested FPGA chip is placed at the chip package socket. A pin parameter setting module used for setting the number of pins of the to-be-tested chip and pin attributes and a configuration module used for setting input and output voltage signals for each channel of the high-speed digital I / O cards are provided in the host computer. The testing device and the method for the FPGA chip function can realize the distributed transmission and acquisition of signals, test multiple chips at one time, and can reflect whether the simulation result of the FPGA function is consistent on the logic function of the real FPGA chip.

Owner:CHINA NUCLEAR CONTROL SYST ENG

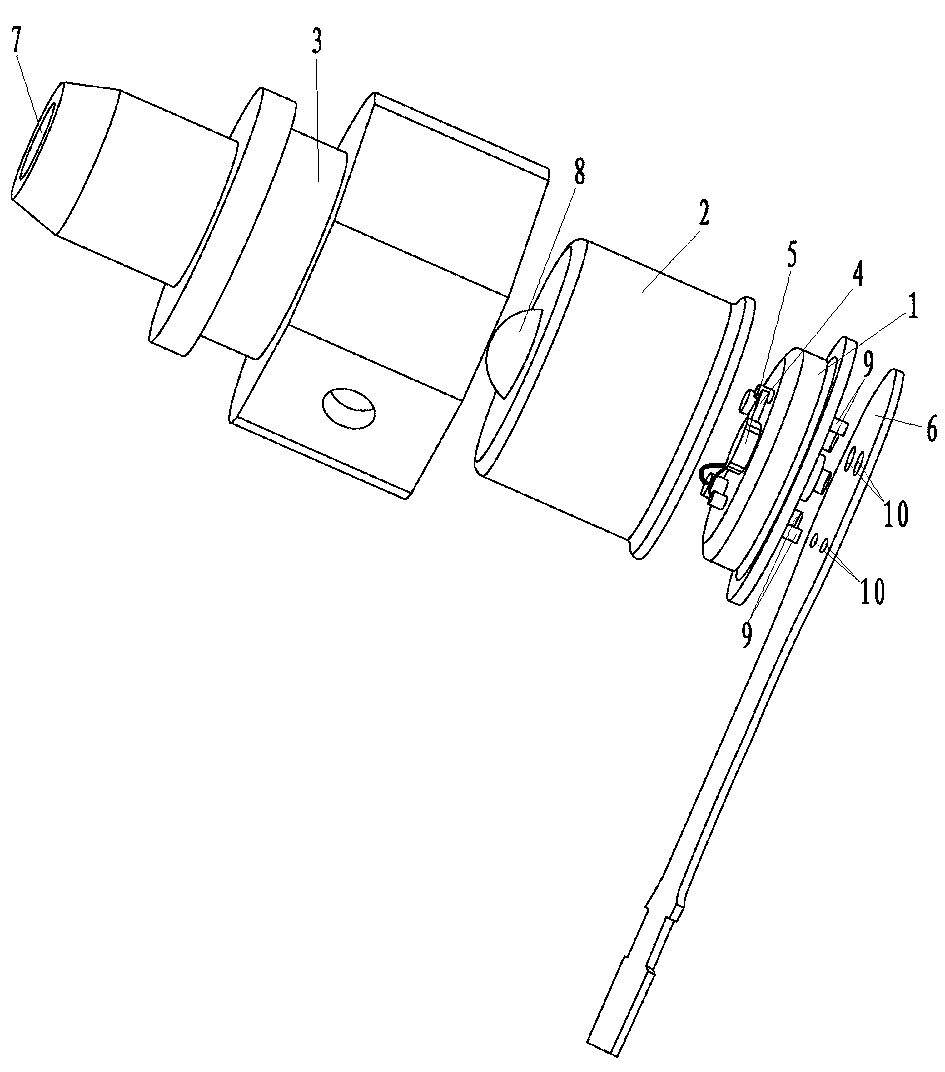

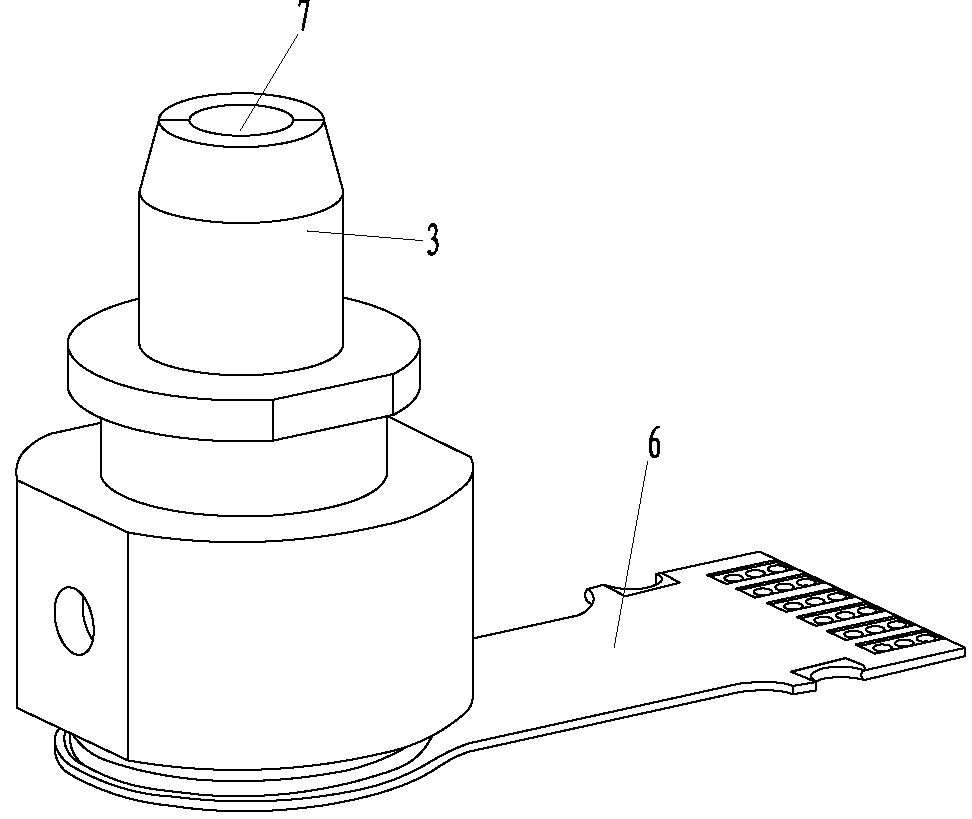

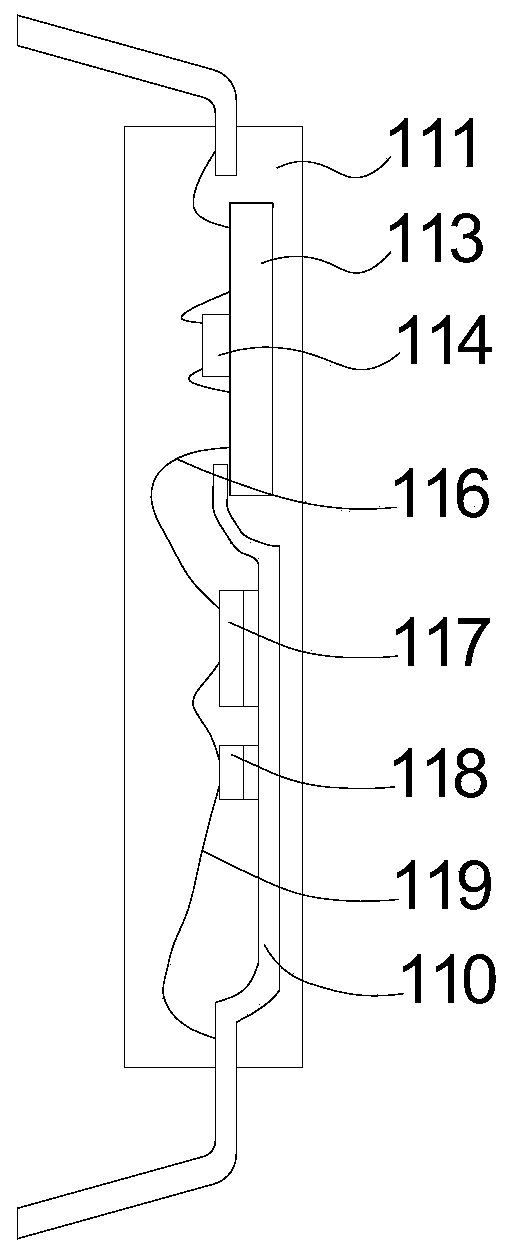

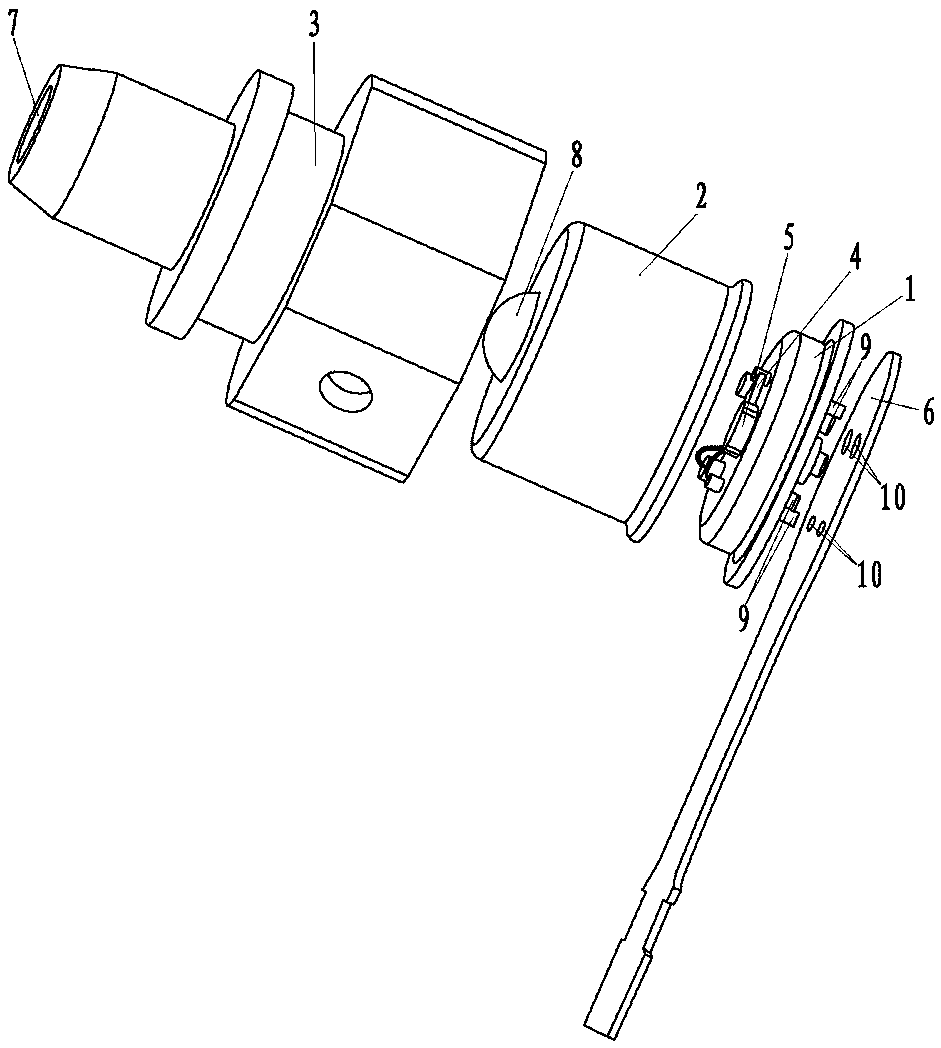

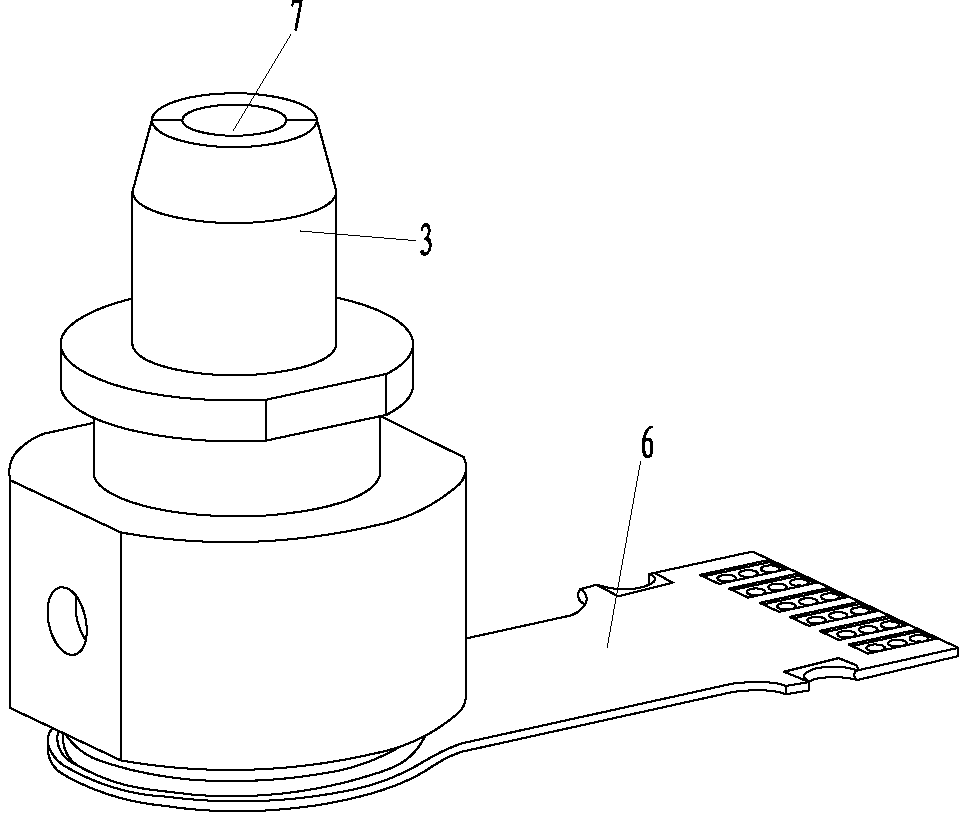

High-speed optical receiver module of integrated limiting amplifier and preparation method for high-speed optical receiver module

ActiveCN103278891AReduce volumeReduce weightCoupling light guidesAudio power amplifierFlexible circuits

The invention discloses a high-speed optical receiver module of an integrated limiting amplifier and a preparation method for the high-speed optical receiver module. The optical receiver module is formed by connecting a tube socket, a tube cap, an adapter, a photoelectric receiver, a monolithic integration high-speed limiting amplifier chip and a flexible printed circuit board, wherein the photoelectric receiver, the monolithic integration high-speed limiting amplifier chip and the flexible printed circuit board are connected with each other. The preparation method for the high-speed optical receiver module comprises the following steps: firstly mounting the photoelectric receiver and the monolithic integration high-speed limiting amplifier chip onto the tube socket; then, welding the photoelectric receiver and the input end of the monolithic integration high-speed limiting amplifier chip together by using a gold wire bonder, and meanwhile, welding a bonding pad of the monolithic integration high-speed limiting amplifier chip and pins of the tube socket together; then, sealing the tube cap by adopting a cap sealing machine; subsequently, performing light path alignment on the tube cap, and then, fixing the adapter to the tube cap; and finally, enabling the flexible printed circuit board to sheathe the roots of the pins of the socket and welding to fix the flexible printed circuit board. According to the high-speed optical receiver module of the integrated limiting amplifier disclosed by the invention, the space of the rear end module design is saved, a packaging design can be flexibly realized, and meanwhile, the power consumption and the cost of a whole module application system are also reduced.

Owner:WUHAN TELECOMM DEVICES

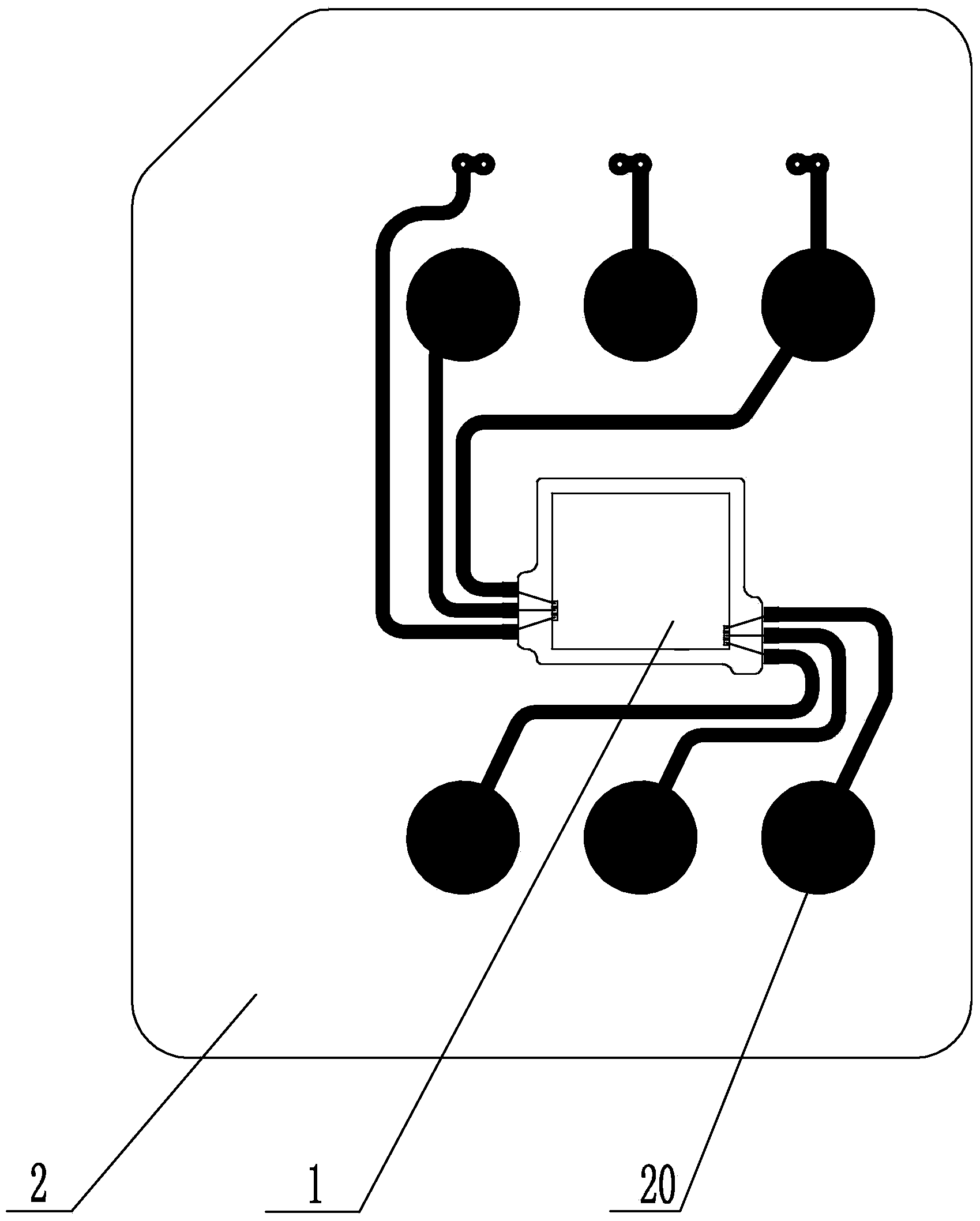

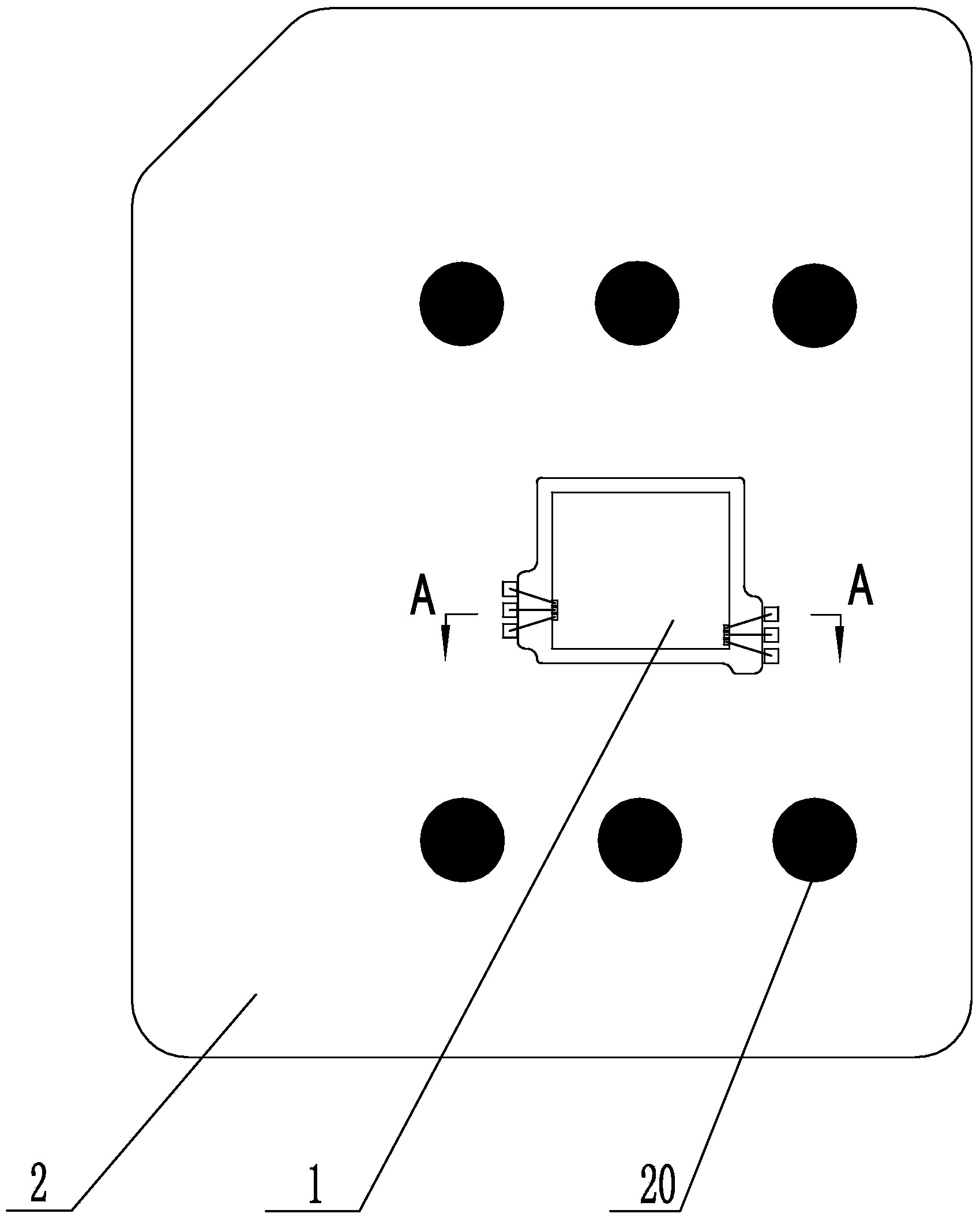

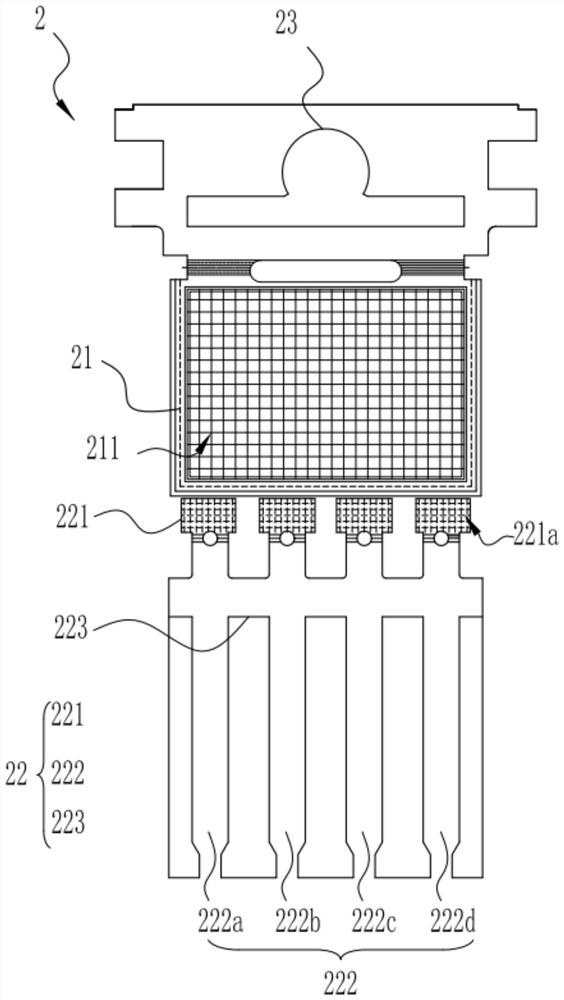

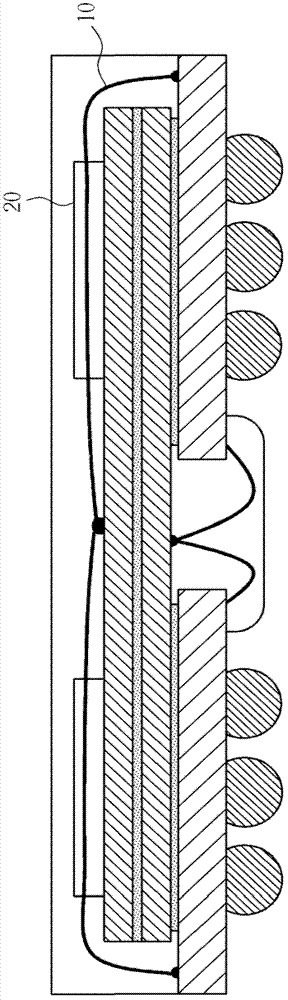

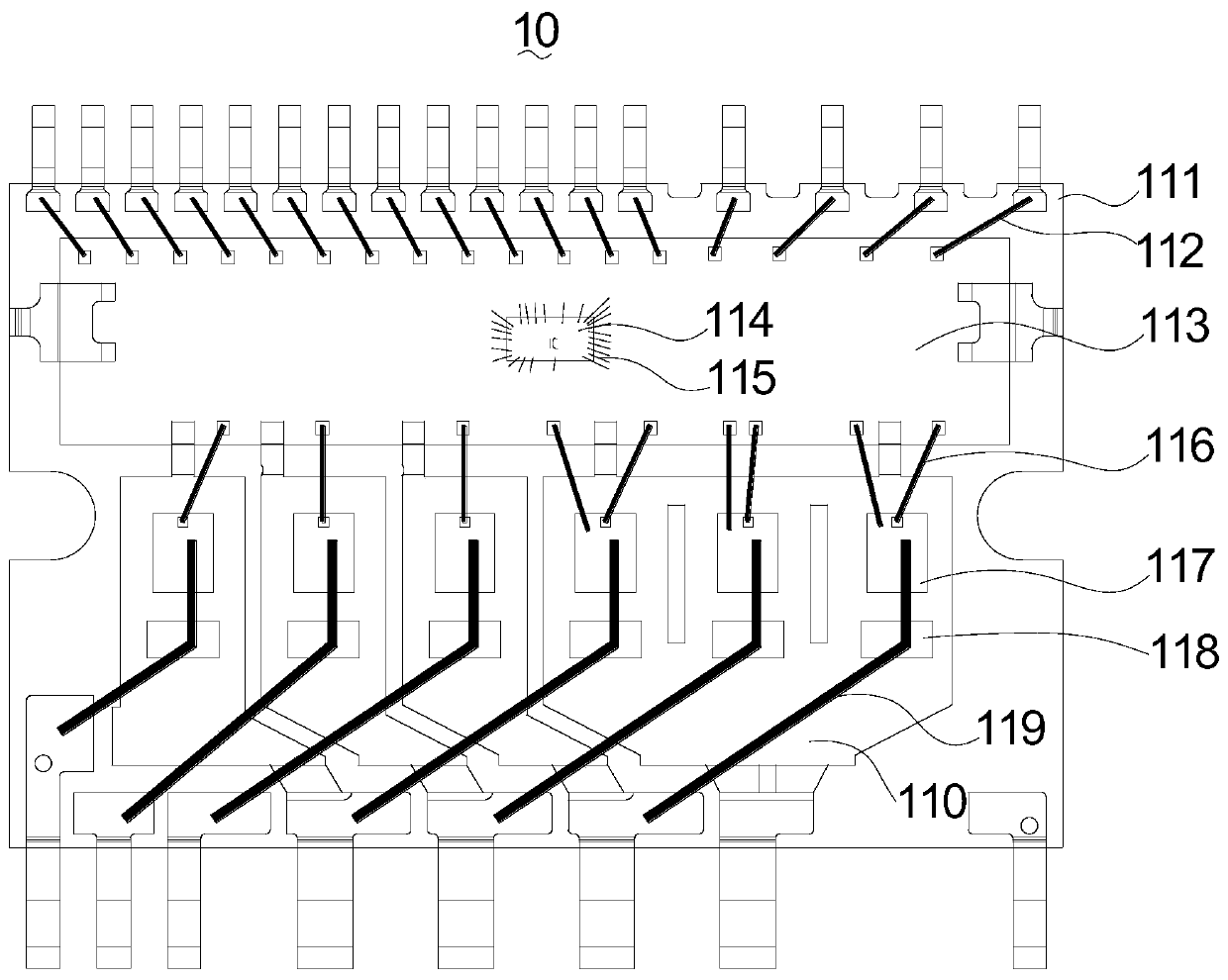

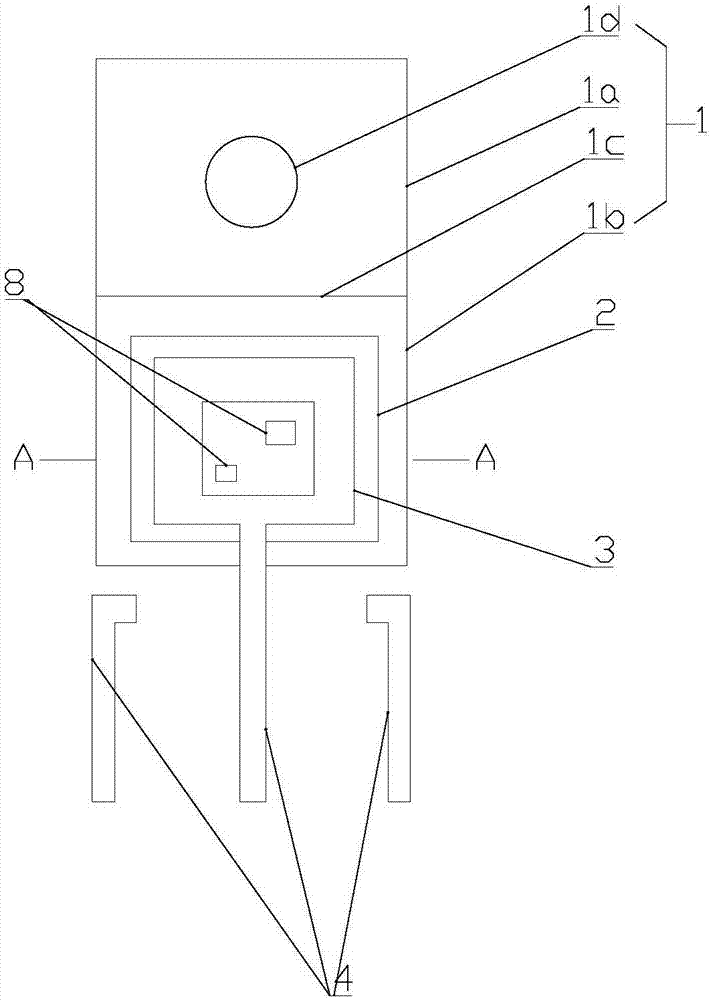

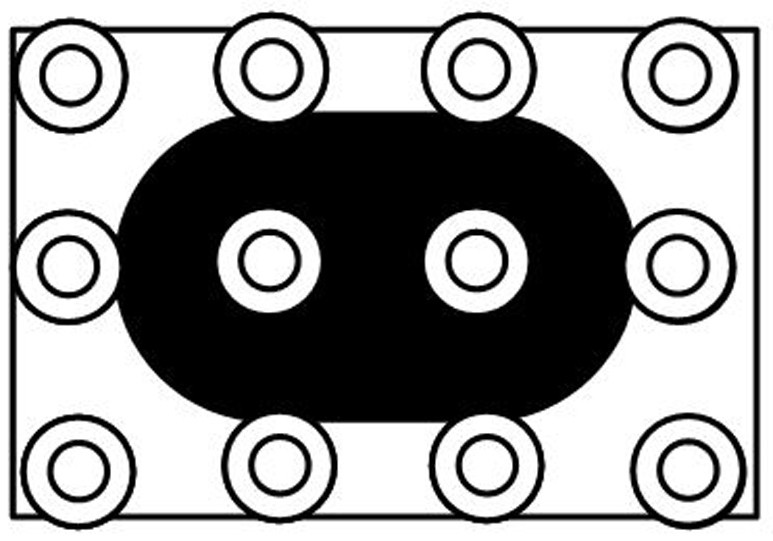

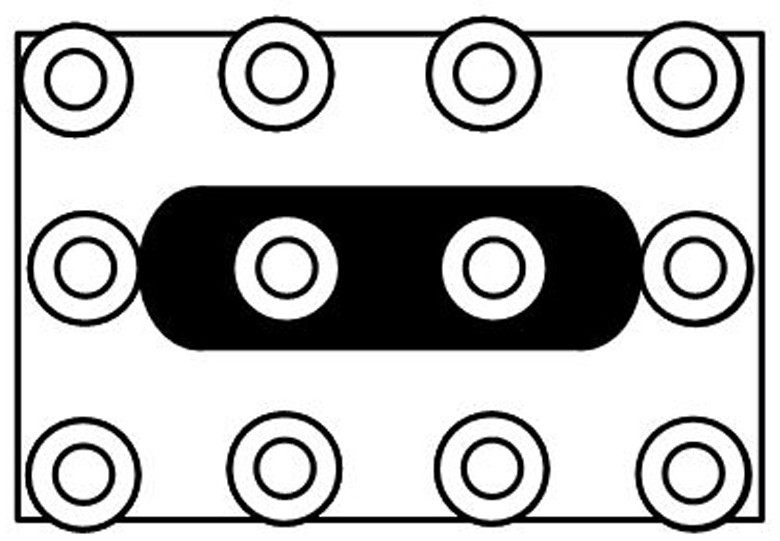

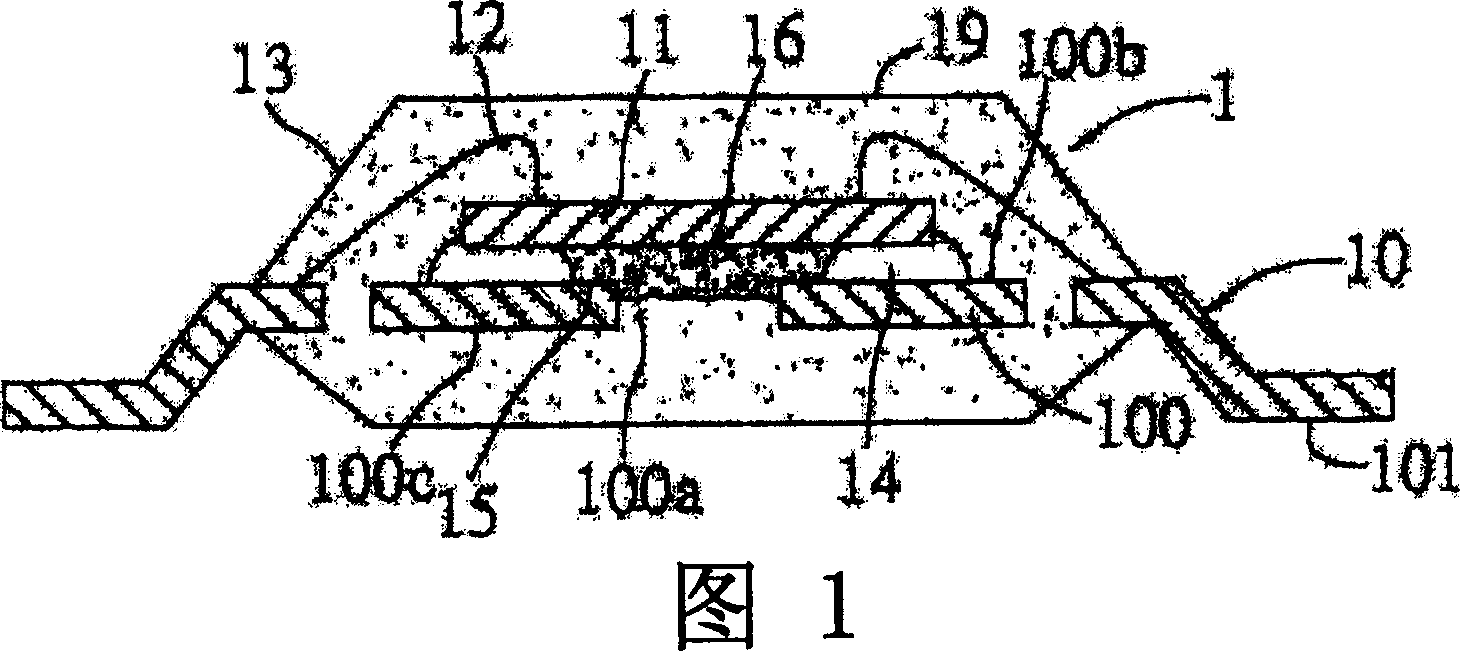

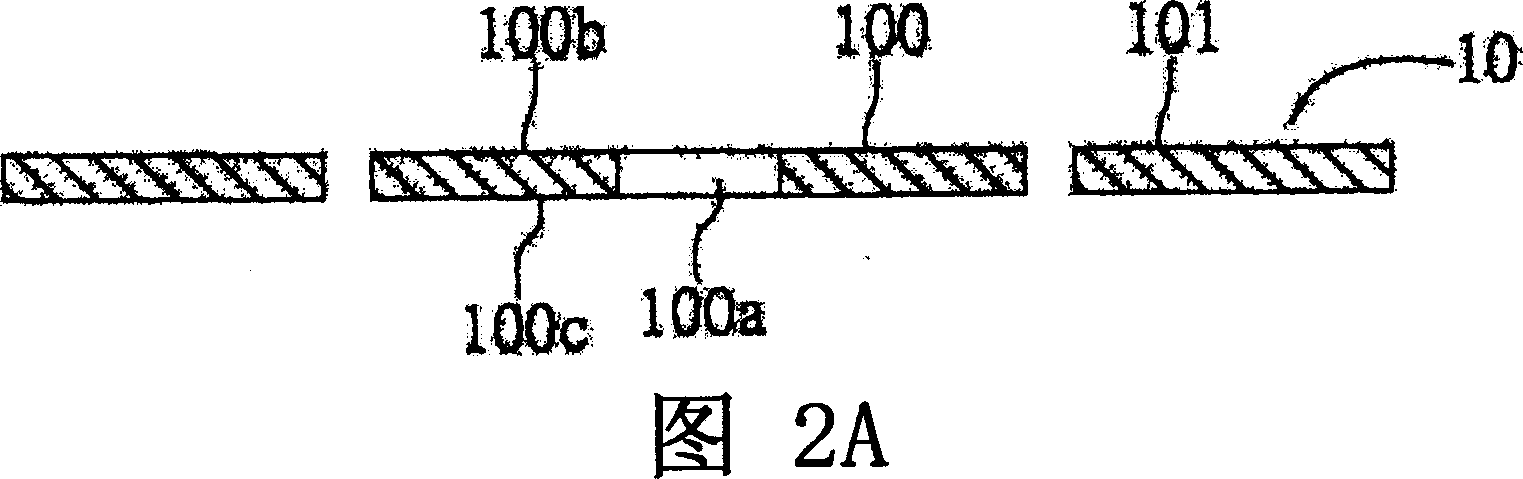

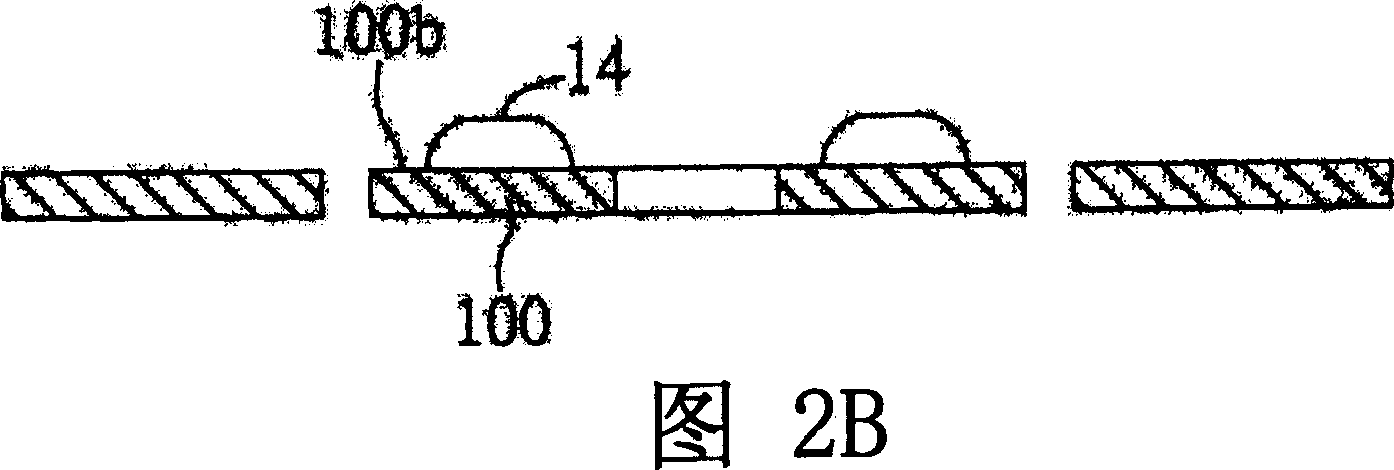

Semiconductor chip packaging structure and packaging method

InactiveCN103531549AReduce thicknessThe package structure is stable and reliableSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipChip and PIN

The invention discloses a semiconductor chip packaging structure and a packaging method. A through hole matched with a chip in a circuit board is a mounting hole; a lower protective layer seals the bottom of the mounting hole, and is fixedly connected with the circuit board; the lower protective layer in the mounting hole is a chip loading platform; the chip is wholly or partially embedded into the mounting hole; the surface of the chip is flush with or lower than the upper surface of the circuit board; the bottom surface of the chip is bonded with the chip loading platform; leads are connected with connection points of the chip and pins of the circuit board; and solid sealing glue is filled between a hole wall of the mounting hole of the circuit board and the chip, and coats and seals the upper surface of the chip and the leads. The packaging method comprises the steps that the through hole of the circuit board is processed; the lower protective layer seals the through hole of the circuit board; the surface of the lower protective layer is smooth, or a raised groove matched with the chip is formed in the surface of the lower protective layer; the bottom surface of the chip is bonded with the chip loading platform; the connection points of the chip are linked with the leads of the pins of the circuit board; and the solid sealing glue fills and coats the chip and the leads. According to the packaging structure and the packaging method, the thickness of the circuit board is utilized effectively; the thickness of the packaging structure is reduced significantly; the solid sealing glue protects the leads and the connection points; and a product is stable and reliable.

Owner:桂林微网半导体有限责任公司

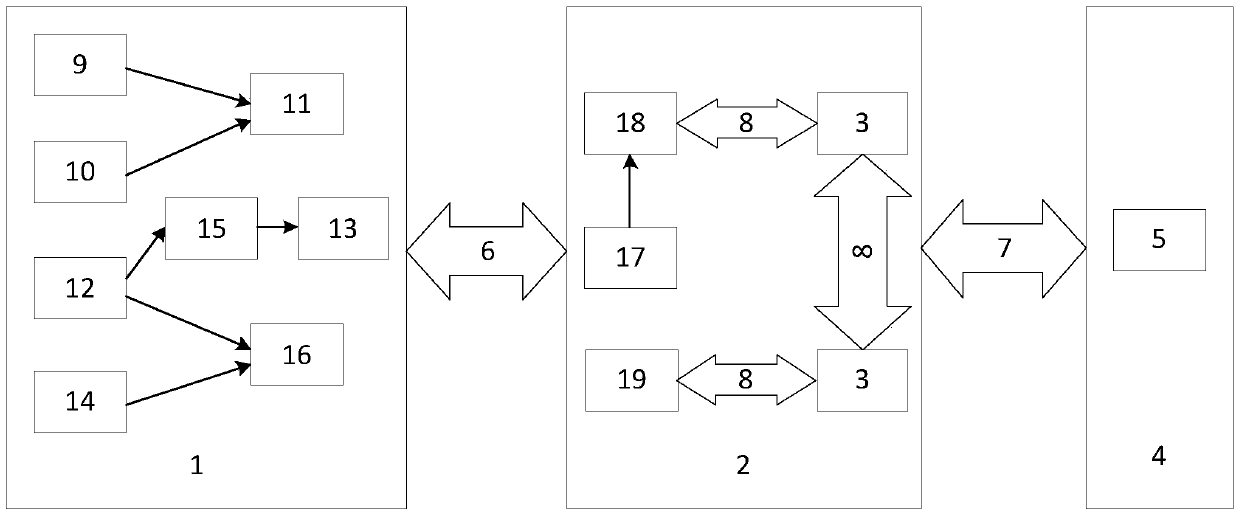

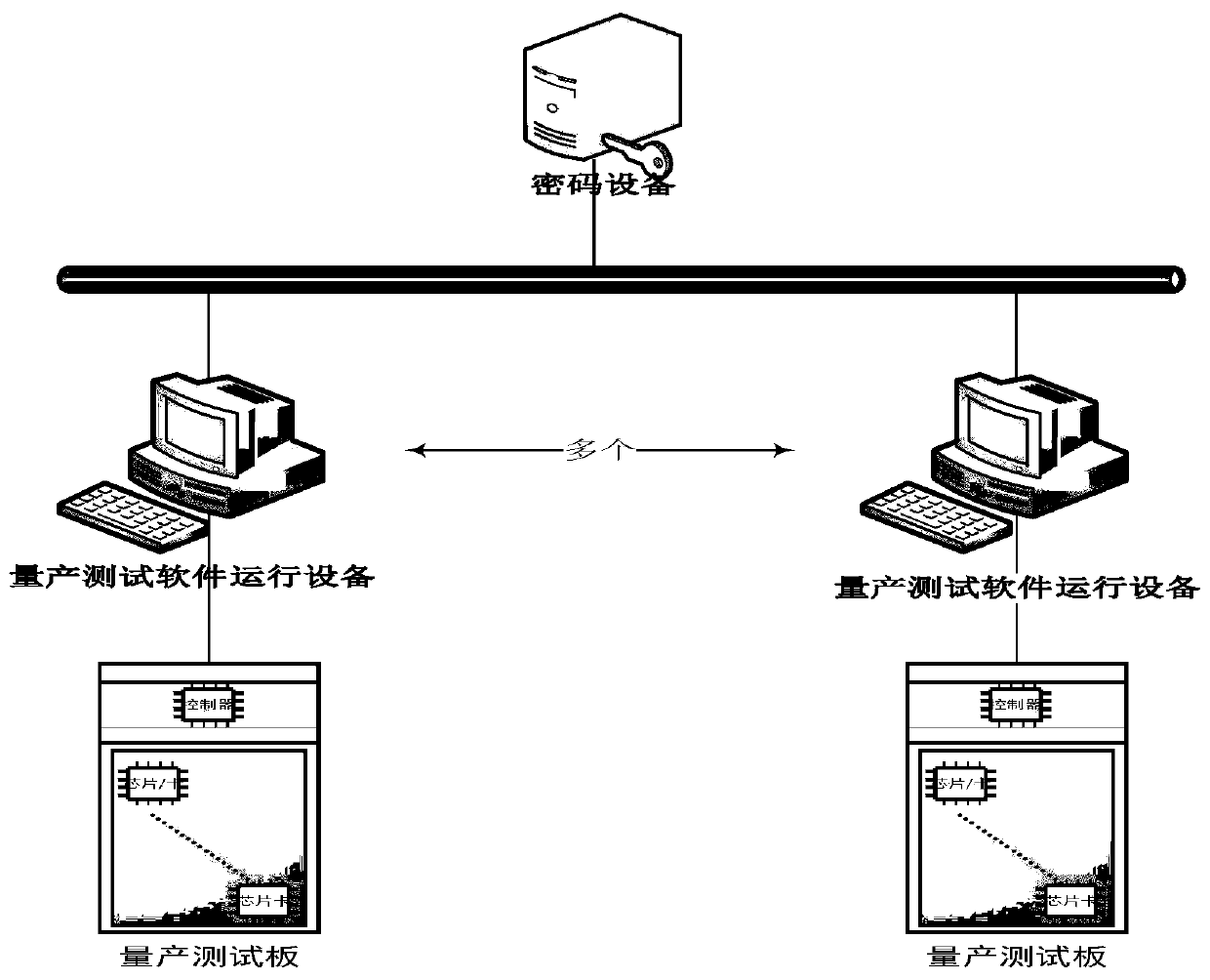

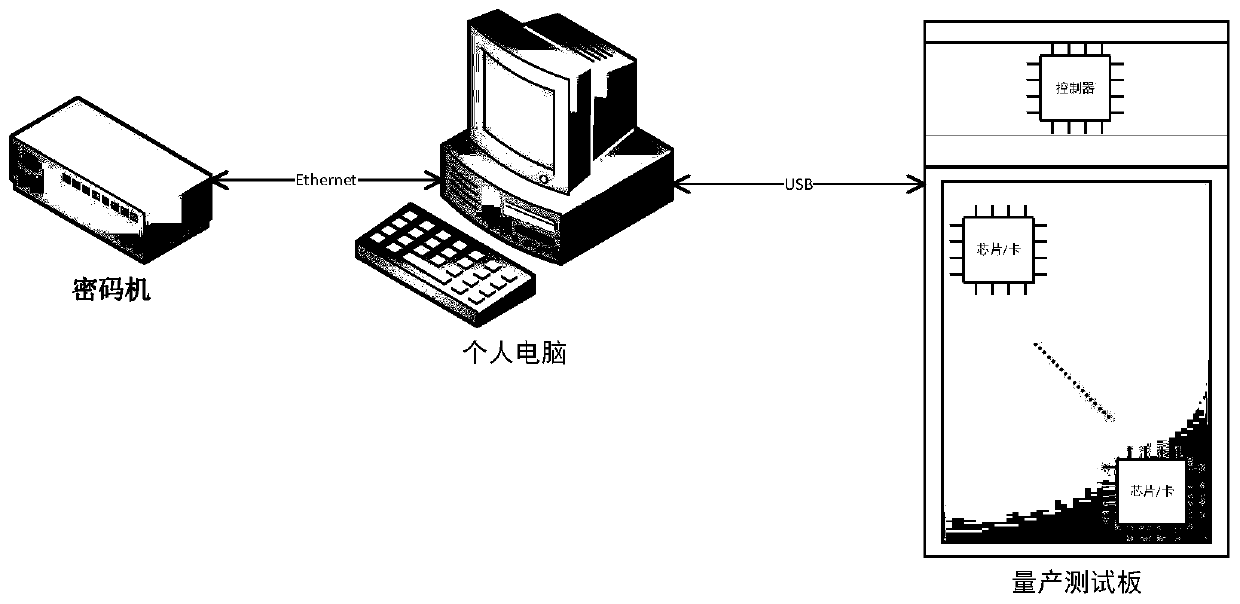

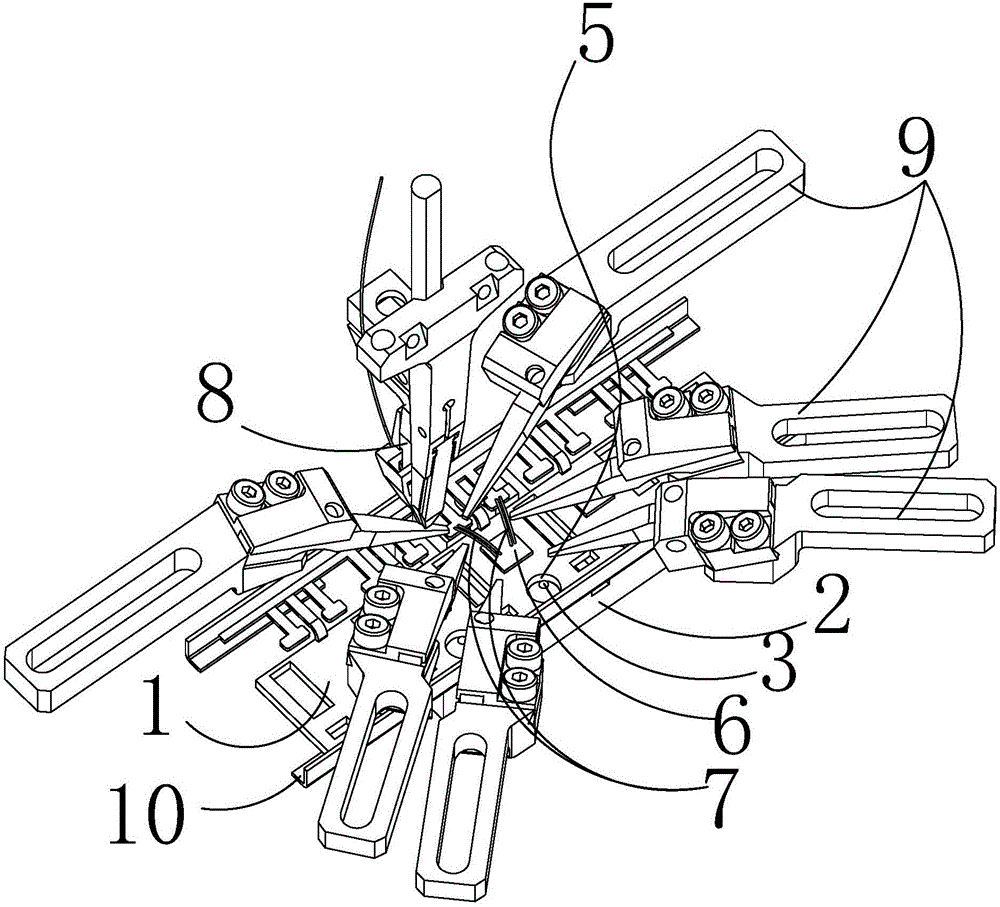

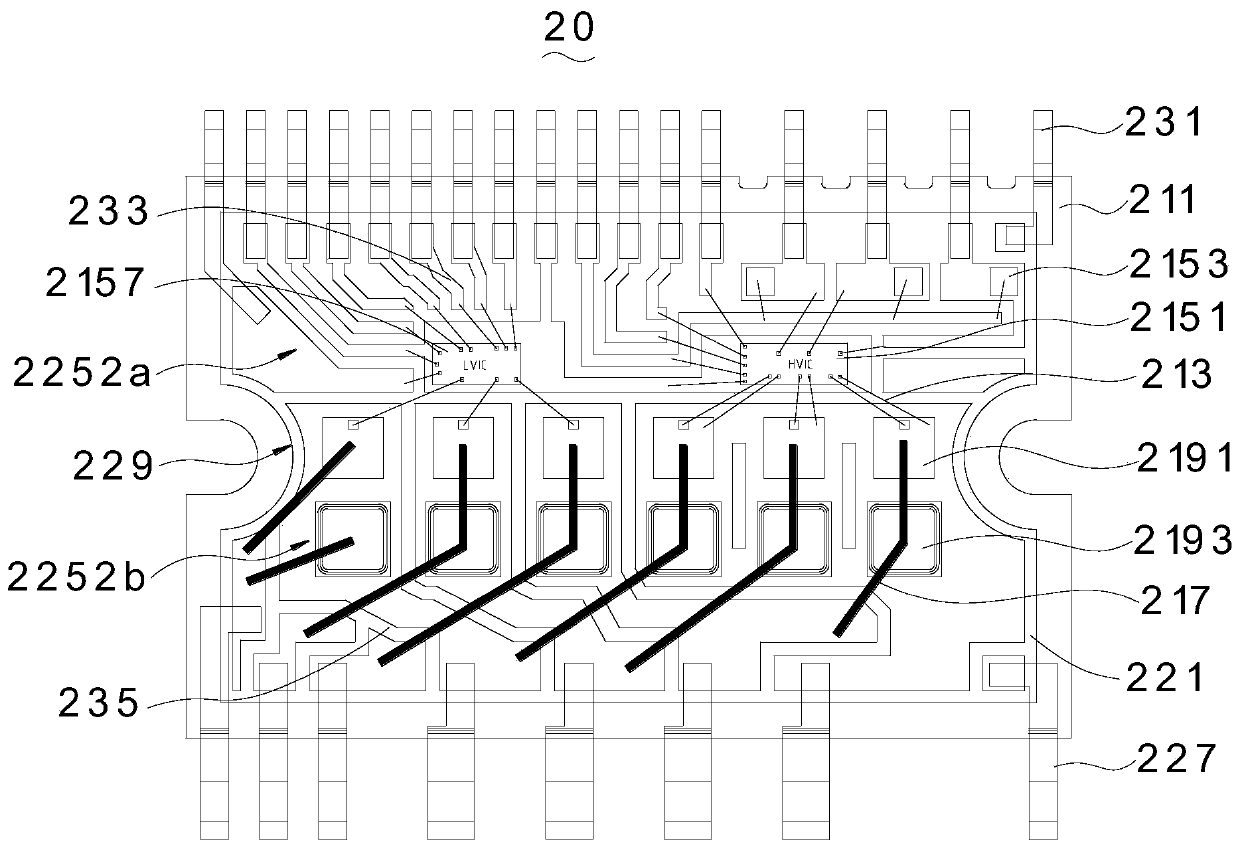

Security chip or cipher card program downloading, testing and key injection system

ActiveCN110874296ASimple processIncrease productivityFaulty hardware testing methodsDigital data authenticationPasswordDaughterboard

The invention discloses a security chip or cipher card program downloading, testing and key injection system. The system comprises key generation equipment, a plurality of mass production test software operation equipment connected with the key generation equipment, and a mass production test board connected with the mass production test software operation equipment. The mass production test board comprises a main board and a daughter board which are connected with each other. The main board is used for placing a main controller, and the daughter board is used for placing a plurality of security chips or password cards; the key generation equipment is used for generating a key and a certificate; and the main controller is used for realizing interaction between the mass production test board and the mass production test software, so that program downloading, testing and key injection are carried out on the security chip or the password card placed on the mass production test board through the mass production test software. According to the invention, the procedures of security chip and password card programs and data injection are simplified, and the production efficiency of products is improved.

Owner:成都三零嘉微电子有限公司

Packaging method of surface-mounted double-sided heat dissipation semiconductor power device

PendingCN113937009AEasy to weldPromote repairSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingHeat sink

The invention provides a packaging method of a surface-mounted double-sided heat dissipation semiconductor power device. The packaging method comprises the following steps of: providing a lead frame and chips; applying soldering paste to the chips, and welding the chips to corresponding base islands through using the soldering paste; carrying out bonding, wherein the chips and pin parts are connected through copper sheets and are subjected to pressure welding; carrying out cleaning, namely cleaning the lead frame welded with the chips and the copper sheets; performing plastic packaging, namely packaging the pressure-welded lead frame by using a plastic packaging material to form a plastic packaging body, and only exposing the pins; carrying out grinding, namely grinding the upper surface of the plastic package body, and exposing the top copper sheet as a cooling fin; carrying out tinning, namely tinning the pins outside the plastic package body and the exposed copper sheets; and conducting rib cutting, testing, printing, packaging and delivering. The heat dissipation problem of the power device can be better solved, and the performance of the power device is improved.

Owner:重庆平伟伏特集成电路封测应用产业研究院有限公司

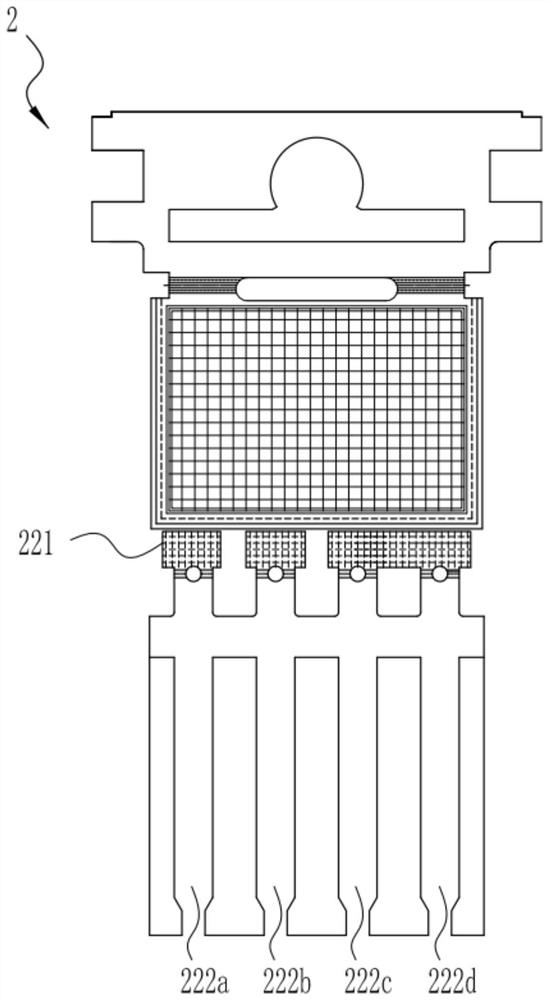

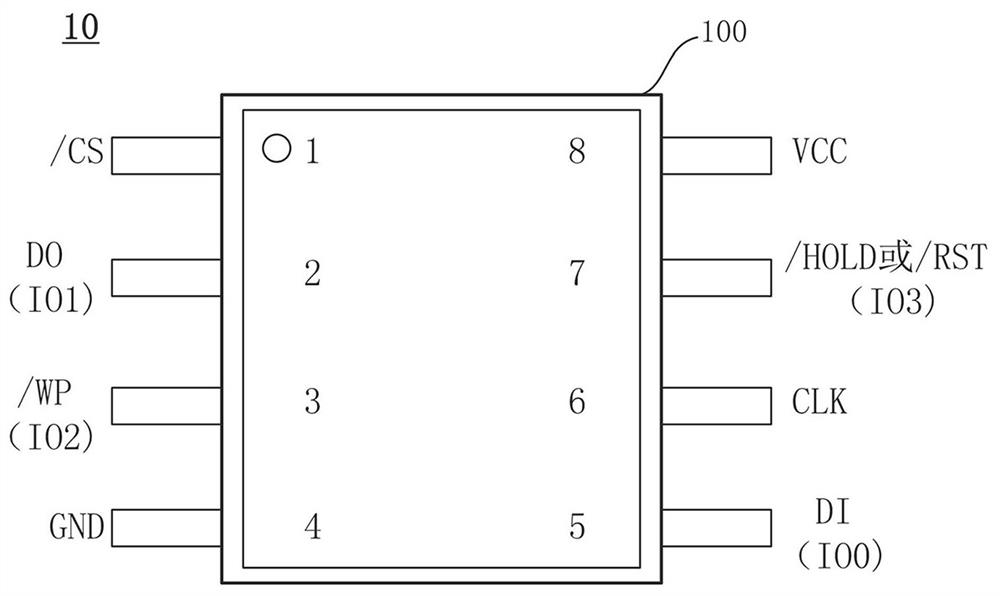

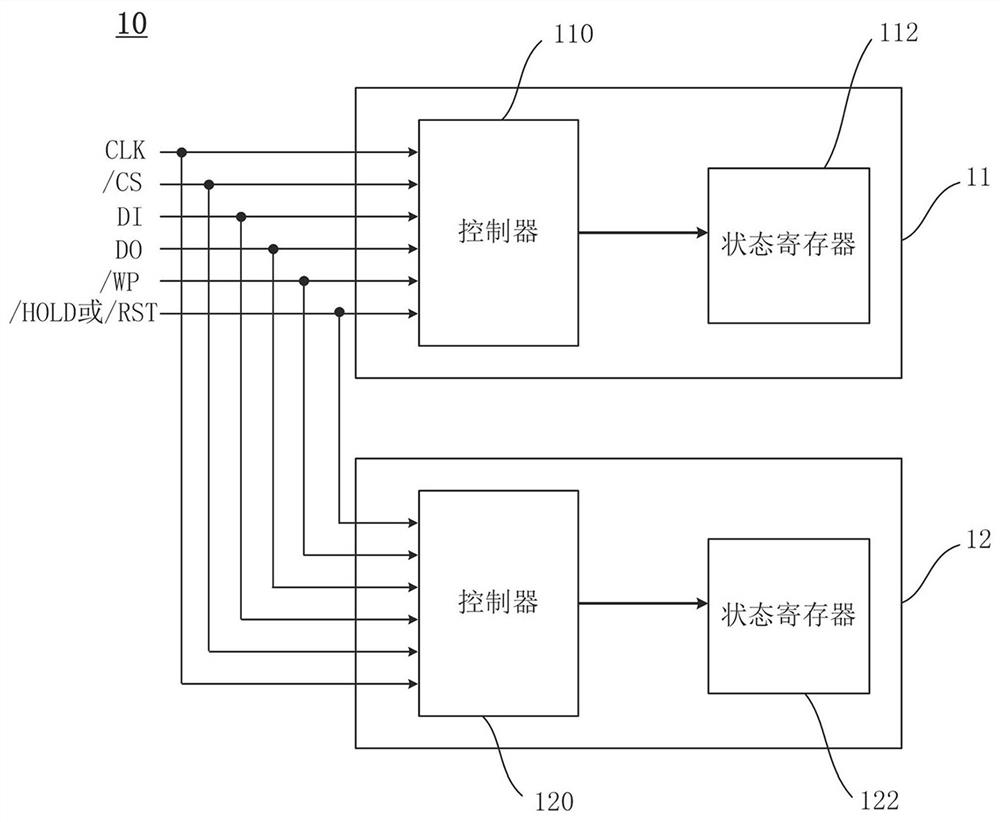

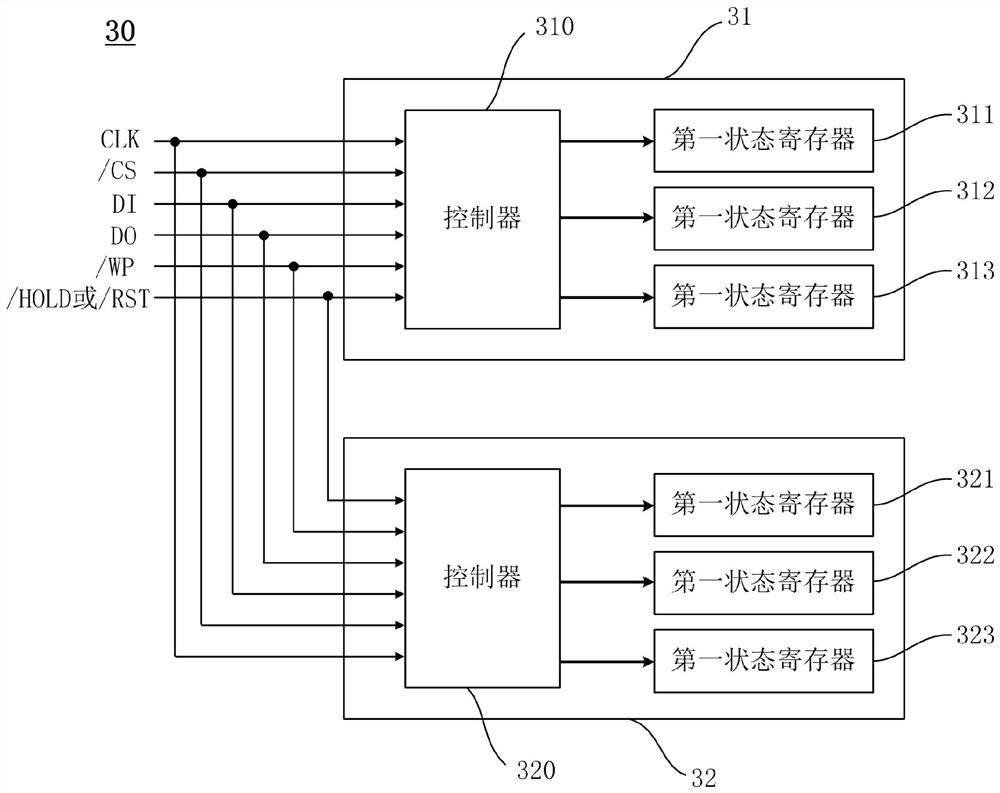

Storage packaging chip and pin multiplexing method thereof

ActiveCN111816627AVersatileImplement configurationSemiconductor/solid-state device detailsSolid-state devicesComputer hardwareMultiplexing

The invention discloses a storage packaging chip and a pin multiplexing method thereof. The storage packaging chip comprises at least one storage chip and an expansion chip which can receive the sameexternal input signal; and by additionally arranging a state register with the state bits for setting multiplexing and function switching of the pin groups of the expansion chip in the expansion chip,the configuration of the corresponding state bits in the expansion chip can be realized, so that the expansion chip supports a QPI mode and can be synchronized with the storage chip.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Wire bonding method

ActiveCN103367179AAvoid mutual short circuitSolve encapsulation bubblesSolid-state devicesSemiconductor/solid-state device manufacturingPlastic materialsEngineering

The invention discloses a wire bonding method which comprises the following steps: (1) placing a chip on a bearing member; (2) fixing plastic material on the chip through dispensing, wherein the plastic material is between wire bonding pads of the chip and pins of the bearing member; and (3) bonding welding wires on the wire bonding pads and the pins such that the welding wire are connected between the wire pads and the pins and are embedded in the plastic material. According to the wire bonding method provided by the invention, in a wire bonding process, the welding wires are immediately buried and fixed by the plastic material, thus welding wire collision and short circuit caused by vibration in the wire bonding process can be avoided, and the production yield can be improved.

Owner:NAN YA TECH

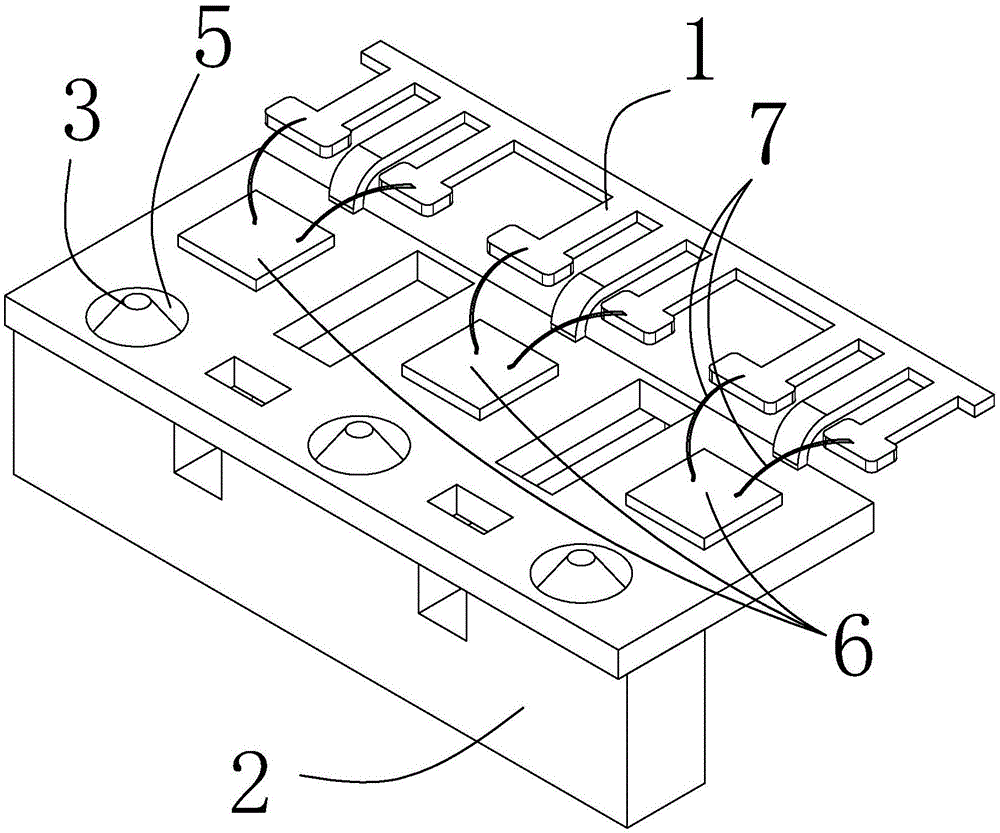

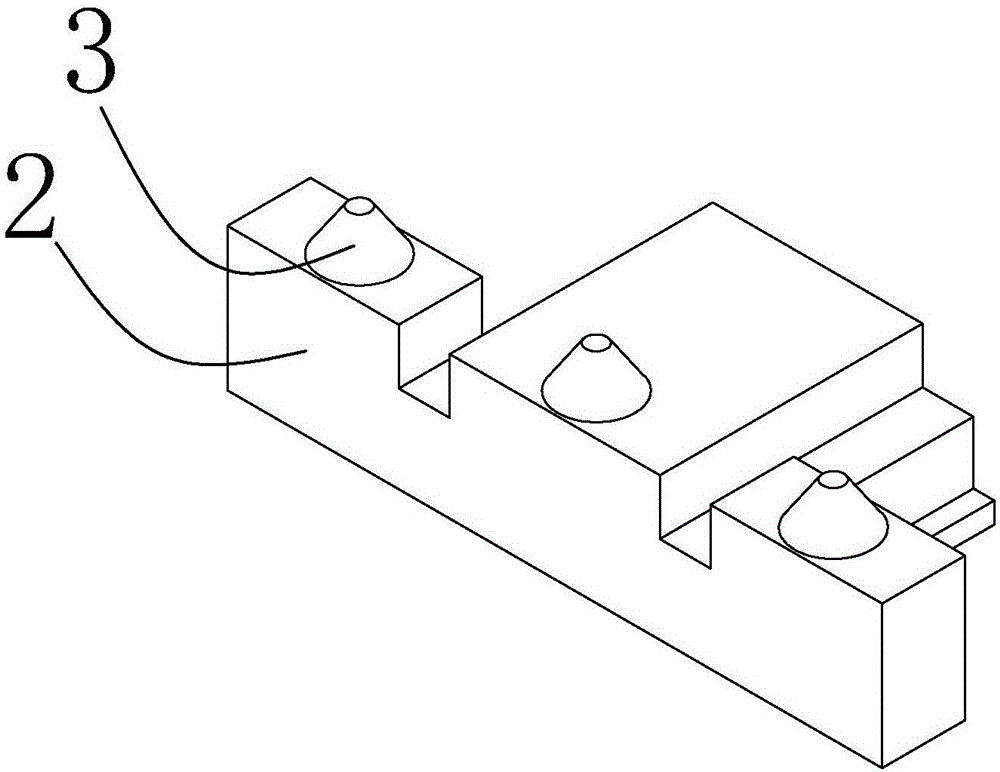

Welding platform device for semiconductor encapsulation aluminum wire or on aluminum strip bonding machine

ActiveCN106695197AAvoid damage to technical phenomenaImprove pass rateWelding/cutting auxillary devicesSemiconductor/solid-state device manufacturingSemiconductor packageEngineering

The invention relates to a welding platform device for a semiconductor encapsulation aluminum wire or on an aluminum strip bonding machine. The welding platform device comprises a worktable main body and a plurality of locating pins, wherein a plurality of locating hole-slots are formed in the worktable main body, and the locating pins with the same number are installed in the locating hole-slots; each locating pin is fixed in the corresponding locating hole-slot after penetrating a locating traction hole in a copper frame; a pressure claw presses the copper frame when the device is in welding and bonding, a welding point carries the welded aluminum wire or aluminum strip to move to a bonding pad designated spot to perform the welding, a chip and pins on the copper frame are welded together; in the process, the copper frame is pressed on the working platform through the mutual matching of the locating pins and the locating hole-slots and the combined action of a plurality of pressure claws, so that the copper frame cannot displace when receiving an external force at different directions, the technology phenomenon in the prior art is avoided, the surface quality of the welded copper frame is improved, and the percent of pass of a product is improved.

Owner:深圳市鹏程翔实业有限公司

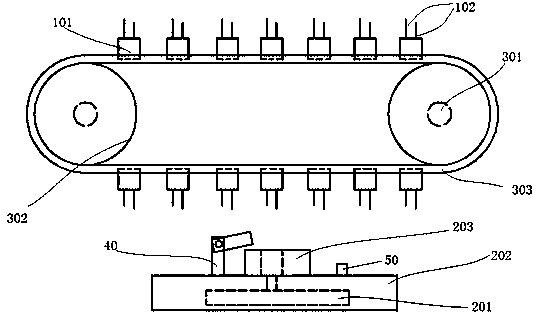

Continuous IC burning device and burn method thereof

ActiveCN107894892AHigh degree of automationLiberate manual loading and unloadingConveyorsSoftware deploymentElectric machineEngineering

The invention provides a continuous IC burning device. The device comprises an IC, a burner and a conveyor assembly, wherein the IC comprises chips and pins, the pins are arranged on the surfaces of the chips, the chips are in communication connection with the pins, the burner comprises a data output unit, a base and a burning base, the data output unit is arranged in the base, the burning base isarranged on the surface of the base, the burning base is matched with each pin in shape, the data output unit and the burning base are in communication connection, the conveyor assembly comprises stepping motors, conveyor gears and a conveyor belt, the output shafts of the stepping motors are in axial connection with the conveyor gears, the stepping motors can drive the conveyor gears to rotate along the axes of the conveyor gears, bulges meshed with the conveyor gears are arranged on the inner side of the conveyor belt, grooves matched with the chips in shape are formed in the outer side ofthe conveyor belt, the chips are embedded into the outer side of the conveyor belt, the pins are exposed on the outer portion of the conveyor belt, and the burning base is located under the conveyor belt. The IC burning device is capable of continuous burning and low in cost.

Owner:HUIZHOU JUNYA DIGITAL TECH CO LTD

Power module and packaging method thereof

InactiveCN110176451ALow costSimple packaging processSemiconductor/solid-state device detailsSolid-state devicesHigh densityComputer module

The invention provides a power module and a packaging method thereof. The power module comprises a bearing plate; the bearing plate comprises an insulating layer and a metal layer arranged on one surface of the insulating layer; and the power module further comprises at least one power chip and at least one driving chip, which are attached to the surface, far away from the insulating layer, of themetal layer, and are electrically connected with the metal layer through bonding wires. The power chips, the driving chips and pins are attached to the metal layer of the bearing plate, namely, a high-density lead frame and a PCB used in the prior art are replaced with the bearing plate, so that the cost is greatly reduced and the packaging process is simplified.

Owner:EDGELESS SEMICON CO LTD OF ZHUHAI

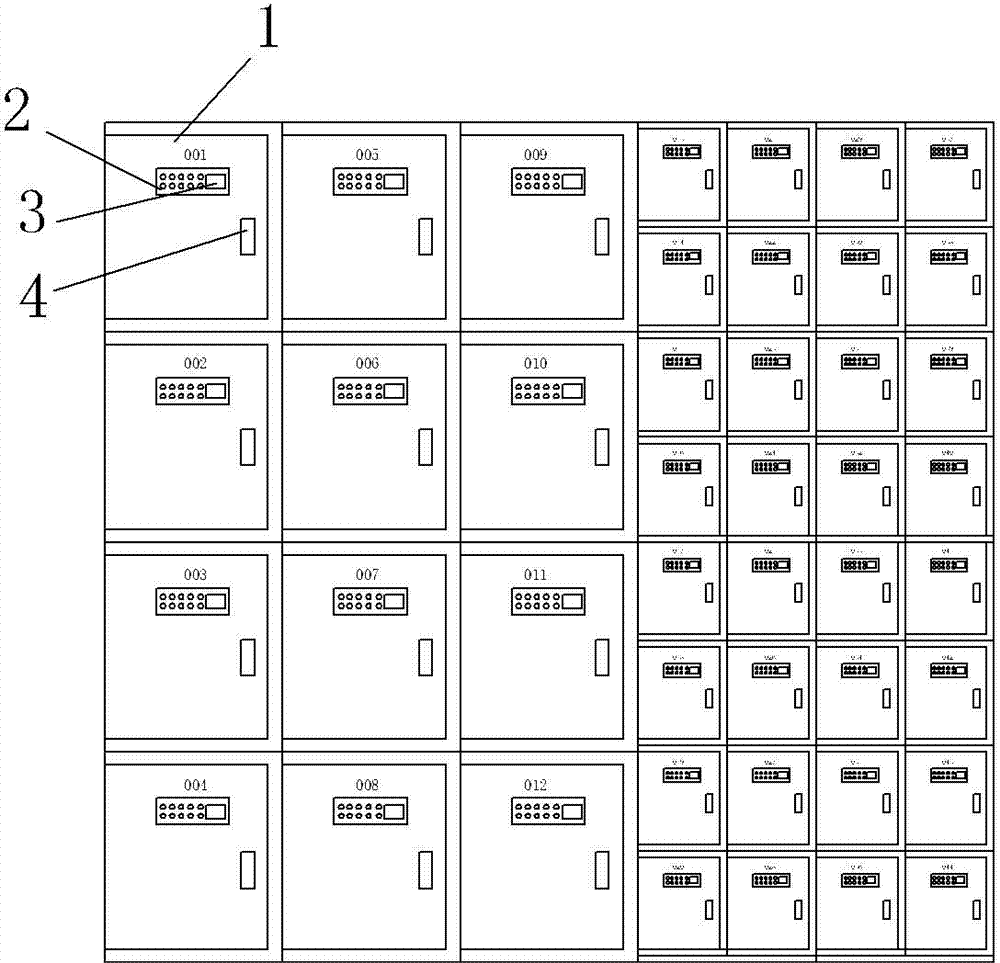

Special receiving and sending equipment and application method thereof

InactiveCN104504818AEnsure safetyEffective dockingApparatus for meter-controlled dispensingPasswordControl manner

The invention provides special receiving and sending equipment. The equipment allows users to easily receive and send goods, allows couriers to work under an intensity relatively concentrated and balanced, allows the goods to be greatly safeguarded, allows excellent safety and allows the couriers and the users to be easily connected, thus ensuring convenience and quickness. The invention further provides a special method of applying the special receiving and sending equipment. The special receiving and sending equipment comprises single lockers; each single locker is provided with a chip and a combination lock; each chip is internally provided with a password generating program; each chip is connected with the corresponding combination lock in an electronic control manner; the single locks are set in a concentrated residential area or a concentrated office area; to use one single locker of the corresponding specification, a user inputs a request signal to the single locker, the single locker generates a password or a barcode and opens, the user to rent the locker puts a package in the single locker of the corresponding specification, closes a door and transmits the password or the barcode and a door number to a receiver, and the receiver inputs the password or the barcode to take the package.

Owner:WUXI ZHENGYANG MACHINERY

High-speed light-receiving component with integrated limiting amplifier and its preparation method

ActiveCN103278891BReduce volumeReduce weightCoupling light guidesAudio power amplifierFlexible circuits

Owner:WUHAN TELECOMM DEVICES

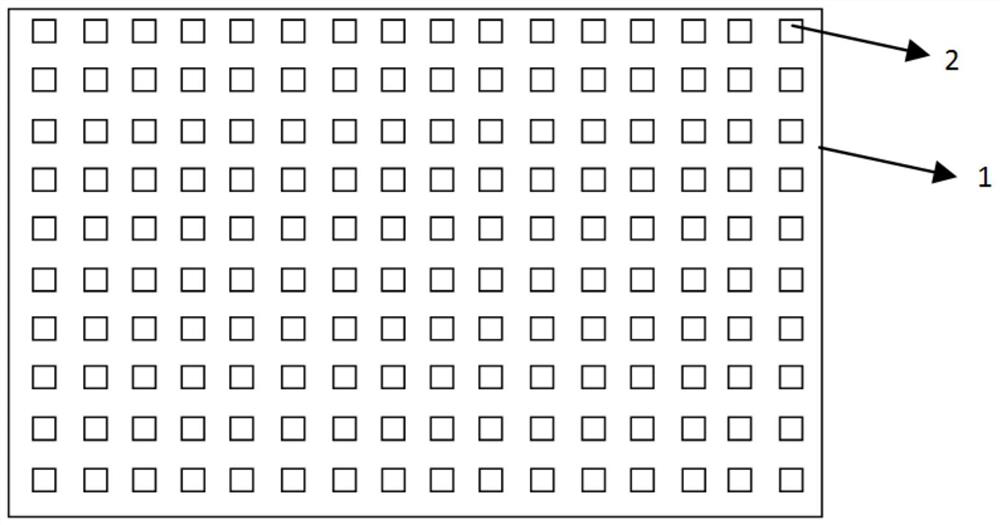

Locking glue array lead frame and application thereof in chip packaging piece

PendingCN111987069AReduce binding areaReduce areaSemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

The invention discloses a locking glue array lead frame and application of the locking glue array lead frame in a chip packaging piece; a plurality of locking glue holes are uniformly formed in the surface of a substrate of the lead frame, and areas, without holes, among the locking glue holes are used for lead bonding. When the lead frame is applied, the application comprises the following steps:step 1, thinning a wafer of a chip, and then pasting a DAF film on the back surface; step 2, adhering the chip to the substrate of the lead frame; step 3, cleaning a circuit to be bonded, and carrying out lead bonding between the chip and the substrate, between the chip and pins, between the substrate and the pins, or between the chips to obtain a bonded circuit; and step 4, performing plasma cleaning on the bonded circuit, performing plastic package by a plastic package material, embedding the plastic package material into plastic locking holes to form a plastic package body, curing the plastic package body, then sequentially carrying out electrotinning, laser marking and rib cutting forming to obtain a single-chip package part. The plastic package material penetrates through the plasticlocking holes, the effects of pinning strengthening and separation layer spreading preventing are achieved, and the reliability of the product is improved.

Owner:郑州兴航科技有限公司

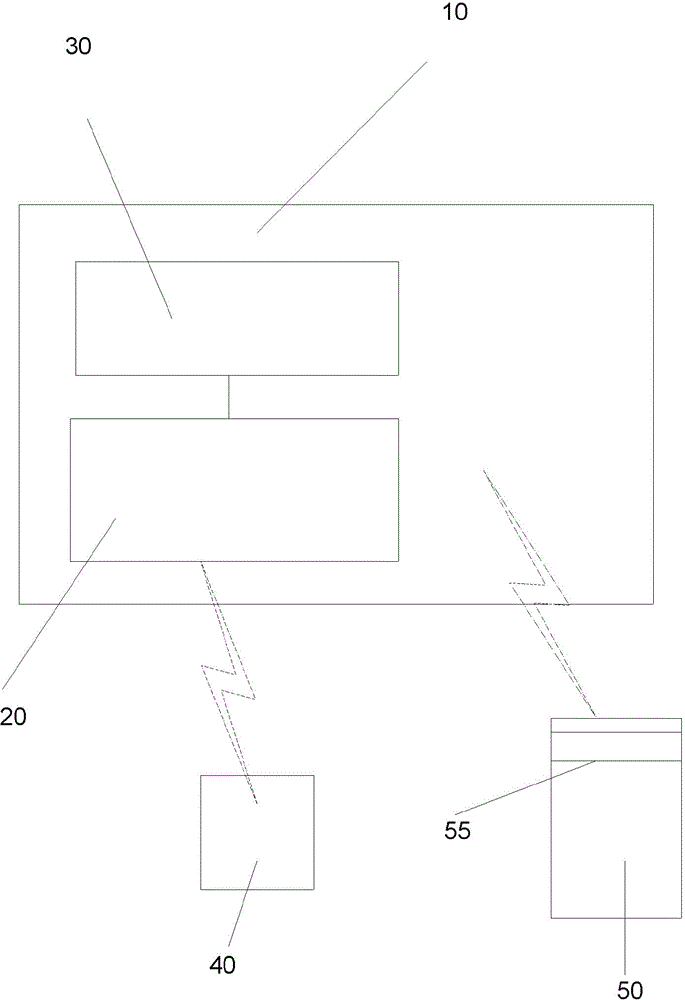

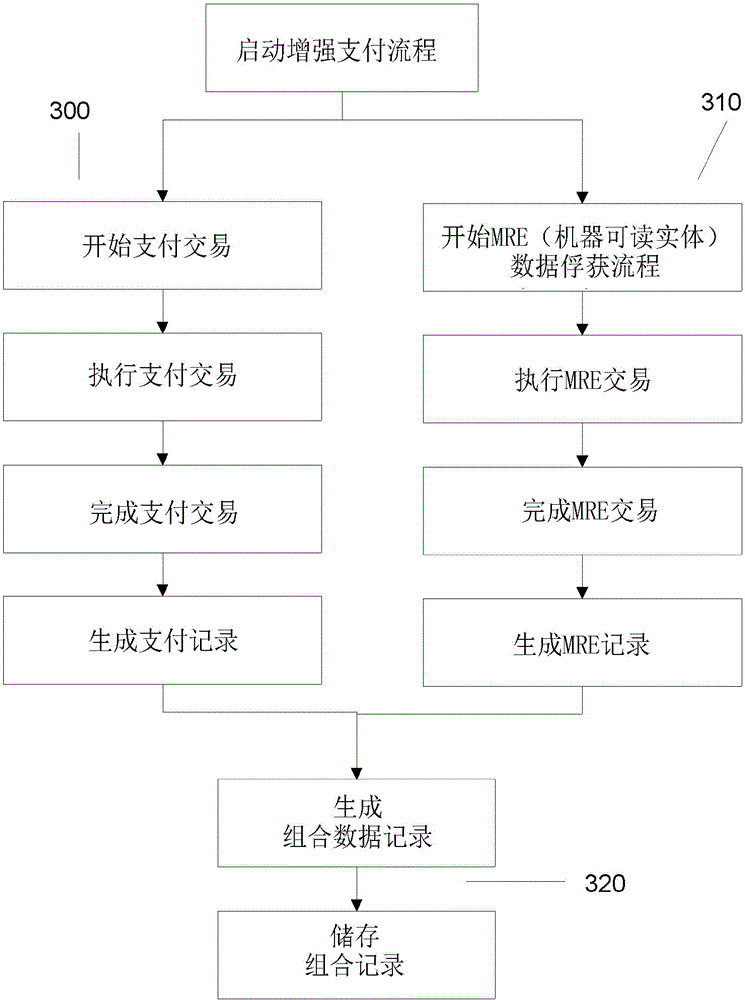

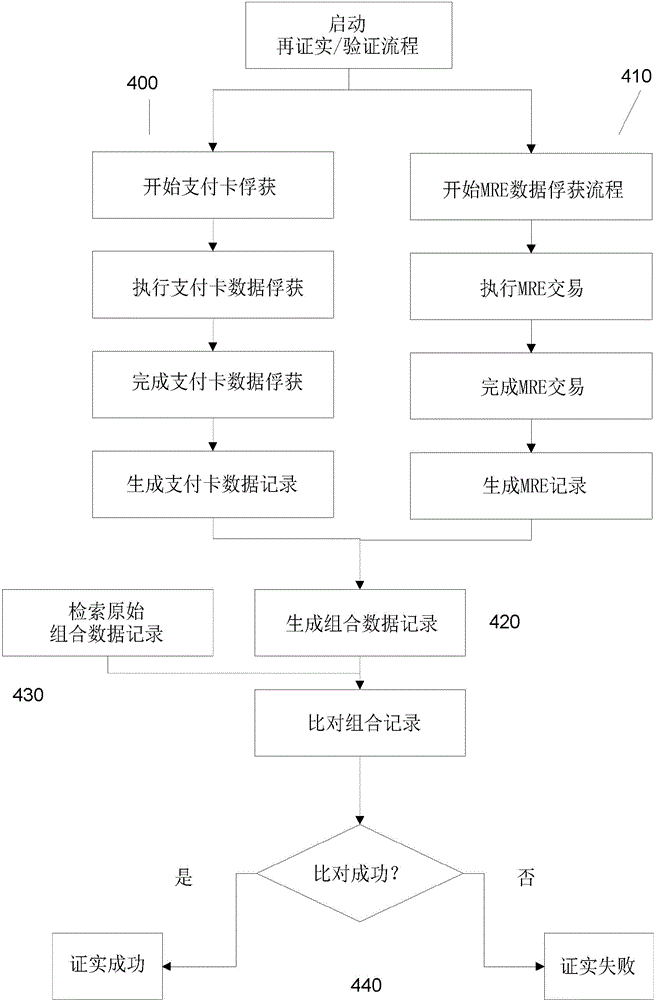

Payment unit, system and method

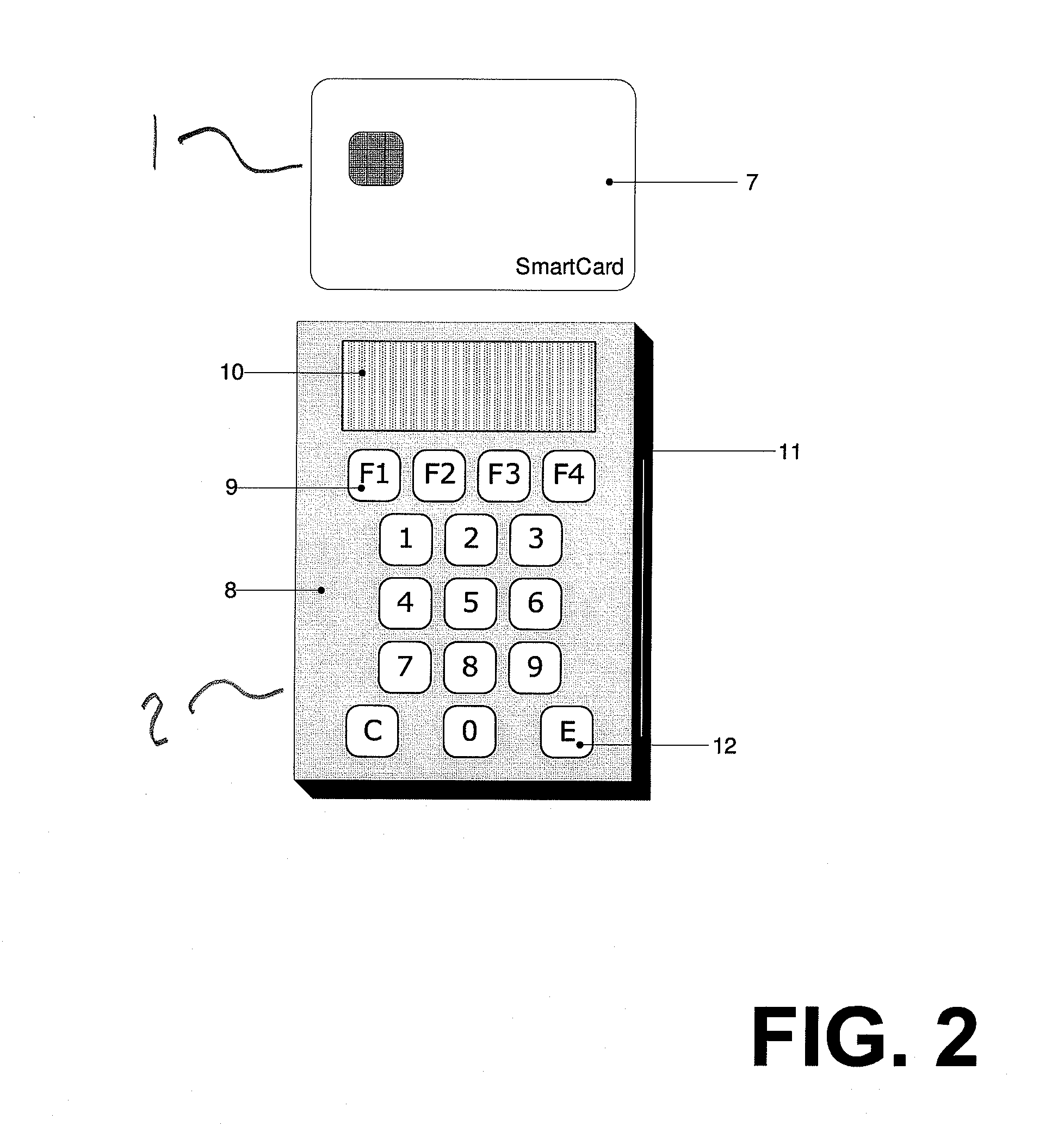

A payment terminal 10 includes a payment card reader 40, which obtains payment data, preferably from a contactless payment unit or card 40 that is physically close to the terminal 10. A secondary reader (not shown) obtains supplementary data (211, fig.3) from a machine readable entity such as a passport or travel document. The secondary reader may comprise a radio frequency transceiver. The secondary data is combined with the payment data to form a payment record, and thus makes the payment by contactless methods more secure by providing greater assurance as to the identity of the customer. A method of payment and a payment system are also disclosed. The payment means may alternatively be a NFC payment device, or a chip and pin device.

Owner:VANCLARE SE

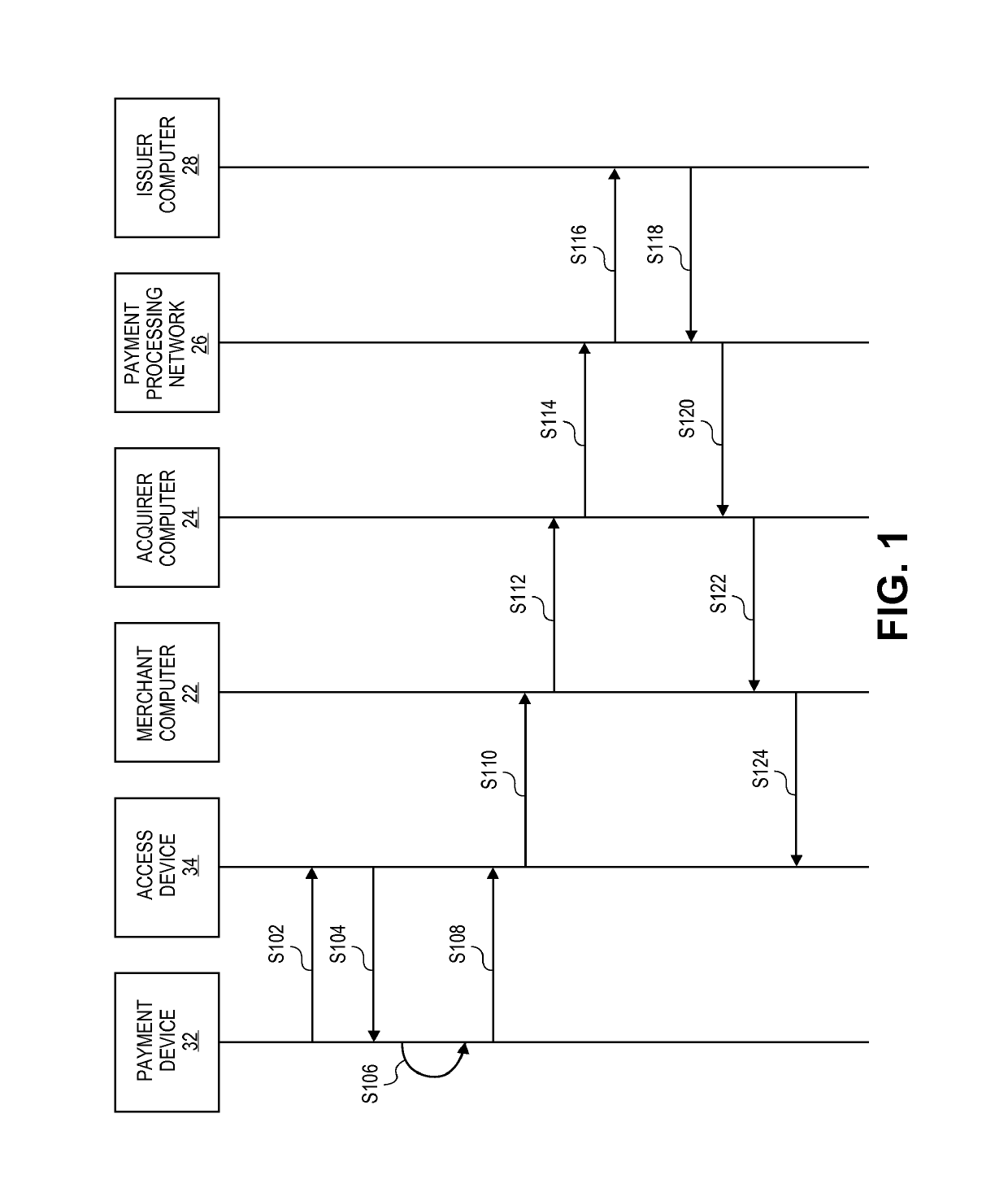

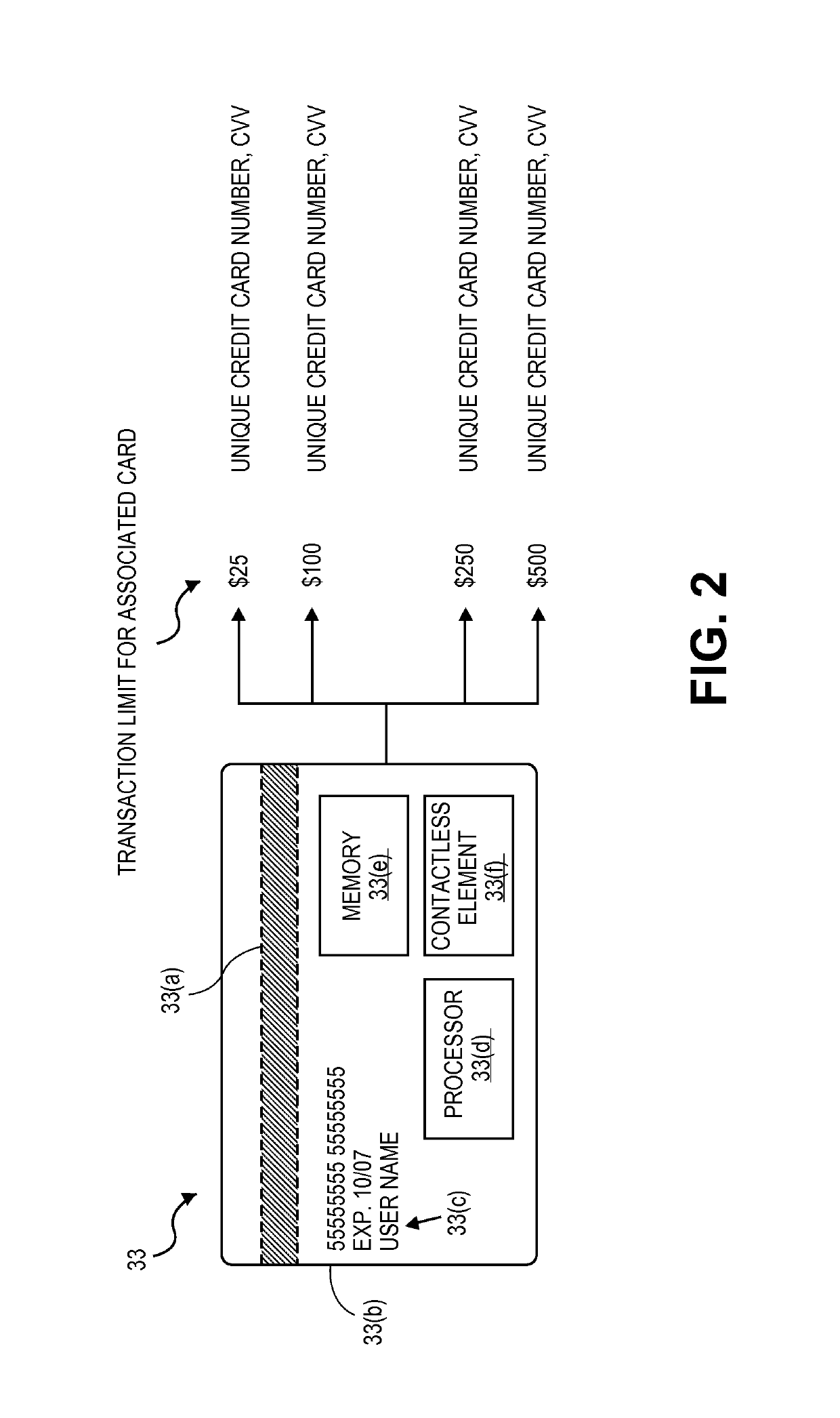

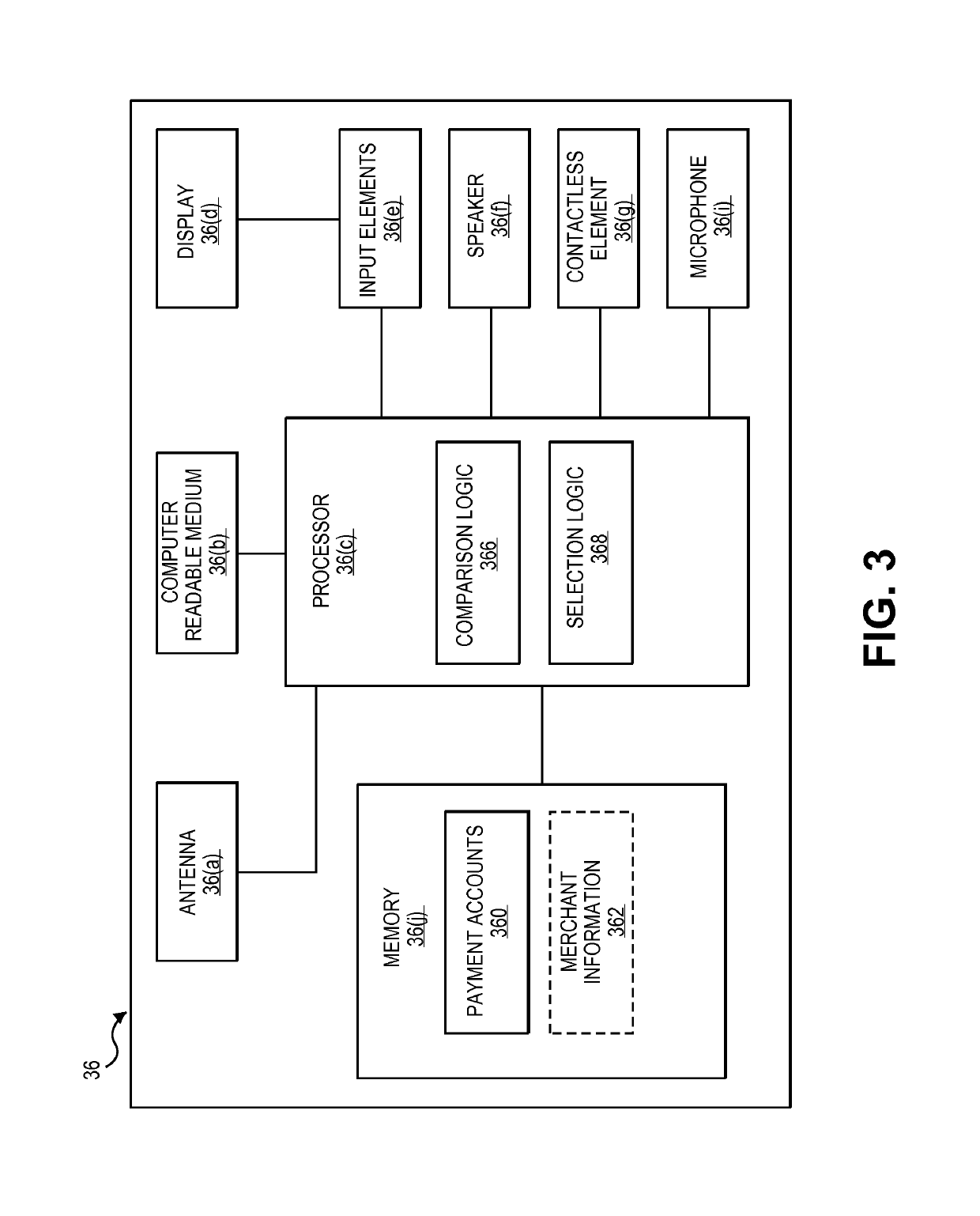

Dynamic account selection

Embodiments automatically select one of the multiple pre-generated payment cards provisioned on a mobile device. The multiple pre-generated payment cards (real or virtual) may each have a different credit limit. The mobile device may automatically select one of the multiple payment cards based on a transaction value of a transaction that is being conducted. An available credit limit of the selected payment card may be equal to or slightly greater than the transaction value. In some embodiments, the available credit limit of the selected payment card may be closer to the transaction value than the available credit limits of the remaining payment cards. In some embodiments, the different payment cards may be provisioned in a chip-and-pin based smart credit card or mobile wallet.

Owner:VISA INT SERVICE ASSOC

Multi-purpose data storage key

A secure non-volatile solid state memory data key appears similar to a conventional USB flash drive modified to have a physical shape resembling a door key with an eyelet for attaching the data key to a key ring or lanyard. The data key includes a USB port, a microprocessor (effectively serving as the “chip” in the chip-and-pin configuration), and a secure memory for holding secure transaction information, such as credit and debit card numbers, verified personal identification (federated ID), and other secure data. The data key may include a dual-purpose electrical contact that serves both as a four-pin USB contact and an eight-pin chip-and-pin contact. Another example is a data key with a near-field communication (NFC) receiver that allows to data key to turn a smartphone, laptop or other computer into an NFC merchant terminal.

Owner:UQONTROL

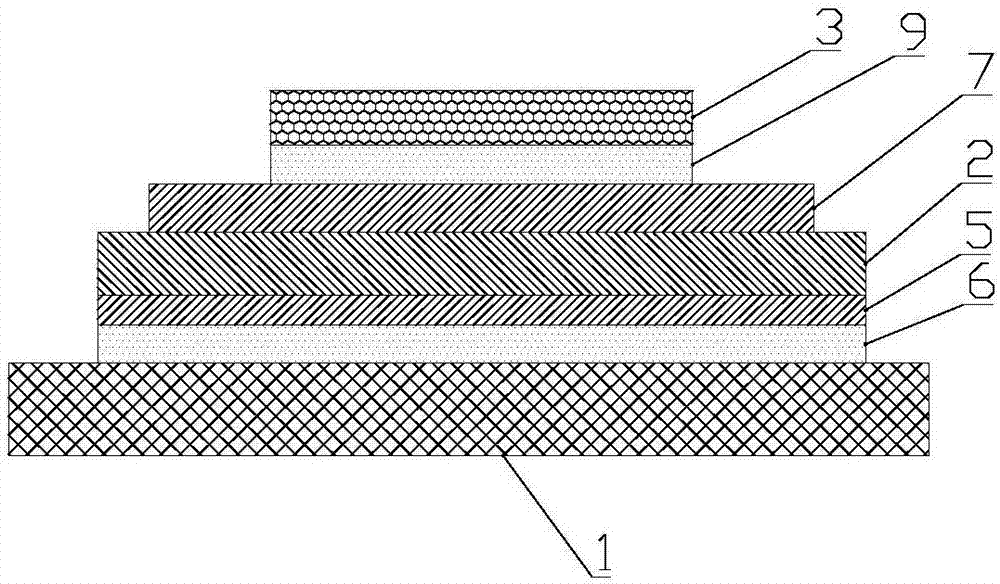

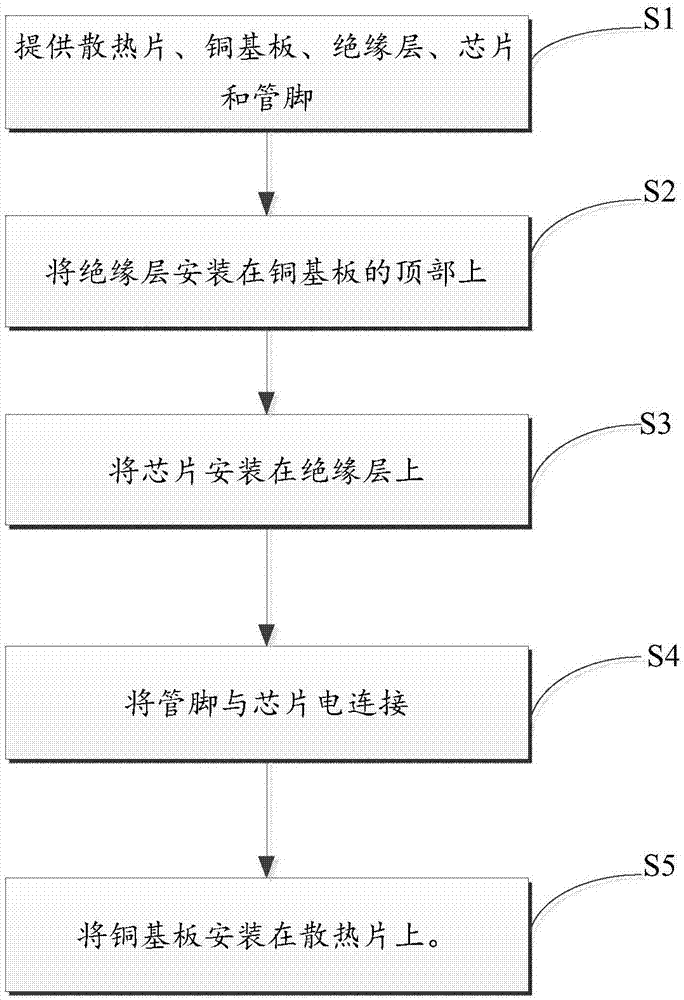

Manufacturing method for insulation structure of power electronic device

InactiveCN107316843AEasy to useHeat conduction effect plusSemiconductor/solid-state device detailsSolid-state devicesElectricityInsulation layer

The invention discloses a manufacturing method for an insulation structure of a power electronic device, and belongs to the technical field of power electronics. The manufacturing method comprises the steps of providing a heat sink, a copper substrate, an insulation layer, a chip and pins; installing the insulation layer at a top part of the copper substrate; installing the chip on the insulation layer; electrically connecting the pins and the chip; and installing the copper substrate on a heat sink. According to the manufacturing method for the insulation structure of the power electronic device, the insulation layer is arranged on the copper substrate, thus, a current generated by the chip cannot be transferred to the copper substrate, the copper substrate is electrically insulated, and correspondingly, the insulation layer is unnecessary to arrange between the copper substrate and the heat sink. With the insulation structure of the power electronic device, manufactured by the method, the heat conduction effect of the copper substrate to the heat sink is better on the condition that the normal use function of the power electronic device is ensured, and the normal use of the power electronic device is more favorably ensured.

Owner:QINGDAO JIAEN SEMICON

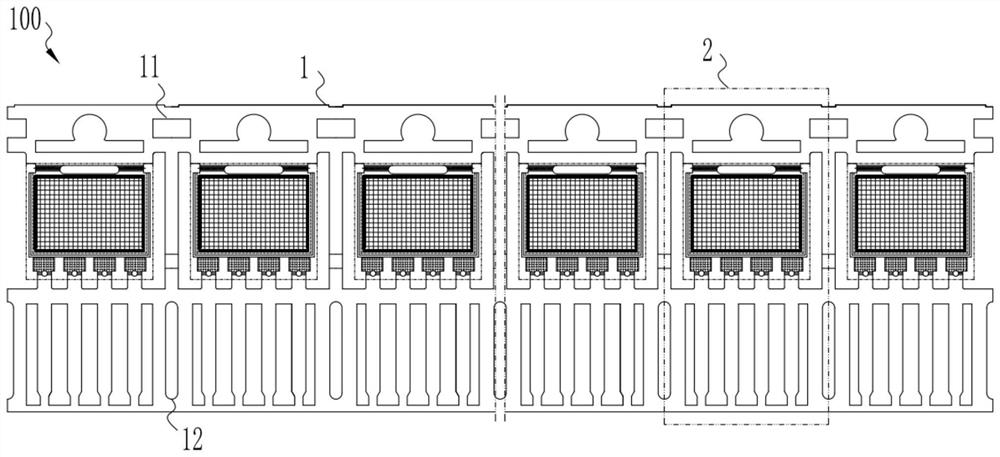

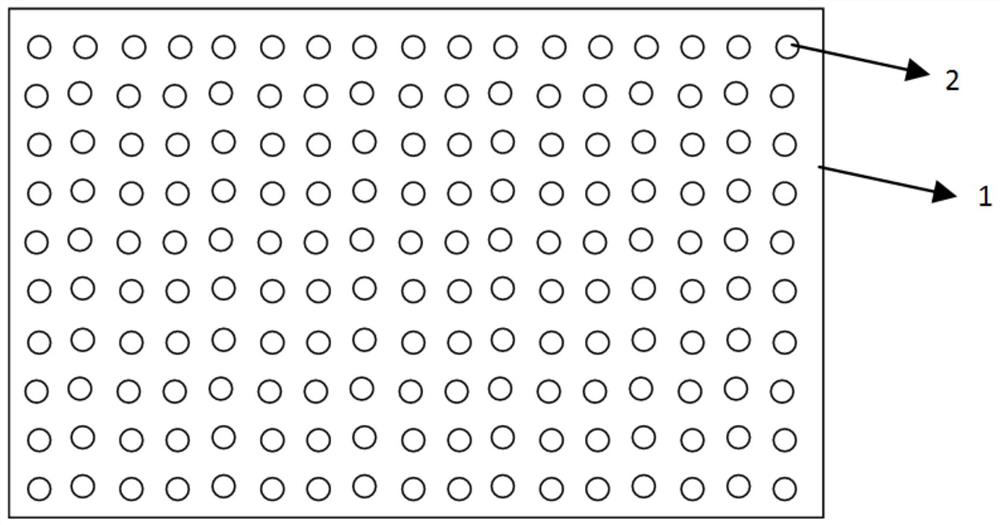

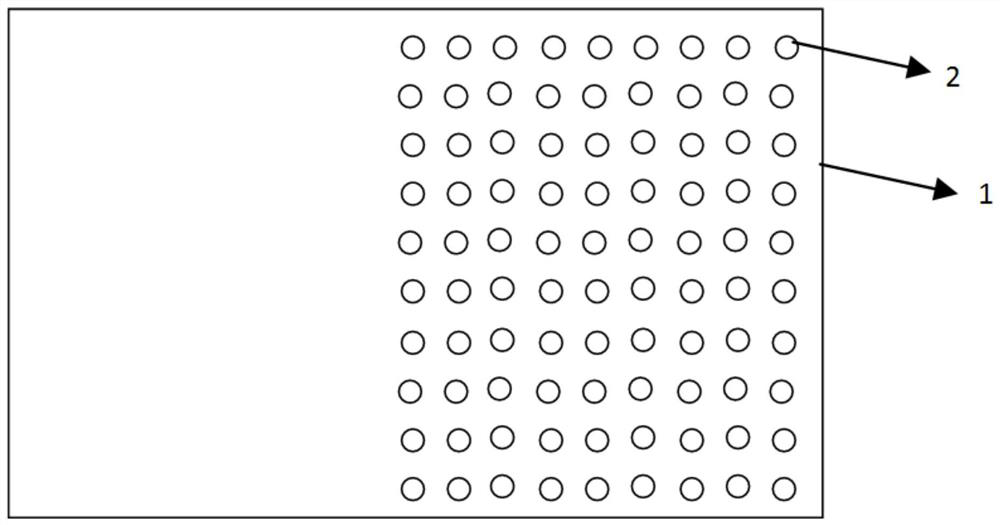

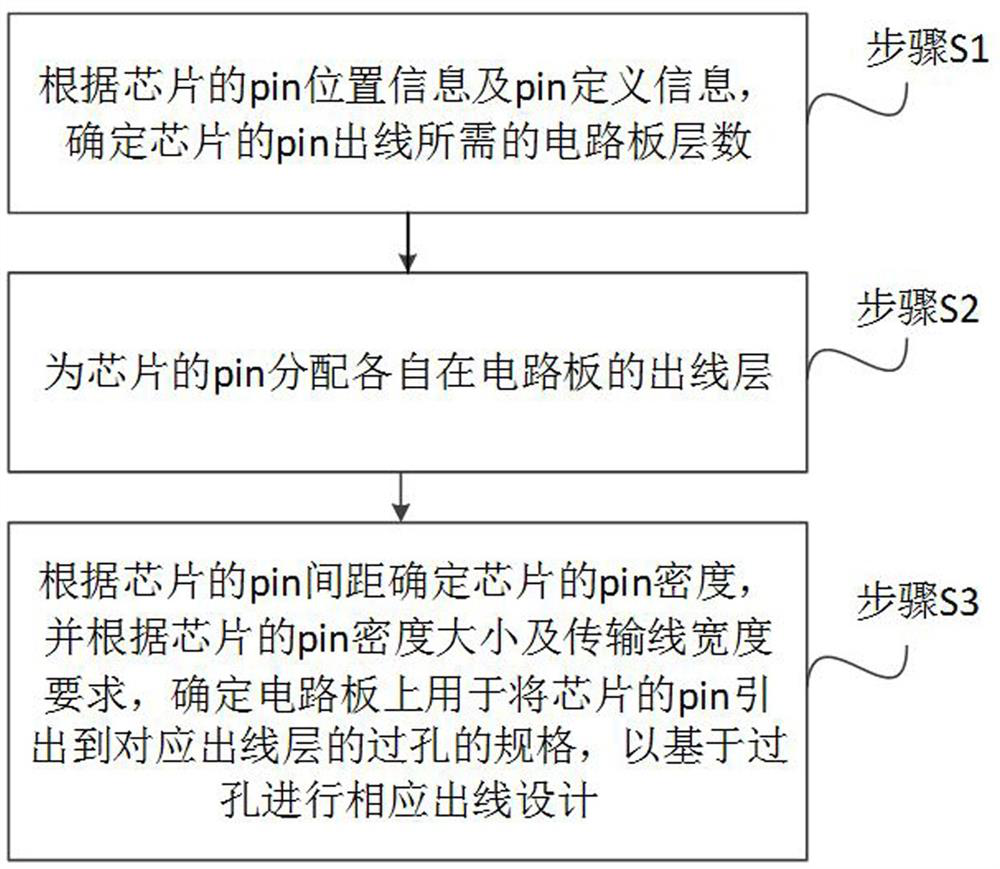

Chip and pin outgoing line design method thereof

ActiveCN113435154ASimple designGuarantee the quality of outlet designComputer aided designSpecial data processing applicationsComputer hardwareEmbedded system

The invention discloses a chip and a pin outgoing line design method thereof, which are applied to a BGA packaged chip. The method comprises the following steps of determining the number of layers of circuit boards required by the pin outgoing lines of the chip according to the pin position information and the pin definition information of the chip; distributing the respective outgoing lines layers on the circuit boards for the pins of the chip; and according to the pin density of the chip and the width requirement of the transmission lines, determining the specification of a via hole for leading out the pins of the chip to the corresponding outgoing line layer on the circuit board so as to carry out the corresponding wire outlet design based on the via hole. Therefore, the invention provides a unified chip pin outgoing line design aiming at the BGA packaged chip, and the design is more refined, so that the outgoing line design quality of the chip pin is ensured.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

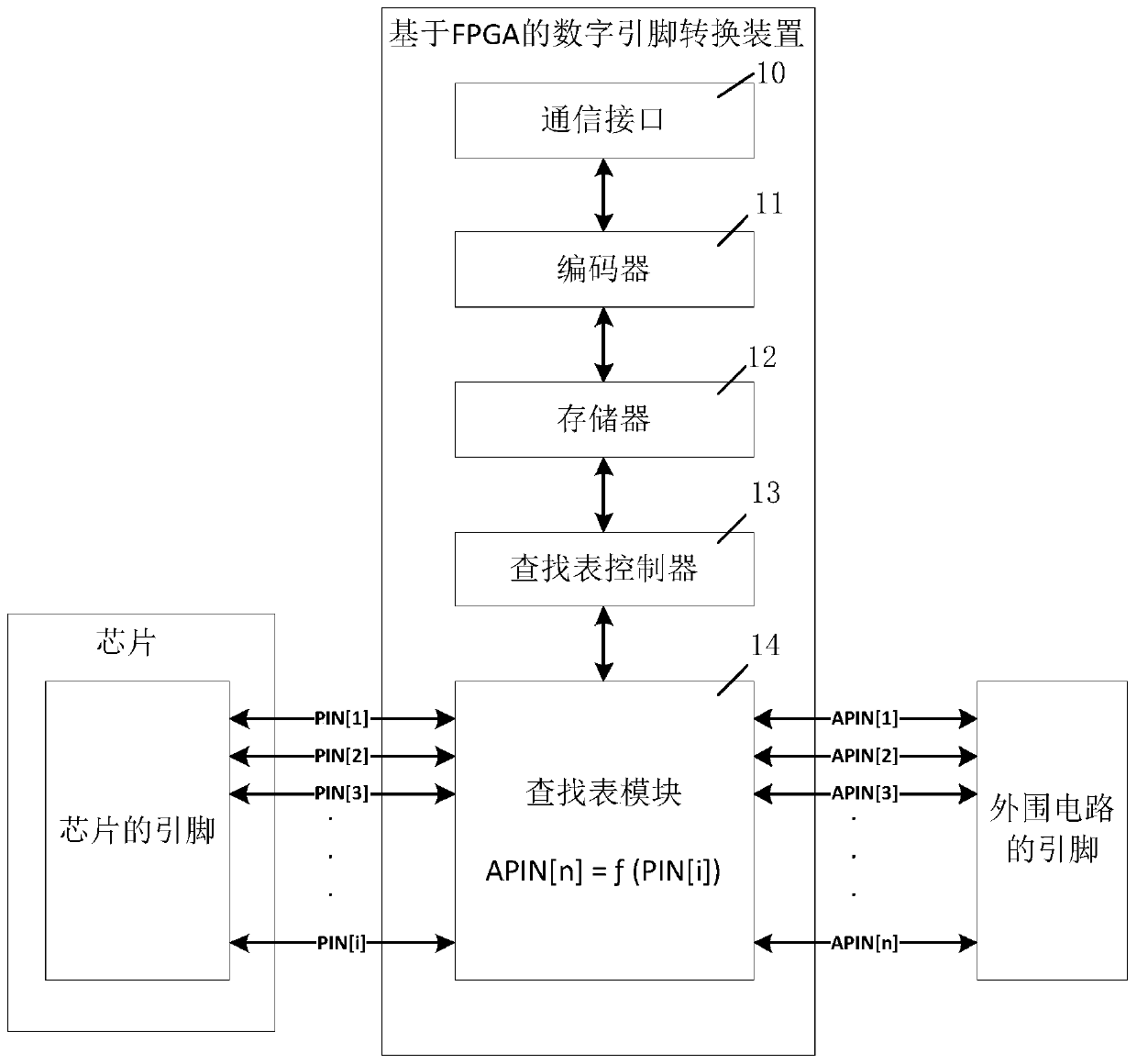

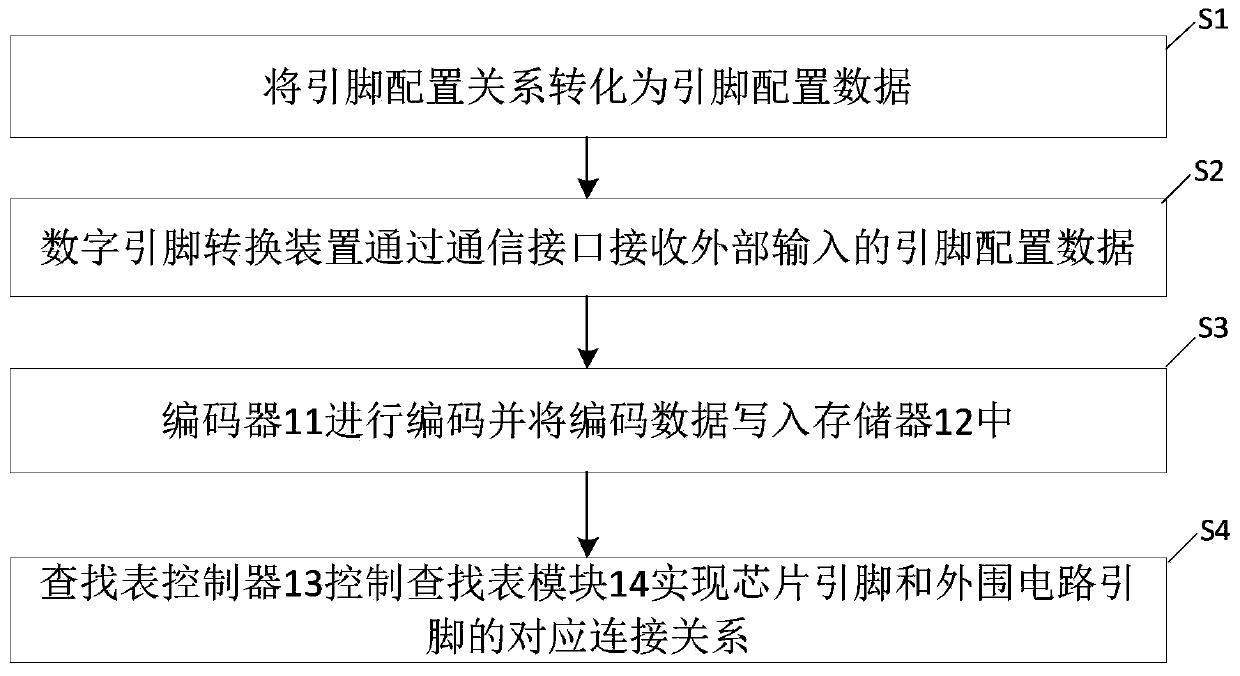

Digital pin conversion device and method based on FPGA

ActiveCN110674077ARandom arrangementIncrease flexibilityArchitecture with single central processing unitElectric digital data processingCommunication interfaceLookup table

The invention discloses a digital pin conversion device and method based on an FPGA. The device comprises a communication interface, an encoder, a memory, a lookup table controller and a lookup tablemodule. The communication interface receives externally input pin configuration data, wherein the pin configuration data comprises pin data of the chip and pin data of a peripheral circuit. The encoder encodes the pin configuration data according to the pin configuration requirement of the peripheral circuit so as to generate a two-dimensional relationship data table in one-to-one correspondence between the encoded chip pins and the pins of the peripheral circuit. The memory stores the two-dimensional relationship data table, and the lookup table controller reads the address information and the data information in the memory so as to control the lookup table module to select the connection relationship between the pin of the chip and the pin of the peripheral circuit. According to the digital pin conversion device and method based on an FPGA, random arrangement of existing pins of the chip can be realized through random configuration of software on the existing pin resources of the chip, and the cost is reduced.

Owner:BEIJING SMARTCHIP MICROELECTRONICS TECH COMPANY +2

Method for packaging large-power LED chip

InactiveCN103456868AReduce the impactProcess energy saving and environmental protectionSemiconductor devicesSilver colloidEngineering

The invention discloses the chip packaging mode that a large-power LED and a support are solidified through composite iron glue. Firstly, the support is sufficiently cleaned through IPA and ACE, a backside plating reflection layer is led to a large-power LED chip process according to a DBR technology which is basically introduced in wafer factories currently, the LED chip is fixed to the support through the energy-saving and environment-friendly composite iron glue with good heat dissipation effect, after drying and solidification, electrodes of the LED chip are connected with leading wires of the support, fluorescent powder is evenly stirred in colloids, the large-power LED chip and pins of the large-power LED chip are wrapped with the fluorescent powder and the colloids, and then drying is carried out, the colloids are solidified, and the support is inserted into an aluminum substrate finally. The method is easy and feasible, saves energy and protects the environment; under the current situation that the DBR backside plating technology is basically utilized in large-power LEDs currently, because silver colloids are replaced by the composite iron glue, packaging cost and effect of metal in the collides on human bodies and the environment are reduced, and strong economical efficiency and practical value are achieved.

Owner:KUNSHAN AODELU AUTOMATION TECH

Chip carrier holed semiconductor package element and mfg. method thereof

InactiveCN1303678CSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageColloid

A semicondcutor packaging unit with an aperture on its chip holder and its process method is to adhered a chip to a chip seat having at least one aperture to shield the back of the chip and expose the aperture, then to fully coat the back that exposes the aperture of the seat, after finishing connecting solder wire of the chip and pin and molding for forming packaging colloid wrapping the said chip and holder, the voide problem between the chip and the seat will not happen when the packaging colloid becomes solid since there is no seam in between, and no die crack or popcorn occur in the products.

Owner:SILICONWARE PRECISION IND CO LTD