Semiconductor chip packaging structure and packaging method

A technology of chip packaging structure and packaging method, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of reducing thickness, etc., and achieve thickness reduction, convenient quantitative production and use, and fast processing Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Embodiment of semiconductor chip packaging structure

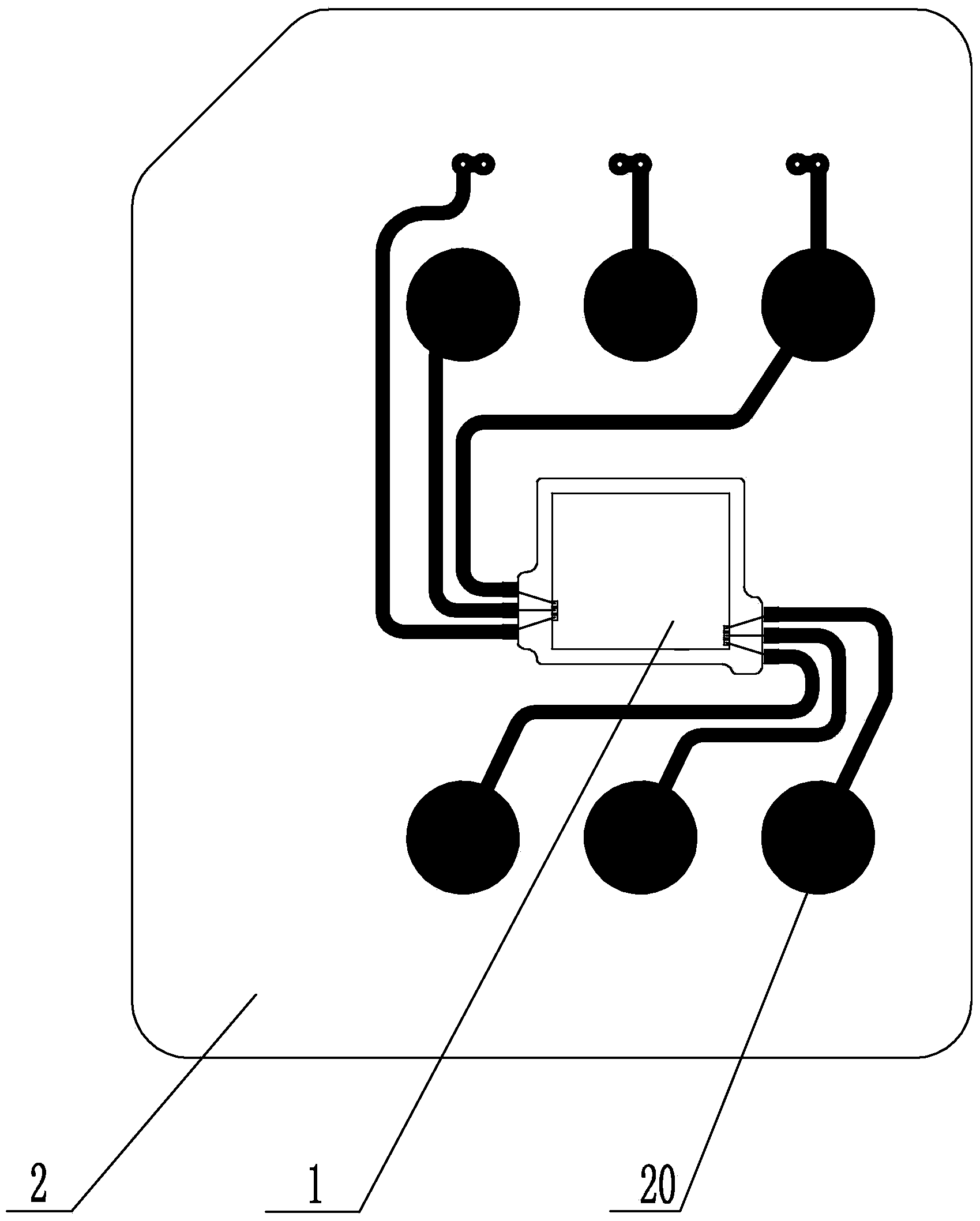

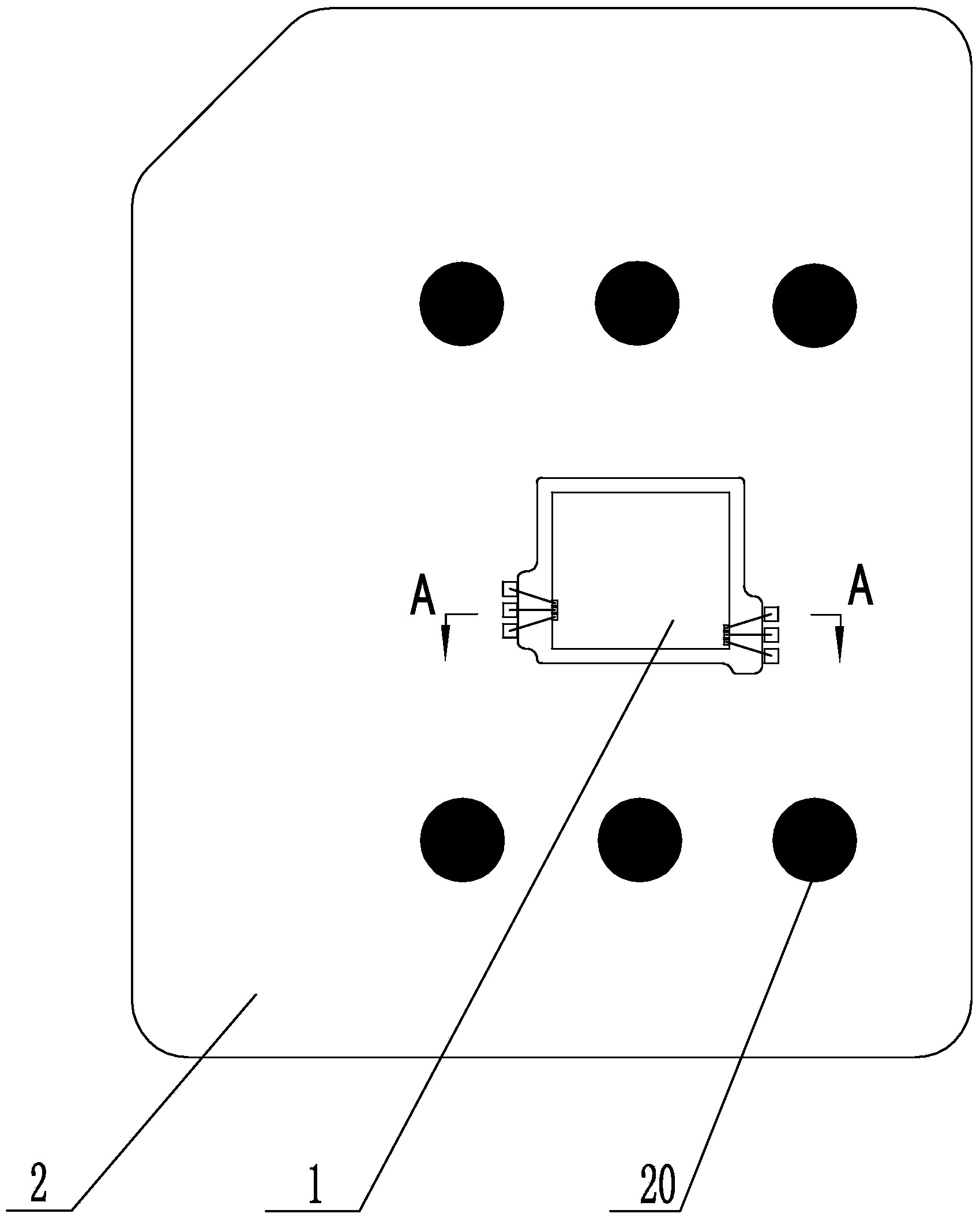

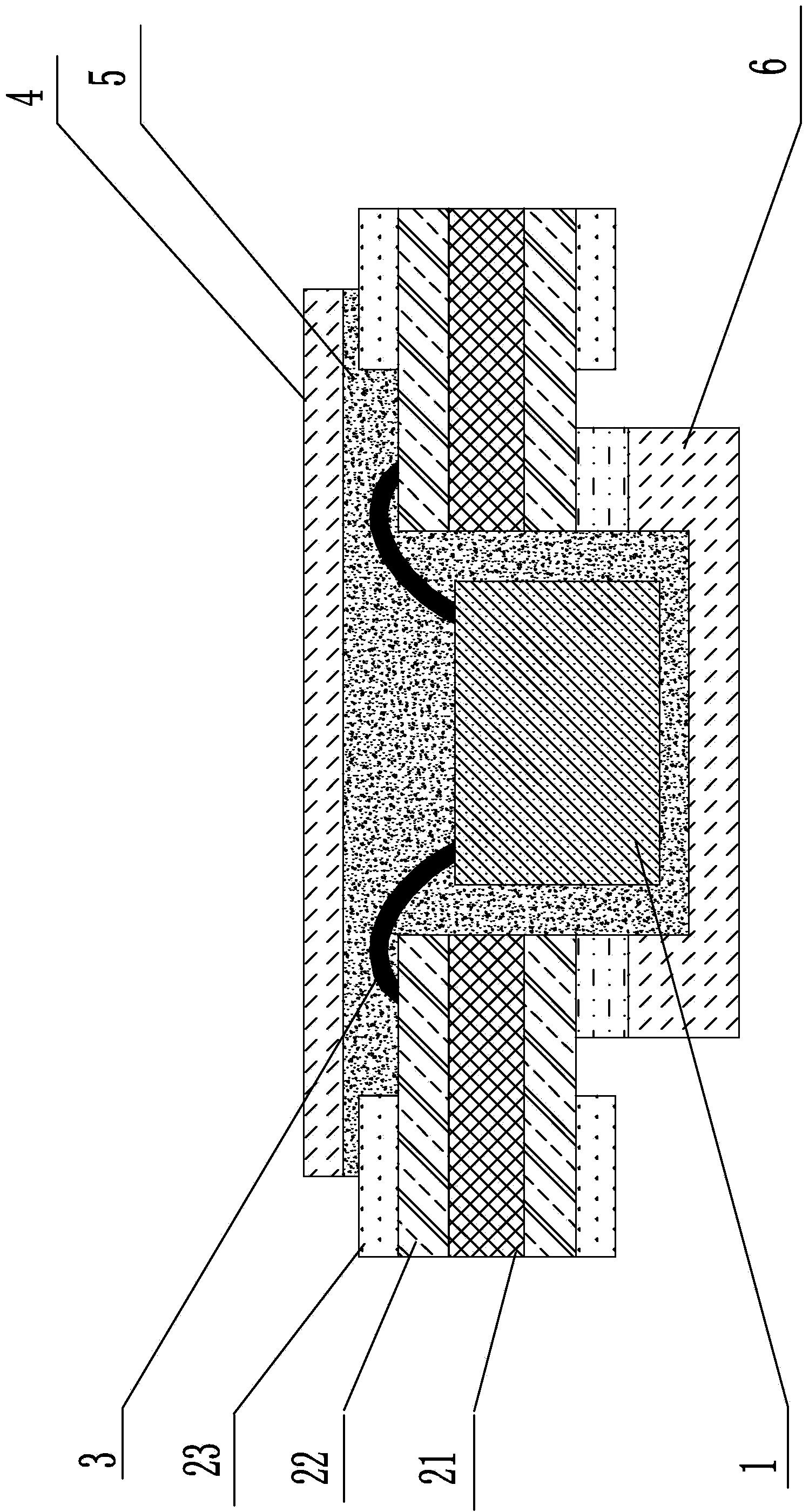

[0038] The embodiment of this chip packaging structure is a patch card (or a film card) for a SIM card of a mobile phone, such as Figures 1 to 3 shown. The upper and lower surfaces of the substrate 21 of the circuit board 2 are covered with a conductive layer 22, and the conductive layer 22 on the circuit board forms pins, contacts 20 and conductive lines, and the corresponding contacts 20 and pins are connected through conductive lines, such as figure 1 As shown, it is covered with a solder resist layer 23, and the solder resist layer 23 has corresponding holes at the pins and contacts, so that the pins and contacts are exposed, as figure 2 shown.

[0039] In this example, the chip 1 is rectangular, and the rectangular through-holes on the circuit board 2 that cooperate with the chip 1 are mounting holes, whose length and width are 0.1 mm larger than the length and width of the chip 1 . The circuit board in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More