A Subcircuit Extraction Method of Digital Logic Circuit

A technology of digital logic circuit and extraction method, applied in the direction of logic circuit with logic function, etc., can solve the problem of no common part, etc., and achieve the effect of strong versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

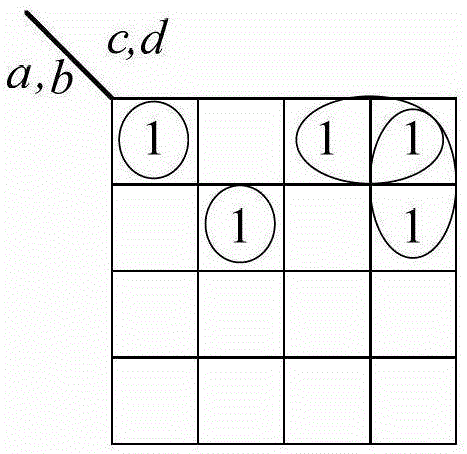

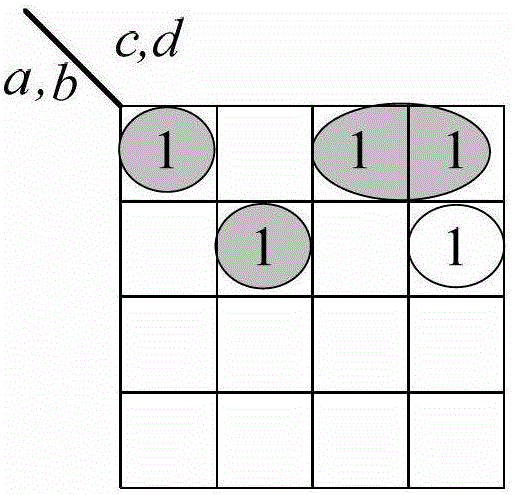

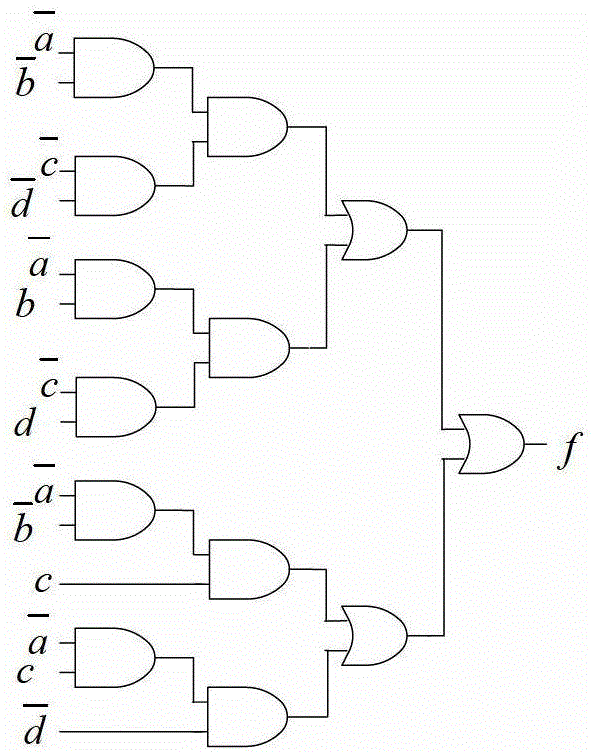

[0038] A sub-circuit extraction method of a digital logic circuit is characterized in that the logic function corresponding to the original circuit is defined as f, and f is expressed as a logic "or" form of m product items; the logic function corresponding to the sub-circuit is f 1 , f 1 Expressed as a logical "or" form of n product items; the set of product items corresponding to f is C, f 1 The corresponding set of product terms is C 1 ;C contains m product terms, any one of which is defined as p i ;C 1 contains n product terms, any one of which is defined as p k ; Symbol "Θ" represents the disjoint sharp product of two known Boolean logic function product terms; does not appear in the product term; and assume that the logic function corresponding to the original circuit is a single-output logic function The bit corresponding to the subcircuit that needs to be extracted is a single output logic function f 1 =a, then C={0-00,1--1,1-1-}, C 1 ={1---}, m=3, n=1; the spe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More