Deterministic path routing method for tolerating many faults of super-large-scale network-on-chip

A network-on-chip, ultra-large-scale technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve the problems of sacrifice, can not ensure that the NoC has enough available node design requirements, etc., to achieve the effect of small single-hop delay

- Summary

- Abstract

- Description

- Claims

- Application Information

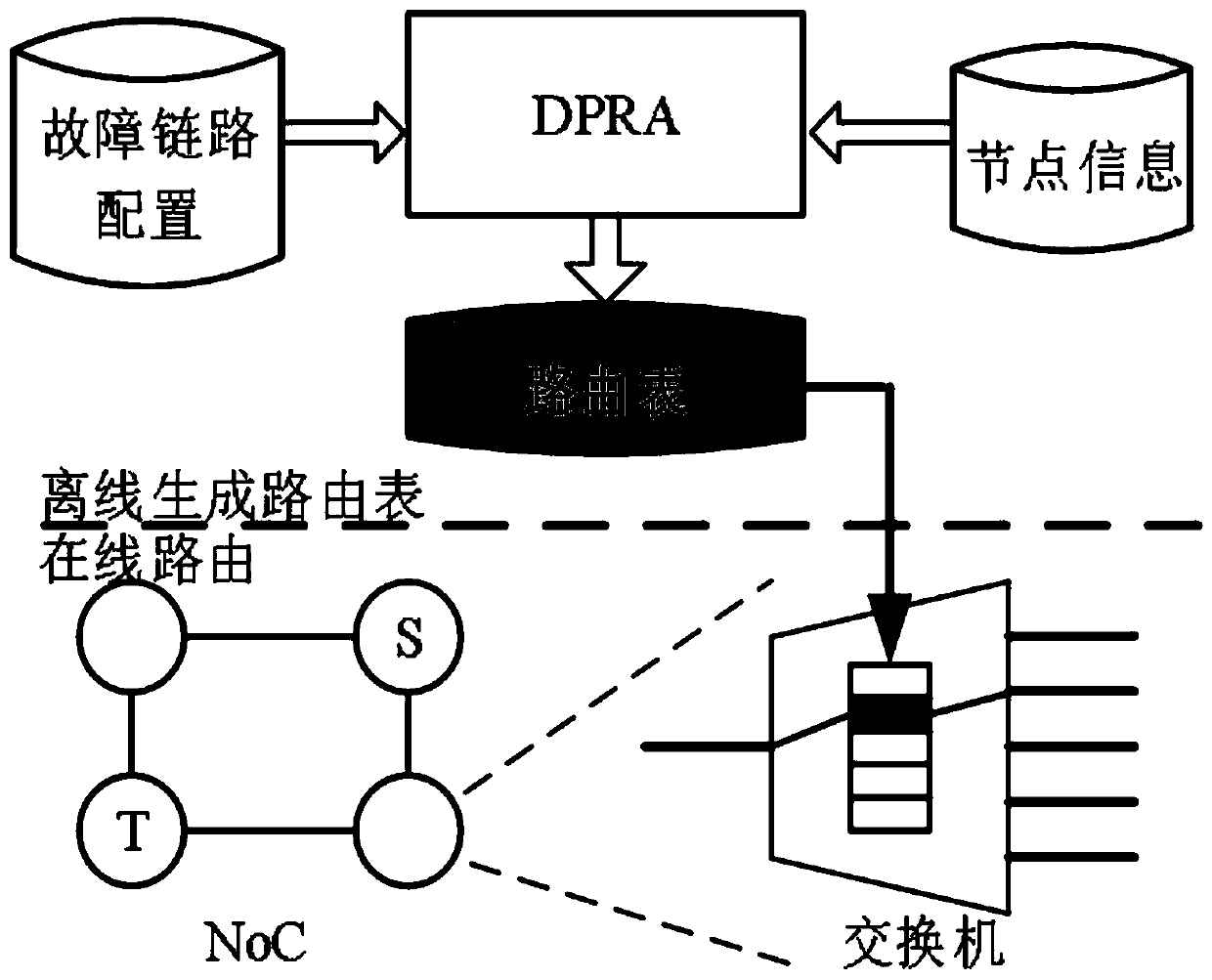

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

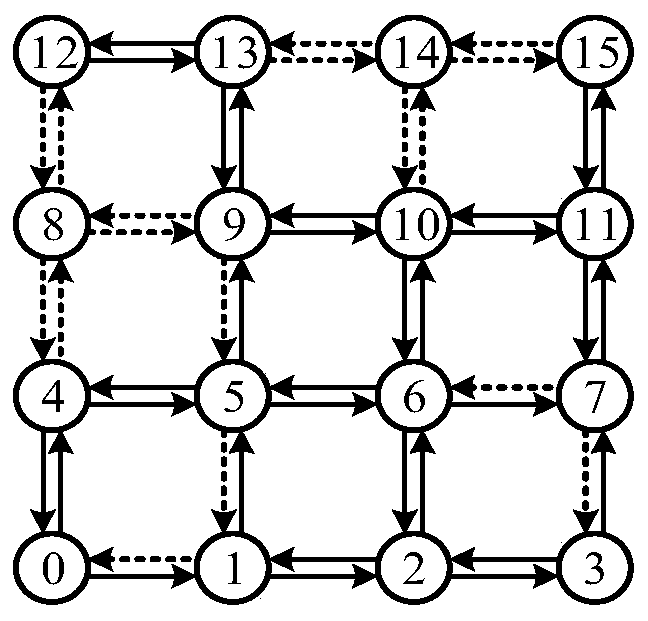

[0057] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments. This embodiment is carried out on the premise of the technical solution of the present invention, and detailed implementation and specific operation process are given, but the protection scope of the present invention is not limited to the following embodiments.

[0058] 1. Relevant definitions and related indicators

[0059] 1. Related definitions

[0060] Network On Chip (Network On Chip, NoC): Network On Chip is a new communication method between IP cores in a system on chip. NoC is an important part of multi-core technology, which brings a new way of thinking to on-chip communication, which is obviously superior to traditional bus-based systems. The NoC-based system is more suitable for the local synchronous global asynchronous clock mechanism in the future multi-core complex SoC design. NoCs address the scalability issues of system-on-c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More