Interrupt delay counting system and method based on FPGA

A counting method and counter technology, which is applied in the computer field, can solve the problems that there is no processing method, and the module that sends the interrupt cannot directly know the length and time required for the host to process the interrupt, so as to achieve strong applicability, portability and enhanced reusability , the effect of highlighting the substantive characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings.

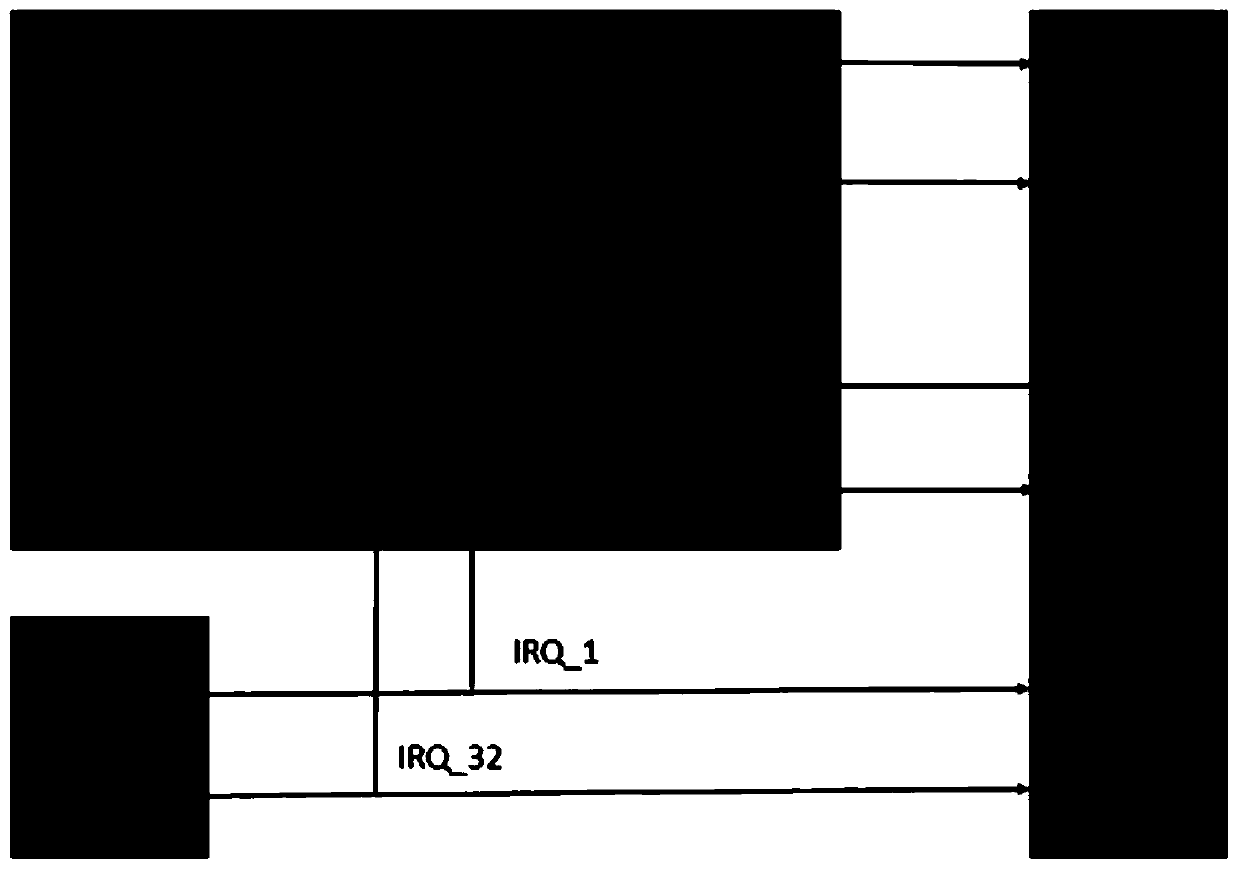

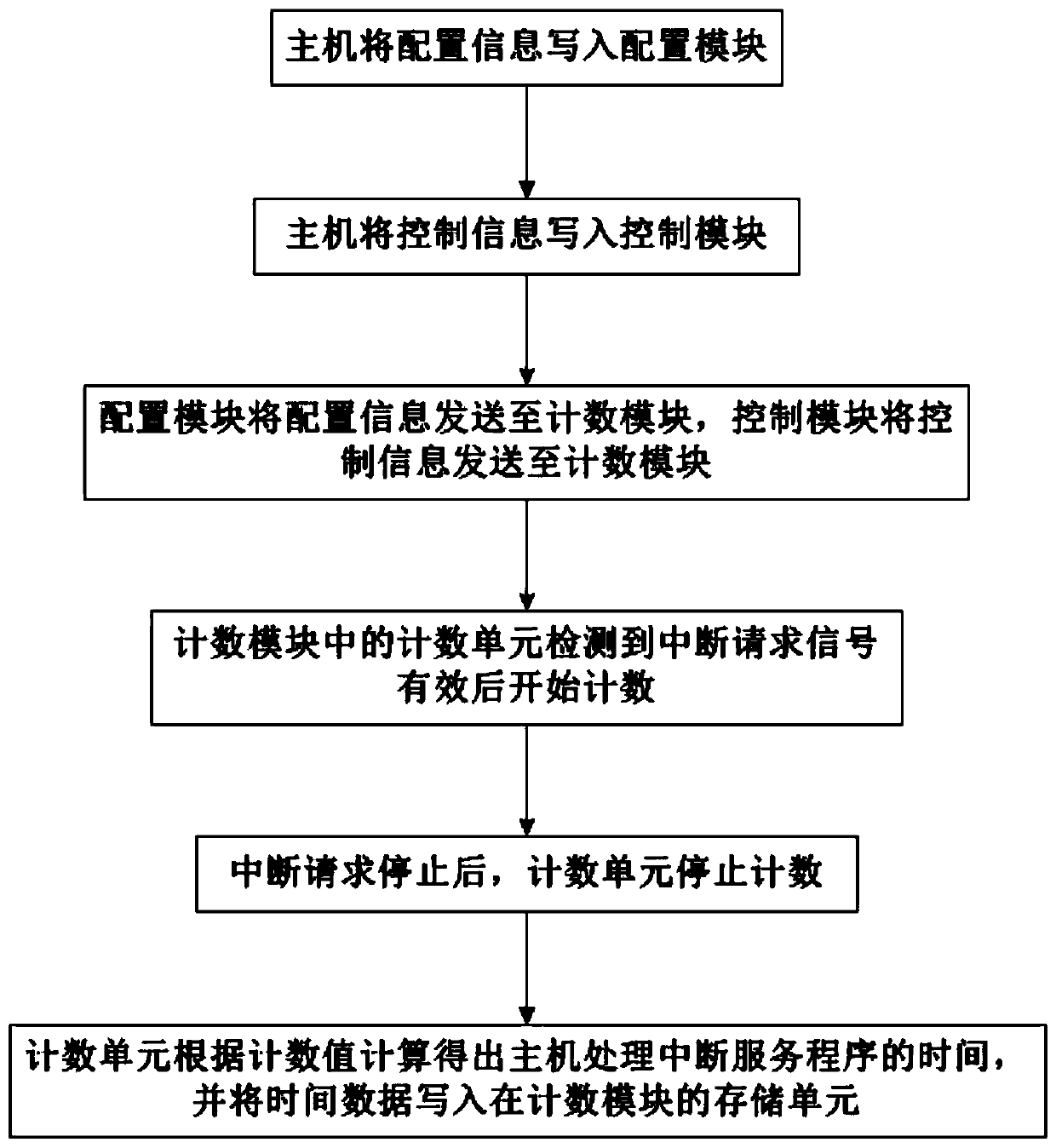

[0033] Such as figure 1 As shown, the present invention provides a FPGA-based interrupt delay counting system, including a host and 32 peripherals, the peripherals respectively send interrupt request signals to the host, and also include an interrupt delay counter, the interrupt delay The counters are connected to the host and peripherals respectively. The interrupt delay counter includes: a configuration module, a control module and a counting module, the configuration module and the control module are respectively connected to the counting module, the configuration module, the control module and the counting module are respectively connected to the host computer, and the counting module is connected to the peripherals. The counting module includes 32 counting units, and each counting unit is respectively connected to a peripheral for receiving an int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More