Dual-channel shared clock trigger delay adjusting device based on PCI bus

A PCI bus, dual-channel technology, applied in the field of dual-channel shared clock trigger delay adjustment devices, can solve the problems of different delay times and errors that cannot be ignored, and achieve the effects of high measurement synchronization accuracy and high delay accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

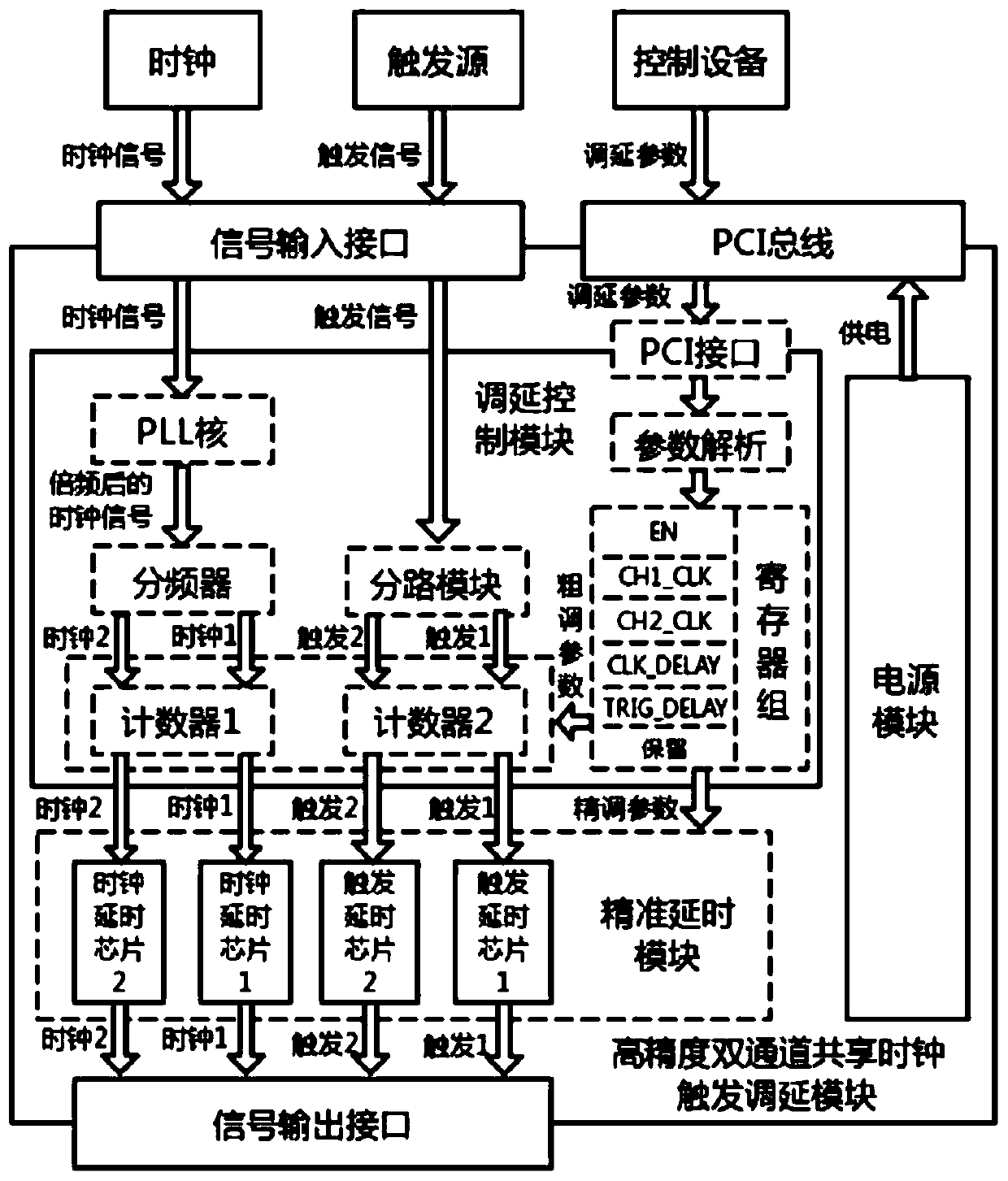

[0033] figure 1 It is a structure diagram of a specific embodiment of a PCI bus-based dual-channel shared clock trigger delay adjustment device of the present invention.

[0034] In this example, if figure 1 As shown, a dual-channel shared clock trigger delay adjustment device based on the PCI bus of the present invention includes: a PCI bus, a power supply module, a signal input interface, a signal output interface, and a delay adjustment control module. system of measurement;

[0035] PCI bus, used to transmit the delay parameters of the control equipment to the device, and supply power to each module in the device;

[0036] The power supply module supplies power to the whole device through the PCI bus;

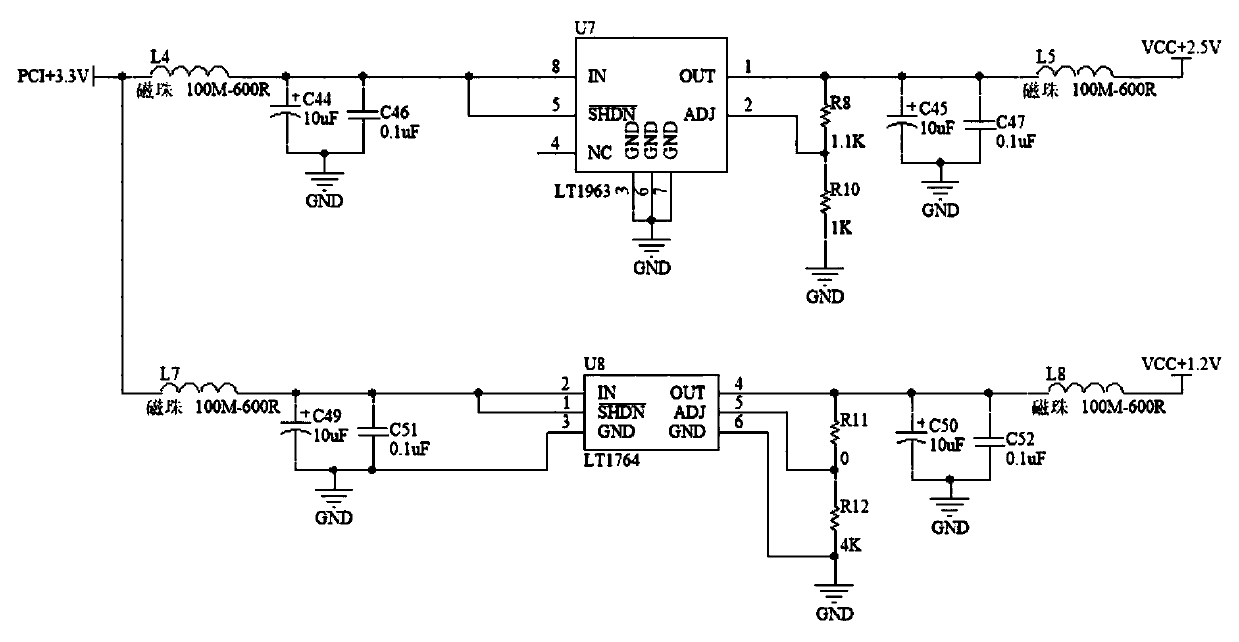

[0037] The PCI bus needs to provide 3.3V, 5V, ±12V power supply for each module, so the power supply module needs to provide 3.3V, 2.5V and 1.2V power supply input. Compared with 2.5V and 1.2V power supply, this embodiment adopts two LDO power supply chips of Linear Tec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More