A Distributed Shared Clock Triggered Delay System

A distributed clock technology, applied in time division multiplexing systems, electrical components, multiplexing communications, etc., can solve problems such as different delay times, errors that cannot be ignored, and large error gaps, and achieve high measurement synchronization accuracy. , the effect of high delay precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

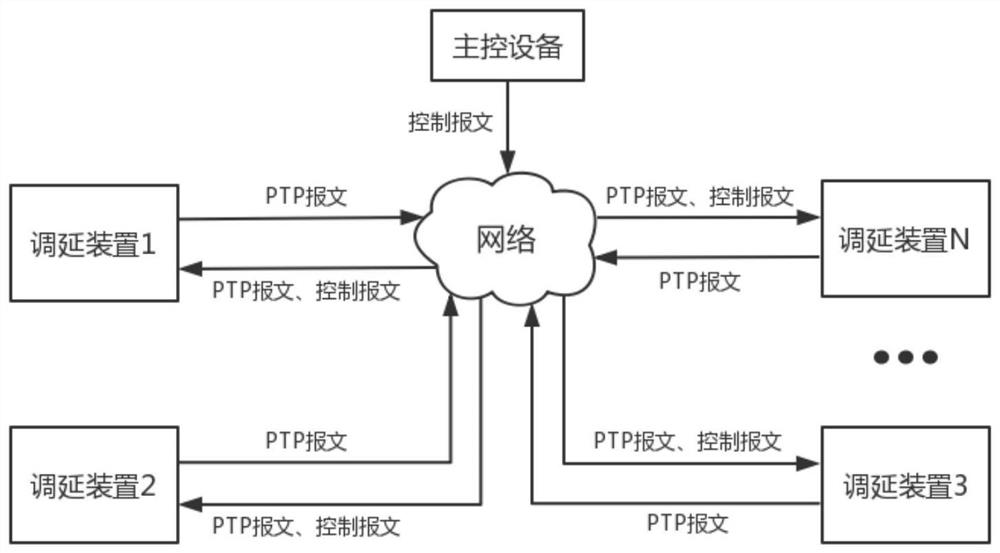

[0048] figure 1 It is a structure diagram of a specific implementation mode of a distributed shared clock trigger delay adjustment system of the present invention.

[0049] In this example, if figure 1 As shown, a distributed shared clock trigger delay adjustment system of the present invention includes: a main control device, a plurality of dual-channel shared clock trigger delay adjustment devices, and a master control device connected to multiple dual-channel shared clock trigger delay adjustment devices local area network;

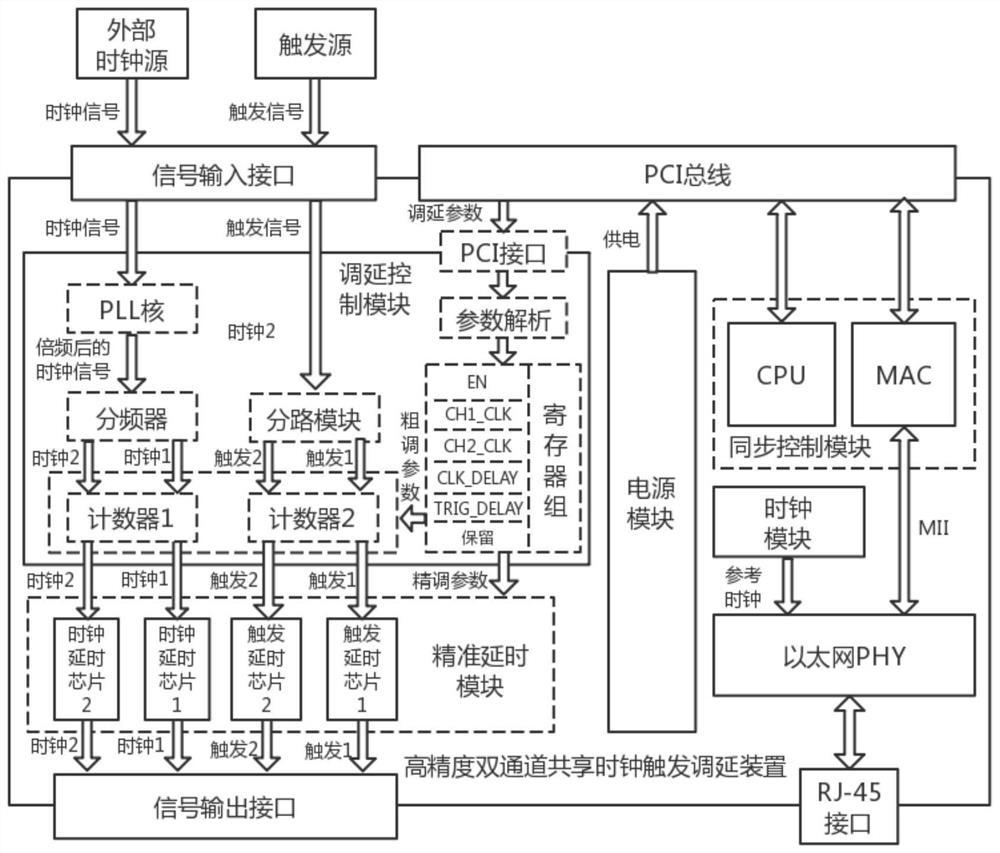

[0050] Among them, such as figure 2 As shown, the dual-channel shared clock trigger delay adjustment device includes the following components:

[0051] The PCI bus is used to realize the data transmission between the master control device and the dual-channel shared clock trigger delay adjustment device, and to supply power to each module in the device;

[0052] The power supply module supplies power to the whole device through the PCI bus;

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More