Method and system for testing system-on-chip chip

A system-on-chip and test method technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of cable signals interfering with each other, signal integrity, limiting test frequency, etc., to improve test efficiency, simplify connection methods, Guaranteed effect of accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

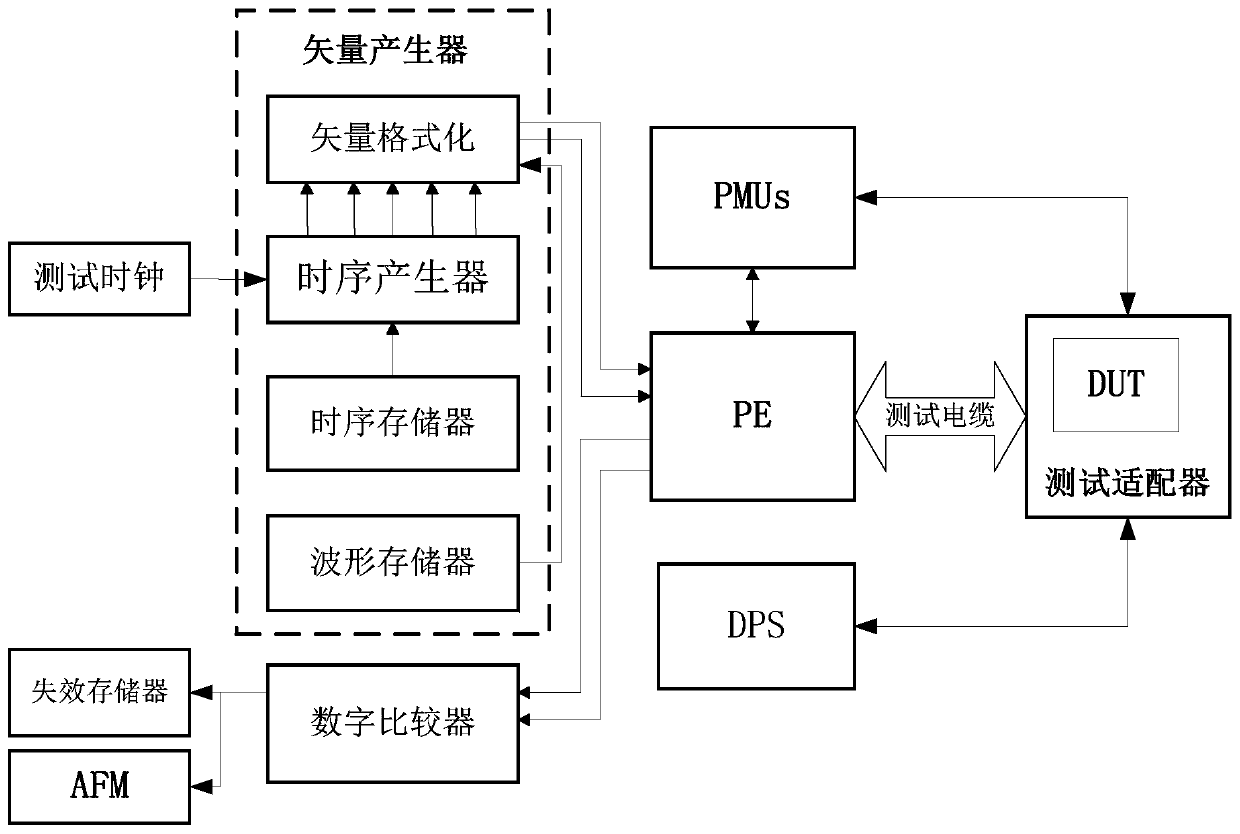

[0052] The technical content of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

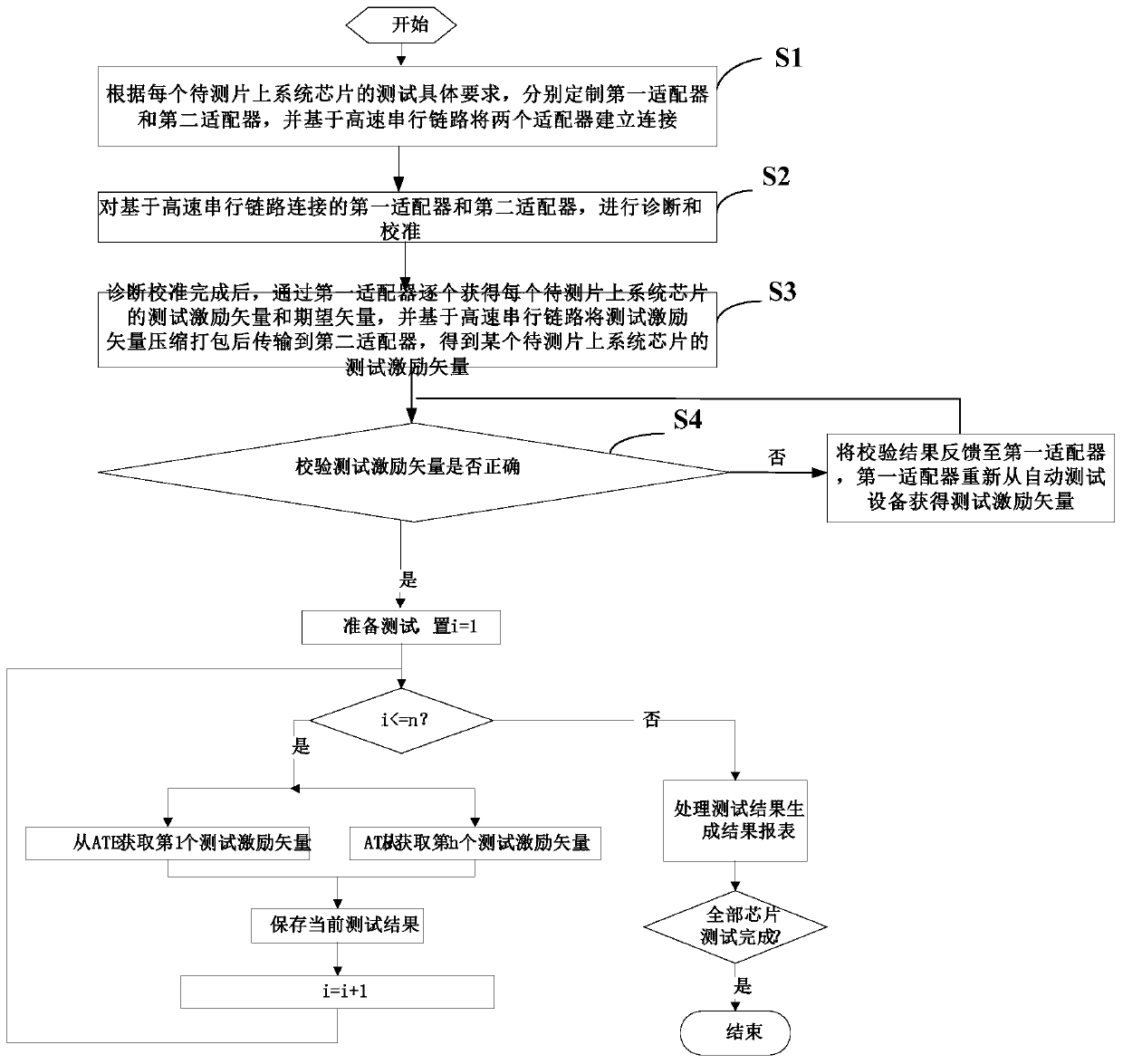

[0053] Such as figure 2 As shown, the testing method of the SoC chip provided by the present invention comprises the following steps:

[0054] Step S1: According to the test specific requirements of each SoC to be tested, respectively customize the first adapter and the second adapter, and establish a connection between the two adapters based on a high-speed serial link.

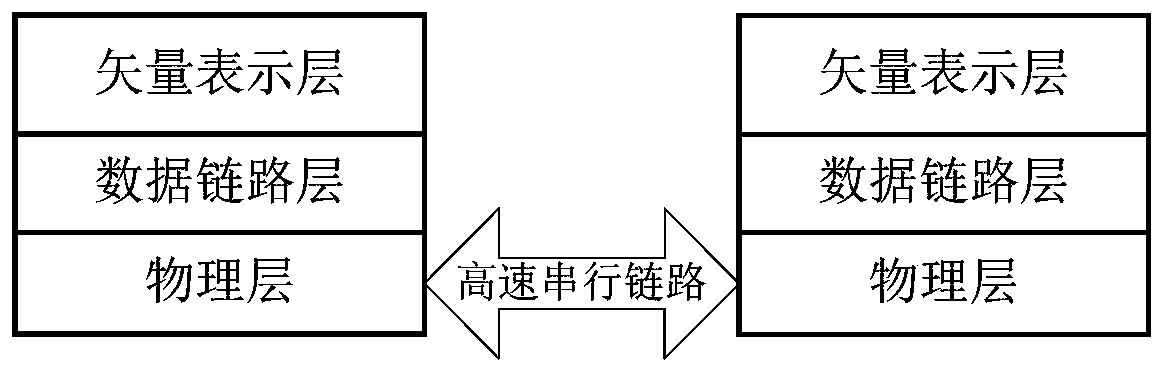

[0055] Wherein, both the first adapter and the second adapter are customized high-speed serial link adapters based on the specific test requirements of the high-speed serial link and the system-on-chip to be tested. Specifically, the first adapter is a vector serialization compression adapter installed at the integrated circuit automatic test equipment (AutomaticTestEquipment, ATE) end; the second adapter is a vector deserialization decomp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More