A high speed parallel data receiving system based on clock driver and fpga

A receiving system and driver technology, applied in electrical digital data processing, radio wave measurement systems, instruments, etc., can solve the problems of high quantization bits of RF ADC chips, large data bandwidth, and inability to reliably achieve data reception.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

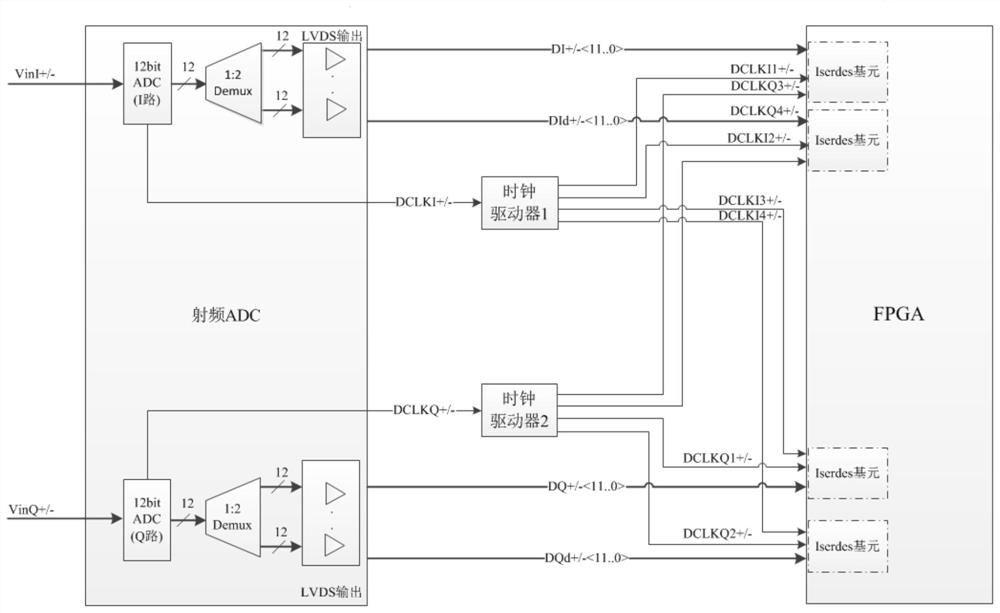

[0022] Such as figure 1 As shown, a high-speed parallel data receiving system based on a clock driver and an FPGA provided by the present invention includes a radio frequency ADC, a clock driver 1, a clock driver 2, and an FPGA.

[0023] The maximum sampling frequency of the RF ADC is 1.6GHz, the number of quantization bits is 12bit, and supports single-channel 1:1, 1:2 and 1:4 LVDS output under double-channel interleaved sampling.

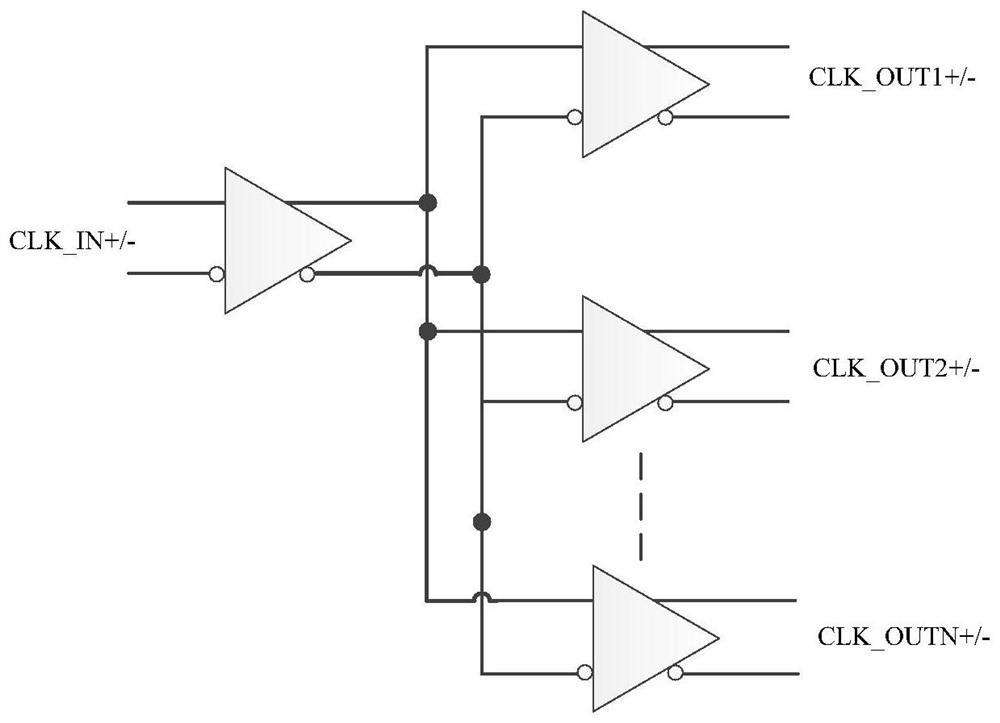

[0024] Clock driver 1 and clock driver 2 have optional dual differential clock inputs and up to 10 differential clock outputs.

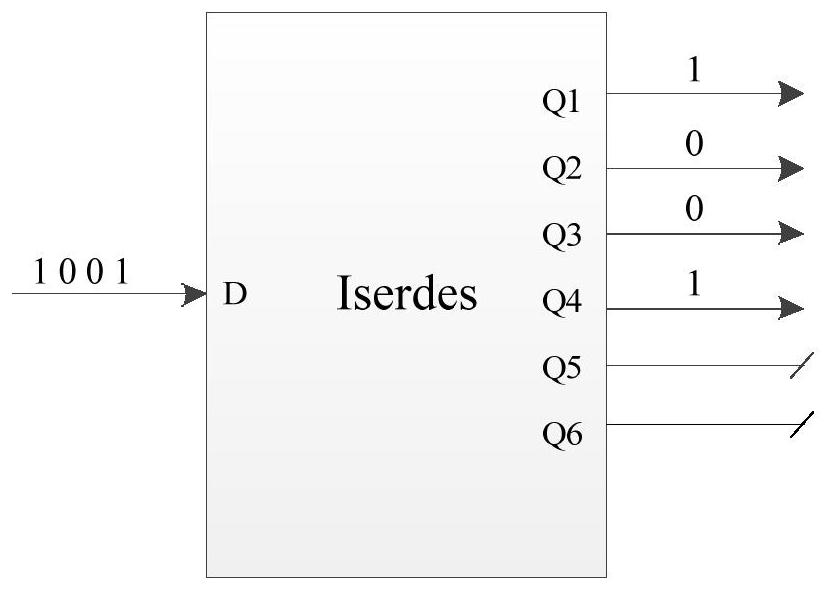

[0025] FPGA (U4) has an Iserdes (input serial-to-parallel converter) primitive, which realizes serial data input and parallel data output.

[0026] The RF ADC is a dual-channel, high-performance analog-to-digital converter, and the quantized output adopts the LVDS method, such...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap