Hardware SAT solver for multi-thread parallel execution

A multi-threaded, solver technology, applied in the computer field, can solve the problems of lack of fast memory and high overhead, and achieve the effect of high solving success rate, avoiding time overhead, and reducing resource overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0040] The hardware SAT solver of a kind of multi-thread parallel execution of the present invention adopts FPGA technology to realize, and all data of the solver are all stored in the on-chip memory of FPGA, have avoided because the time overhead that reads off-chip data brings, can reach Maximum performance. At the same time, the multi-thread strategy is used to greatly reduce the resource overhead of the on-chip memory, and the total turnover per second is doubled, and the solution success rate is high.

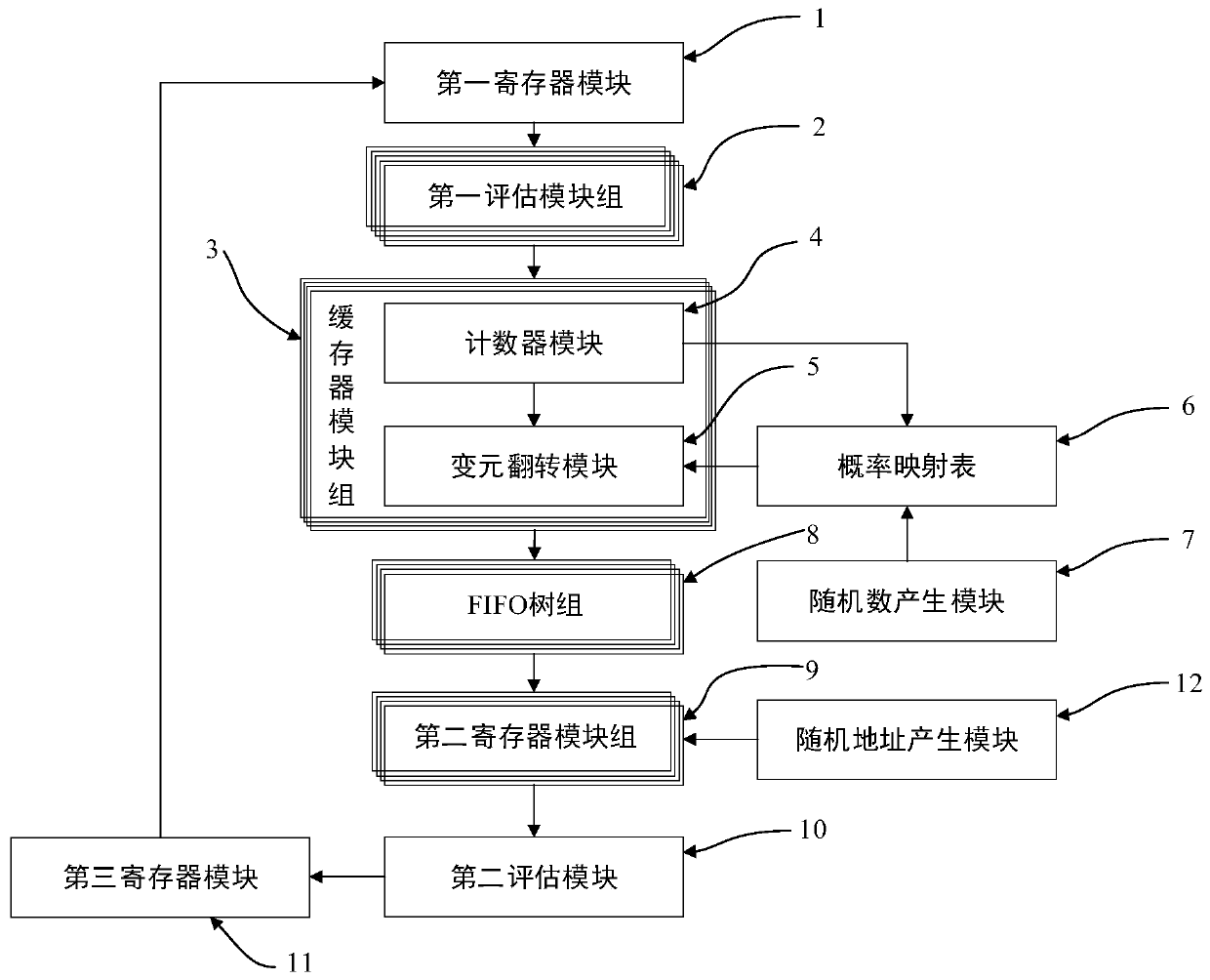

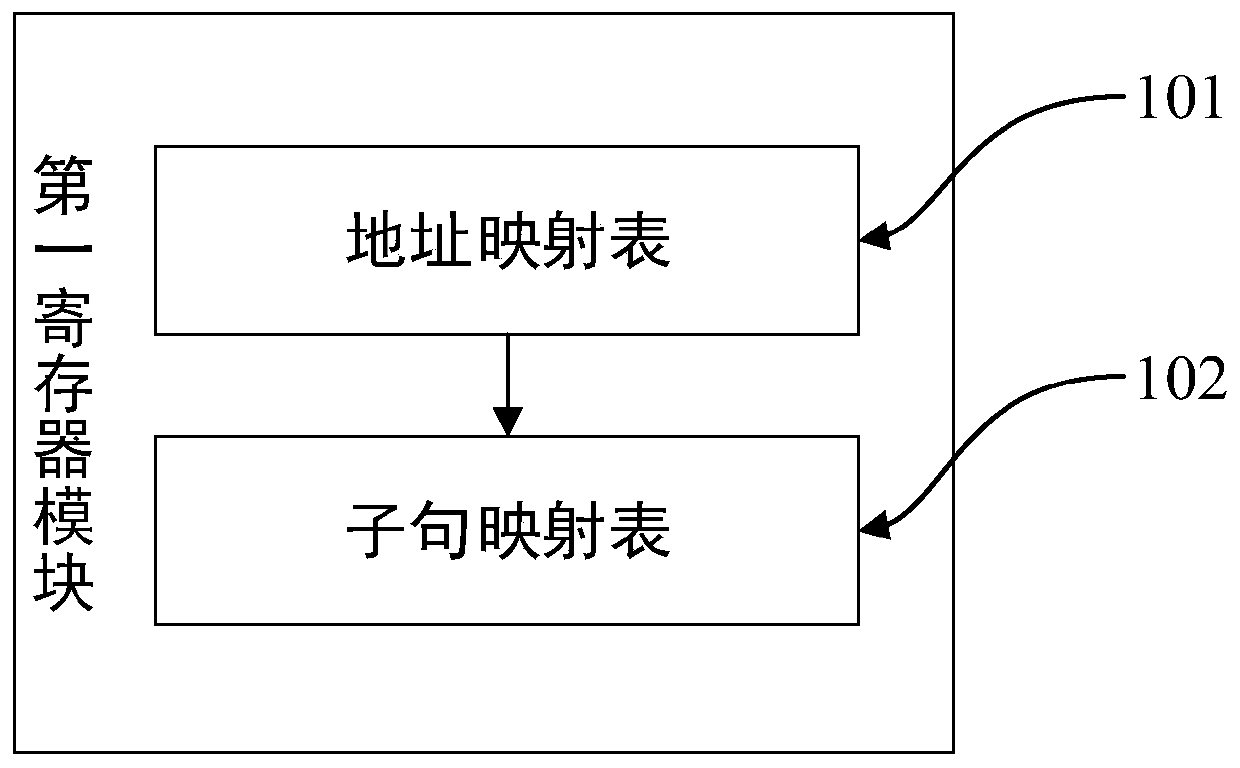

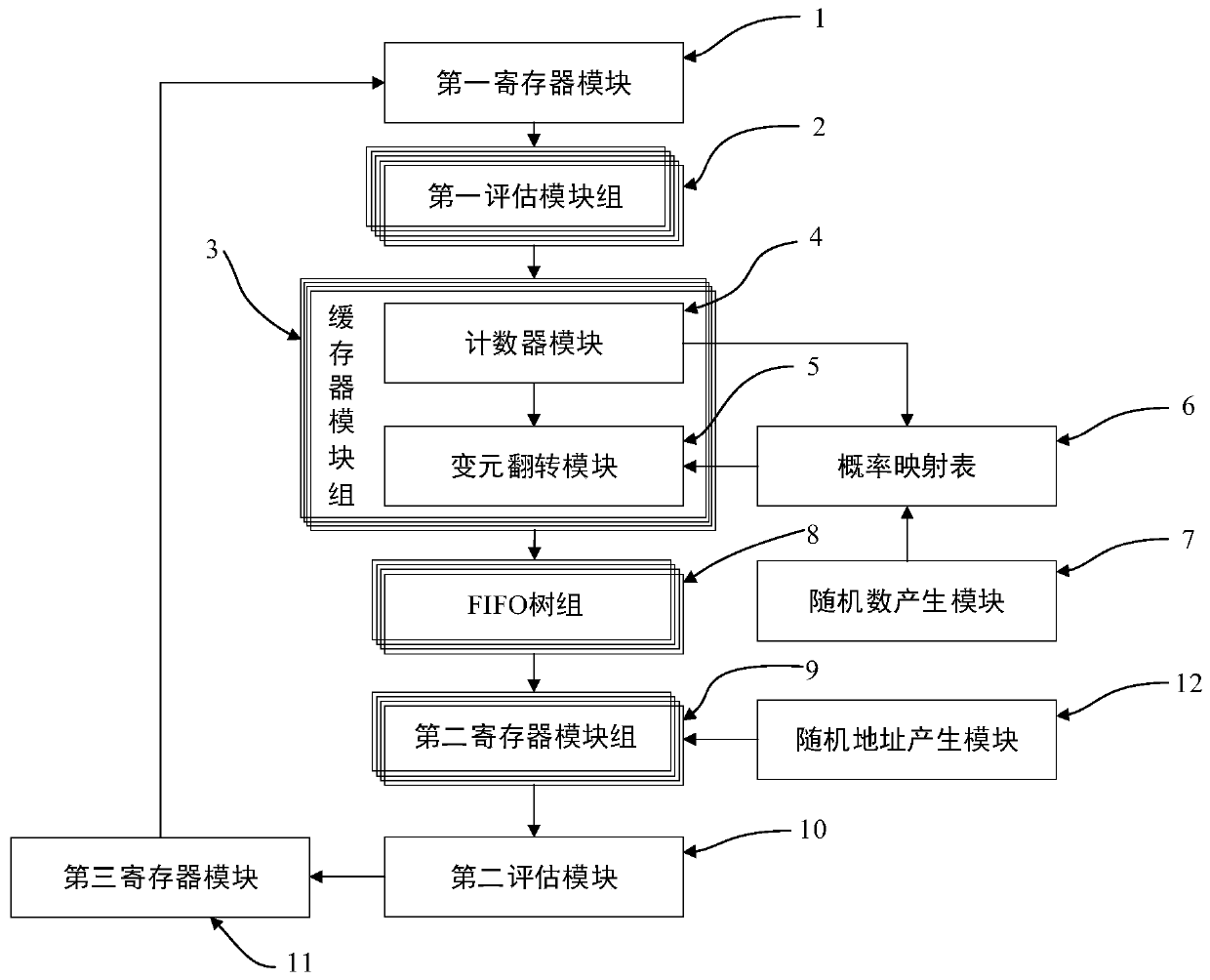

[0041] In an optional embodiment, the present invention provides a structure of a hardware SAT solver executed in parallel by multiple threads, such as figure 1 As shown, it includes a f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More