Cache design method and cache design device for parallel double channels

A design method and dual-channel technology, applied in the direction of machine execution device, program control design, concurrent instruction execution, etc., can solve the problems of limiting the parallel execution of storage instructions and the low efficiency of processor out-of-order execution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

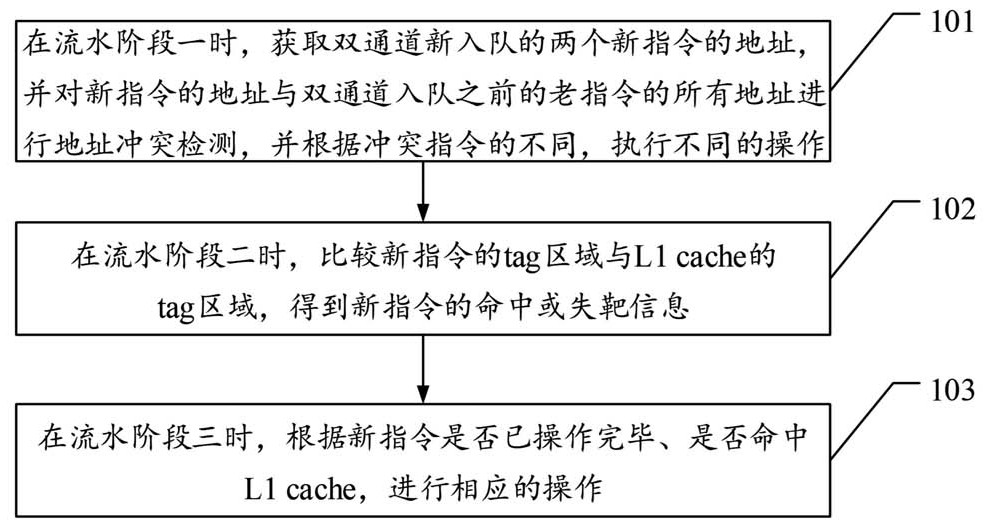

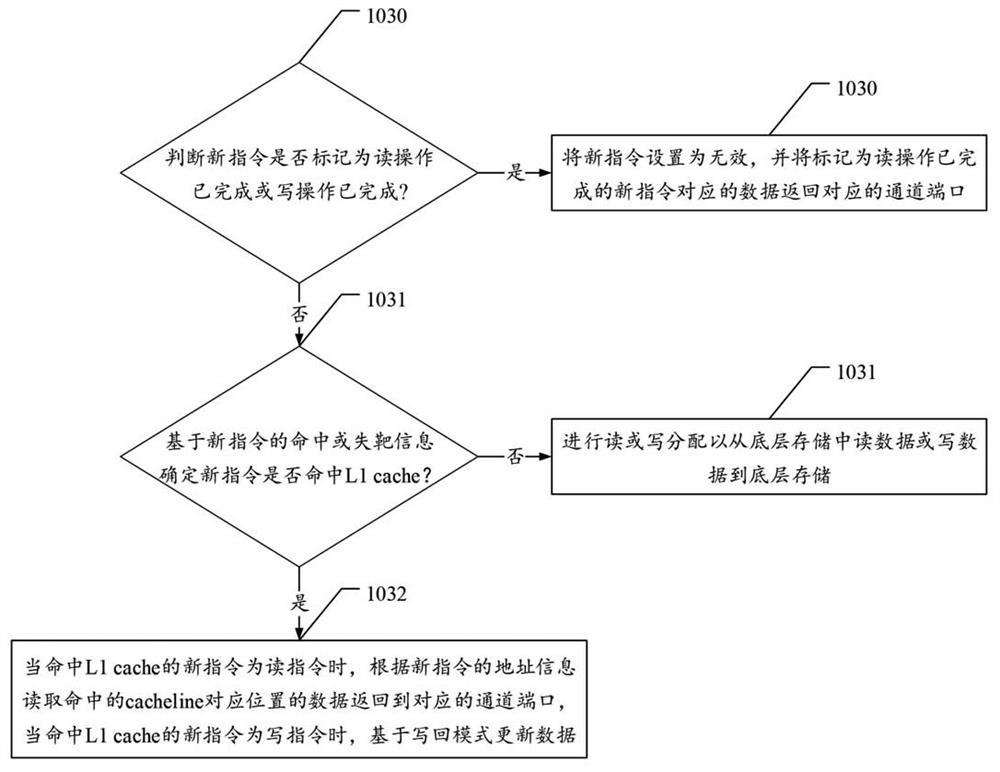

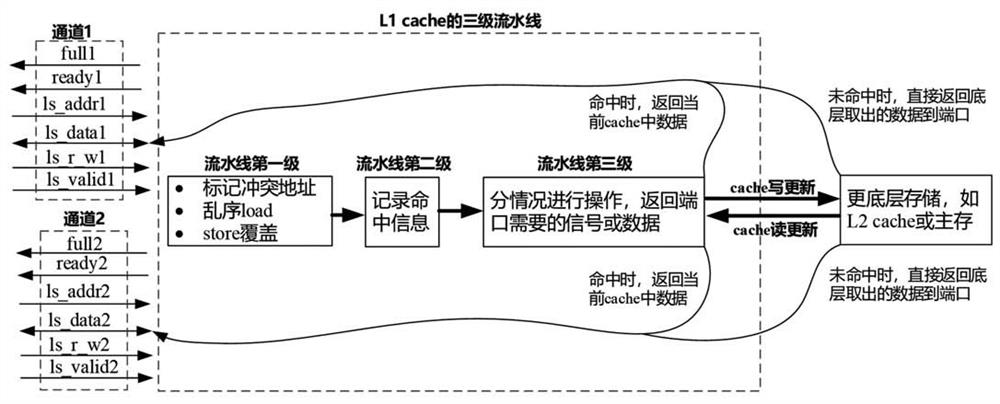

[0056] The present application provides a parallel dual-channel cache design method and device, which is used to solve the problem that in the existing single-channel cache design, the read or write instructions share one storage channel, which limits the parallel execution of storage instructions and causes the processor to execute out of order The technical problem of lower efficiency.

[0057] In order to enable those skilled in the art to better understand the solution of the present application, the technical solution in the embodiment of the application will be clearly and completely described below in conjunction with the accompanying drawings in the embodiment of the application. Obviously, the described embodiment is only It is a part of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More