Patents

Literature

76results about How to "Short transmission delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

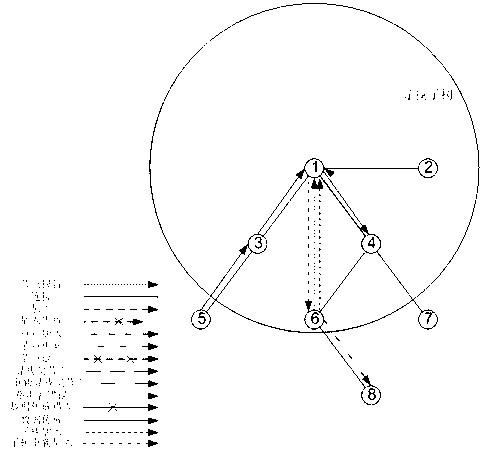

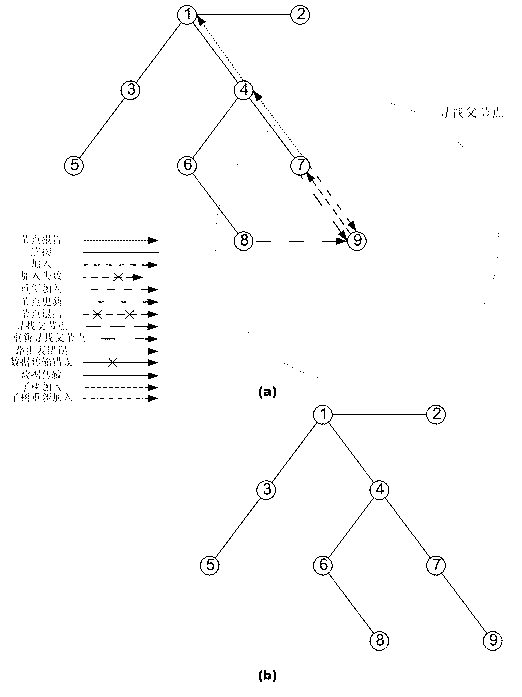

Dynamic self-organizing hierarchical routing method applied to wireless sensor network

ActiveCN102711209ASend back reliablyAlleviate the problem of excessive consumptionNetwork topologiesReliable transmissionWireless mesh network

The invention relates to a dynamic self-organizing hierarchical routing method. The method is applied to the tree topology structure of a wireless sensor network, the problems of path failure and data transmission incapability due to node mobility or failure are solved, and the topology structure of the network can be dynamically regulated. The network is established by adopting a multi-branch-tree-based topology structure, and each node maintains a routing table of one level, and records a sub-tree topology structure taking the node as a root. The routing table is effectively updated by inserting a sequence number during node access application, so that the problems of repeated node numbers in the routing table of upper-level nodes are solved. Only when data cannot be transmitted, the routing tables reorganize the topology structures, and timely maintain the topology structures in the network, so that energy overhead, computing overhead and data transmission real-time performance are combined, the reliable transmission of the data is ensured, the overhead is reduced, and the advantages of a routing protocol and a routed protocol are utilized.

Owner:GUANGZHOU HKUST FOK YING TUNG RES INST

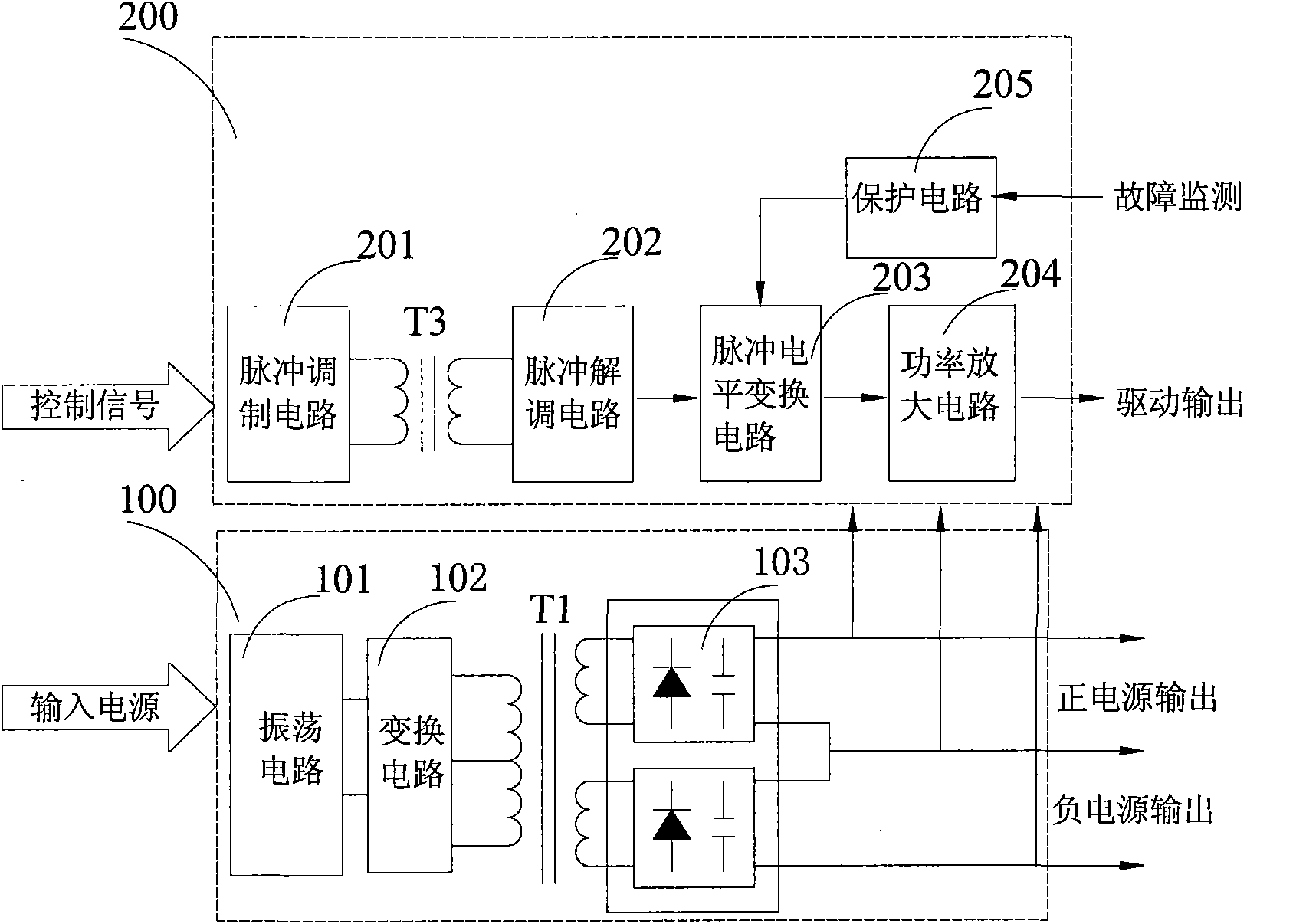

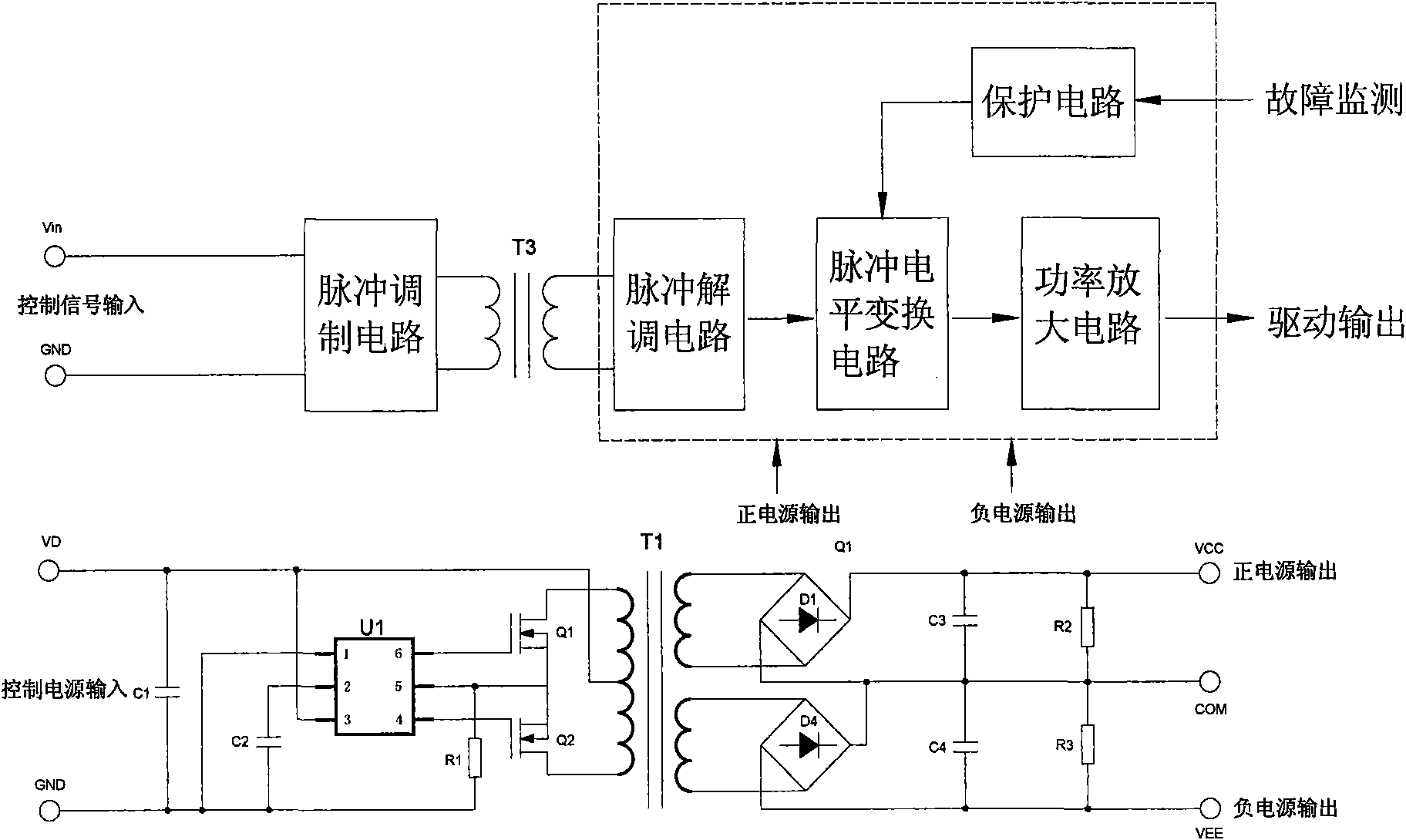

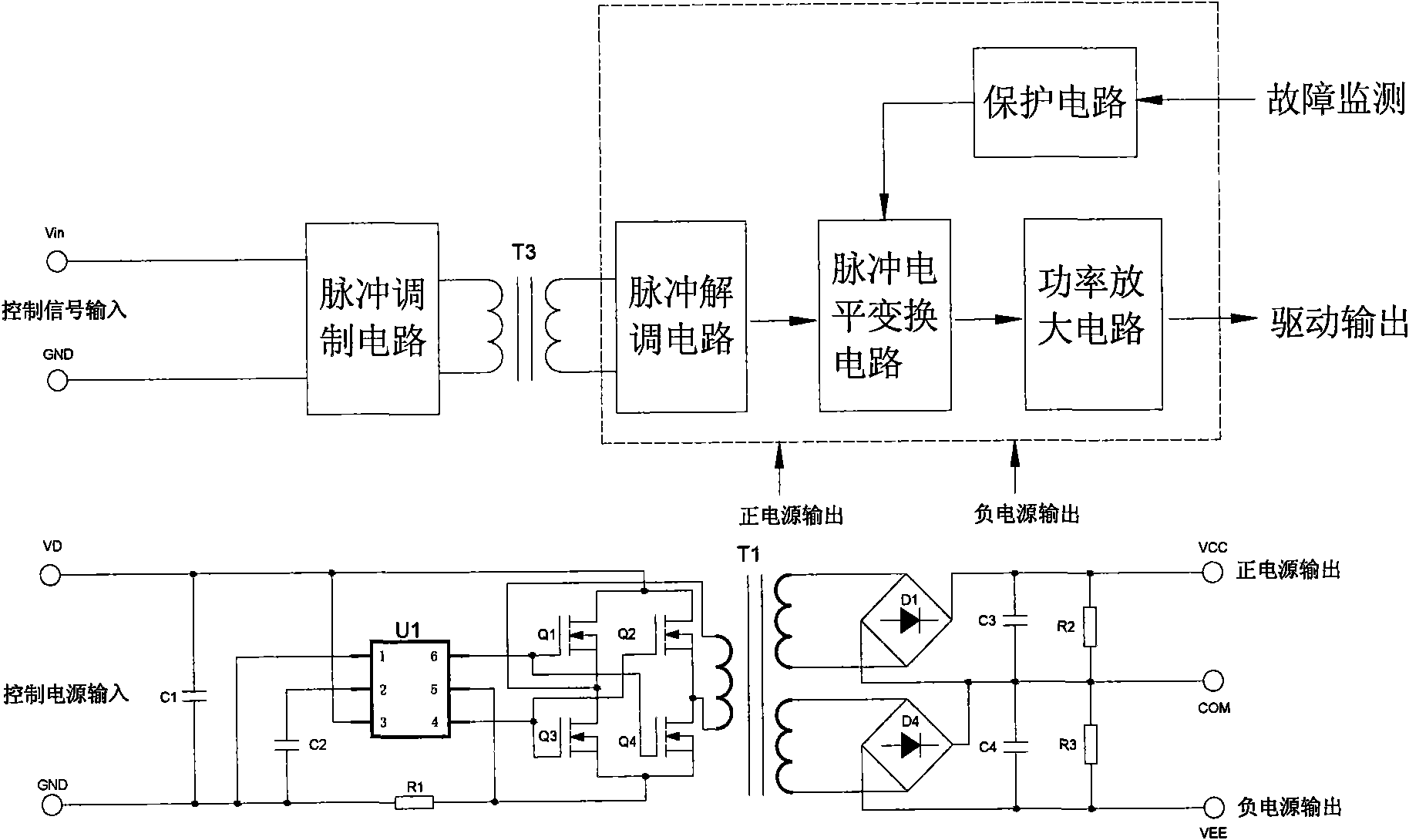

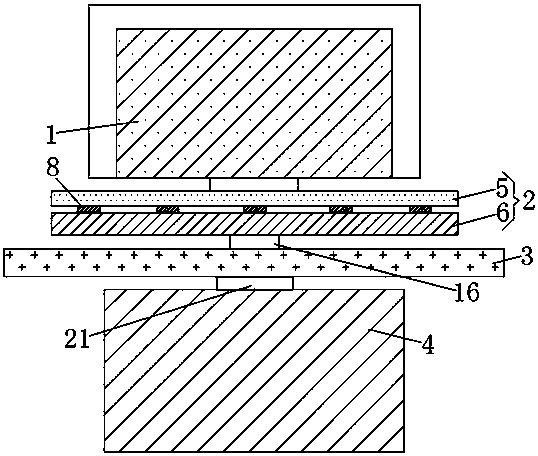

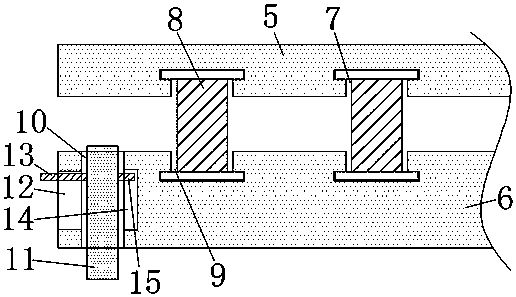

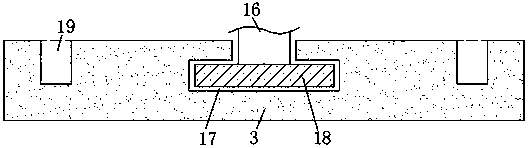

IGBT driving circuit embedded with isolating source

ActiveCN101640526AReduce stray inductanceImprove reliabilityElectronic switchingApparatus with intermediate ac conversionTransformerPush pull

The invention discloses an IGBT driving circuit embedded with an isolating source, comprising a power supply circuit and a driving circuit; wherein the power supply circuit sequentially comprises an oscillating circuit in charge of producing a push-pull driving signal, a transforming circuit which comprises at least one pair of switch tube and realizes energy transformation by alternate on / off according to the push-pull driving signal, a power transformer in charge of transmitting energy from the primary winding thereof to the secondary winding and a rectifying filtering circuit in charge of independent rectifying filtering on the secondary winding of the power transformer in two paths, wherein a common terminal is led out to realize positive and negative power supply output, so as to supply power to the driving circuit. A high-efficiency DC / DC isolating converter and the IGBT driving circuit are integrated, thus saving an outdoor isolating source and being convenient for application of a driver; and the invention is easy to be realized by adopting hybrid integrated thick film circuit, thus being beneficial to adopting SIP encapsulation and saving PCB area.

Owner:MORNSUN GUANGZHOU SCI & TECH

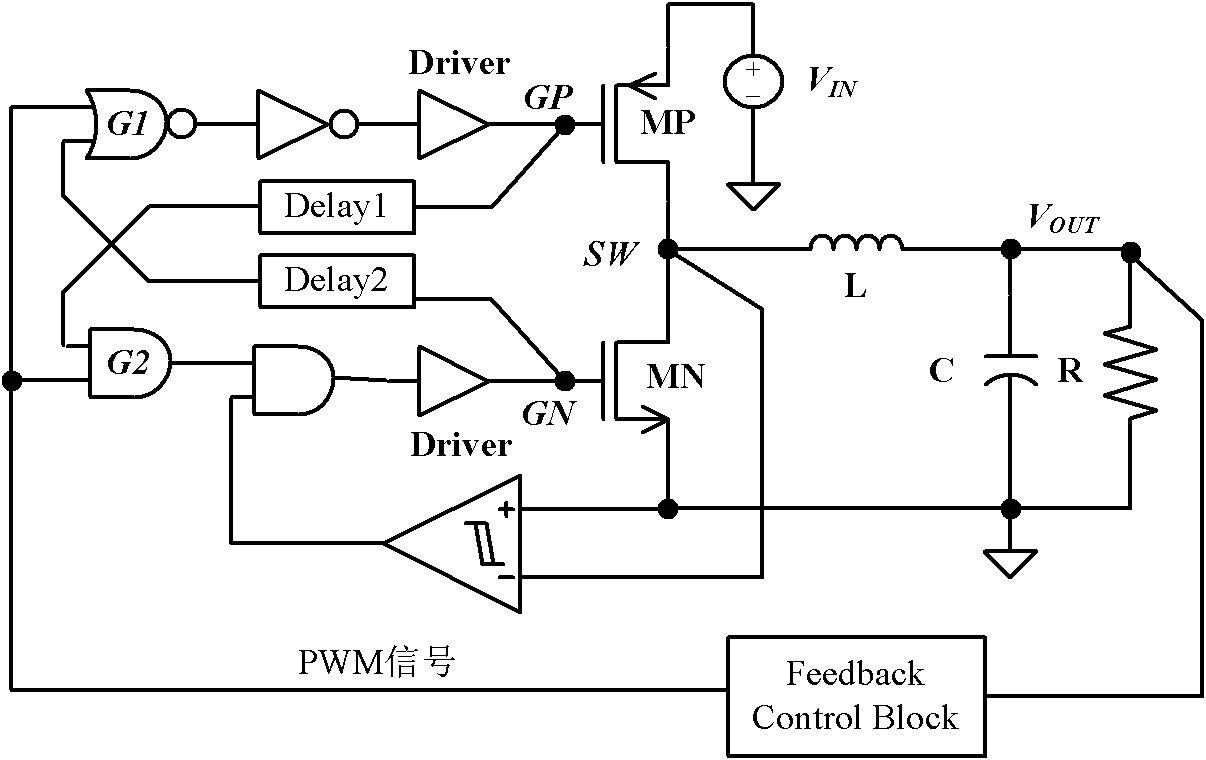

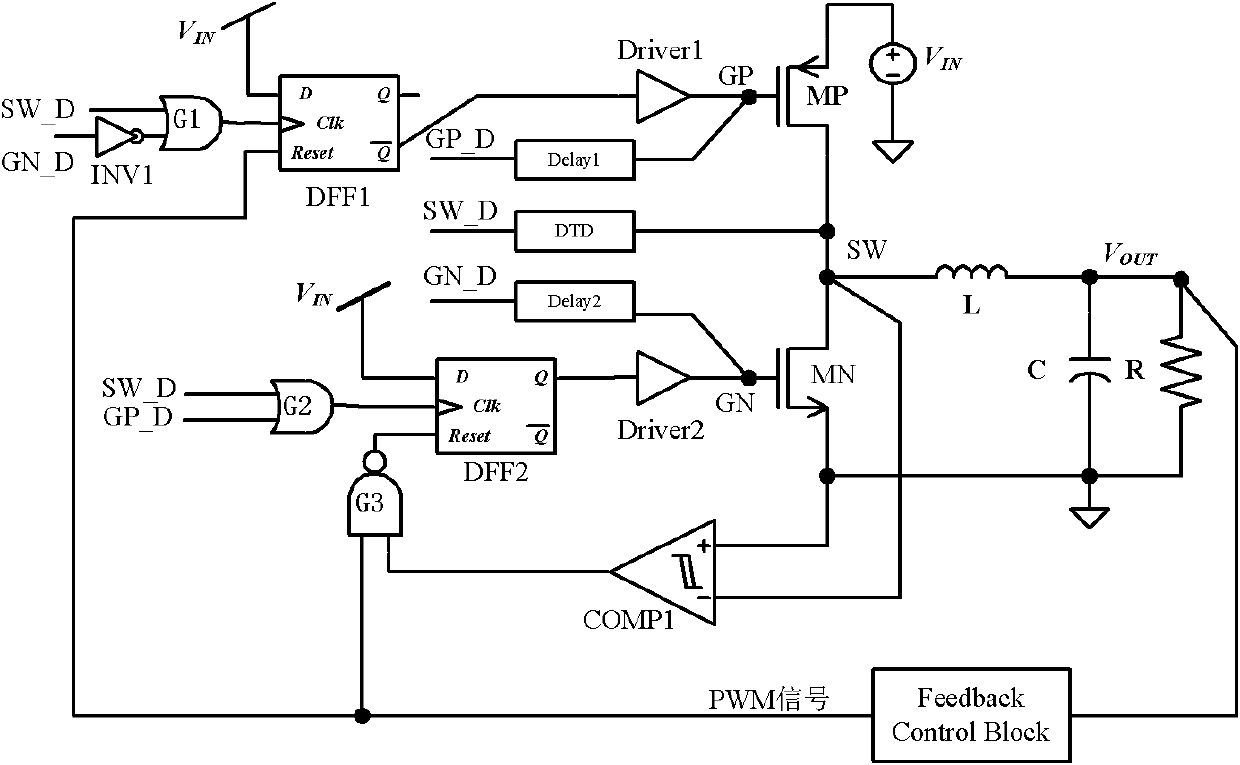

A dead time control circuit used in a DC-DC converter

ActiveCN102170228AShort transmission delaySmall sizeDc-dc conversionElectric variable regulationDc dc converterReverse recovery

The invention discloses a dead time control circuit used in a DC-DC converter. In allusion to unnecessary power loss brought by conduction loss and reverse recovery in the DC-DC converter, the dead time control circuit used in the DC-DC converter enables a body diode conduction to be detected quickly along the two edges of PWM signal through a dead time detector, thereby turning off a power tube or a rectifying tube to make the body diode conduction time be reduced to be close to the transmission delay time of a drive unit, reducing the power loss brought by the body diode conduction substantially and improving efficiency substantially. The improved efficiency brought by employing the structure enables a higher switch frequency to be feasible, thereby reducing the size of a passive device. Moreover, the circuit of the invention can adjust the dead time adaptively in accordance with different load currents.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

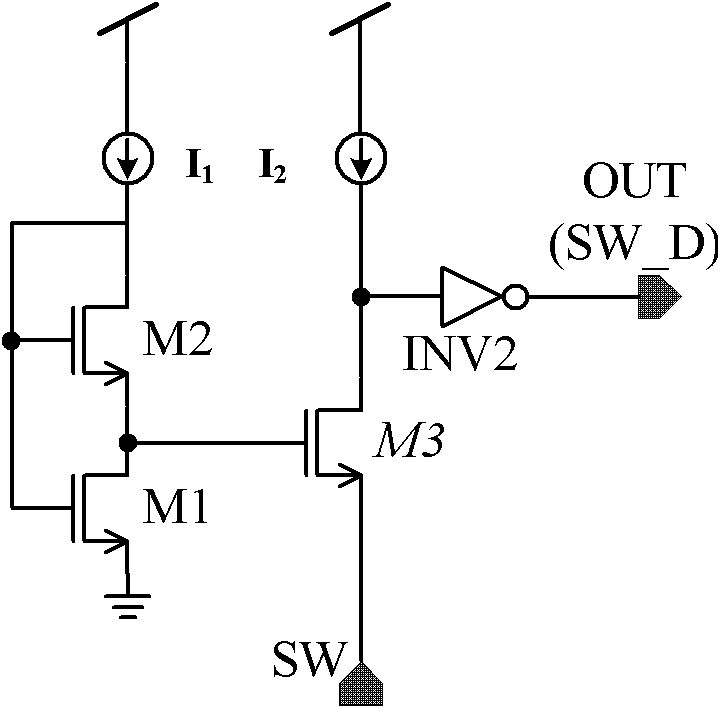

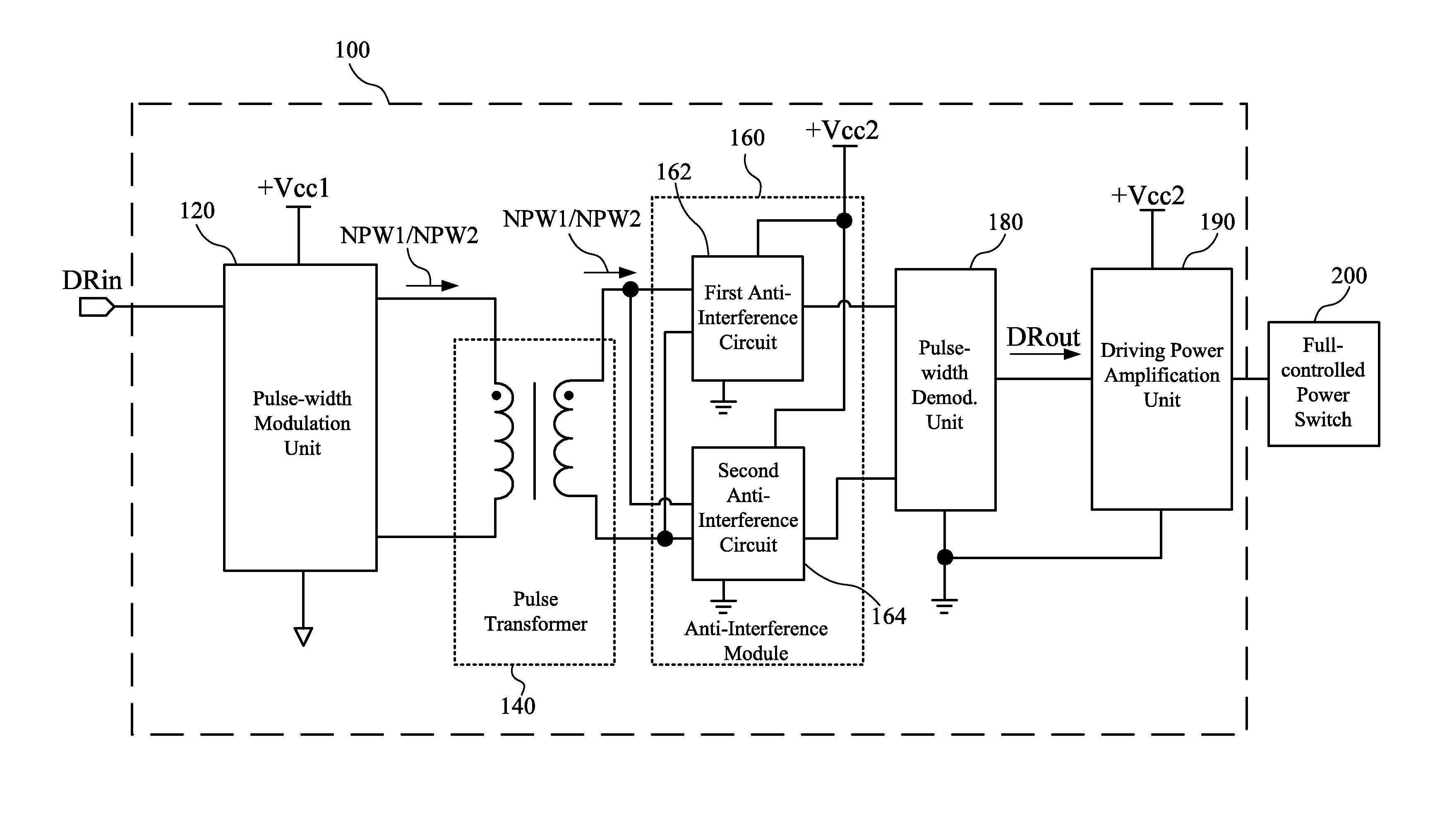

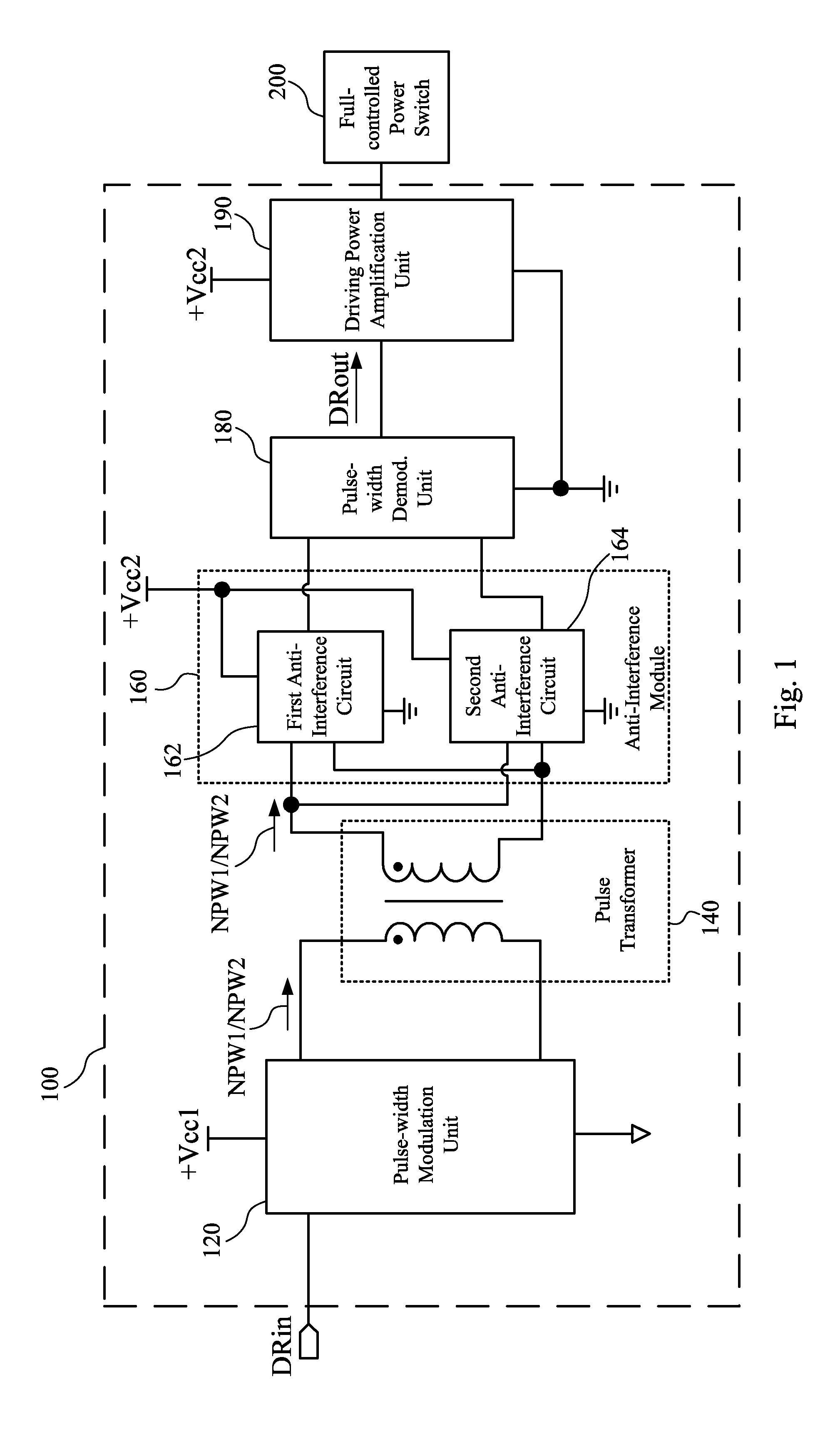

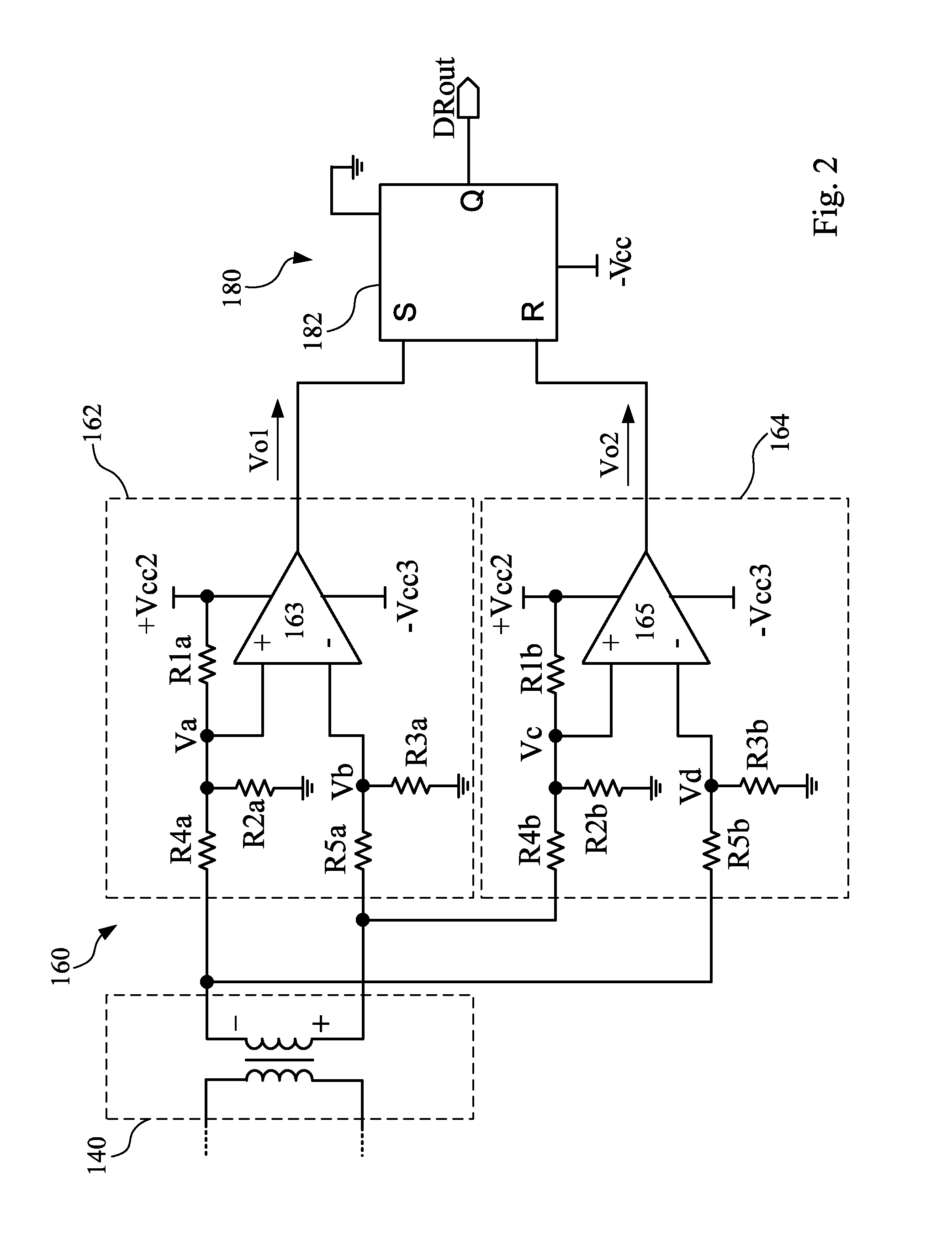

Switch driving circuit

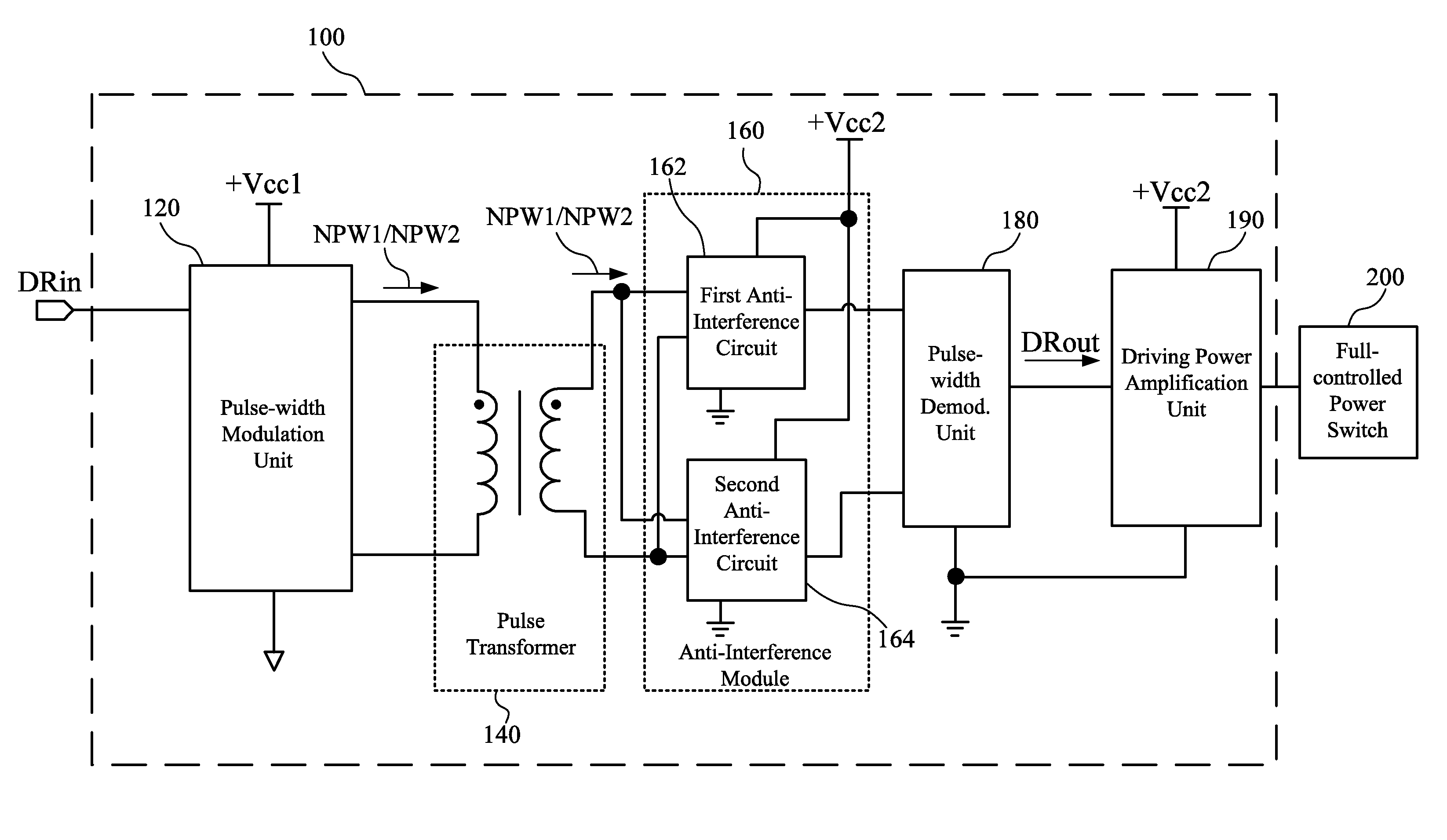

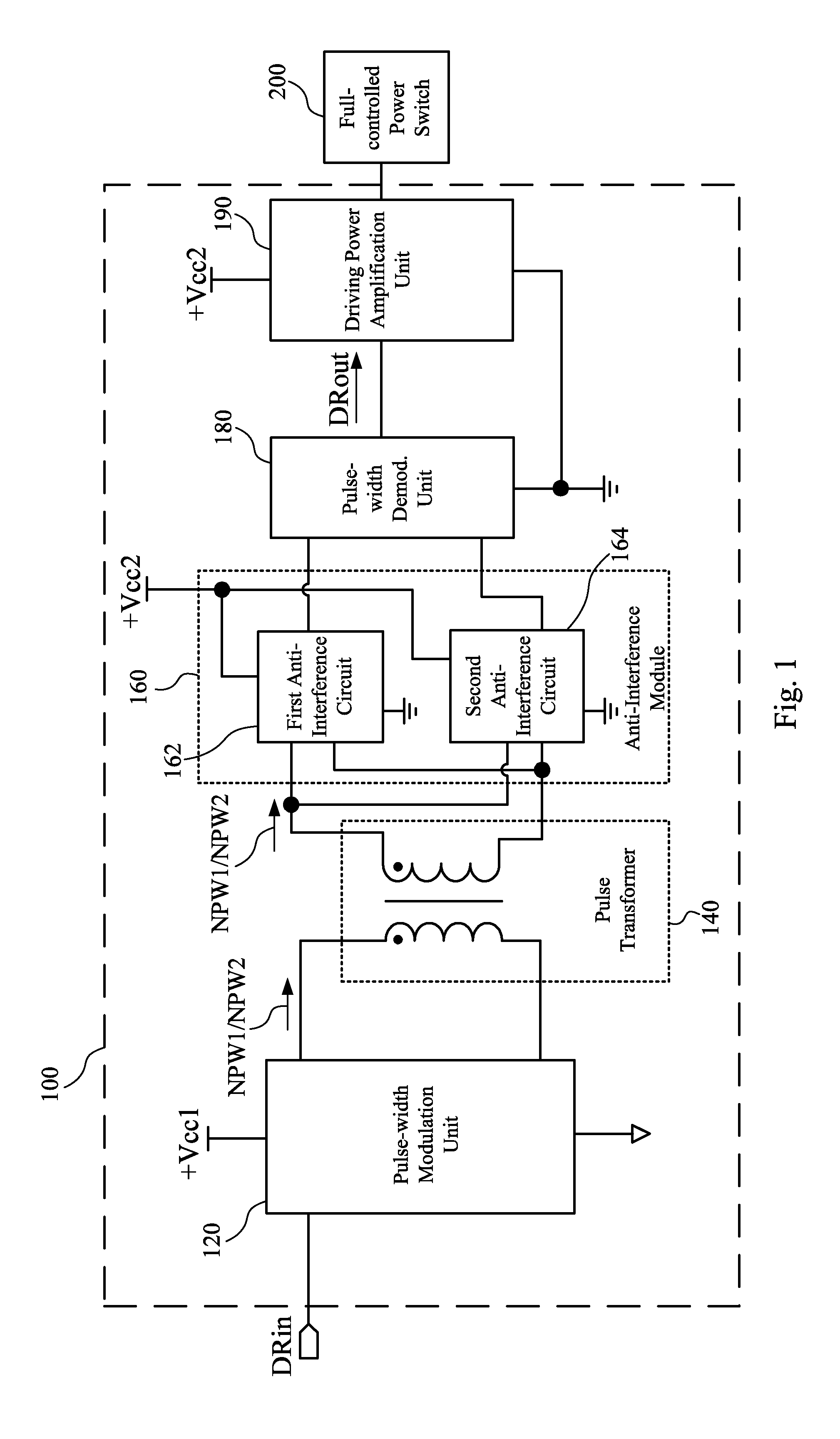

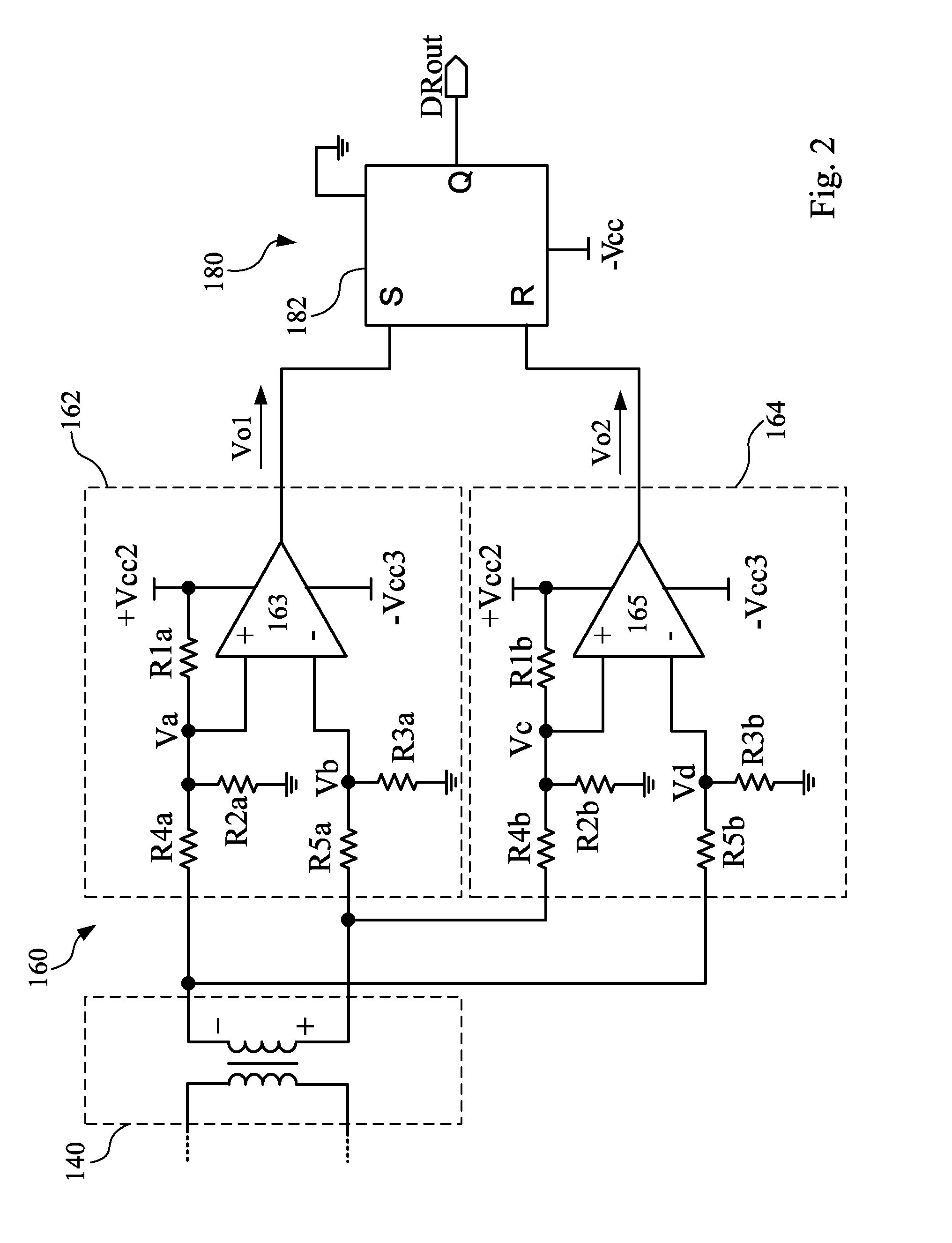

ActiveUS20140055172A1Short transmission delayImprove anti-interference abilityElectronic switchingElectric pulse generatorControl powerAudio power amplifier

A switch driving circuit for driving a full-controlled power switch is disclosed, including a pulse-width modulation unit, a pulse transformer, an anti-interference module, a pulse-width demodulation unit and a driving-power amplifier. The pulse-width modulation unit converts a driving input signal into a positive-negative narrow pulse-width signal. The anti-interference module is coupled to the secondary side and the positive-negative narrow pulse-width signal includes multiple positive pulses and negative pulses. The anti-interference module filters out the ones from the positive pulses and negative pulses of which the pulse amplitude does not reach an effective threshold, and meanwhile the anti-interference module suppress a common-mode noise caused by a high voltage transient variation at a moment when the full-controlled power switch is turned on or off. The pulse-width demodulation unit converts the filtered positive-negative narrow pulse-width signal into a driving output signal.

Owner:DELTA ELECTRONICS INC

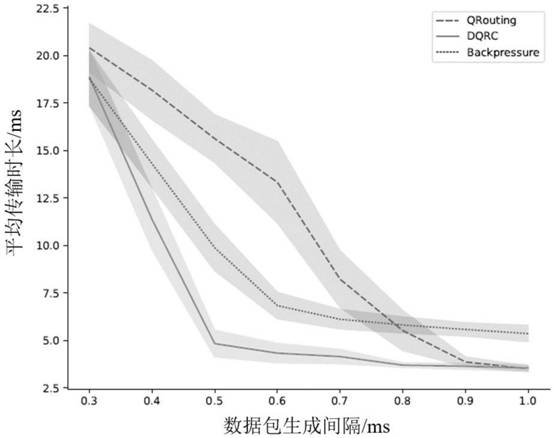

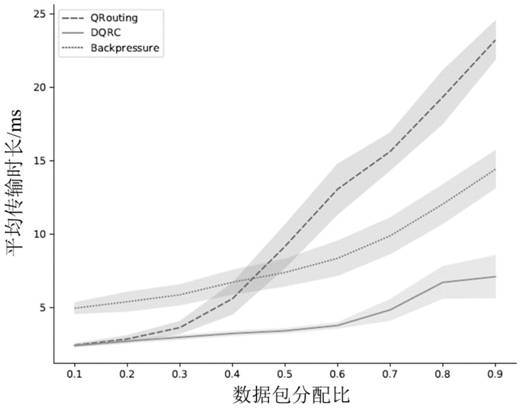

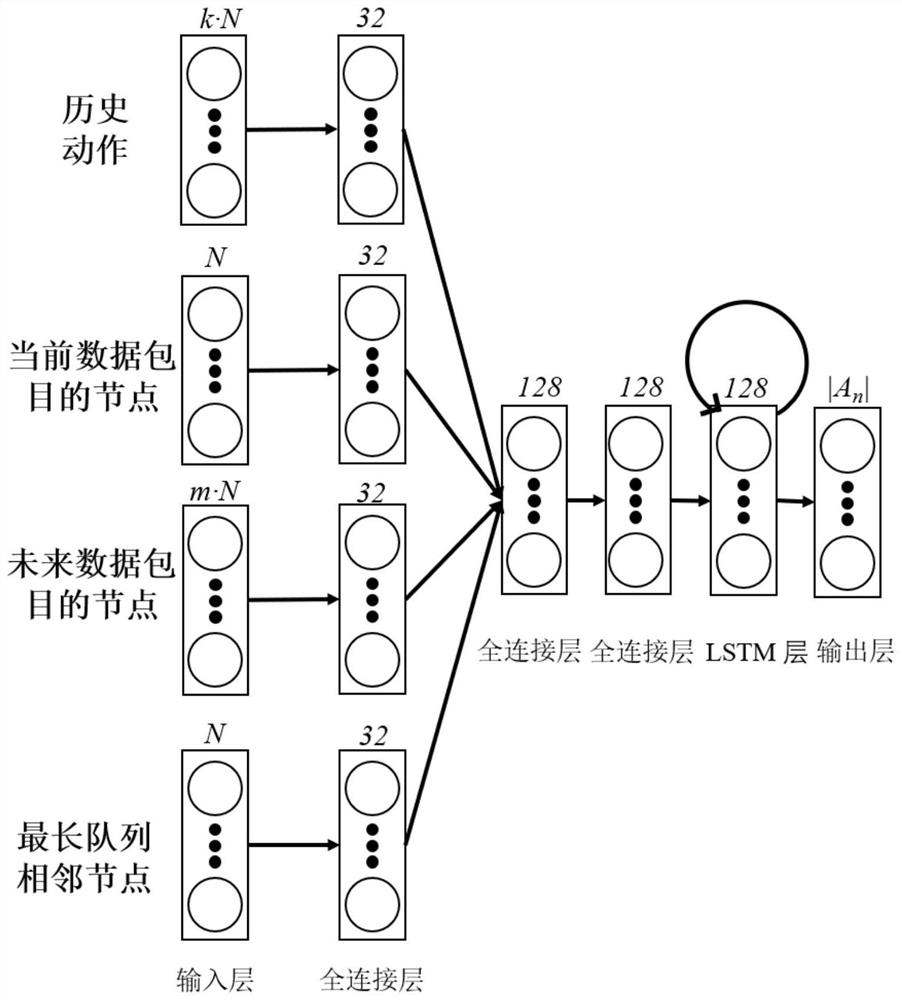

Data packet routing algorithm based on multi-agent deep reinforcement learning

ActiveCN112491712AShort transmission delayImprove performanceNeural architecturesData switching networksPathPingData pack

The invention belongs to the technical field of distributed routing, and particularly relates to a data packet routing algorithm based on multi-agent deep reinforcement learning. In order to relieve the congestion condition in a computer network, an end-to-end adaptive routing algorithm is designed by using a multi-agent deep reinforcement learning technology, and each router completes data packetscheduling according to local information, so that the transmission delay of data packets is reduced. According to the method, firstly, a mathematical model of distributed routing is constructed, specific meanings of all elements in reinforcement learning are defined, then a neural network is trained, and finally algorithm performance testing is carried out in a simulation environment. Simulationexperiment results show that introduction of the deep neural network can mine feature information in an input network state, balance between an unblocked path and a shortest path is achieved, and compared with other common routing algorithms, shorter data packet transmission time delay is achieved.

Owner:FUDAN UNIV +1

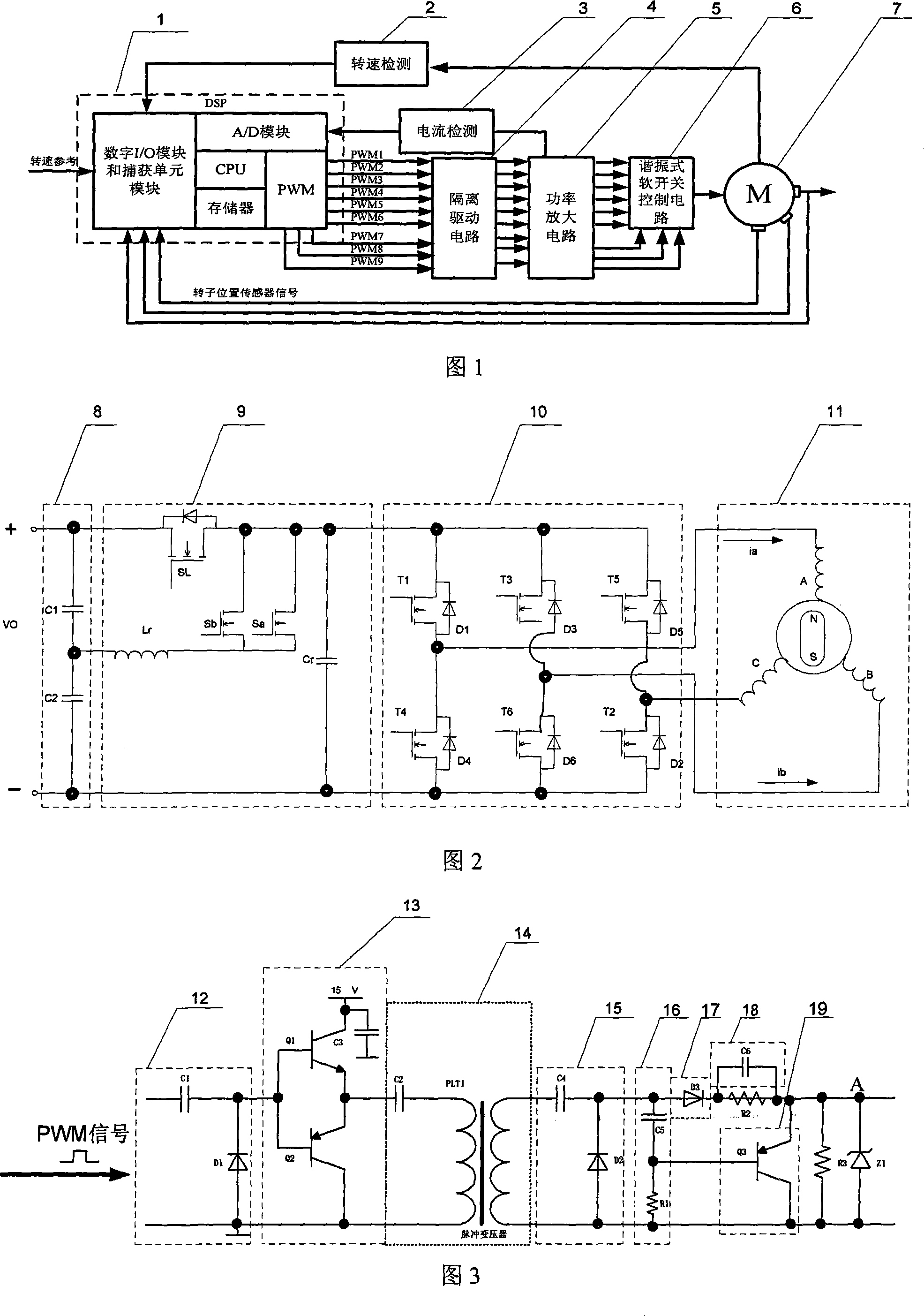

A flying wheel electromotor control system with magnetic suspending reaction

InactiveCN101170295AImprove reliabilitySimple structureSingle motor speed/torque controlElectronic commutatorsAttitude controlFlywheel

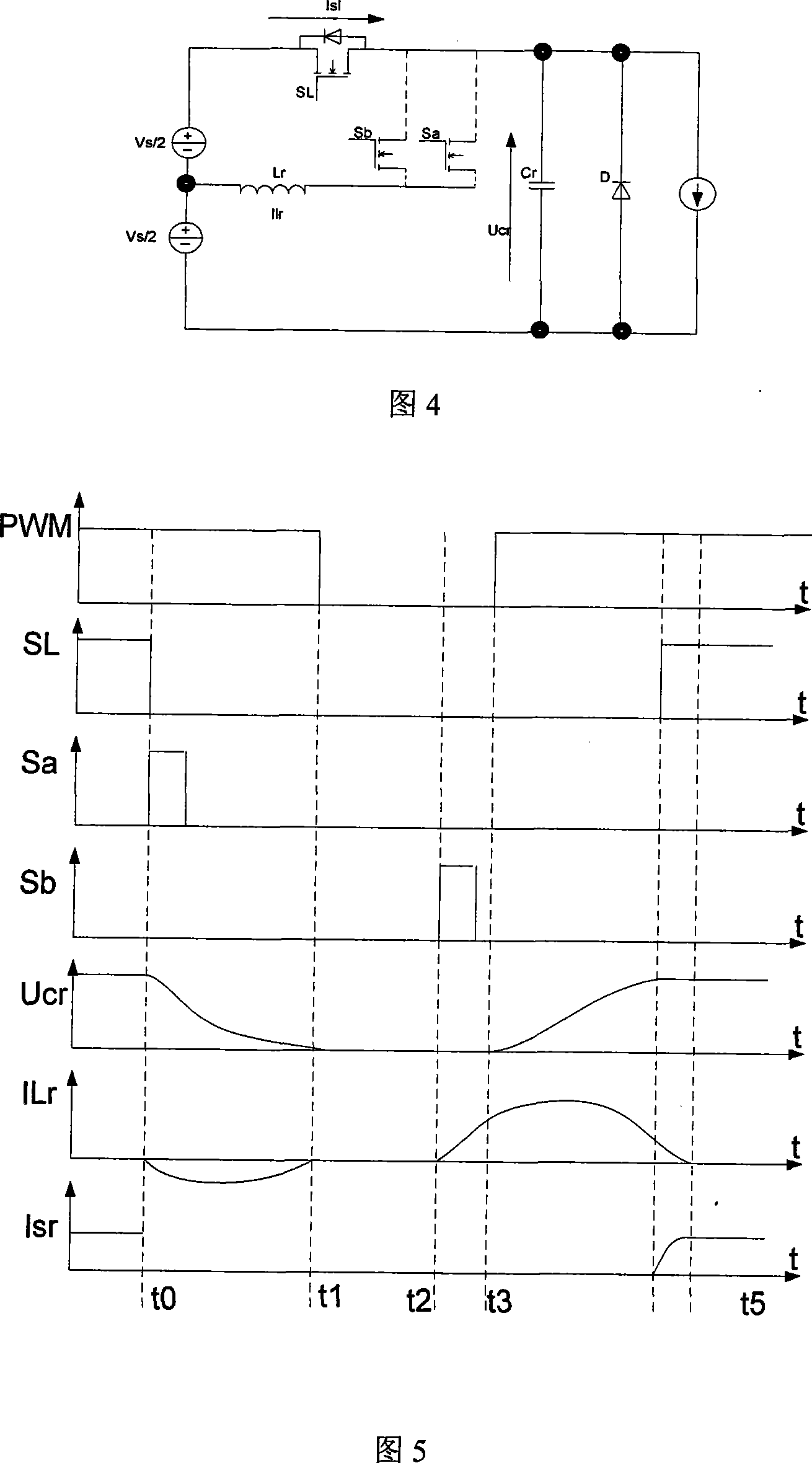

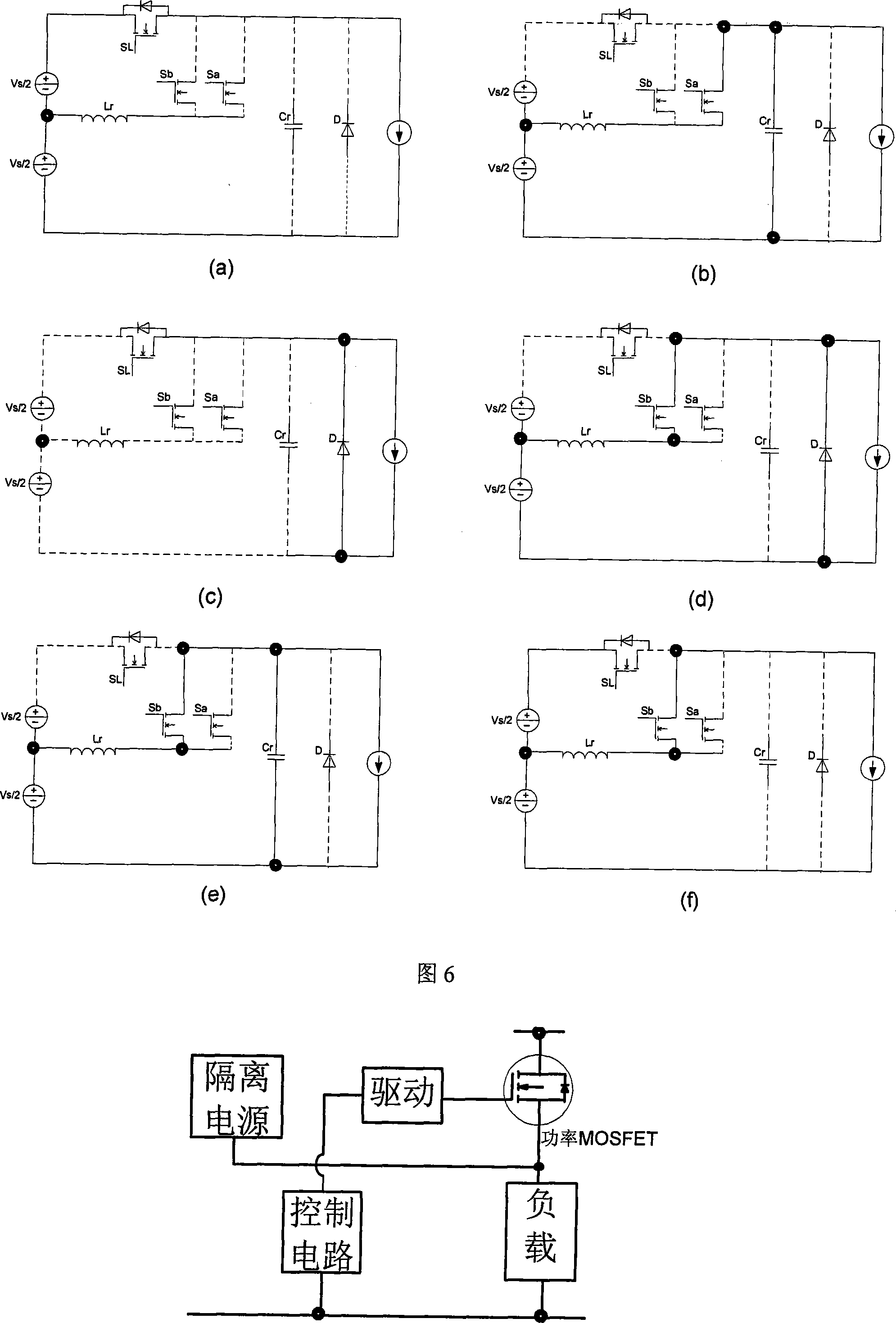

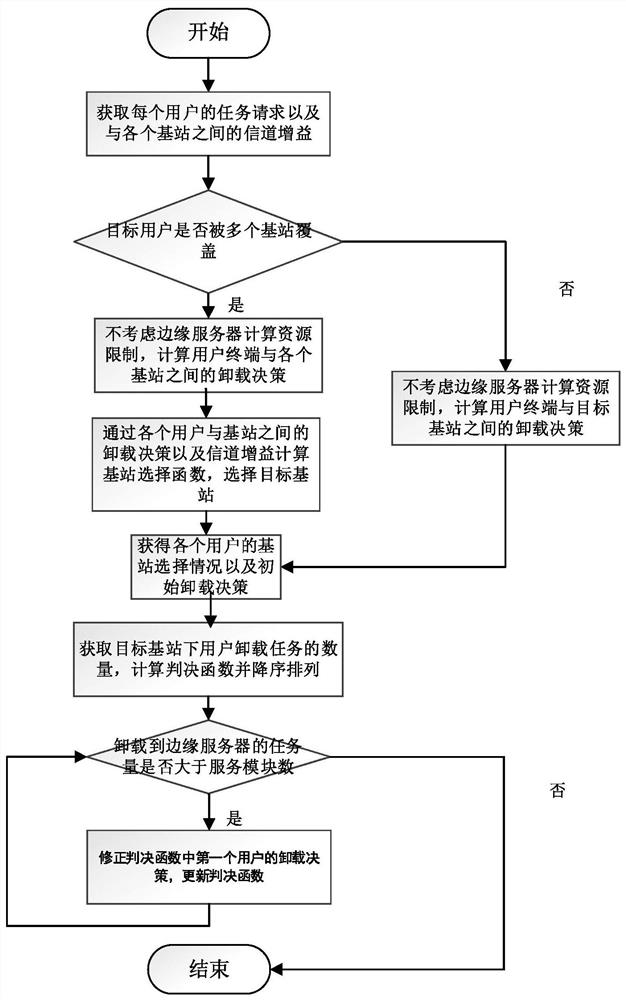

A magnetic suspension counteraction flywheel motor control system adapts to control of three-phase permanent-magnet brushless DC motors for magnetic suspension counteraction flywheels, a new generation of high accuracy attitude control actuating mechanism for high-stability satellites. The invention mainly comprises a controller with a core of a Digital Signal Processor (DSP), a power amplifier, an upper bridge arm driving circuit in the power amplifier, a lower bridge arm driving circuit in the power amplifier, a resonance-type soft switch control circuit, a three-phase permanent-magnet brushless DC motor, a current detection circuit, a 28VDC steady power source, a +15VDC steady power source and a +5VDC steady power source. The invention can control On / Off of each power switch tubes on resonance-type soft switches through a non-demodulated isolation driving circuit, so as to fulfill high-reliability but low power-consumption running of control system driving circuits for magnetic suspension counteraction flywheel motors.

Owner:BEIHANG UNIV

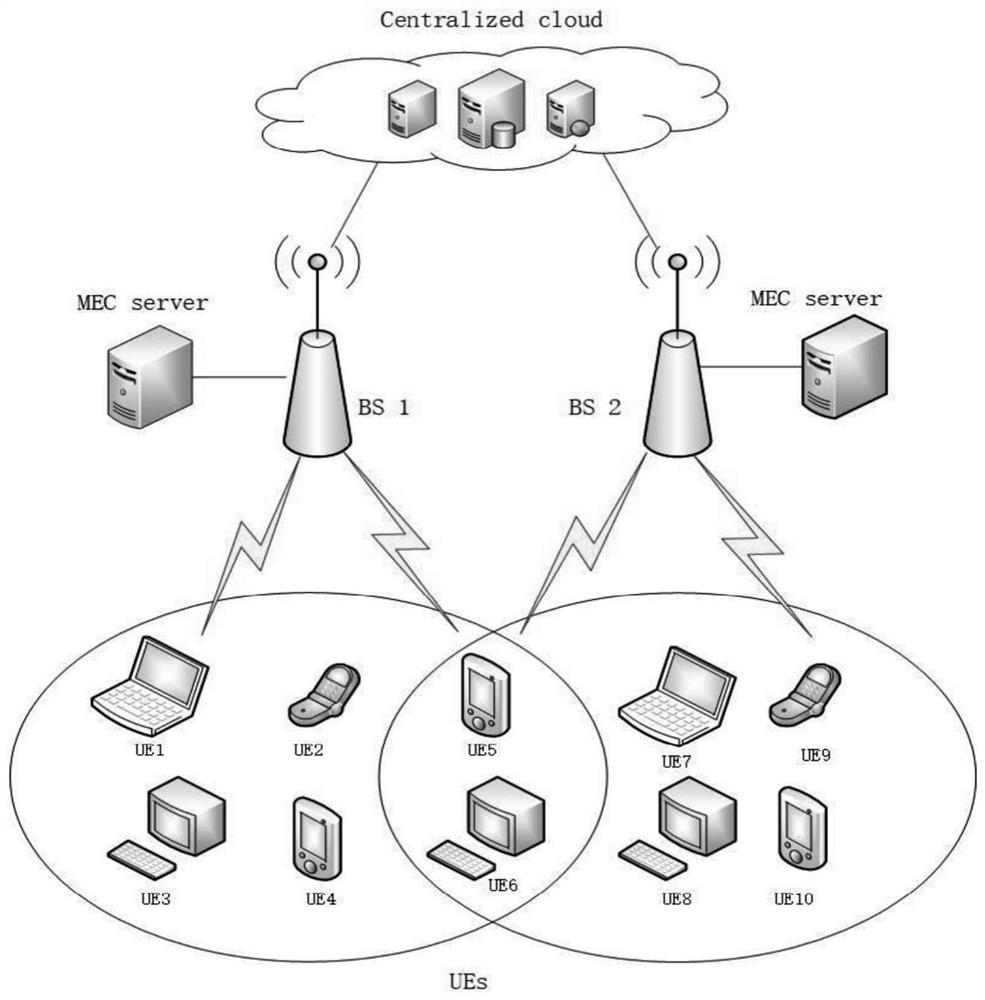

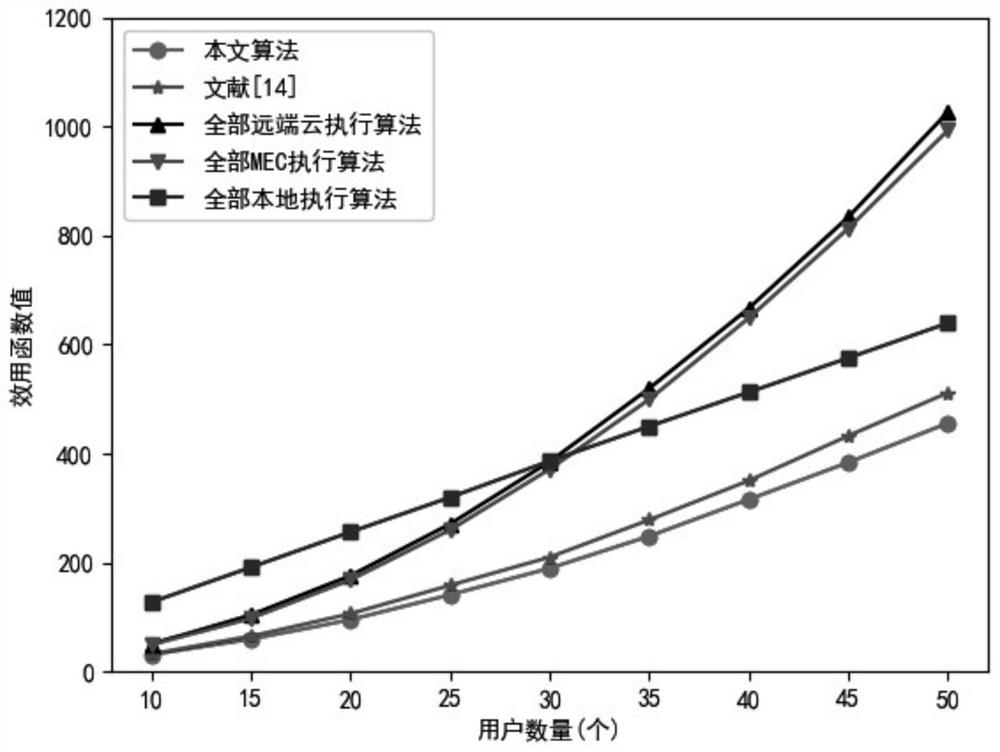

Unloading method of mobile user computing task

ActiveCN112492626AShort transmission delayAbundant computing resourcesResource allocationNetwork traffic/resource managementComputation complexityEdge computing

The invention discloses a mobile user computing task unloading method, and the method comprises the following steps: on the premise of meeting the computing resource constraint of an edge computing server, carrying out unloading scheduling on each task request and selecting a base station suitable for a user to ensure that the system delay and the terminal energy consumption of a user terminal forcompleting a task are minimum; and obtaining a base station selection, unloading decision and task scheduling scheme of the user. According to the method, the calculation complexity is greatly reduced, the user satisfaction is improved, and the purpose of optimizing the system time delay and the terminal energy consumption is achieved.

Owner:NANJING UNIV OF POSTS & TELECOMM

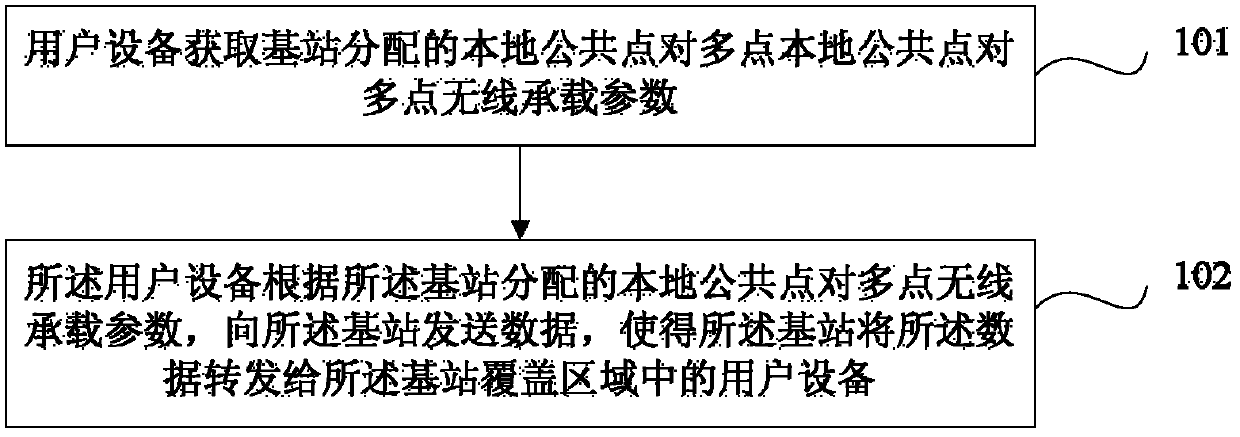

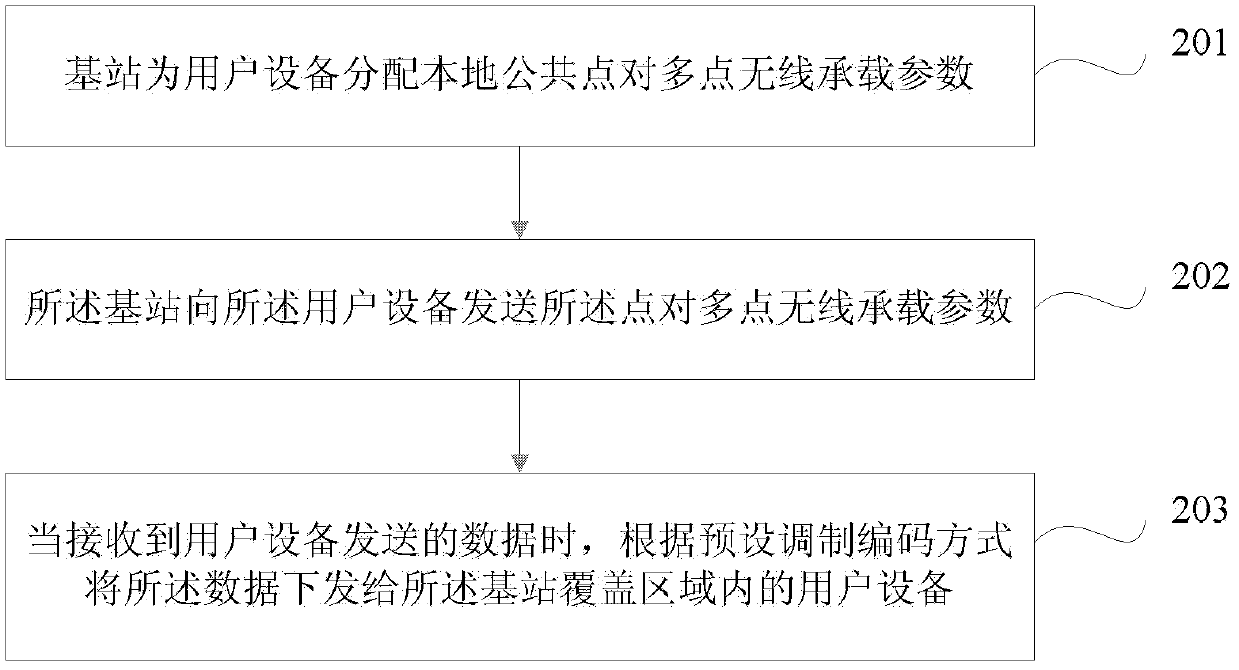

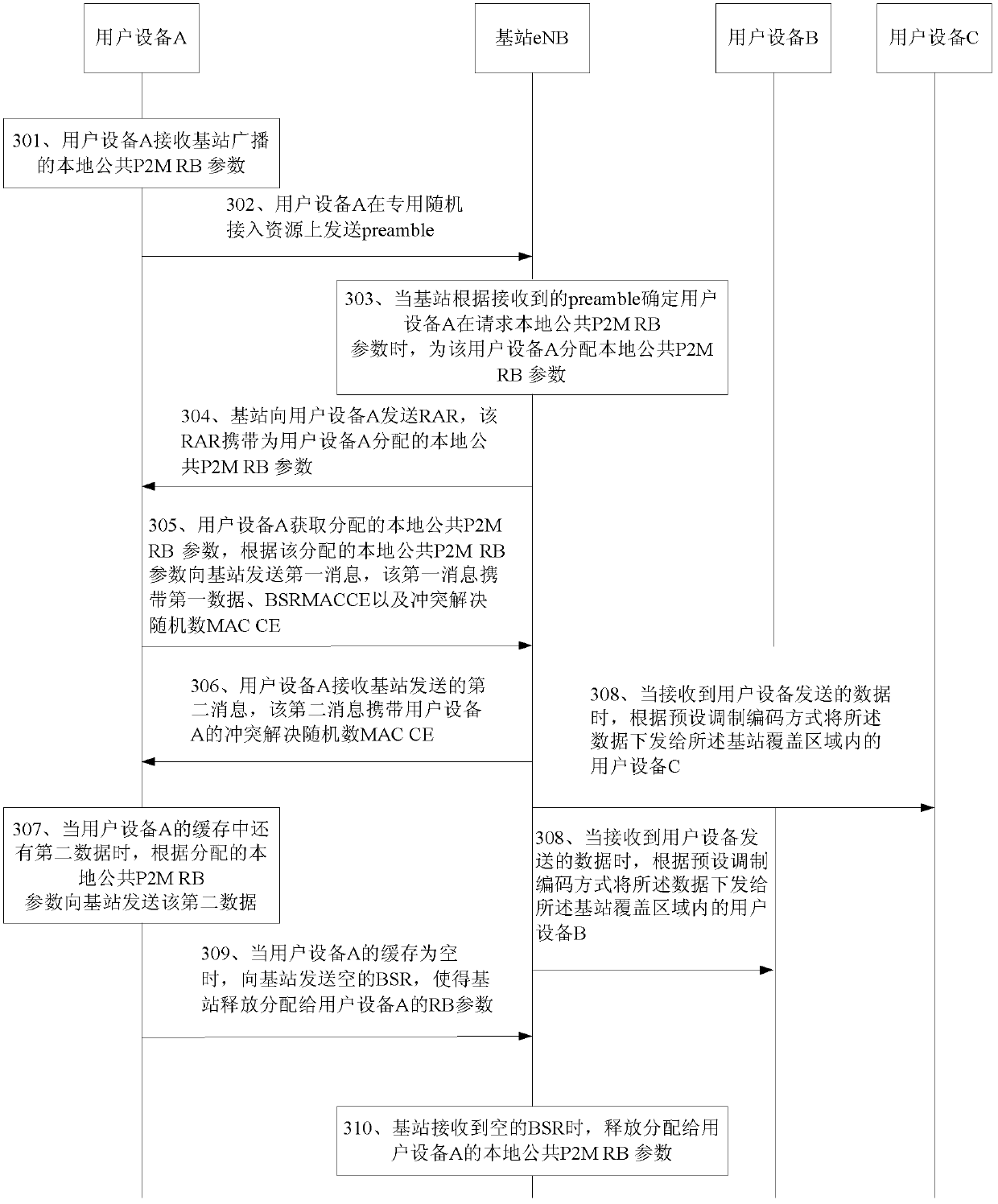

Data transmission method, user devices, base station and system

ActiveCN103379581ASolve the delay problemFast data transferAssess restrictionModulation codingRadio Base Station

The invention discloses a data transmission method, user devices, a base station and a system, and belongs to the technical field of communication. The data transmission method includes the steps of enabling the user devices to obtain local-common-point-to-multipoint radio bearer parameters distributed by the base station, and enabling the user devices to send data to the base station according to the local-common-point-to-multipoint radio bearer parameters distributed by the base station so as to enable the base station to forward the data to the user devices in the covering area of the base station. The data transmission method further includes the steps of enabling the base station to distribute the local-common-point-to-multipoint radio bearer parameters to the user devices, enabling the base station to transmit the local-common-point-to-multipoint radio bearer parameters to the user devices, and when the data transmitted by the user devices are received, enabling the base station to issue the data to the user devices in the covering area of the base station according to a preset modulation coding manner. The data transmission method, the user devices, the base station and the system solve the problems of the informed delay uncertainty and the excessively large delay of a warning message in the prior LTE technology.

Owner:HUAWEI TECH CO LTD

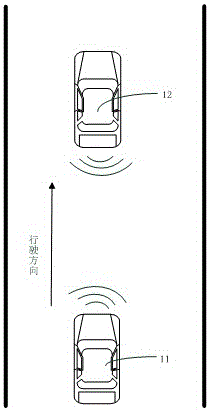

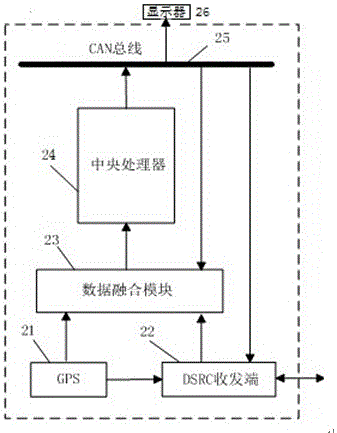

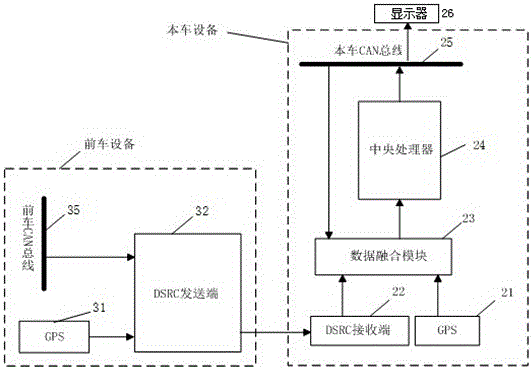

Emergent vehicle brake early warning system

ActiveCN105894858AIncrease speedShort transmission delayAnti-collision systemsSignalling/lighting devicesDriving safetyVIT signals

The invention discloses an emergent vehicle brake early warning system which comprises a CAN bus, a central processor, a data fusion module, a GPS positioning module and a special short-distance communication transmitting-receiving end. The state information of a former vehicle can be actively acquired, and furthermore, with the combination of the state information of a vehicle of a user, a brake early warning signal can be judged and reminding can be output, so that collision accidents happening in emergent braking of vehicles can be avoided, and an active protection function for safe driving can be achieved. By adopting the emergent vehicle brake early warning system, the limits that a conventional distance detection sensor is short in measurement distance, small in detection angle and great in obstruction influence of a barrier can be broken through, the position information of the former vehicle and the vehicle of the user is acquired by using the GPS positioning module, real-time communication between vehicles is achieved by virtue of a DSRC special short-distance communication technique, a brake early warning signal can be judged, and a brake early warning function can be achieved.

Owner:CHONGQING CHANGAN AUTOMOBILE CO LTD

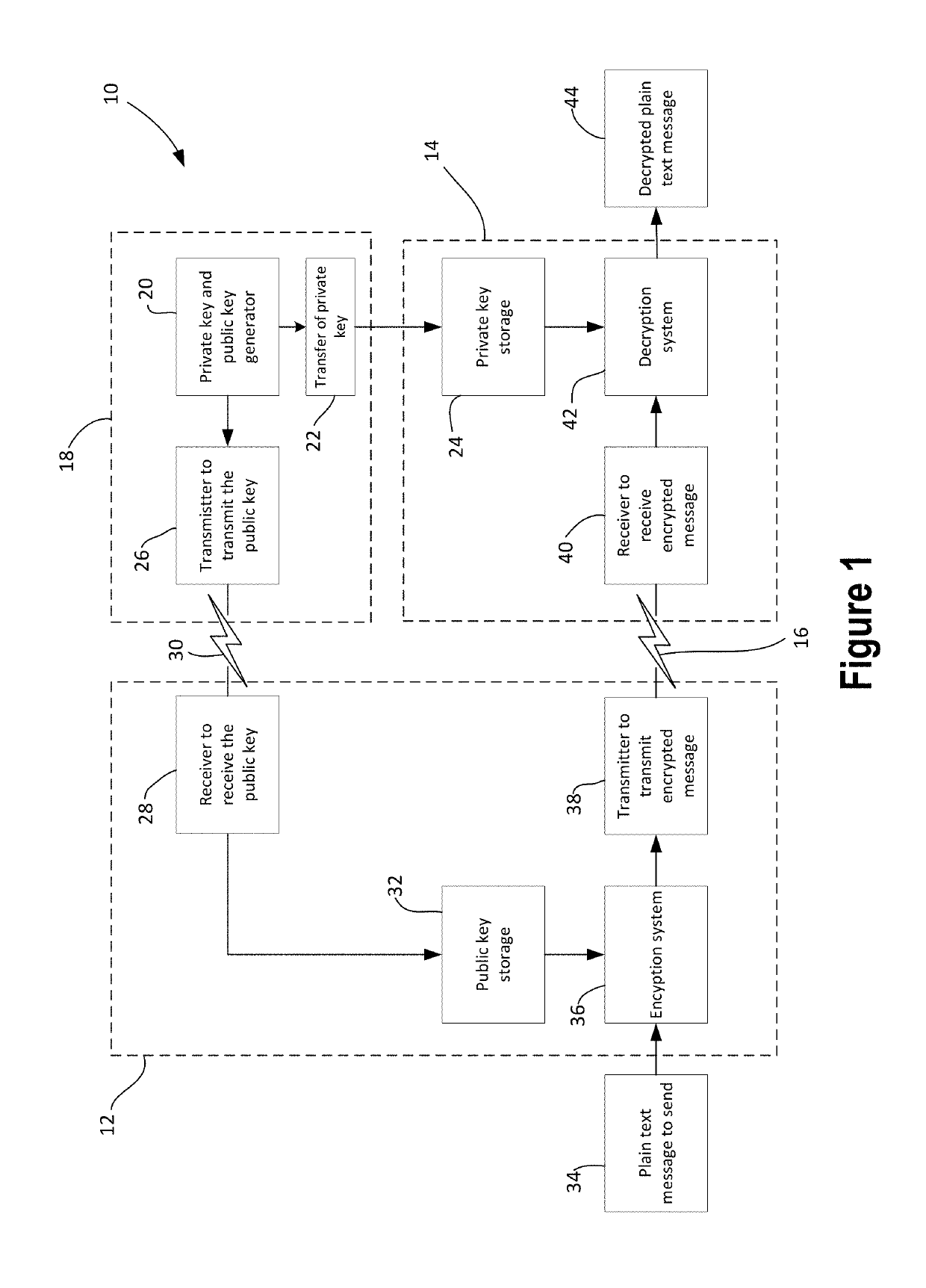

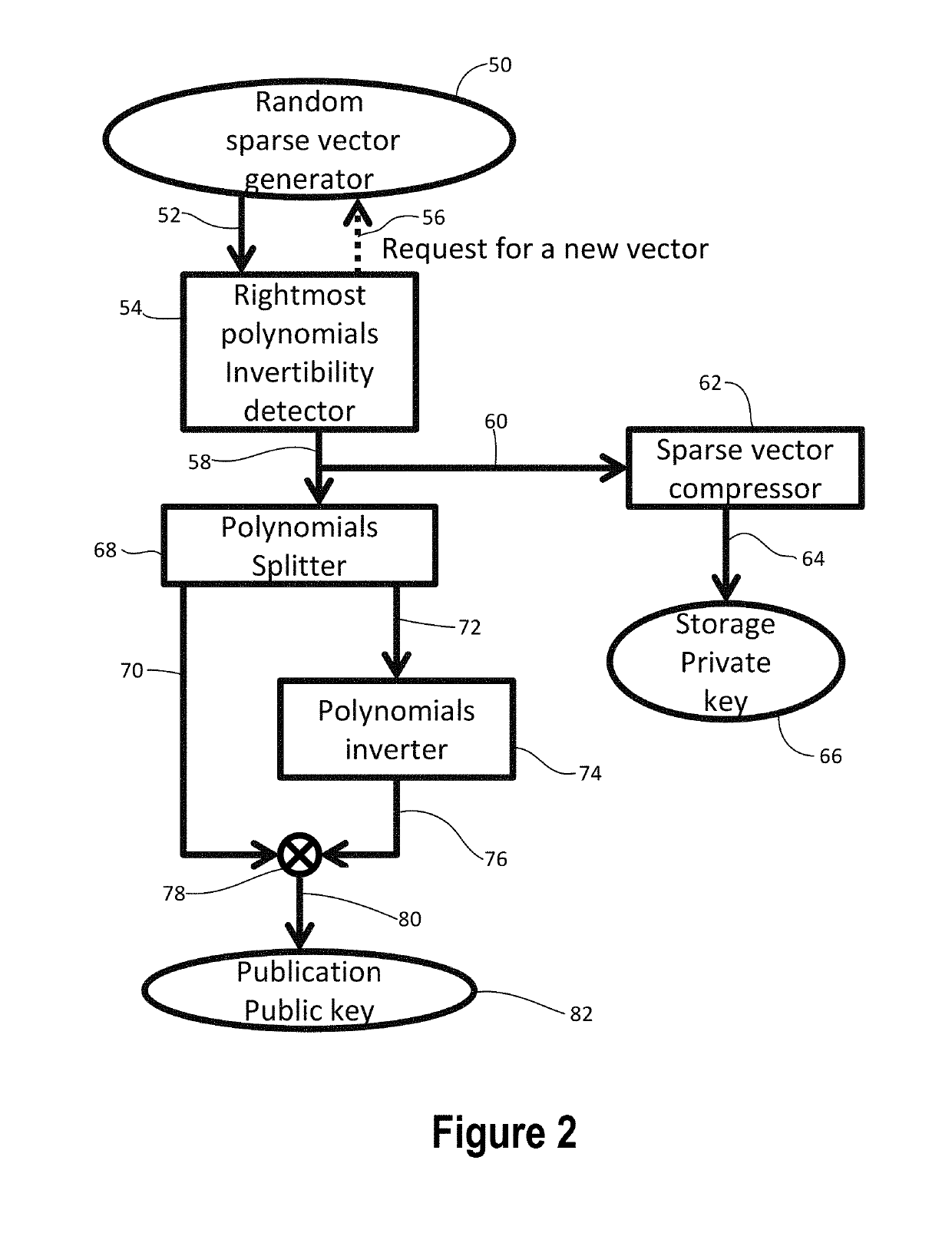

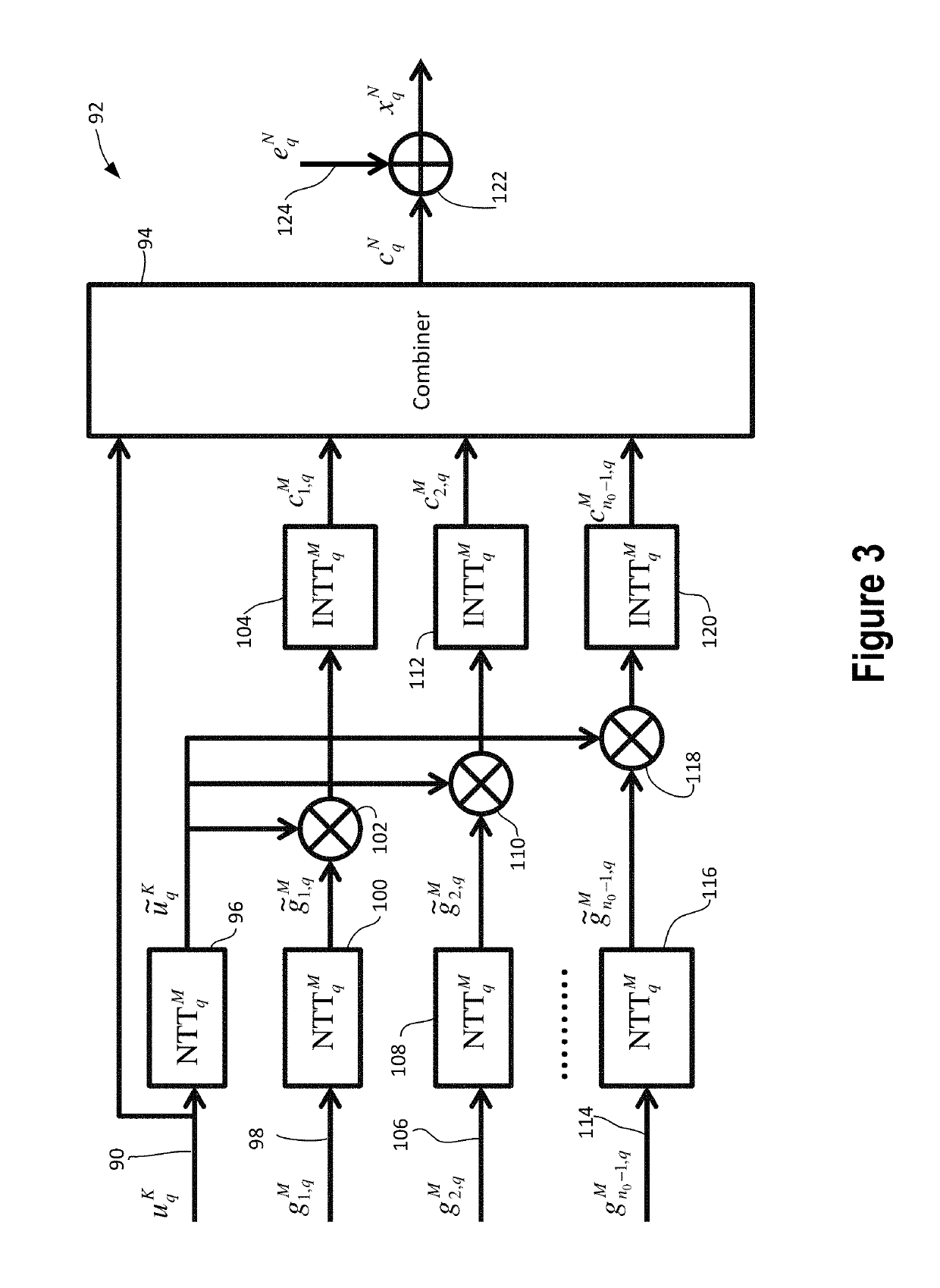

METHOD AND APPARATUS FOR ASYMMETRIC CRYPTOSYSTEM BASED ON QUASI-CYCLIC MODERATE DENSITY PARITY-CHECK CODES OVER GF(q)

ActiveUS20200028674A1Correction capabilityHigh failure rateKey distribution for secure communicationJoint error correctionKey (cryptography)Theoretical computer science

Methods and apparatus for code-based asymmetric cryptosystem using Quasi-Cyclic Moderate-Density Parity-Check (QC-MDPC) error correcting codes. Specifically, the method and apparatus generalizes the framework of (QC-MDPC) Code-Based (CB) cryptography from the binary domain (Galois Field of two elements) to an arbitrary size of Galois Field and provides an apparatus for implementing the cryptosystem with a simplified computational complexity of key generation, encryption, and decryption components of the cryptosystems and reduced sizes of the public and private security keys.

Owner:ZENITH F ECTRONICS LLC

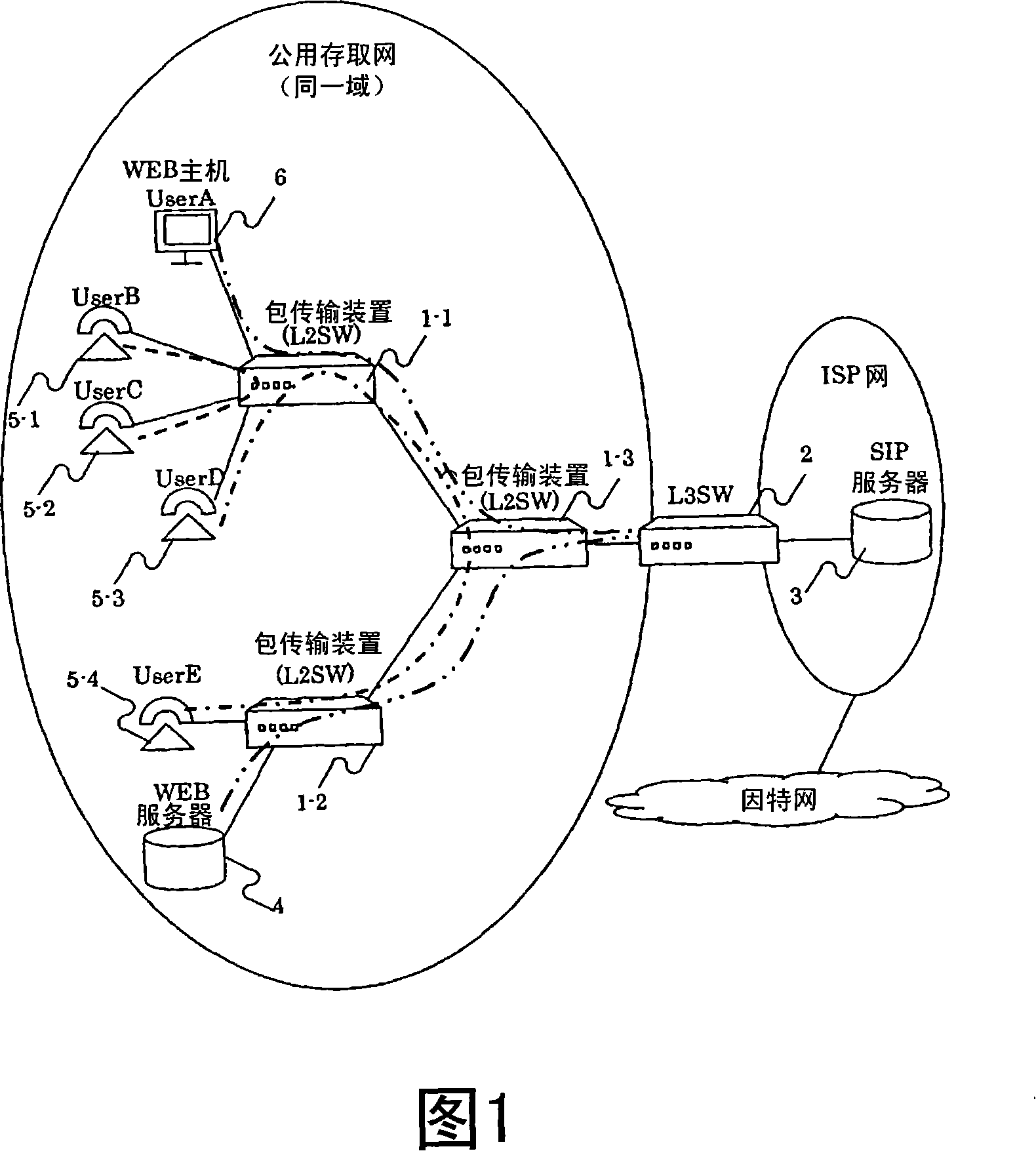

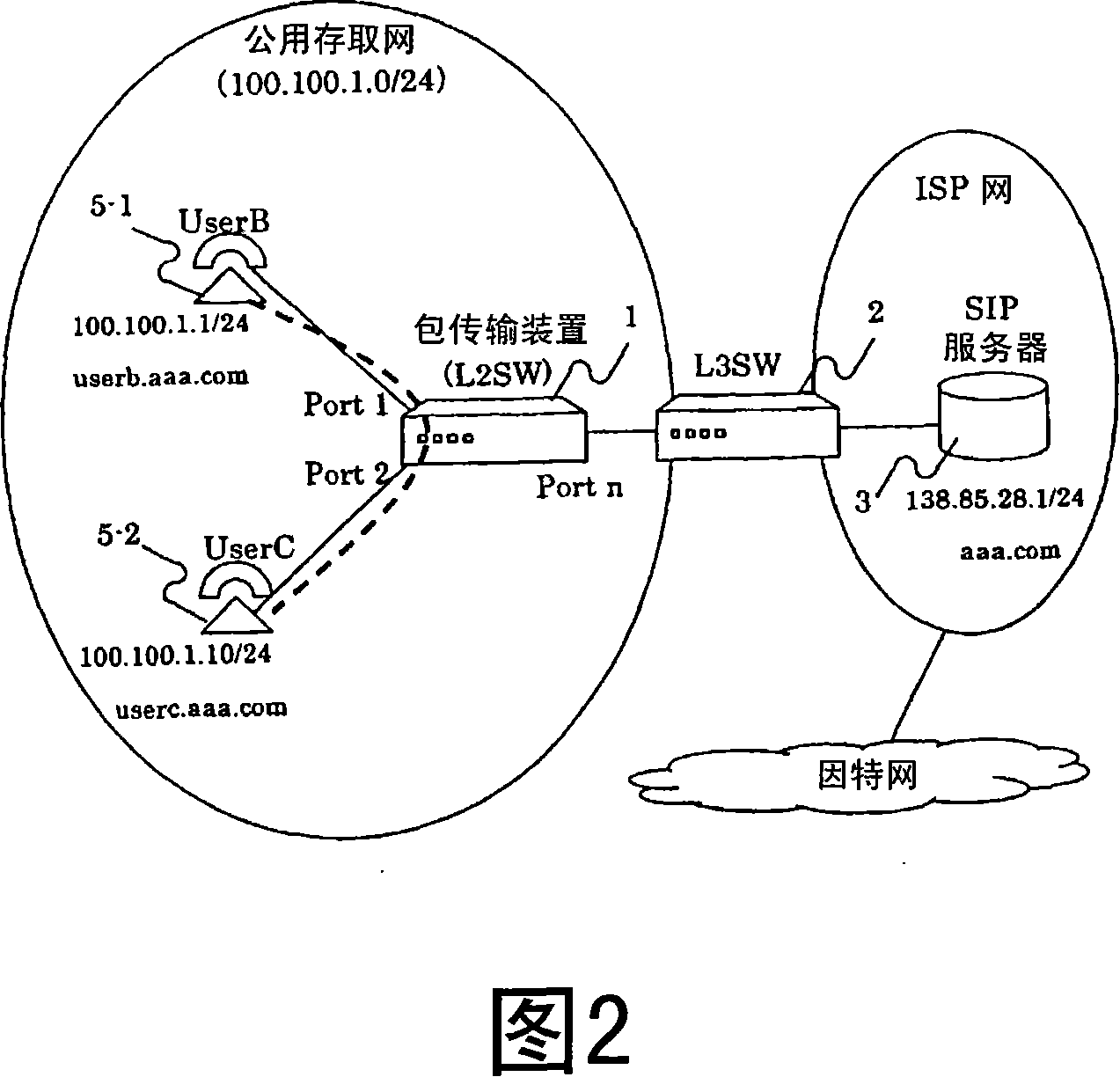

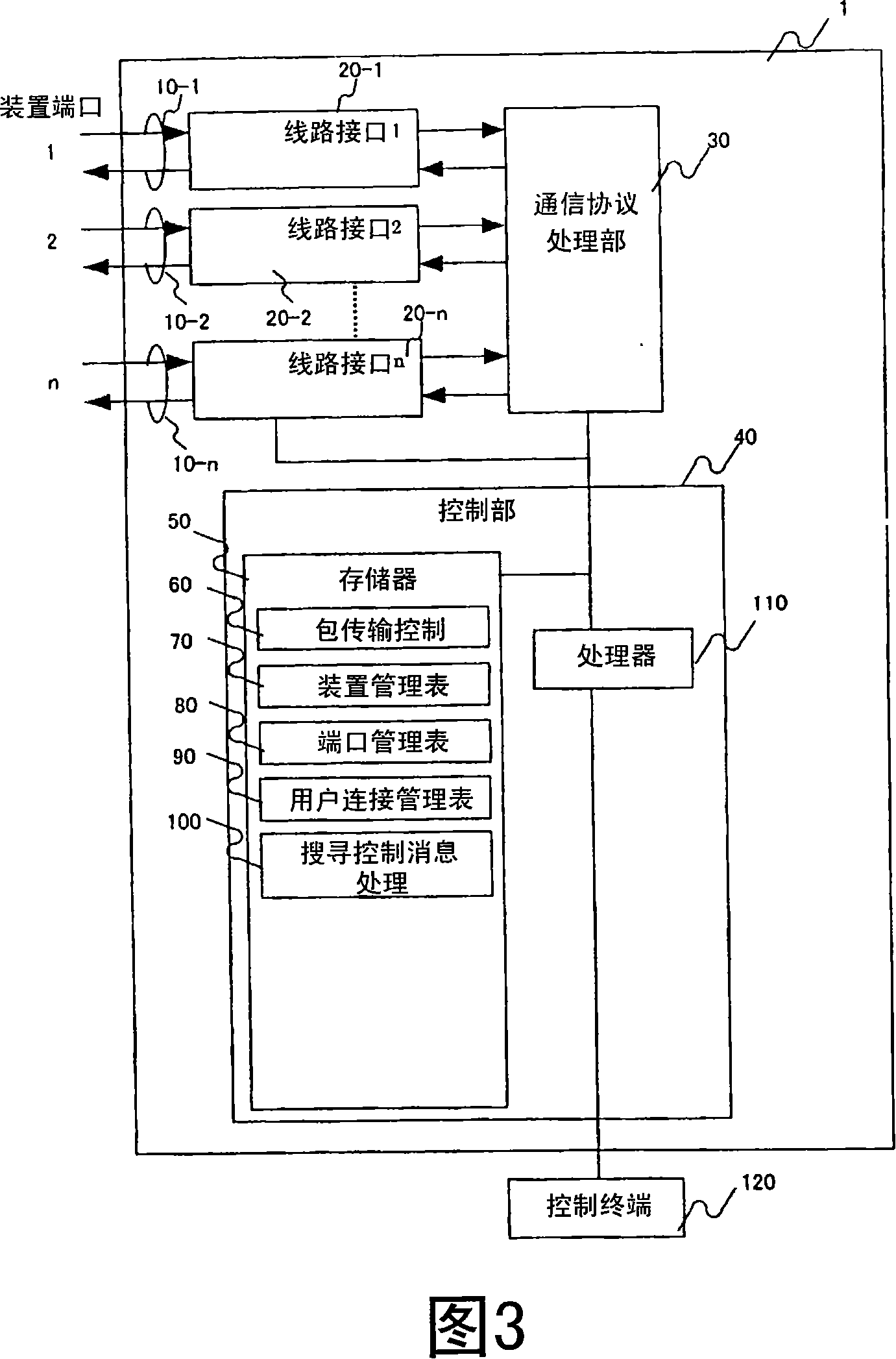

Packet transfer device and communication system

InactiveCN101106524AAvoid transmission delaysReduce transmission delayInterconnection arrangementsNetworks interconnectionCommunications systemSession control

In a network having an L2SW in which uplink VLAN is set, a transfer delay of a voice call packet is prevented. In a process of establishing a session between terminals ( 5 ), a packet transfer device ( 1 ) stores information capable of specifying a sending terminal ( 5 - 1 ) and a receiving terminal ( 5 - 2 ) and a correspondence relation (user connection information) to a connection port into a table. A SIP message of a session control packet communicated between the terminals ( 5 ) is snooped, and a destination IP address, a transmission source IP address, a destination port number, a transmission source port number, a connection port etc. are stored into the table. In a case where an RTP packet as voice data is received after the session is established, the packet transfer device ( 1 ) performs a loopback transfer or transfers it to an uplink port in accordance with the table.

Owner:HITACHI LTD

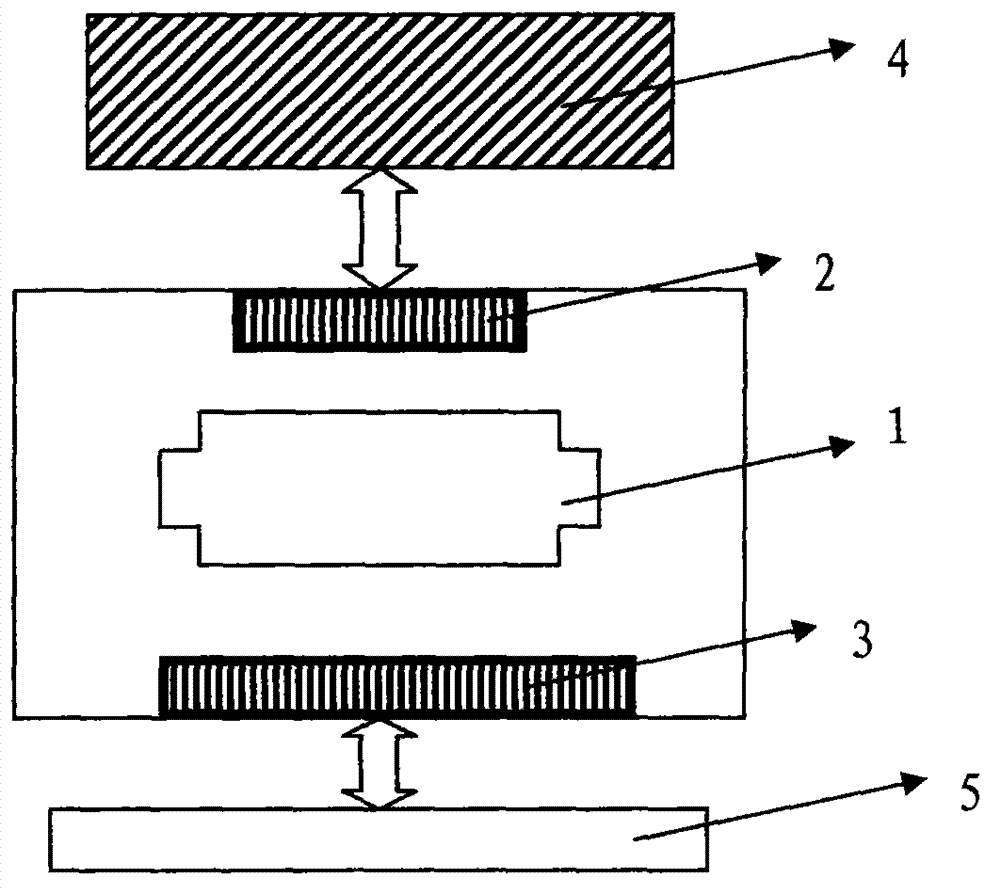

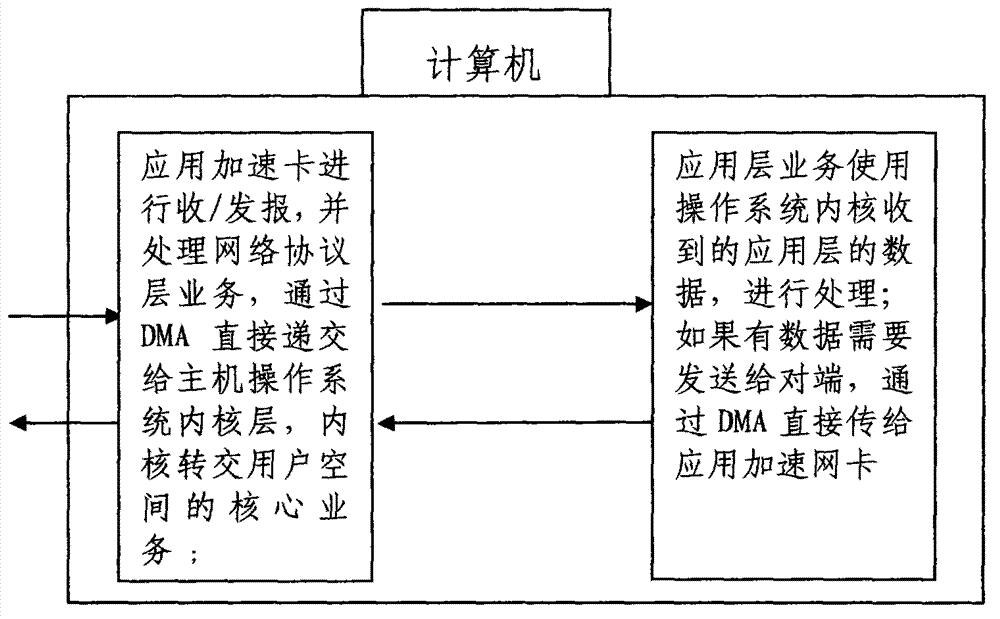

Acceleration network card for cloud computing application layer

InactiveCN102811127ATo achieve concurrent accessLower latencyData switching detailsBus interfaceEnergy conservation

The invention discloses an acceleration network card for a cloud computing application layer. The acceleration network card for the cloud computing application layer comprises a network card chip, a network interface and a host bus interface, wherein the network card chip is connected with the network interface and the host bus interface; a multi-core processing module is cured in the network card chip 1; a network protocol stack is cured in the multi-core processing module; the network interface is connected with a network; and the host bus interface is connected with a host. According to the acceleration network card, a multi-core technology is adopted, and the network protocol stack is cured in the network card chip, so that high-efficiency network transmission is realized; in the same situation, the concurrent access of more users and shorter transmission delay can be realized by a server, the deployment scale of the server can be reduced, and energy resources are saved; the supporting of application protocol processing is realized in hardware, so that the processing burden of the central processing unit (CPU) is uninstalled, and the efficiency of the system is improved; and the functions such as protocol stack timer management and message verification and computation can be realized in the hardware of the network card, and the access delay of the server can be reduced obviously.

Owner:SHENZHEN UTOPIA SYST INTEGRATION

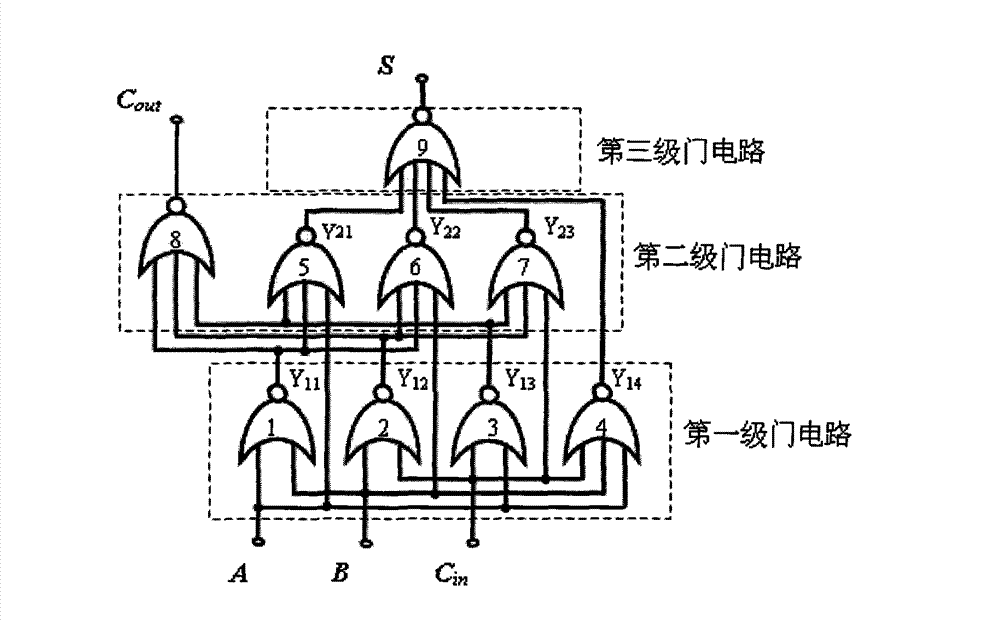

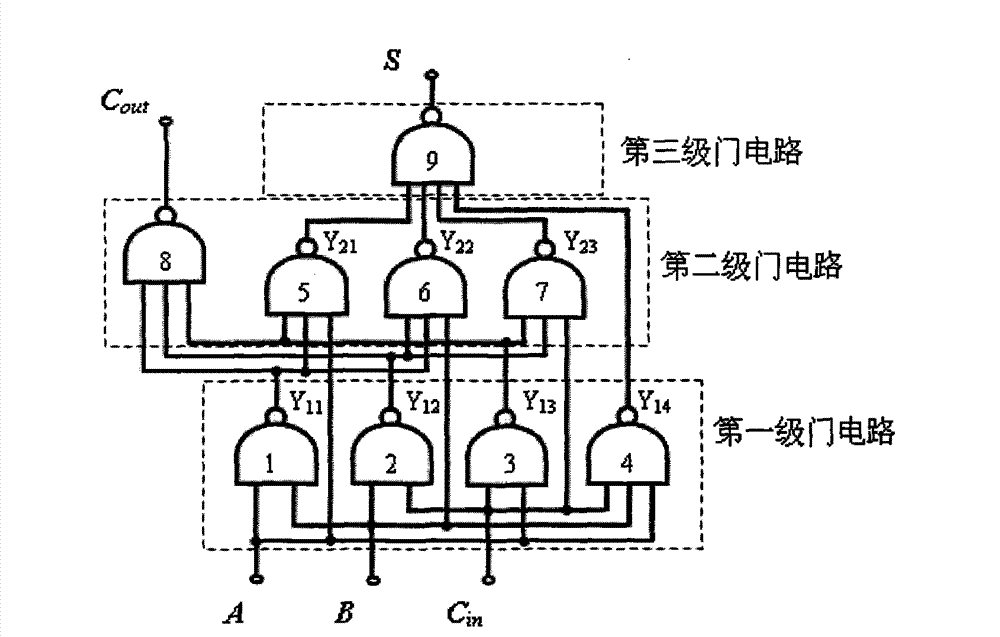

High-performance full-adder arithmetic element circuit

InactiveCN102739237AShort transmission delaySimple structureLogic circuits characterised by logic functionNOR gateEngineering

The invention provides a full-adder arithmetic element circuit. The full-adder arithmetic element circuit comprises a first-order gate circuit, a second-order gate circuit and a third-order gate circuit, wherein the first-order gate circuit comprises an NOR gate 1, an NOR gate 2, an NOR gate 3 and an NOR gate 4, the inputs of the four NOR gates are respectively as follows: (A, B), (B, Cin), (A, Cin), and (A, B, Cin), wherein the A, B and Cin are three one-bit binary input signals, and the outputs of the four NOR gates are respectively as follows: Y11, Y12, Y13, and Y14; the second-order gate circuit comprises an NOR gate 5, an NOR gate 6, an NOR gate 7 and an NOR gate 8, the inputs of the four NOR gates are respectively as follows: (A, Y11, Y13), (B, Y11, Y12), (Cin, Y12, Y13), and (Y11, Y12, Y13), and the outputs of the four NOR gates are respectively as follows: Y21, Y22, Y23, and Cout; and the third-order gate circuit comprises an NOR gate 9, the input of the NOR gate 9 is (Y21, Y22, Y23, Y14), and the output of the NOR gate 9 is S.

Owner:ANHUI UNIVERSITY OF ARCHITECTURE +1

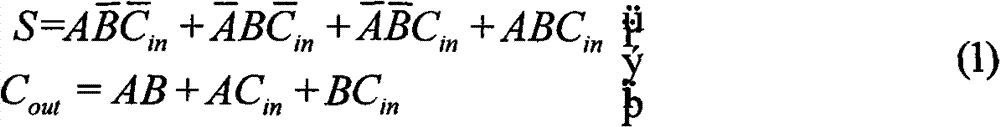

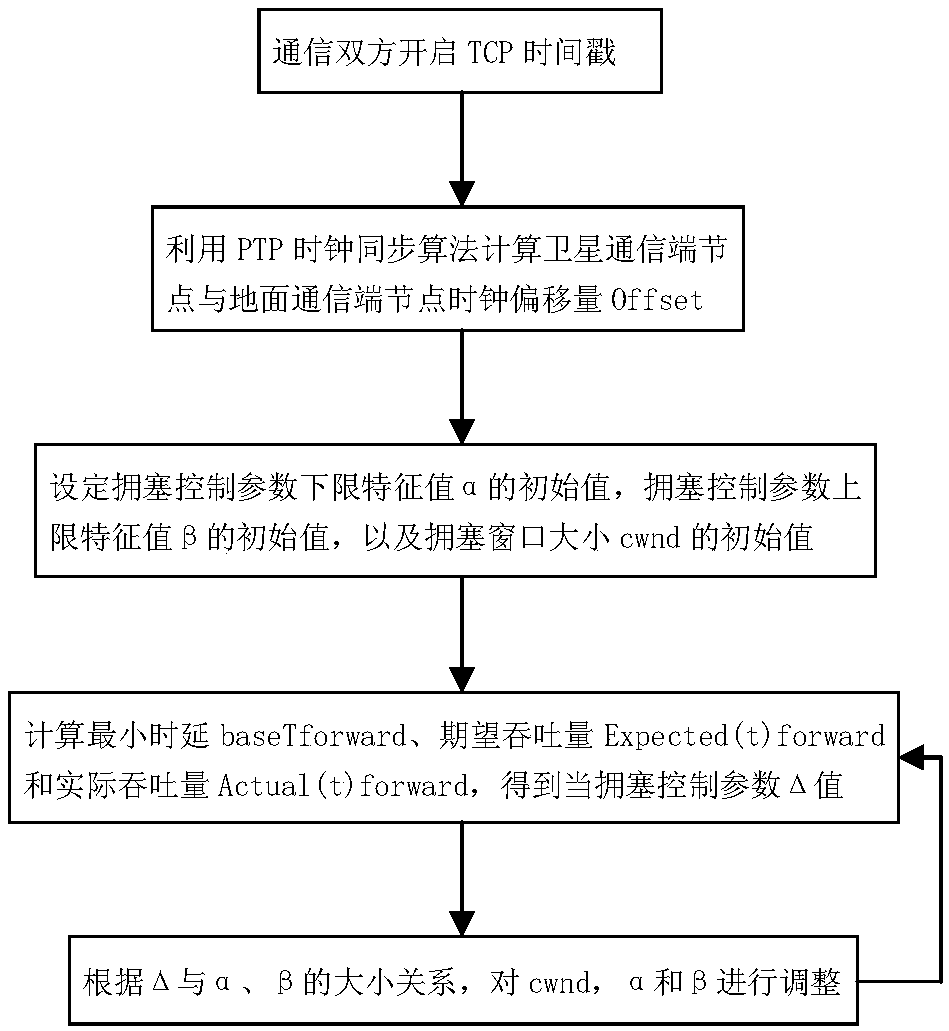

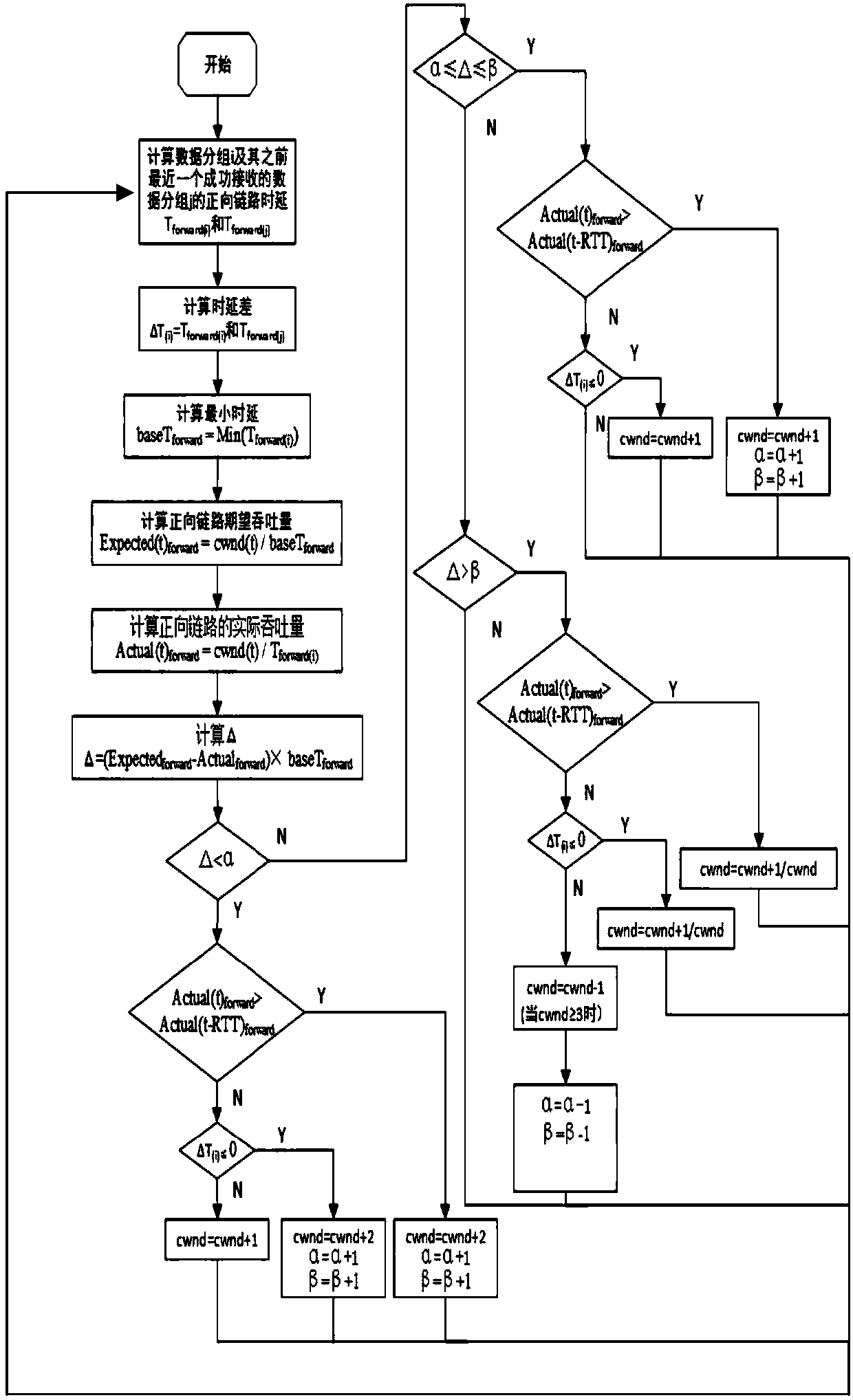

Satellite network transmission control layer jam control method based on forward time delay

ActiveCN107787014AAccurate judgmentImprove regulation efficiencyNetwork traffic/resource managementNetwork topologiesControl layerTelecommunications link

The invention belongs to the technical field of spatial network data communication, and particularly relates to a satellite network transmission control layer jam control method based on forward timedelay. Since a satellite network is characterized in asymmetric bandwidth, a ground-to-air reverse link is likely to be jammed. In order to solve the problem above, according to the satellite networktransmission control layer jam control method based on the forward time delay, when the reverse link is jammed, a sending window of a sending side is narrowed to reduce the jam, and meanwhile, the throughput rate of a forward ground-to-air link of the network is decreased. According to the satellite network transmission control layer jam control method, different control policies can be adopted according to different jam types of a communication link, and the utilization rate of the network bandwidth is increased.

Owner:SHENYANG LIGONG UNIV

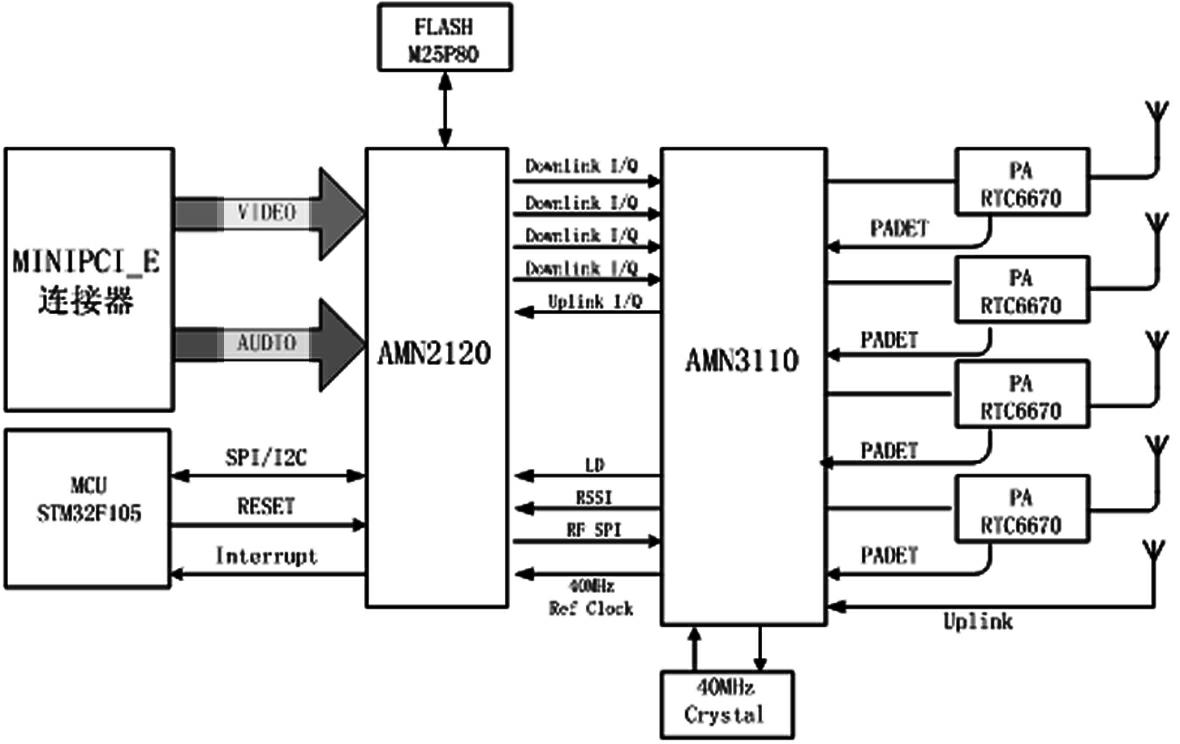

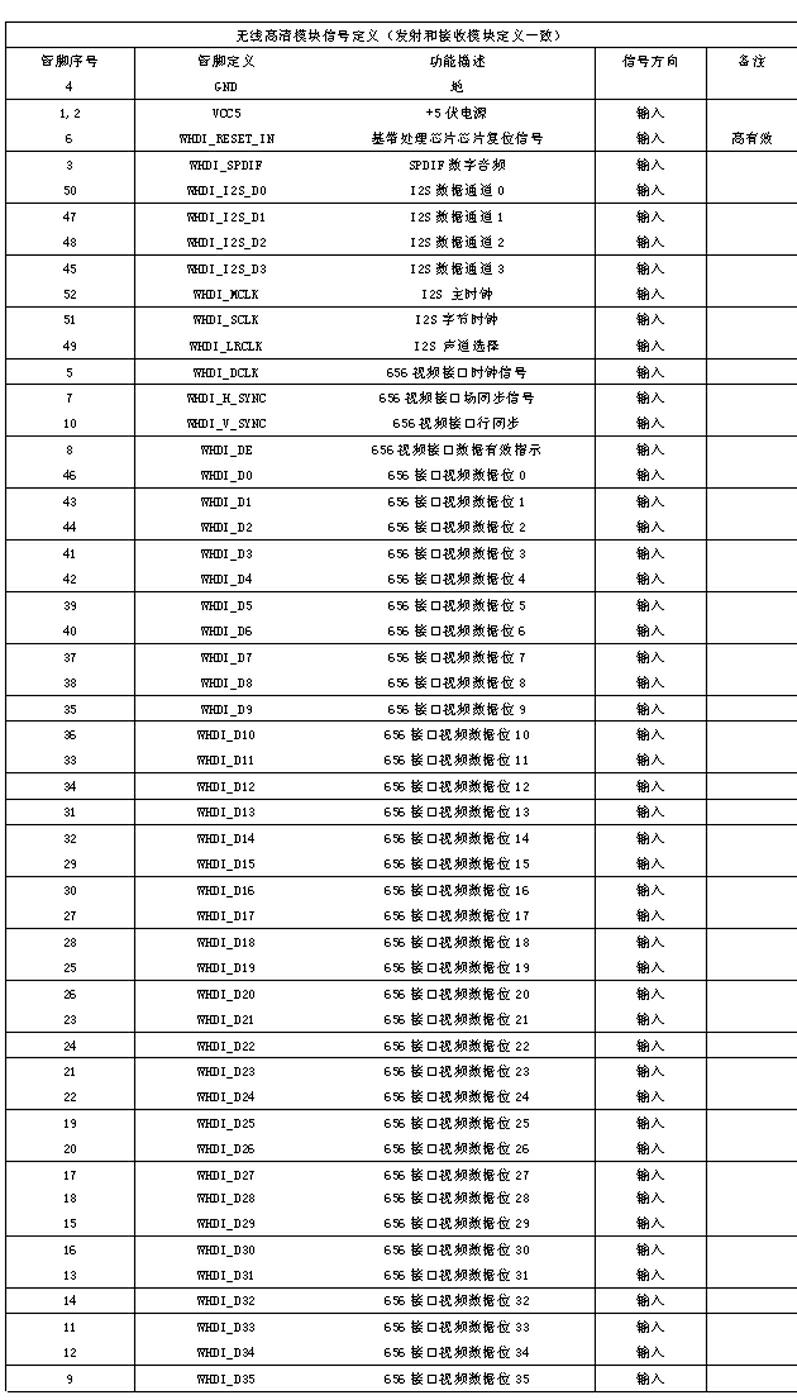

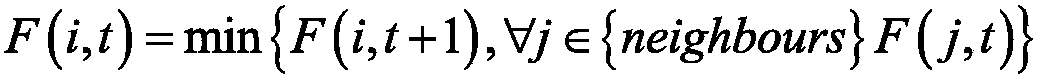

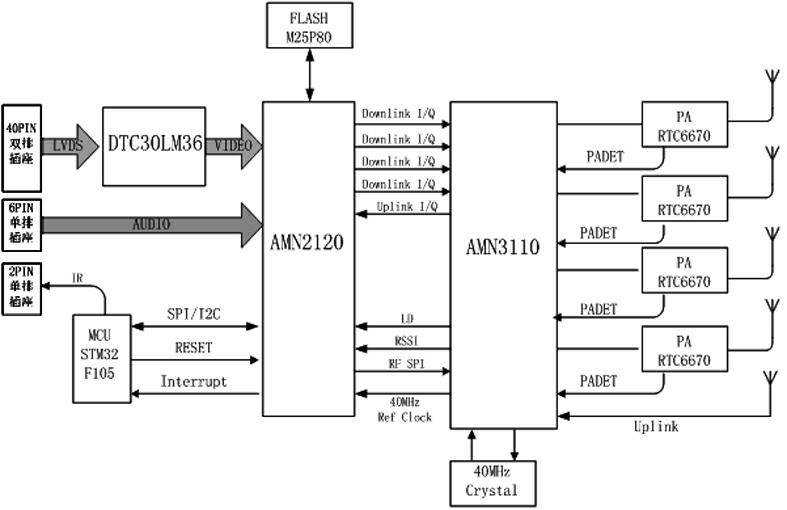

Wireless high-definition video transmission module

InactiveCN102137254AShort transmission delayHigh video resolutionTelevision system detailsPulse modulation television signal transmissionRadio frequencyAir interface

The invention discloses a wireless high-definition video transmission module which comprises an emitting part and a receiving part, wherein the emitting part comprises a baseband processor, a WHDI (Wireless Home Digital Interface) video analyzer, a power amplifier, a control MCU (Microprogrammed Control Unit) and a PF (Pulse Frequency) antenna; the receiving module receives effective audio and video and control data from an air interface through five paths of antennae, the effective audio and video and the control data are sent to a radio frequency chip AMN (Artificial Mains Network) 3210 and then demodulated into five paths of digital IQ (Intelligence Quotient) signals, and the five paths of digital IQ signals are decoded by a baseband chip ANM (Answer Message) 2220. The wireless high-definition video transmission module is integrated into an audio and video device so that a user can easily utilize a WHDI technology to realize wireless transmission of high-definition signals, has the advantages of small transmission delay (less than 1ms), high video definition (supporting 1080P), no compression, long transmission distance (more than 30m), capability of penetrating through barriers, and the like.

Owner:DFINE TECH

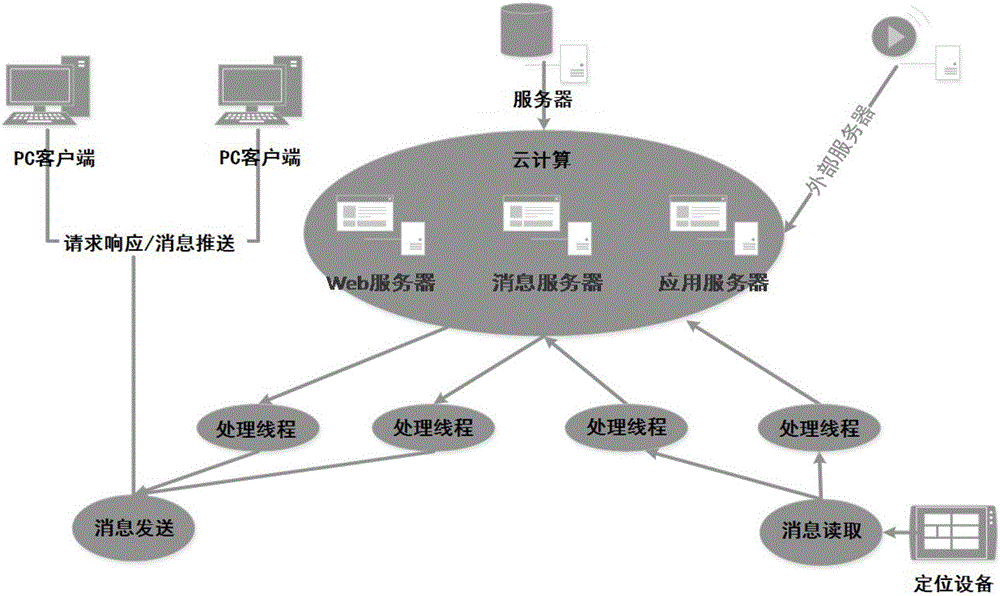

Private network architecture, data acquisition method and edge server

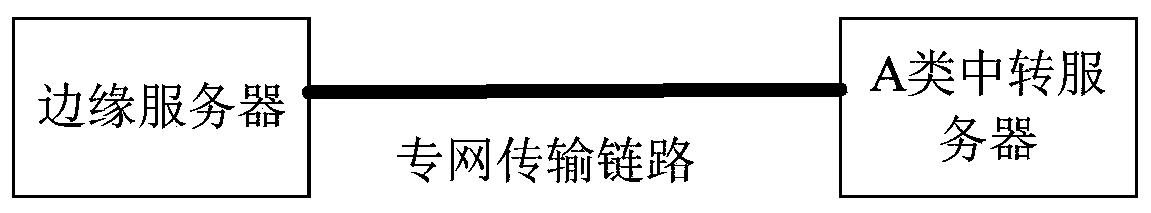

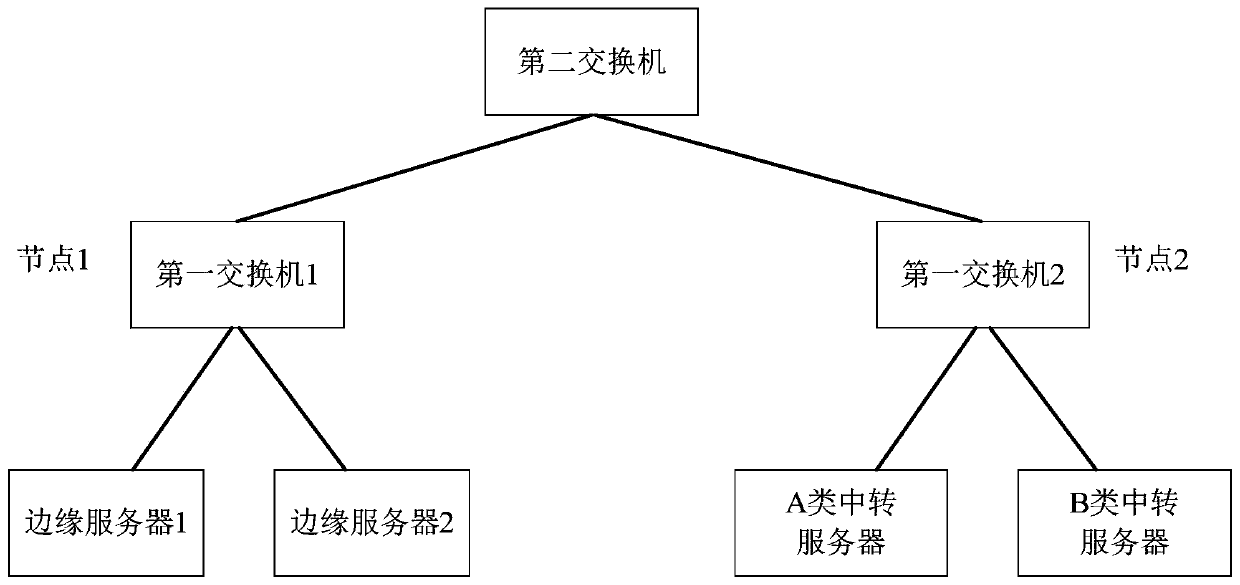

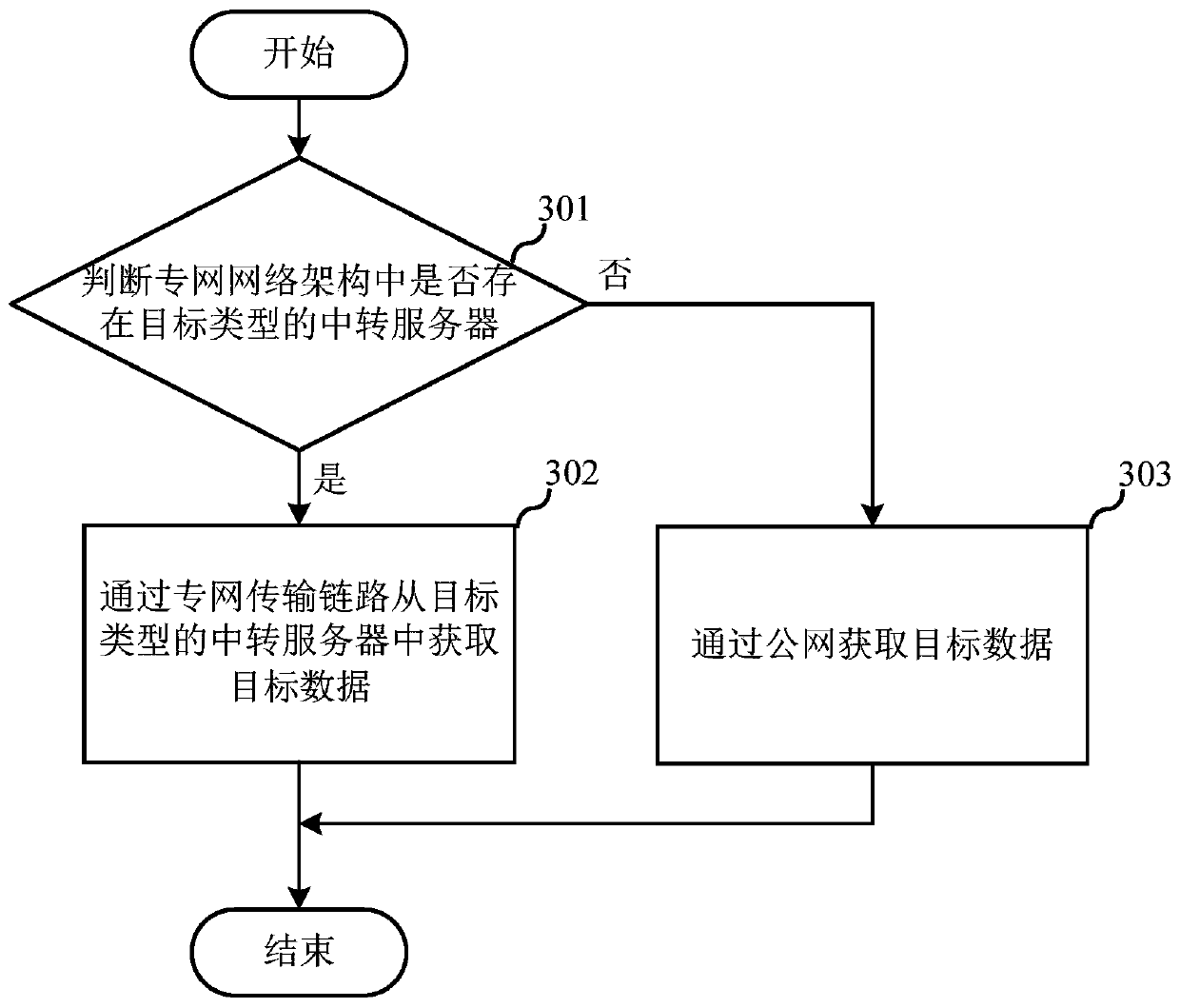

The embodiment of the invention relates to the technical field of Internet, and discloses a private network architecture, a method for acquiring data of a back transfer server and an edge server. Theprivate network architecture comprises at least one type of transit server and at least one edge server, The transit server is connected with the edge server through a private network transmission link; The edge server is used for judging whether a transit server of a target type exists in the private network architecture or not; when it is judged that the transit server of the target type exists,target data are obtained from the transit server of the target type through a private network transmission link, and when it is judged that the transit server of the target type does not exist, the target data are obtained through a public network; And the cost required when the edge server obtains the data back to the transit server is saved.

Owner:CHINANETCENT TECH

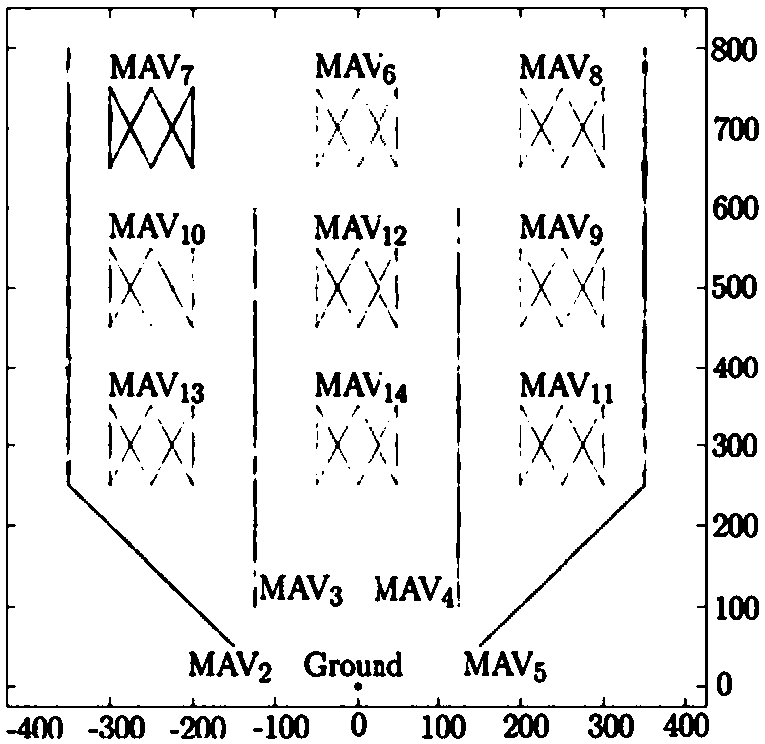

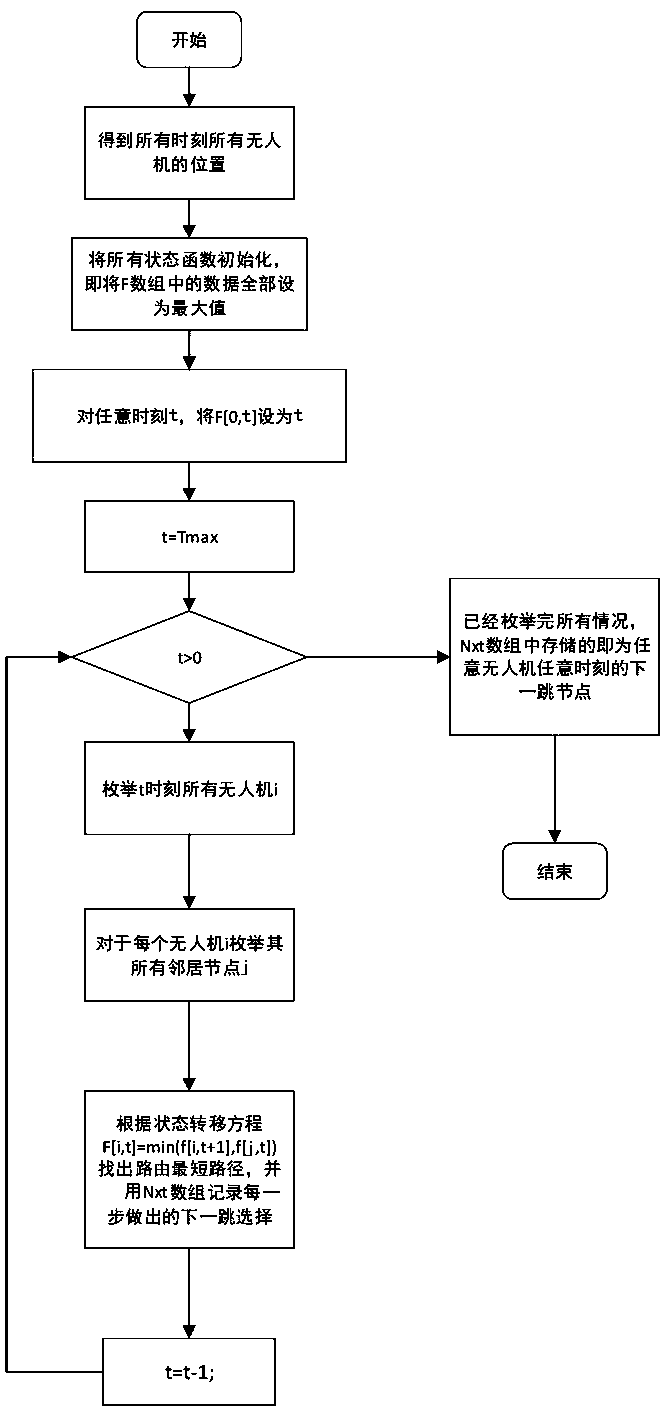

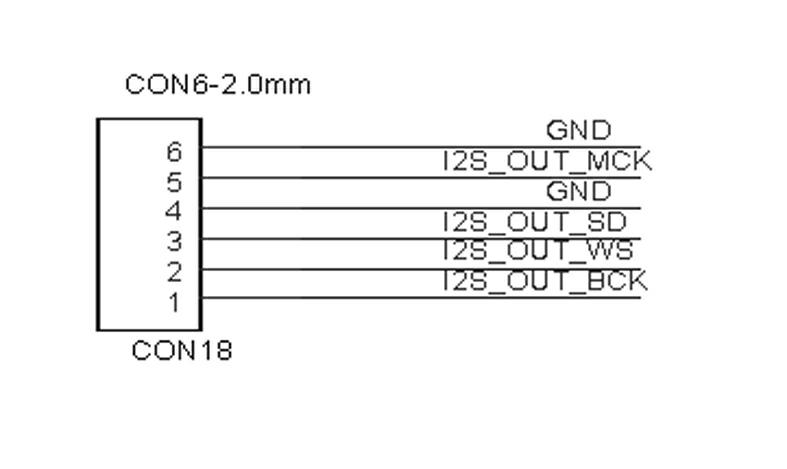

Unmanned plane synergy message transmission method based on dynamic planning

ActiveCN108832995ALower latencyShort transmission delayRadio transmissionData switching networksDynamic planningTransmission time delay

An unmanned plane synergy message transmission method based on dynamic planning comprises the following steps: 1, defining a state function, obtaining a state transition equation and a state transition equation boundary condition; 2, acquiring all unmanned plane positions at all time, and setting conditions; 3, calculating distances between unmanned planes so as to obtain communication capable neighbor nodes of each unmanned plane at the present moment; 4, obtaining transmission next hop of the present moment according to the state transition equation until all moments are iterated and updated, thus obtaining an optimal message transmission object of each unmanned plane at each moment. The method uses a dynamic planning idea to split problems, defines the relation between a problem state and the states, thus solving the problems in a recursion mode, obtaining the minimum message delay formed by the unmanned plane that transmits the message to a certain hop unmanned plane at certain moment, reducing the message transmission time delay, and reducing energy losses caused by message transmission ping-pong effect.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

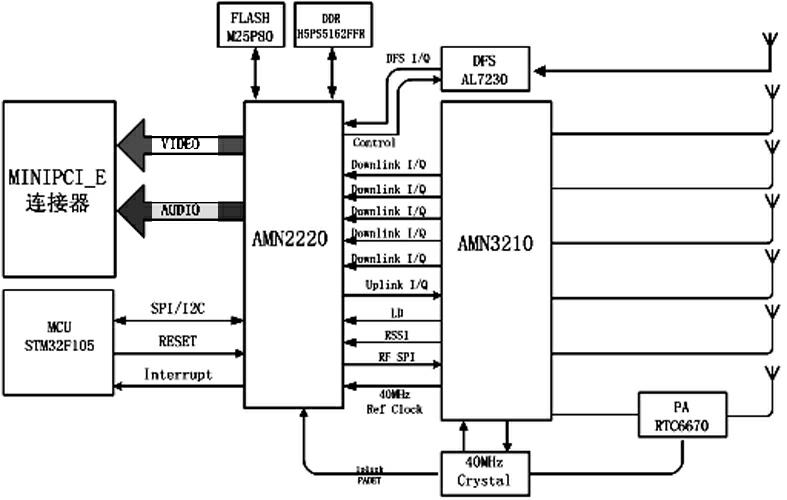

Wireless high-definition LVDS video transmission module

InactiveCN102143363AImprove resolutionShort transmission delayTelevision system detailsColor television detailsVideo transmissionPower factor

The invention discloses a wireless high-definition low voltage differential signaling (LVDS) video transmission module, which is mainly used for televisions and realizes wireless high-definition audio and video signal transmission of the televisions. The module comprises an LVDS receiving module, a base band processing chip, a wireless home digital interface (WHDI) radio frequency processing chip, a power amplifier, a television decoding board, a micro control unit (MCU) and a power factor (PF) antenna. The wireless high-definition LVDS video transmission module is integrated in the television decoding plate so that the television can perform wireless transmission of high-definition signals, and has the advantages of low transmission delay time (shorter than one microsecond), high video resolution (supporting 1080P), compression absence, far transmission distance (more than 30 meters), obstacle penetrability and the like; meanwhile, the whole television becomes lighter and thinner.

Owner:DFINE TECH

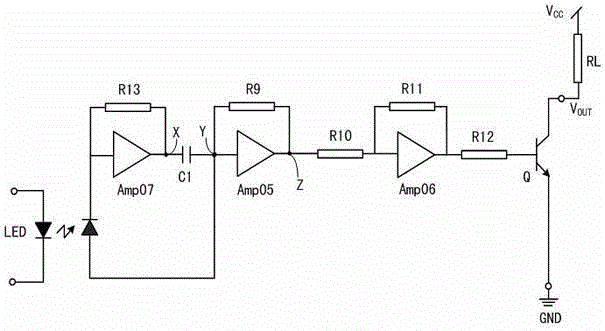

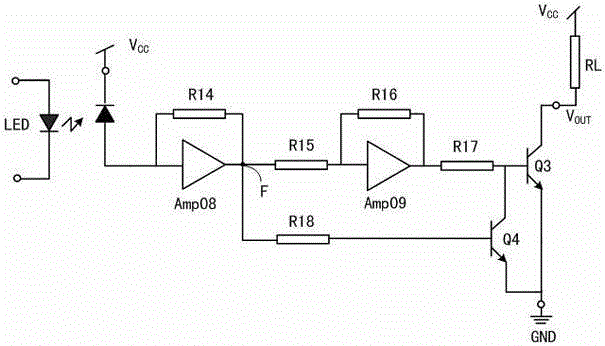

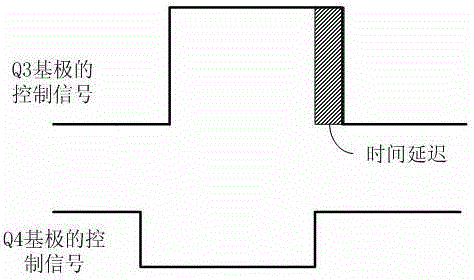

Light receiving circuit

ActiveCN105262548AAccelerated shutdownReduce transmission delayElectromagnetic receiversTime delaysPhotodiode

Provided is a light receiving circuit, comprising four operational amplifiers, eight coupling resistors, an output triode, an auxiliary triode and a photodiode which are connected according to the scheme to respectively form a main line and an auxiliary line, wherein the main line is used for controlling the turn-on / turn-off of triodes; the auxiliary line is used for rapidly discharging the charge stored on the base electrode of the output triode. The invention provides a new light receiving circuit which has the performance of low transmission time delay; meanwhile, the light receiving circuit can reduce the delay difference between two voltage control signals through a second anti-phase amplifier, thereby optimizing output waveforms of the light receiving circuit.

Owner:THE 44TH INST OF CHINA ELECTRONICS TECH GROUP CORP

Switch driving circuit

ActiveUS9287863B2Short transmission delayLow costElectronic switchingElectric pulse generatorDriver circuitControl power

A switch driving circuit for driving a full-controlled power switch is disclosed, including a pulse-width modulation unit, a pulse transformer, an anti-interference module, a pulse-width demodulation unit and a driving-power amplifier. The pulse-width modulation unit converts a driving input signal into a positive-negative narrow pulse-width signal. The anti-interference module is coupled to the secondary side and the positive-negative narrow pulse-width signal includes multiple positive pulses and negative pulses. The anti-interference module filters out the ones from the positive pulses and negative pulses of which the pulse amplitude does not reach an effective threshold, and meanwhile the anti-interference module suppress a common-mode noise caused by a high voltage transient variation at a moment when the full-controlled power switch is turned on or off. The pulse-width demodulation unit converts the filtered positive-negative narrow pulse-width signal into a driving output signal.

Owner:DELTA ELECTRONICS INC

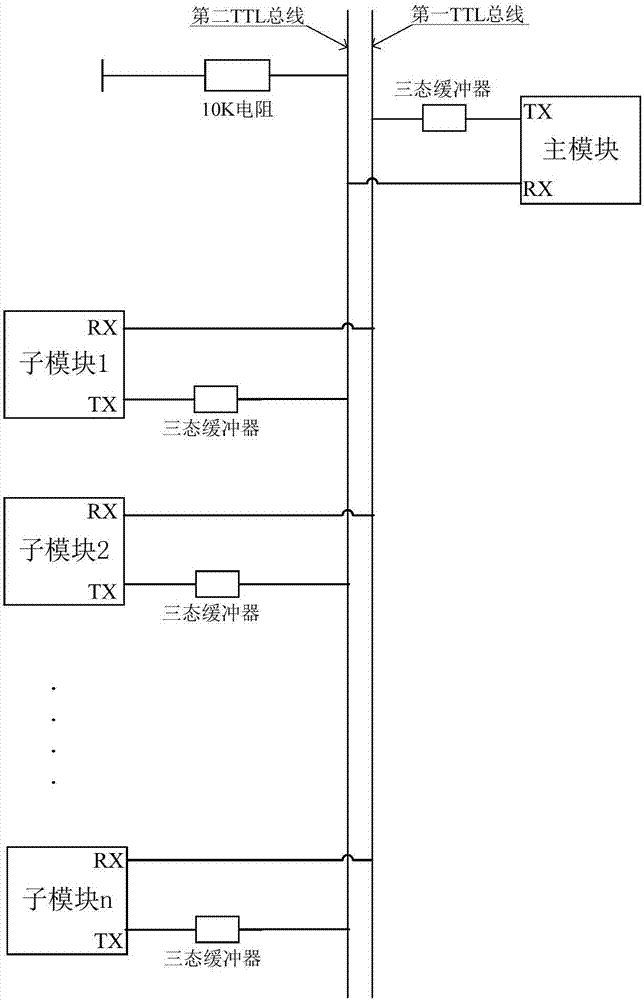

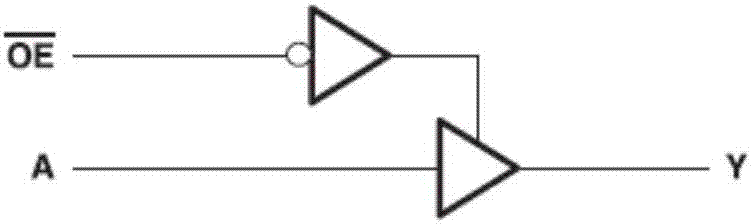

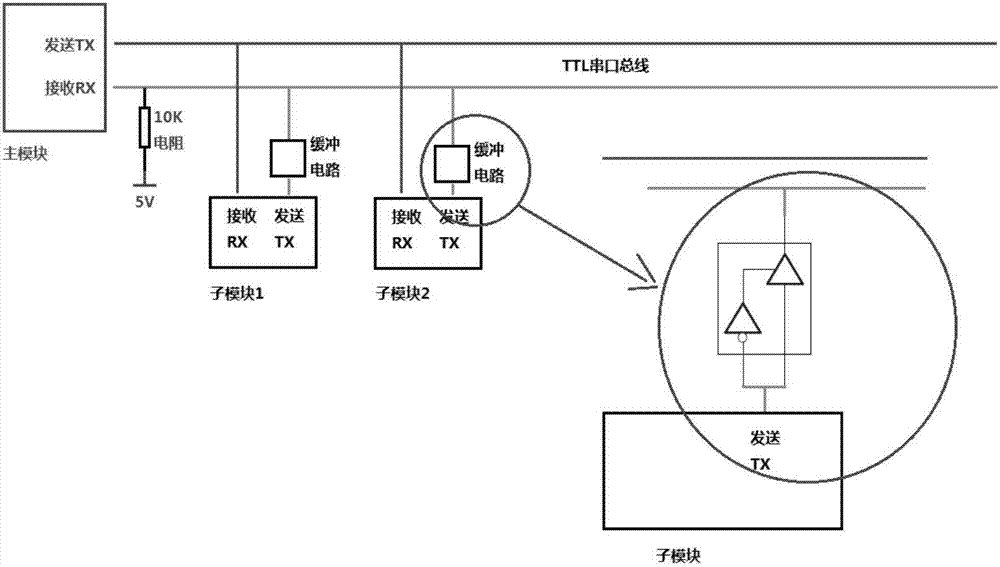

TTL-communication-bus slave-module expanded circuit

PendingCN107229589AUndisturbedFast transmissionElectric digital data processingTelecommunicationsEmbedded system

The invention relates to the field of bus communication, and discloses a TTL-communication-bus slave-module expanded circuit. The TTL-communication-bus slave-module expanded circuit includes TTL buses, tristate buffers, a main module and multiple slave modules, wherein the main module includes transmitting base pins and receiving base pins and is usedfor transmitting request signals and receiving feedback signals, and the multiple slave modules include transmitting base pins and receiving base pins and are used for receiving request signals and transmitting feedback signals. The transmitting base pins of the main module and the receiving base pins of all the slave modules are connected to a first TTL bus, and the receiving base pins of the main module and the transmitting base pins of all the slave modules are connected to a second TTL bus; tristate buffers are arranged between the transmitting base pins of the main module and the first TTL bus, tristate buffers are arranged between the transmitting base pins of all the slave module and the second TTL bus, andthroughthe signal enhancement effect and output enabling function of the tristate buffers, the extension of the slave modules on the communication buses is achieved.

Owner:上海景格信息科技有限公司

Switch tube drive circuit applied to programmable DC power supply

The invention discloses a switch tube drive circuit applied to a programmable DC power supply, the switch tube drive circuit comprises a transformer, a first drive branch and a second drive branch, wherein the first drive branch and the second drive branch are respectively connected with the high potential input end and the low potential input end on primary side of the transformer. Each of the first drive branch and the second drive branch comprises a drive amplification and bootstrap circuit, a blocking and coupling circuit, an acceleration delay circuit, a grid resistance switching circuit and a switching arm circuit. According to the invention, influenced problems including the mutual connection of the switch tubes, switch ringing and the like when the switch tube drives are solved, the circuit can be widely applied to power supply switching, especially in the instrument and equipment with higher requirements than the others, such as the programmable AC power supply, the programmable DC power supply and the like.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

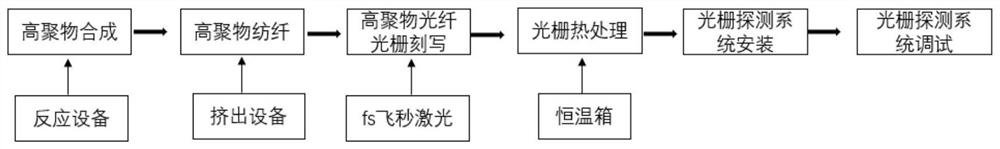

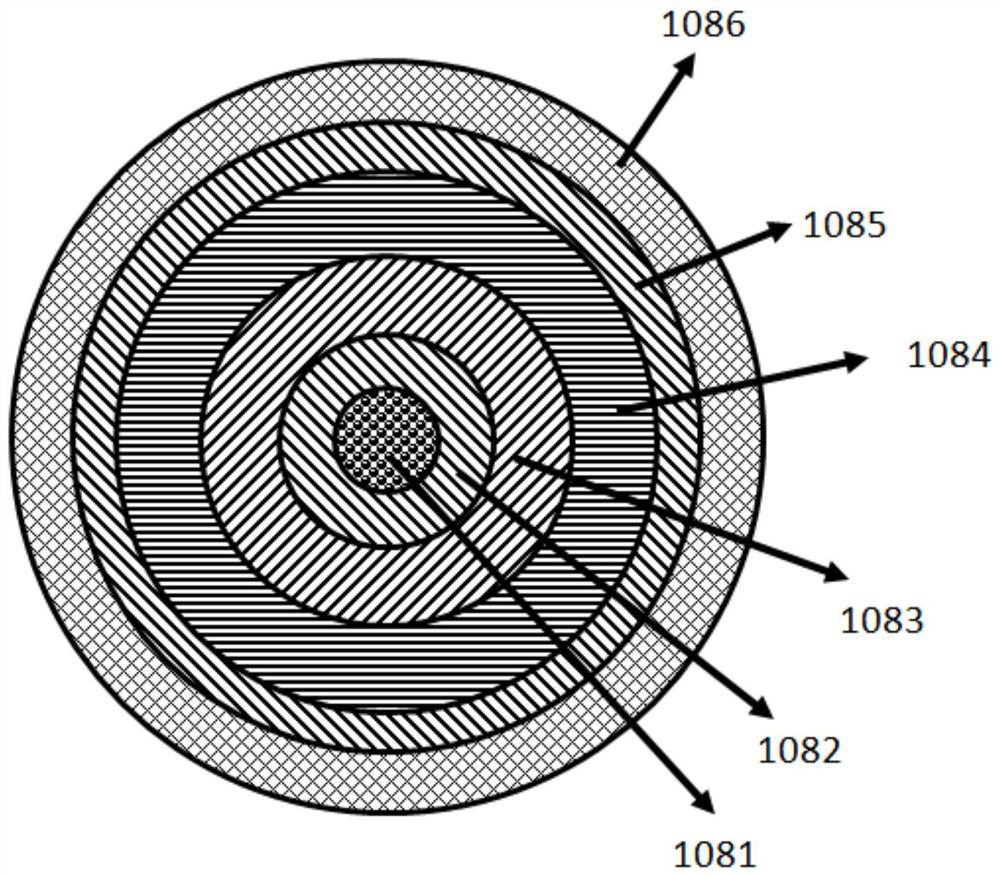

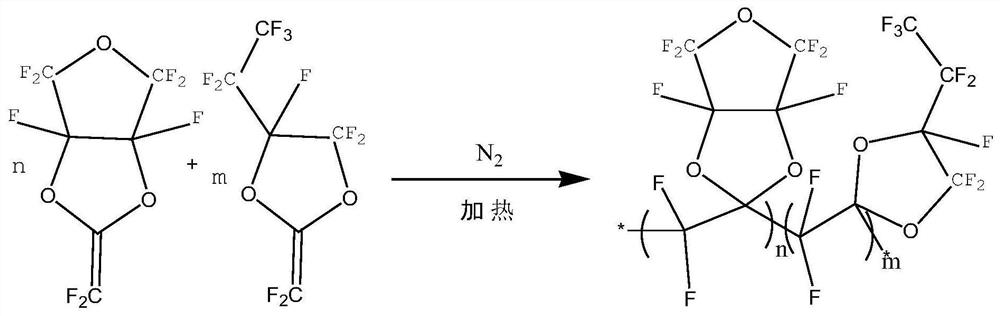

High polymer double-fiber grating micro-detection system and preparation method thereof

InactiveCN112254749AShort transmission delayGood flexibilityConverting sensor output opticallyFiberFemto second laser

The invention relates to a high polymer double-fiber grating micro-detection system and a preparation method thereof. A polymer optical fiber formed by a flexible perfluoro polymer core layer with a high transmission speed and a radial gradient index and a cladding is used, and then a femtosecond laser is used for directly carrying out refractive index modulation on a plane in the axial directionof the optical fiber according to a certain distance, namely, the fiber bragg perfluoro polymer fiber grating is formed by writing or etching, then the grating is installed on a tiny flexible high polymer sleeve, and then the sleeve is fixed on a hard TPU base. Tiny changes of the external environment, like externally applied force and temperature, can change the screw pitch of the grating, so that reflected wavelength displacement changes are generated, and then data analysis is carried out by using photoelectric conversion, a data detection and analysis system and the like to obtain detection parameters.

Owner:浙江启兆光电科技有限公司 +1

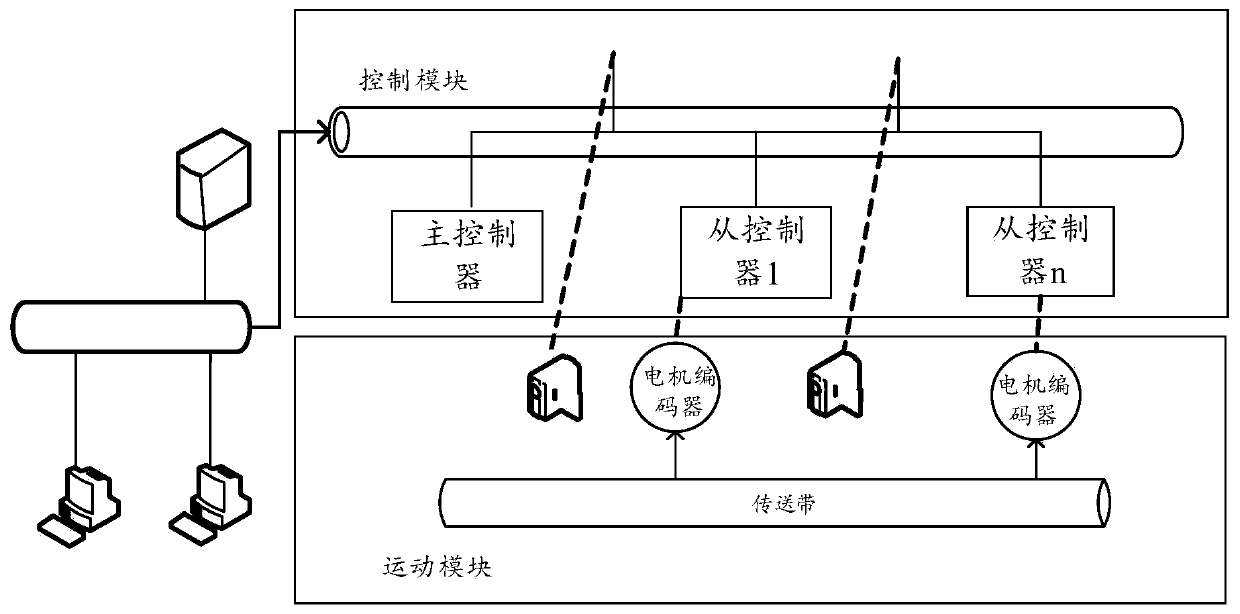

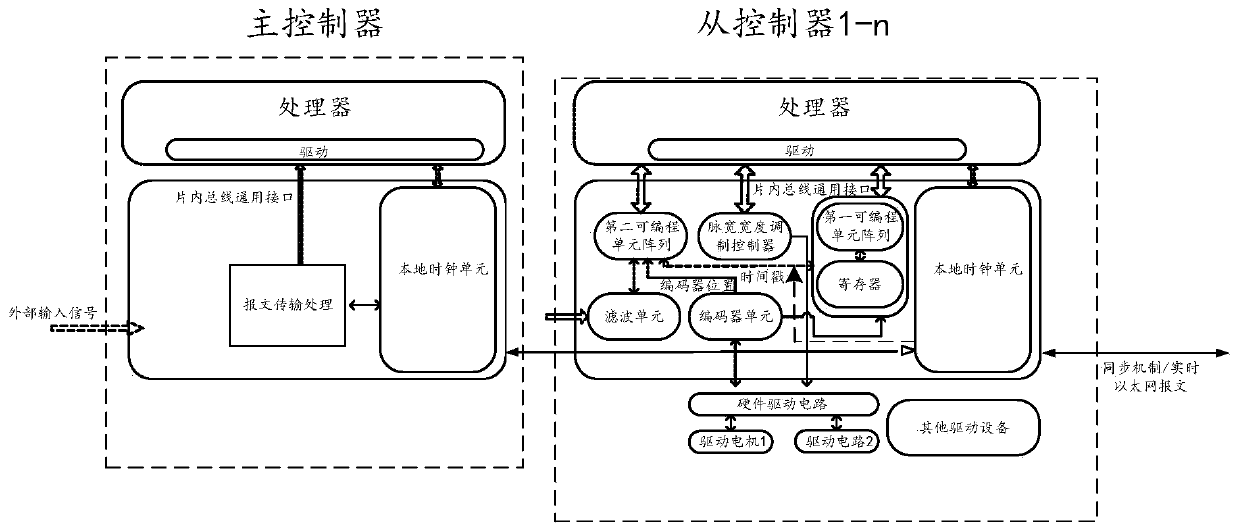

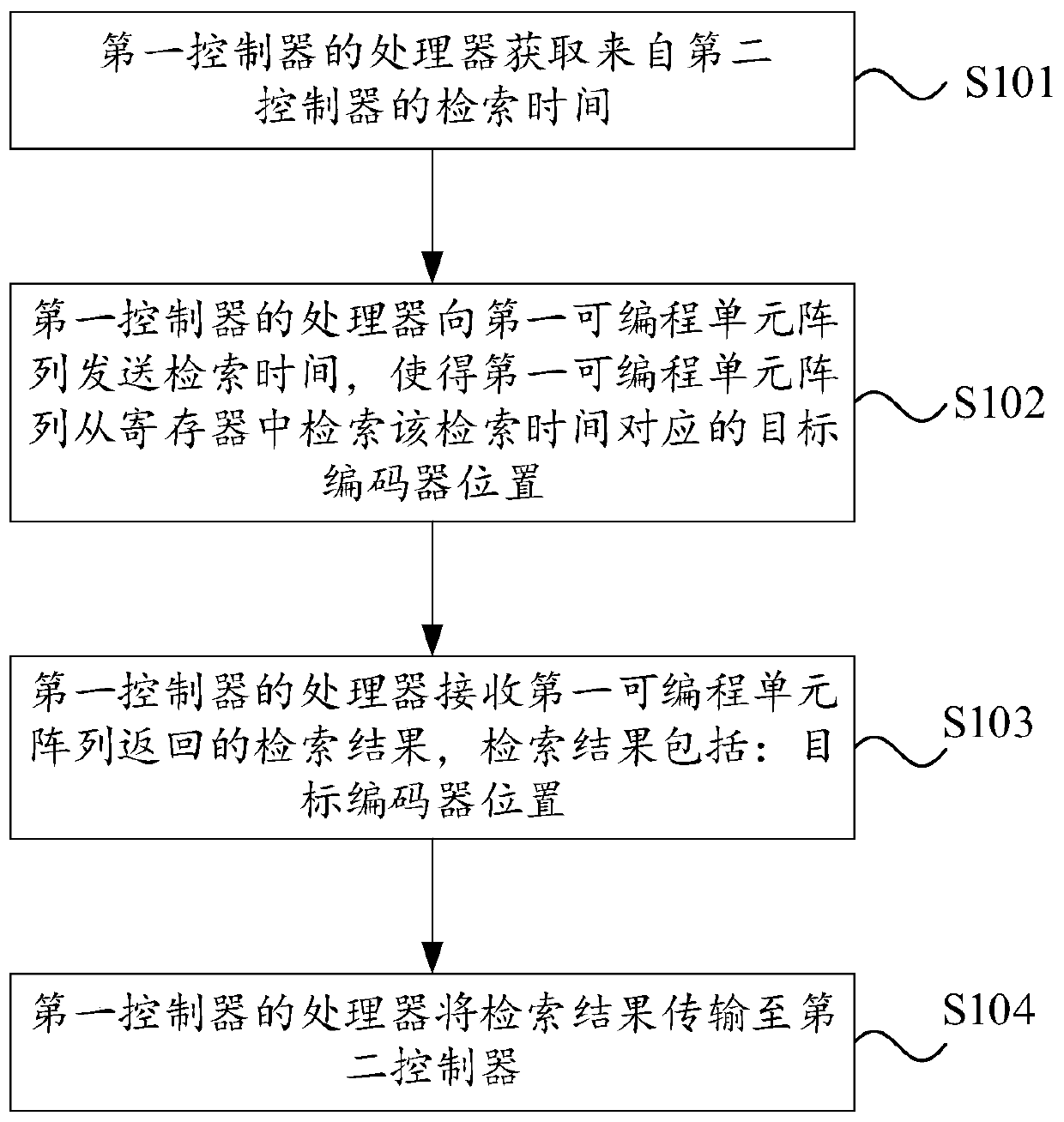

Method for processing position of encoder in distributed system, controller and system

ActiveCN110989475AImprove accuracyEffective positioningProgramme controlComputer controlAutomatic controlFpga chip

The invention provides a method for processing the position of an encoder in a distributed system, a controller and a system, and relates to the technical field of automatic control. The method may comprise the steps that a processor of a first controller acquires retrieval time from a second controller, and sends the retrieval time to a first programmable unit array on an FPGA chip of the first controller, the first programmable unit array is enabled to retrieve a target encoder position corresponding to the retrieval time from a register set on the FPGA chip, and the target encoder positionis returned to the second controller through the processor of the first controller. According to the scheme, efficient positioning of the position of the encoder can be achieved, and the accuracy of the obtained position of the encoder is higher.

Owner:QKM TECH (DONG GUAN) CO LTD

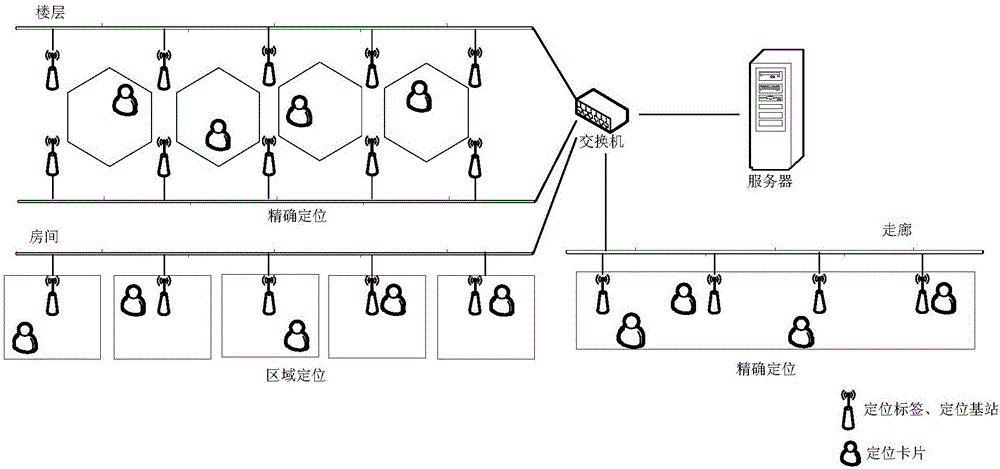

System for intelligently and integrally managing patients in mental hospital

InactiveCN106658706AImprove distribution efficiencyImprove real-time performanceData processing applicationsWireless commuication servicesDual coreMental hospital

The invention discloses a system for intelligently and integrally managing patients in a mental hospital. The system is based on the existing fostering centre digital system platform; furthermore, the system is also combined with a high-precision wireless positioning system and an alarm system; the high-precision positioning system is composed of a network infrastructure and positioning cards; the network infrastructure is composed of all kinds of antennas, positioning labels, positioning base stations and a switch deployed in a monitoring place; the positioning base stations monitor state information of the positioning labels in a receiving range in real time, receive signals from the positioning cards in real time, screen data, and then, upload the data to a server of the fostering centre digital system platform through an appointed transmission link on the switch; the positioning base stations are positioning base stations, which are in double-core high-speed identification by adopting a multi-task FA processing algorithm; and the alarm system and the fostering centre digital system platform are in communication connection. By means of the system disclosed by the invention, the patients in the mental hospital are managed intelligently and integrally; and the system has the characteristics of being high in integration, good in safety, low in power consumption, high in real-time performance and precise to position.

Owner:杭州菲芃科技有限公司

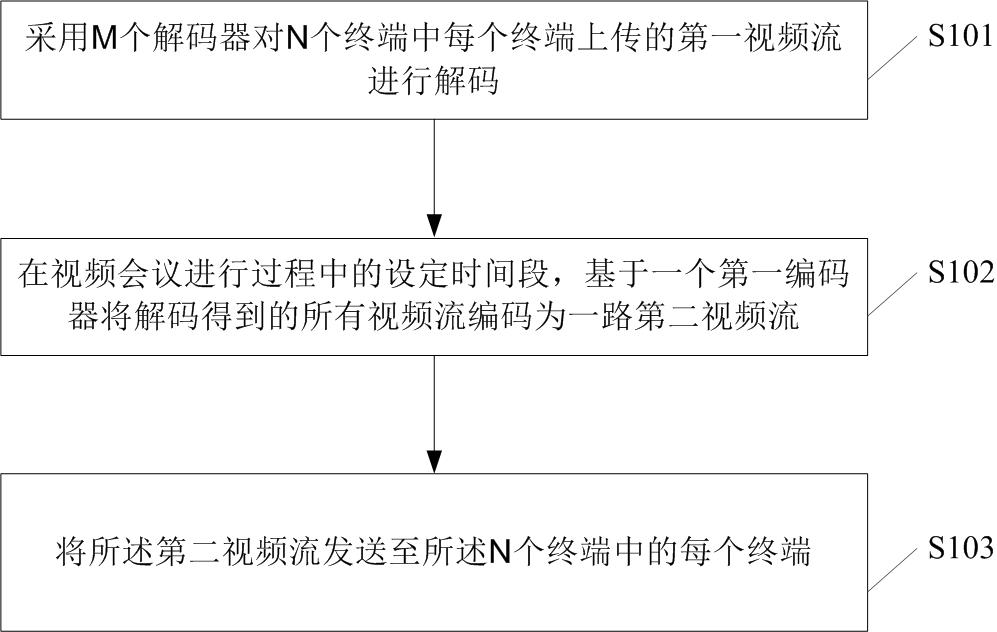

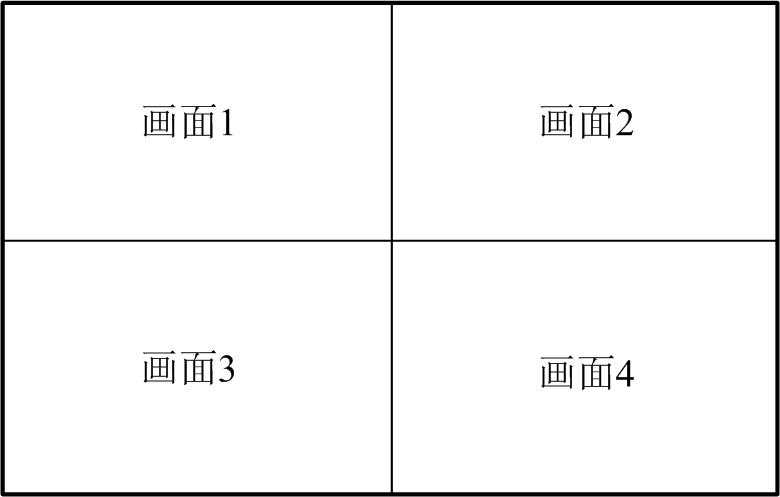

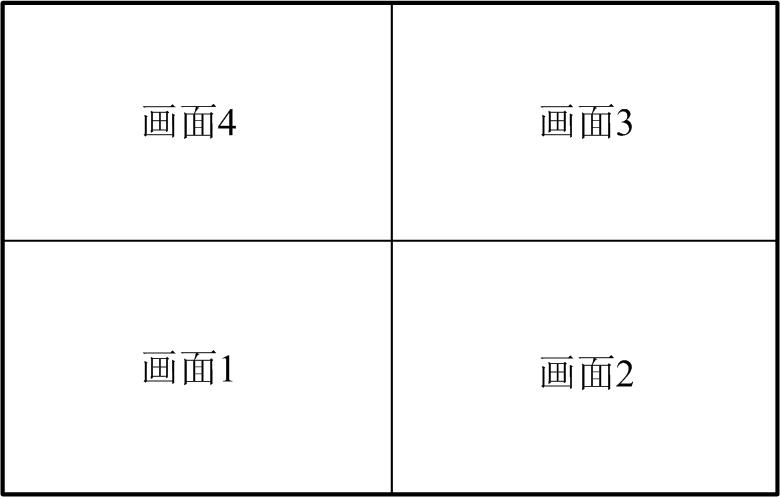

Data transmission method and device, electronic equipment and storage medium

ActiveCN112817913AShort transmission delaySave coding computing resourcesProgram initiation/switchingNatural language data processingComputer hardwareData transmission

The invention provides a data transmission method and device, electronic equipment and a storage medium. The data transmission method comprises the following steps: decoding a first video stream uploaded by each terminal in N terminals by adopting M decoders, wherein M and N are positive integers, M is smaller than or equal to N, and N is larger than or equal to 2; encoding all the decoded video streams into a second video stream based on a first encoder in a set time period in the video conference process; and sending the second video stream to each of the N terminals. In the video conference process, all terminals are enabled to display the same picture in the set time period, so that coding computing resources can be saved, and the transmission delay time of the video conference can be reduced.

Owner:ZHEJIANG HUACHUANG VISION TECH CO LTD

Full high-definition digital image transmission device for ultra-long distance

PendingCN109469805ASmooth transmissionWith shock absorption effectStands/trestlesShock absorbersEngineeringDigital image

The invention discloses a full high-definition digital image transmission device for an ultra-long distance, and relates to the technical field of digital signal transmission. The full high-definitiondigital image transmission device for the ultra-long distance comprises a transmission device, a bearing plate, a supporting plate and a lifting device. The bearing plate comprises a first connectingplate and a second connecting plate, the lower surface of the transmission device is fixedly connected with the upper surface of the first connecting plate, a plurality of first grooves are formed inthe lower surface of the first connecting plate, and supporting springs are fixedly connected with the inner parts of the first grooves. According to the full high-definition digital image transmission device for the ultra-long distance, the bearing plate is composed of the first connecting plate and the second connecting plate, the transmission device has a shock absorbing effect due to the supporting springs, so that the transmission device transmit more stably, the bearing plate can rotate at the top of the supporting plate through a connecting column and a rotating plate, thereby facilitating the adjustment of the direction of the transmission device and the receiving and transmission of signals.

Owner:浙江云来集科技有限公司

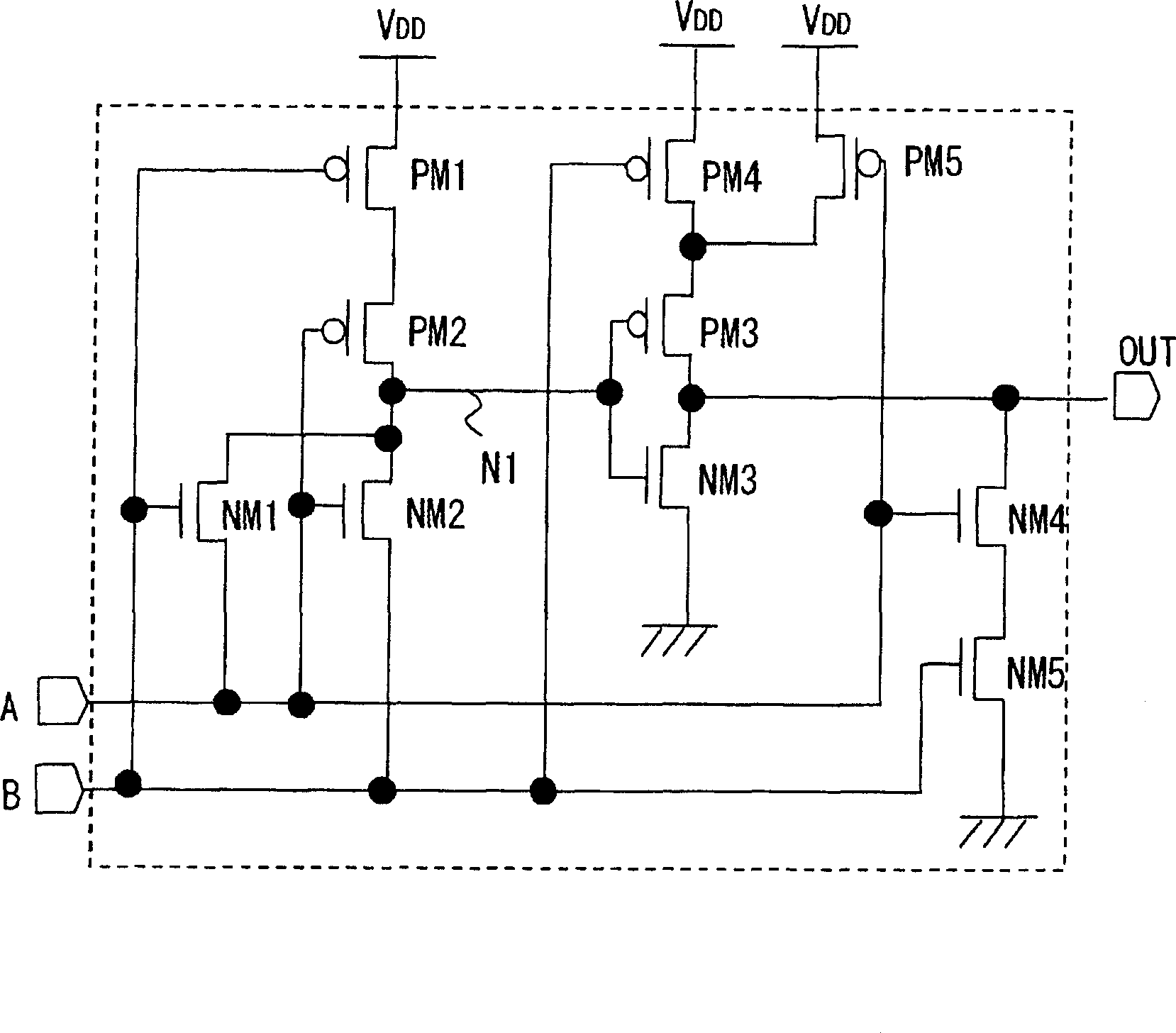

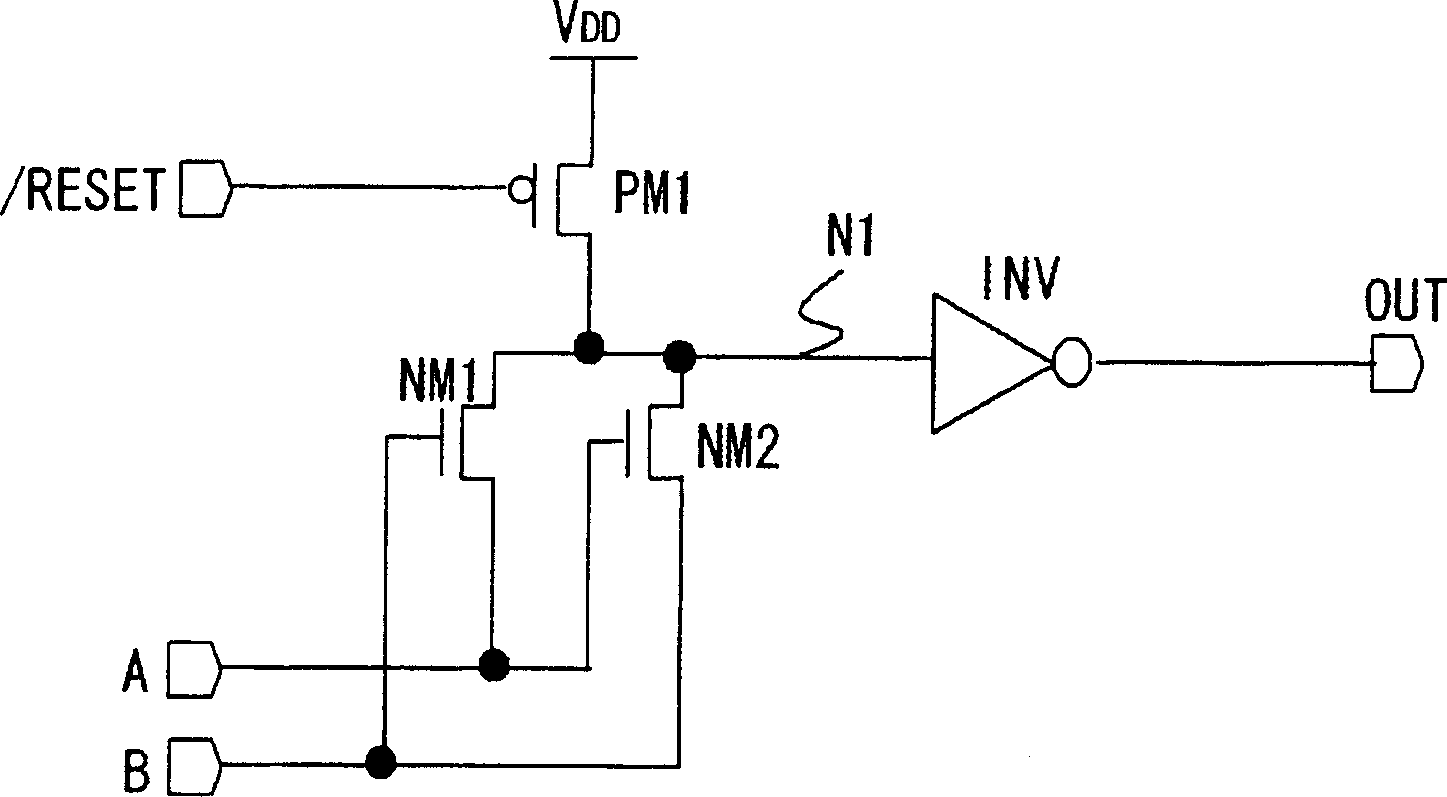

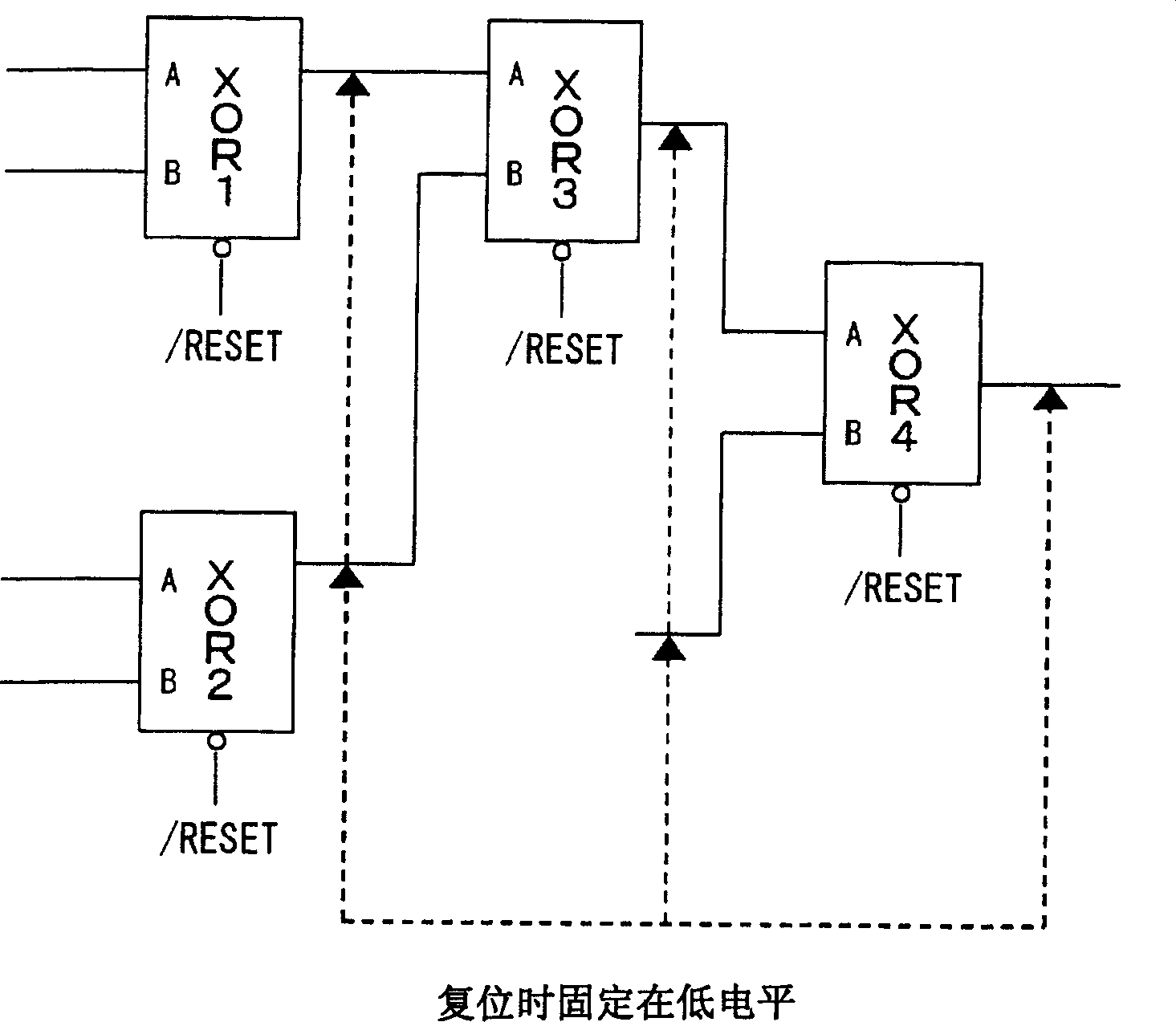

Logic circuit

InactiveCN1783718AReduce the number of seriesShort transmission delayDigital storageDelay compensationCross connectionLogic circuitry

A logic circuit that realizes shortened transmission delay time and can cope with high speed. It has the first and second input terminals (A, B) with logic signals as input, the sources are respectively connected to the corresponding first and second input terminals (A, B), and the gate is connected to the second and first inputs. The first and second MOS transistors (NM1, NM2) that are cross-connected to the terminals (B, A), and the drains of the first and second MOS transistors (NM1, NM2) are connected in common, and have the first power supply VDD and the first and second MOS transistors. The drains of the transistors (NM1, NM2) are connected to the common node (N1), the gate receives the reset signal ( / RESET), and the MOS transistor (PM1) that is turned on at reset also has an input terminal connected to the common node N1 inverter (INV).

Owner:NEC ELECTRONICS CORP

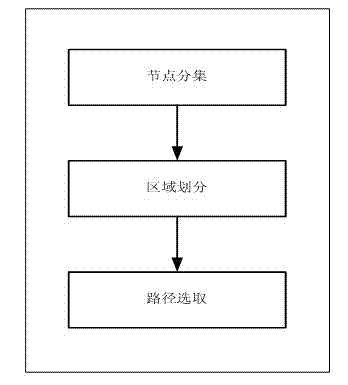

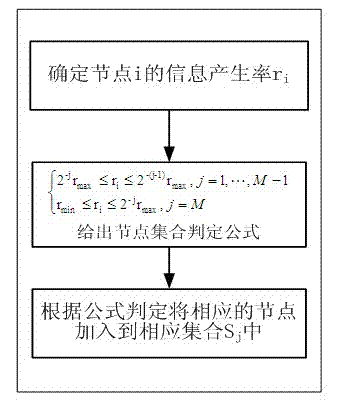

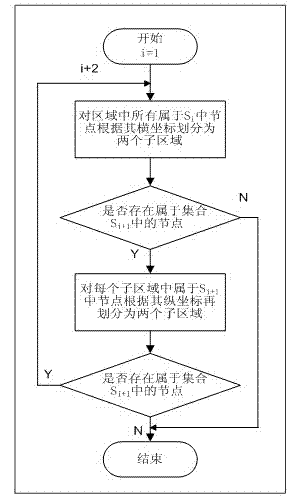

Routing selection method based on node property in social transportation in opportunistic network

ActiveCN102202000BShort transmission delayImprove adaptive functionData switching networksWireless communicationPathPingTrunking

The invention discloses a routing selection method based on node property in social transportation in an opportunistic network. The method comprises the following steps of: diversifying nodes with different data generating rates in a network in specific to all nodes which periodically access the network in the conventional opportunistic network routing technology; zoning nodes in a topological diagram according to different positions of the nodes in each set; and determining a path access strategy of a relay node according to different data generating rates and the zonal positions of the nodes. In the method, different access strategies are adopted for different nodes based on different properties of the nodes in the network, so that the total delay time of all nodes in the network can beshortened, high time delay of nodes with high data generating rates and resource waste caused by nodes with low data generating rate due to the adoption of the same access method are avoided, and thedefects of the conventional routing technology are overcome.

Owner:重庆信科设计有限公司

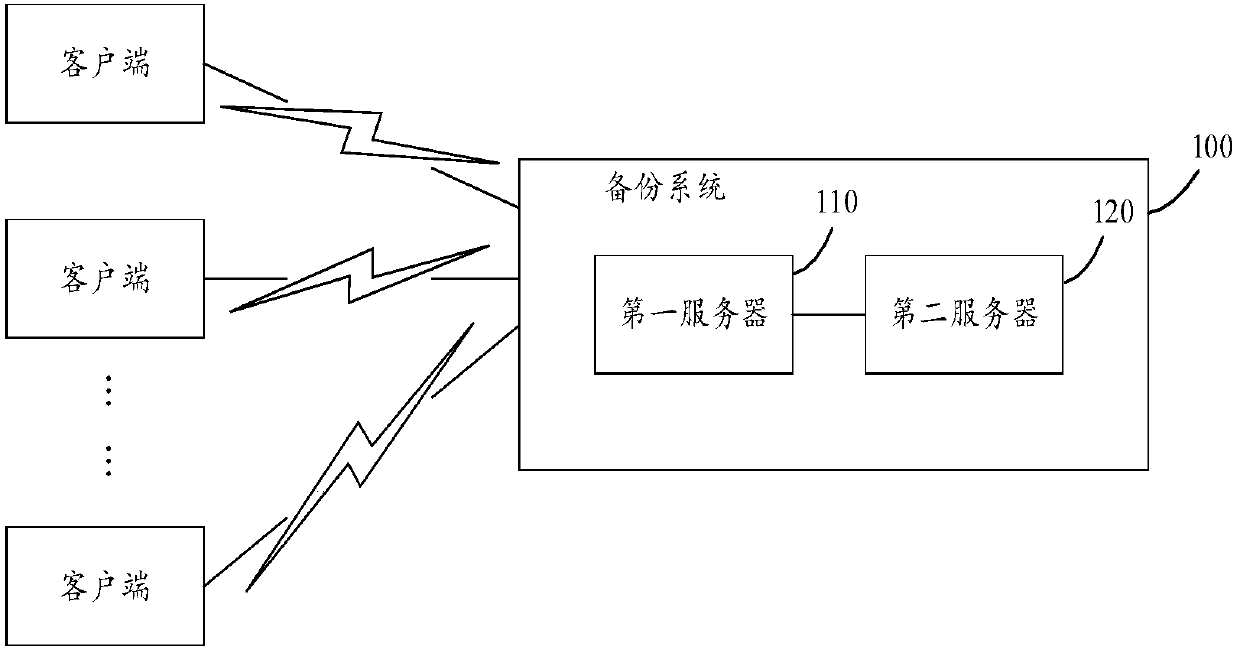

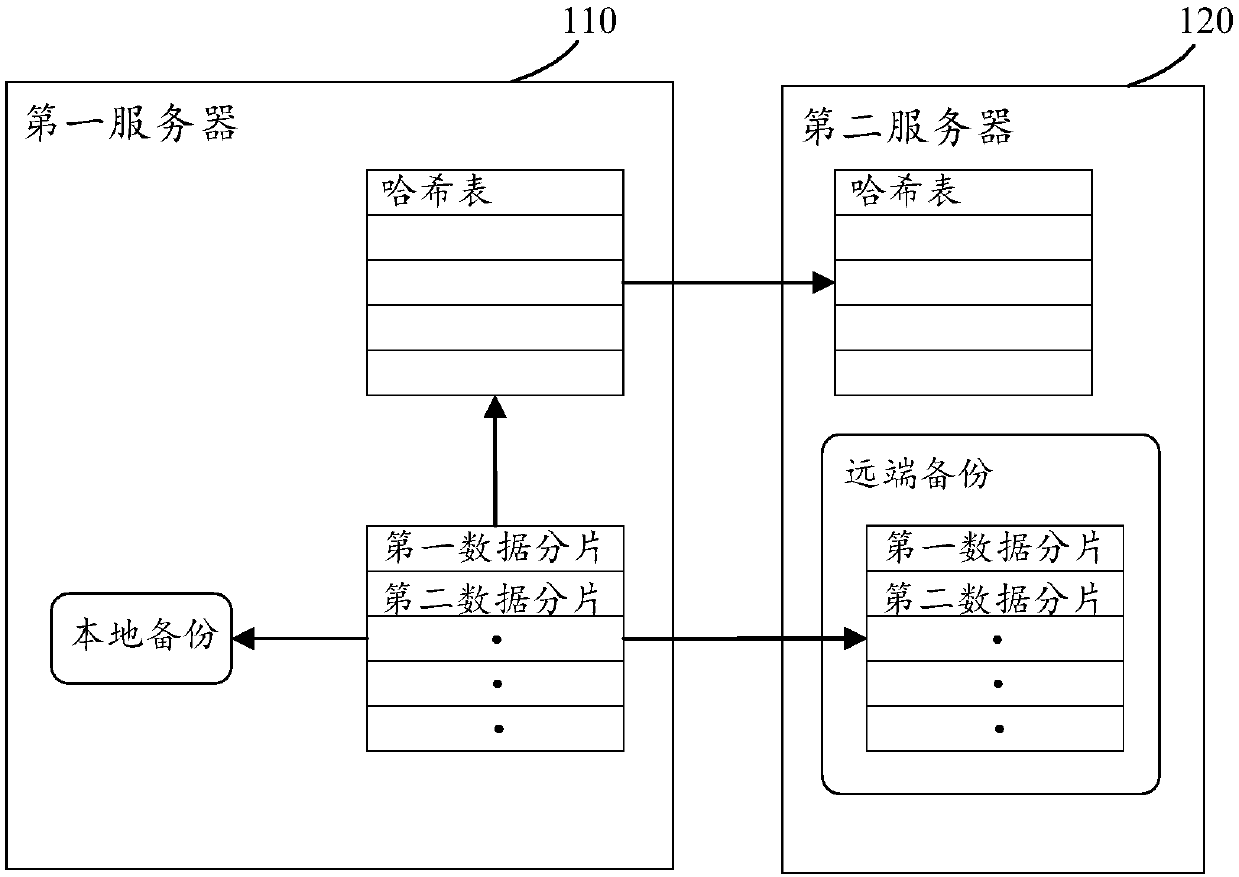

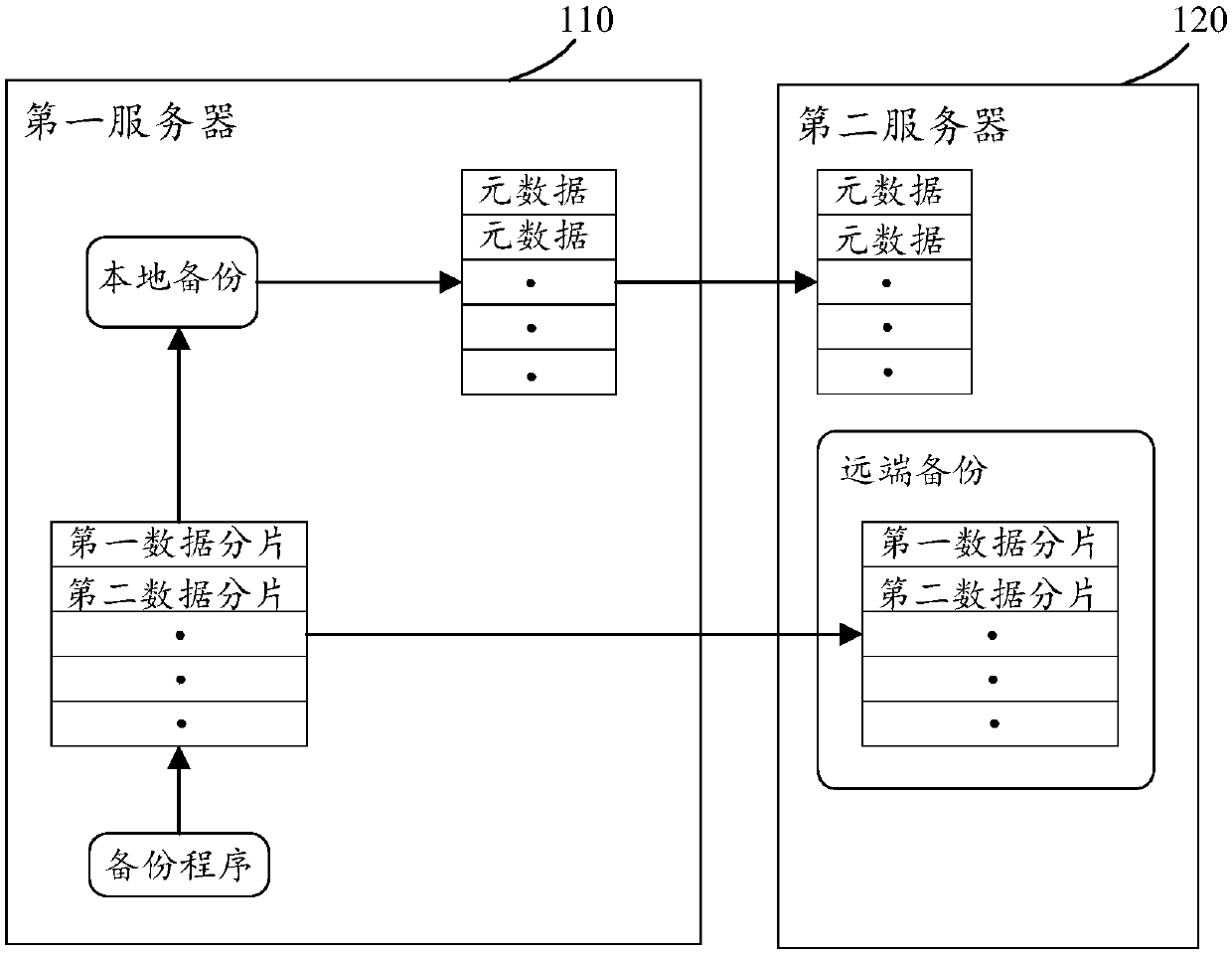

Data recovery method, device and system

ActiveCN109697136AImprove recovery efficiencyReduce data volumeRedundant operation error correctionRecovery methodData recovery

The embodiment of the invention provides a data recovery method, device and system. And the first server receives the metadata of the first data fragment sent by the second server, wherein the metadata of the first data fragment comprises first indication information which is an identifier or a storage position of a backup data fragment of the first data fragment in the first server. And when thefirst server confirms that the first server does not store the backup data fragment of the first data fragment in the first server according to the metadata of the first data fragment, the first server requests the second server for the backup data fragment of the first data fragment in the second server, and stores the backup data fragment of the first data fragment. The data size of the identification of the backup data fragment of the first server or the storage position of the backup data fragment of the first server stored in the metadata is smaller than the data size of the hash value. Therefore, few network resources are used for transmitting a large amount of metadata from the second server, and the data recovery efficiency is improved.

Owner:HUAWEI TECH CO LTD