Logic circuit

A logic circuit and power supply technology, applied in the field of logic circuits, can solve the problems of longer transmission delay time and inability to cope with high speed, and achieve the effect of suppressing time lag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

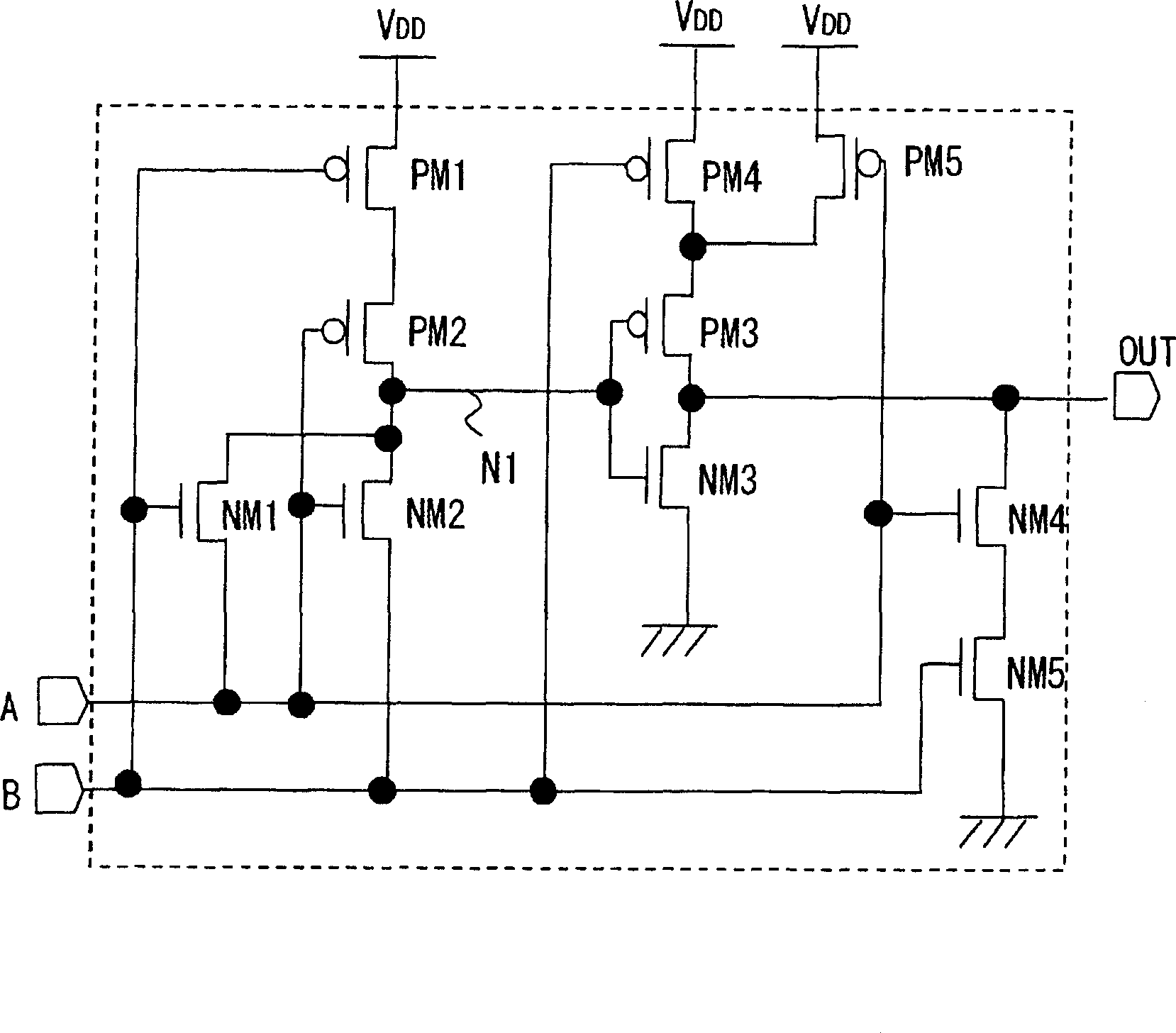

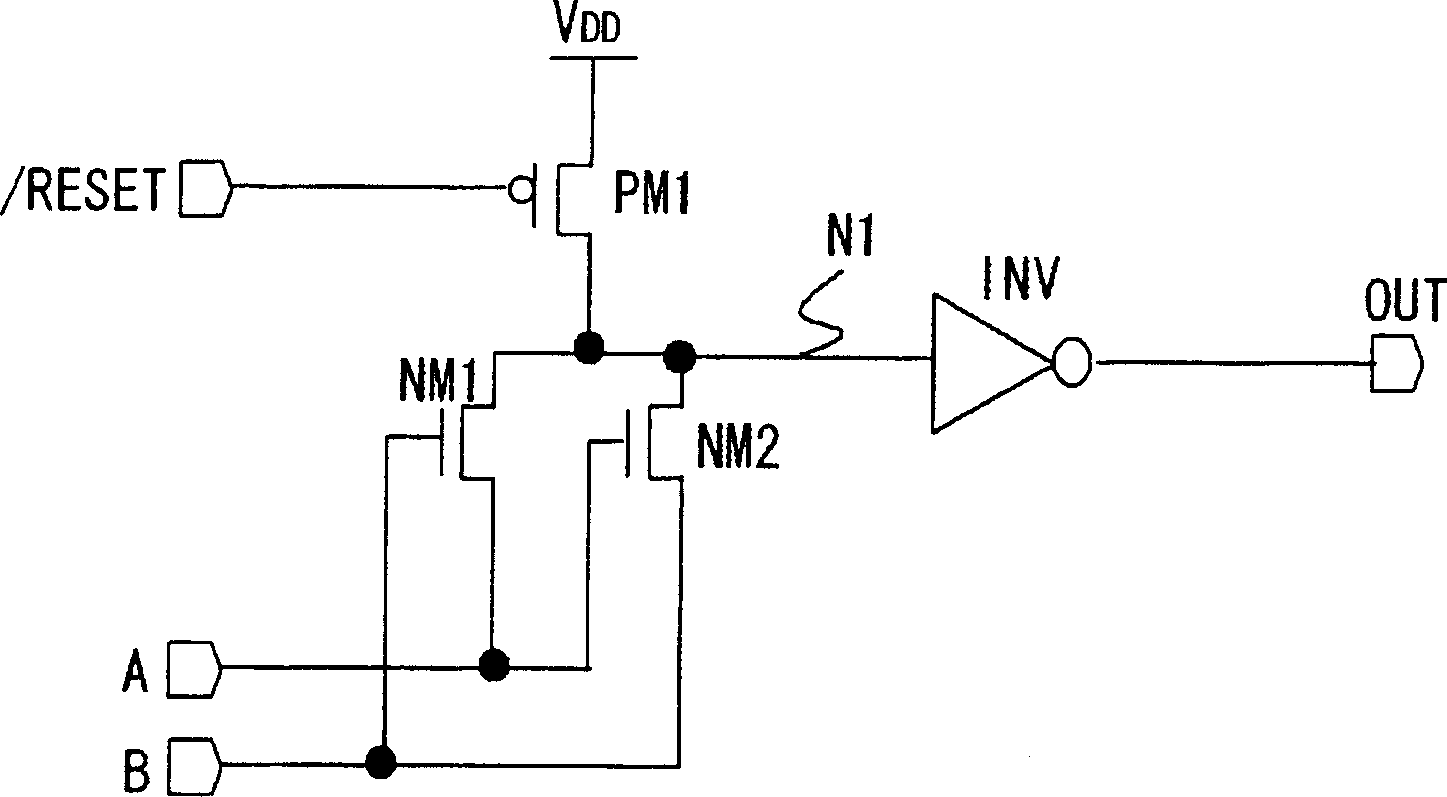

[0039] figure 1 It is a figure which shows the structure of the logic circuit of one Example of this invention. refer to figure 1 , an embodiment of the present invention has input terminals A and B respectively using logic signals as inputs, has sources connected to corresponding input terminals A and B respectively, and an nMOS transistor NM1 whose gate is cross-connected to input terminals B and A , NM2, and the drains of the nMOS transistors NM1 and NM2 are connected in common. Furthermore, there are pMOS transistors PM1, PM1, and NM1 connected in series between the power supply VDD and a node (referred to as a "common node") N1 at which the drains of nMOS transistors NM1 and NM2 are connected in common, and their gates are connected to input terminals B and A, respectively. PM2 also has an inverter composed of an nMOS transistor NM3 whose source is connected to ground and a pMOS transistor PM3 whose drain is connected to the drain of the nMOS transistor NM3 and whose ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More