High-performance full-adder arithmetic element circuit

A technology of arithmetic unit and full adder, which is applied in the direction of logic circuit with logic function, can solve the problem of no improvement of full adder, and achieve the effect of fast working speed, small transmission delay time, and easy selection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

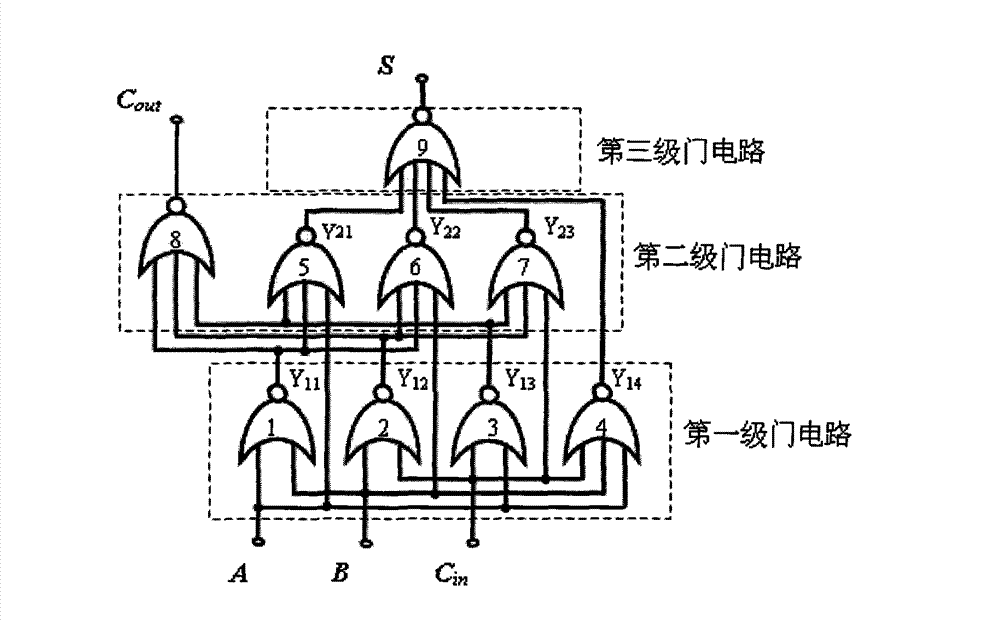

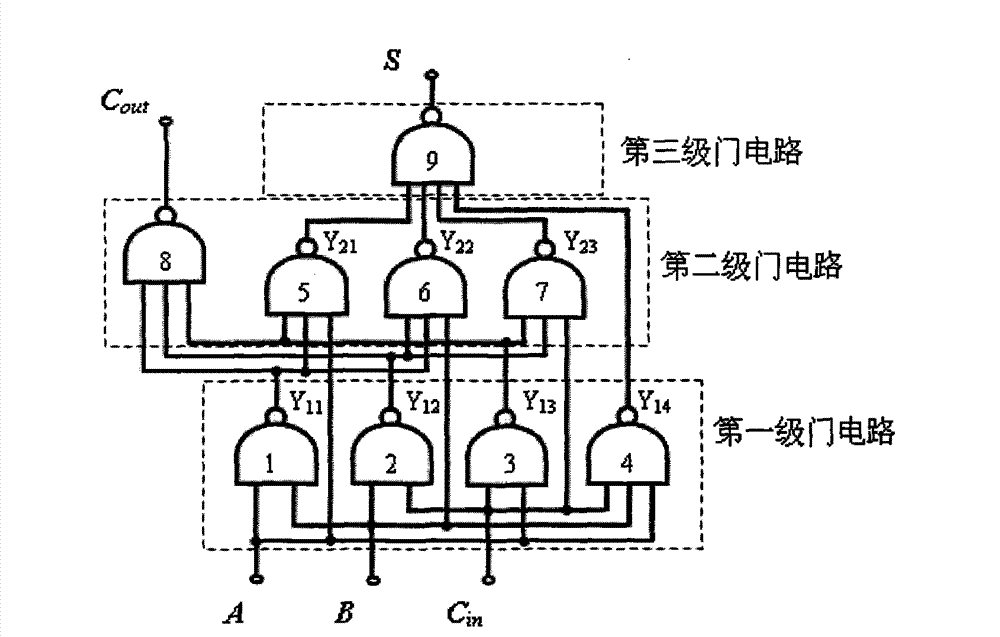

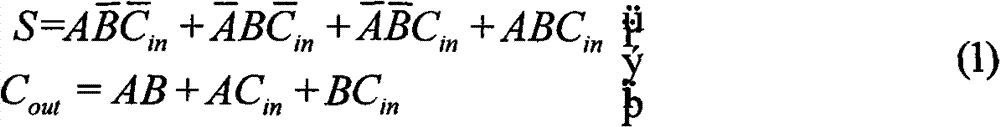

[0028] According to one embodiment of the present invention, a full adder operation unit circuit composed of NOR gates is provided, such as figure 1 shown. The full adder operation unit circuit includes three stages of gate circuits, a total of nine NOR gates; the first stage gate circuit is composed of four gates of NOR gates 1, 2, 3, and 4, and the second stage gate circuit is composed of NOR gates 5, 6, 7, and 8 are composed of four gates, and the third gate circuit is composed of NOR gate 9.

[0029] Among them, the NOR gate 1 in the first-stage gate circuit has two input terminals and one output terminal, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More