Soft error reinforcement method applied to combinational logic circuit

A combined logic circuit and soft error technology, applied to logic circuits with logic functions, etc., can solve problems such as large area costs, and achieve the effects of high reliability assurance, flexible reinforcement solutions, and efficient reinforcement solutions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

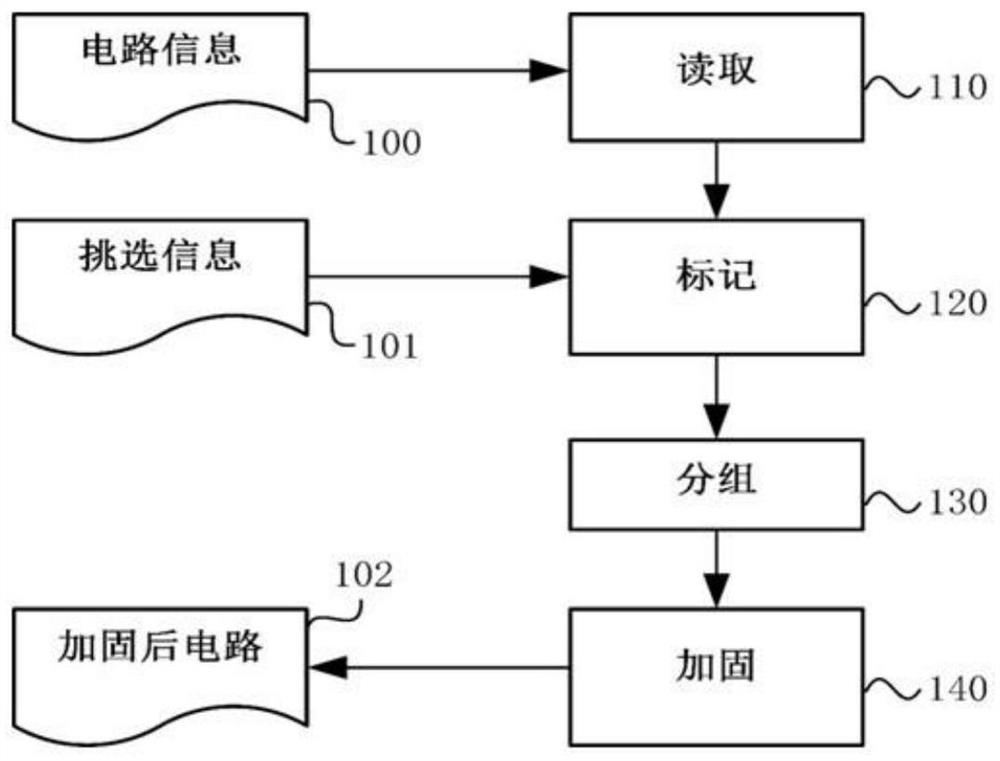

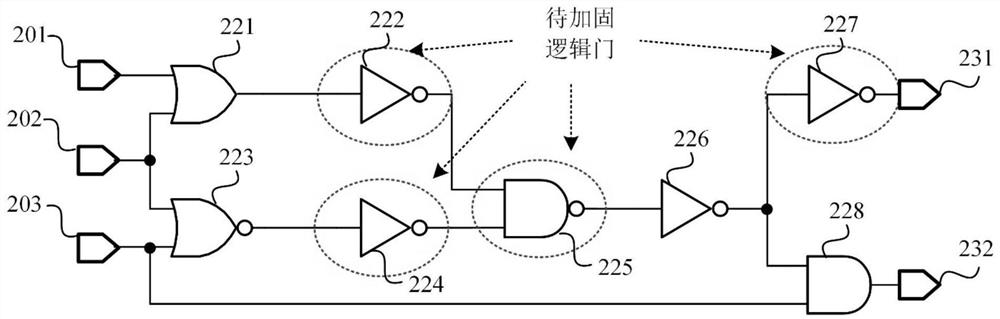

[0067] Embodiment: a kind of combined circuit strengthening method comprises four processes, such as figure 1 shown. They are circuit reading process (110), logic gate marking process (120) to be strengthened, logic gate grouping process (130) and strengthening process (140) to be strengthened respectively. figure 1 Among them, 100 is the target reinforcement circuit, and the target circuit of this embodiment is figure 2 shown. figure 1 Among them, 101 is the logic gate information to be strengthened selected in the target circuit, and the logic gate to be strengthened in this embodiment is figure 2 Logic gates marked with red circles in . figure 1 In 103 is the output circuit after the target circuit is strengthened by the strengthening method of the present invention.

[0068] In this embodiment, the circuit reading process specifically includes the following steps:

[0069] (1) read in figure 2 In the combinational circuit shown, the whole circuit is regarded as a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com