Chip package structure

A chip packaging structure and chip technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of increased power consumption, high thickness of the packaging structure, and increased resistance, so as to reduce the resistance value, reduce The effect of the overall width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

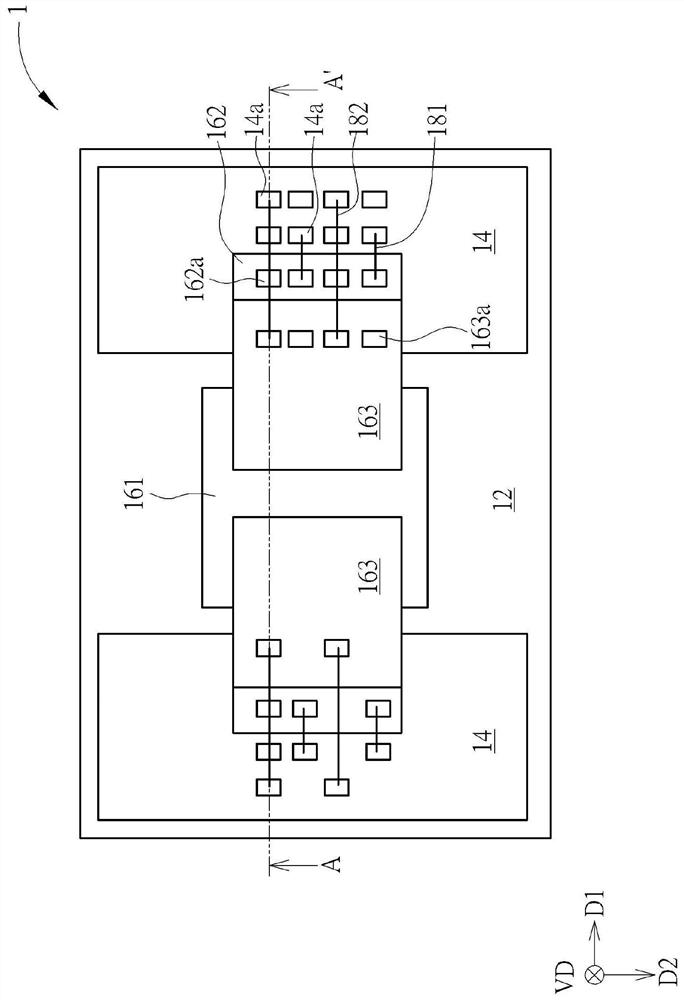

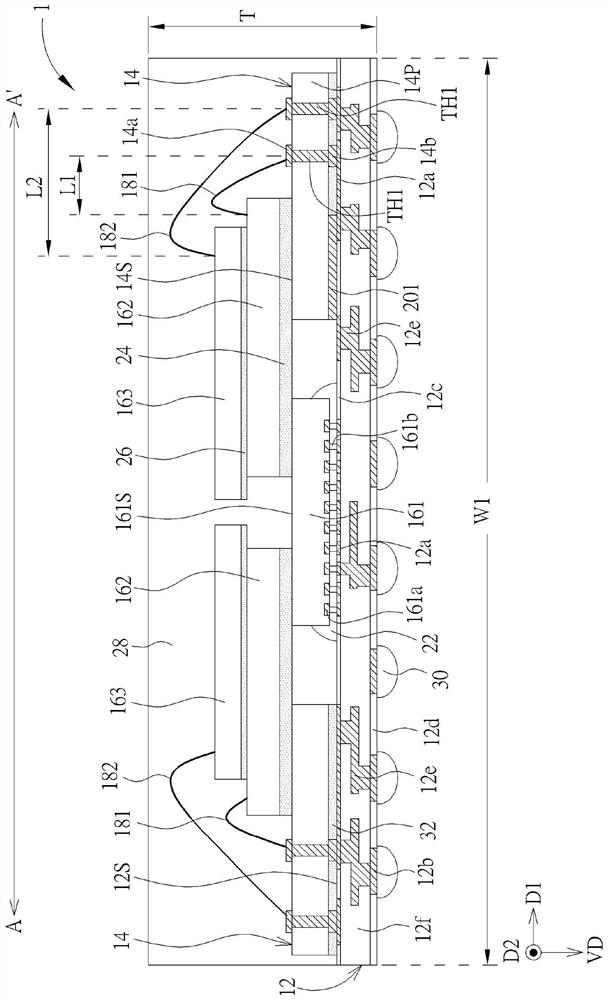

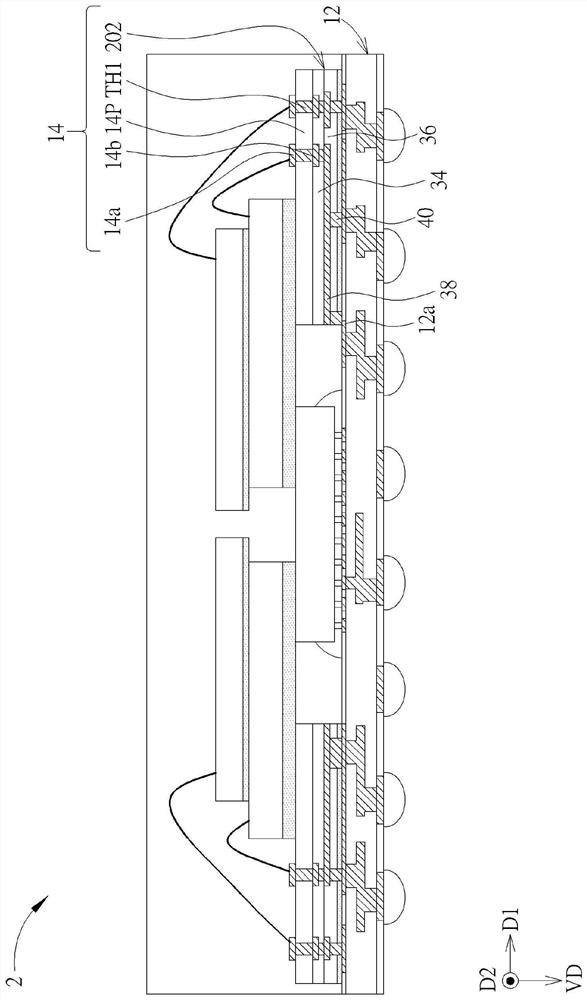

[0046] The present invention can be understood by referring to the following detailed description in conjunction with the drawings. It should be noted that, in order to make the readers easy to understand and the drawings are concise, the drawings of the present invention only draw at least a part of the chip package structure, and the drawings Certain elements in the formulas are not drawn to actual scale. In addition, the quantity and size of each element in the drawings are only for illustration, and are not intended to limit the scope of the present invention.

[0047] Throughout the specification and scope of the appended claims, certain terms will be used to refer to particular elements. Those skilled in the art should understand that electronic device manufacturers may refer to the same element by different names. This document does not intend to distinguish between those elements that have the same function but have different names. In the description and claims belo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More