Semiconductor memory circuit

A storage circuit and semiconductor technology, applied in the direction of semiconductor devices, circuits, information storage, etc., can solve problems such as difficult manufacturing and processing, and achieve the effect of shortening the access time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] Embodiments of the present invention will be described below with reference to the drawings.

[0050] (Embodiment 1)

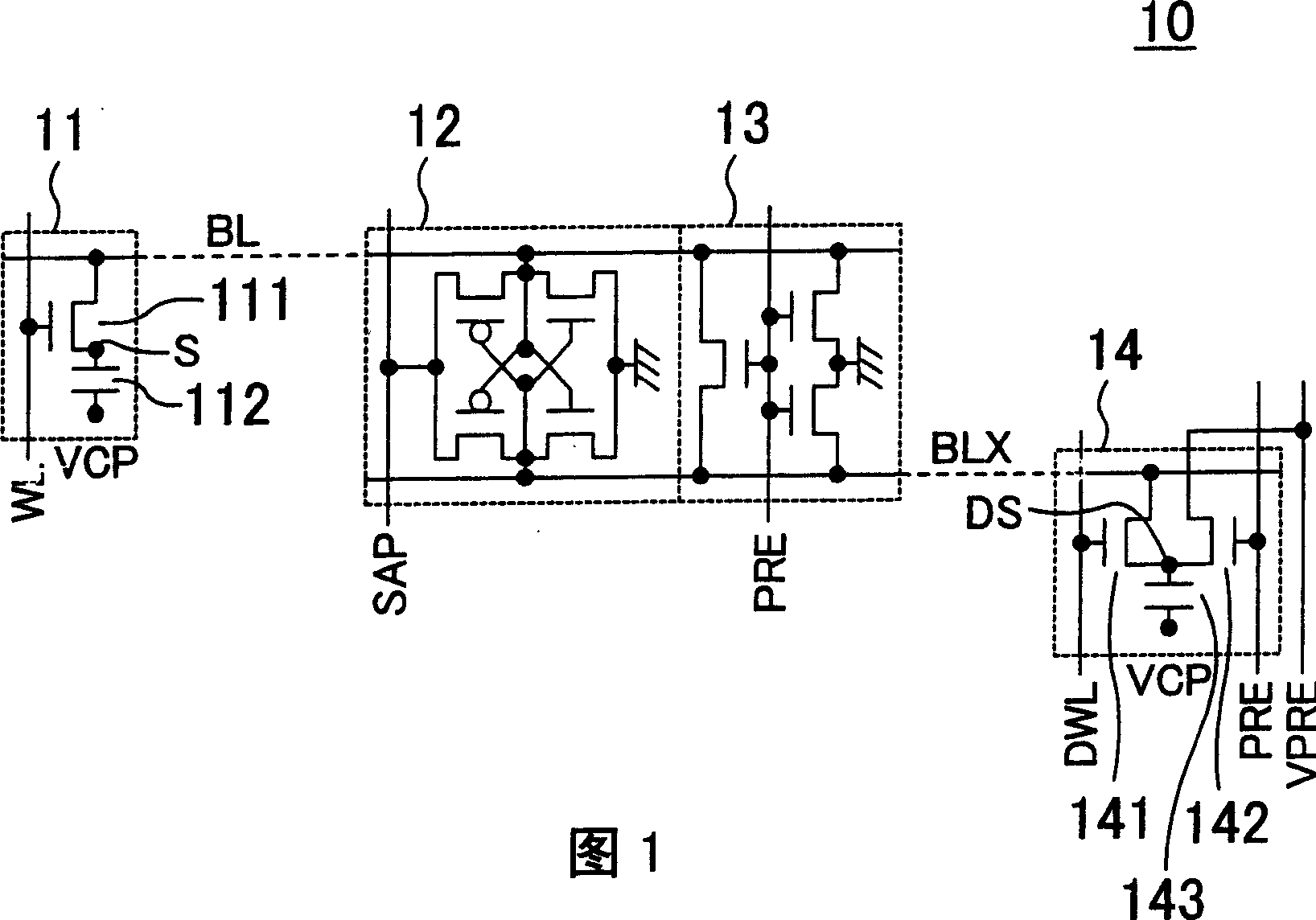

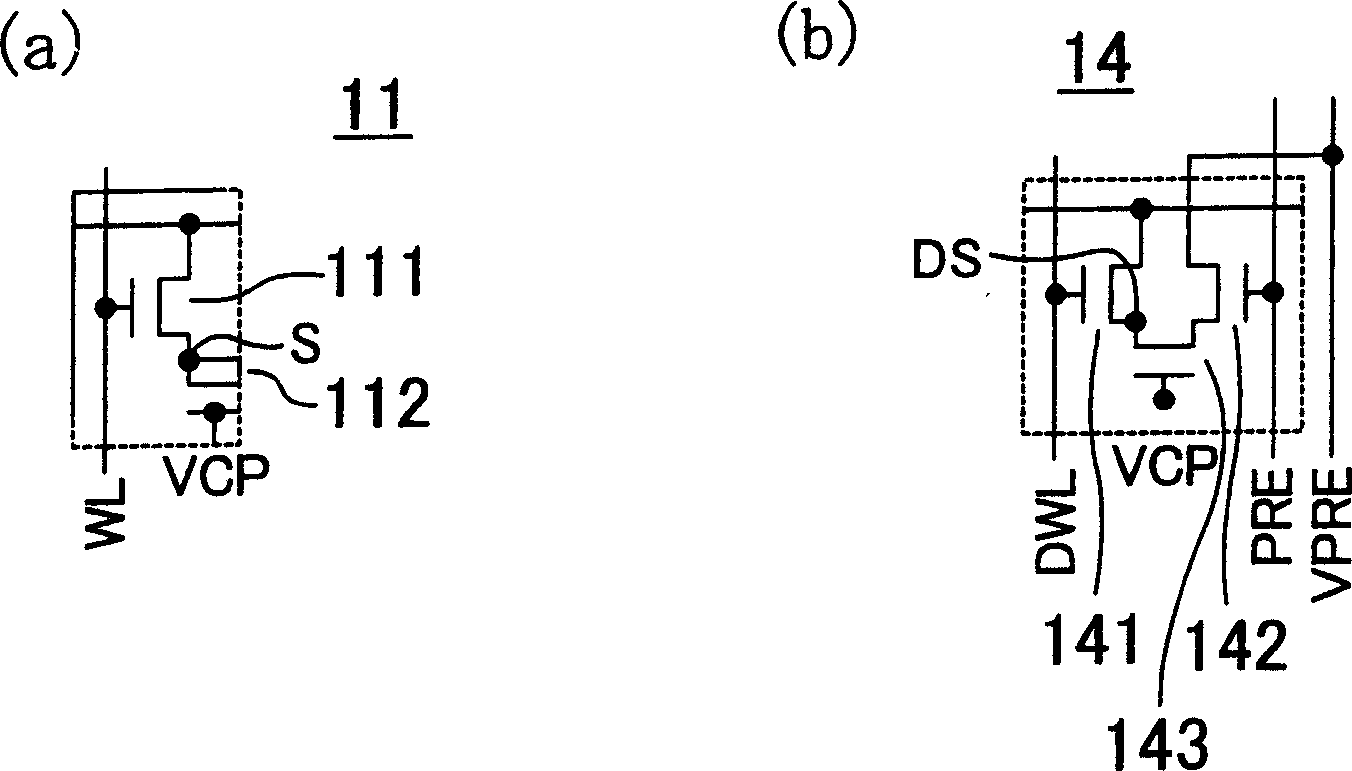

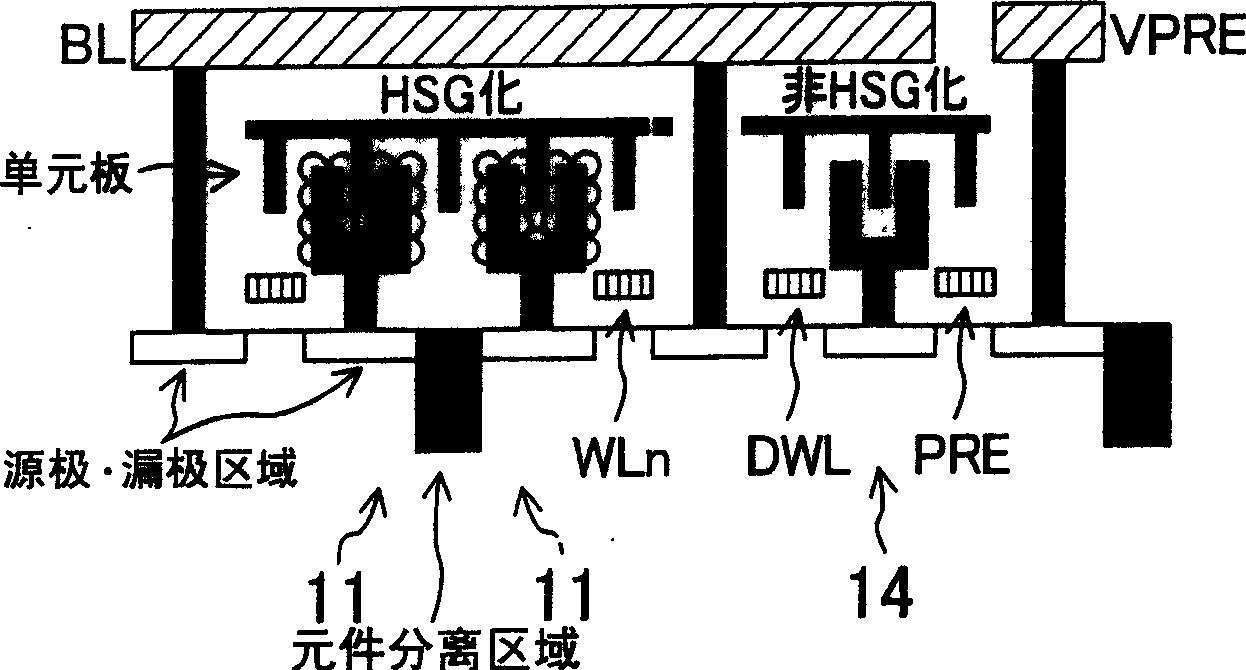

[0051] Fig. 1 shows a circuit configuration of a semiconductor memory circuit according to Embodiment 1 of the present invention. The DRAM 10 as the semiconductor memory circuit of this embodiment is composed of NMOS, and includes a memory cell 11 provided at the intersection of the word line WL and the bit line BL, and a CMOS sense amplifier 12 for detecting and amplifying the potential difference between the pair of bit lines BL and BLX. , a precharge circuit 13 for the bit line pair BL, BLX, and a dummy cell 14 disposed at the intersection of the dummy word line DWL and the bit line BLX.

[0052] The memory cell 11 is a one-transistor type cell constituted by an NMOS transistor 111 and a main capacitor 112 . The NMOS transistor 111 is turned on when the word line WL is activated when the bit line BL is inactive, and electrically connects the main c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More