Multi-thread parallel processing sigma-delta ADC

A technology of digital conversion and delta-sigma, applied in the direction of analog-to-digital converter, analog-to-analog conversion, code conversion, etc., can solve the problems of high-order delta-sigma ADC difficulties and instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The detailed content of the description is an example of the best mode of the present invention for illustration, but the present invention is not limited to the following example or its operation mode.

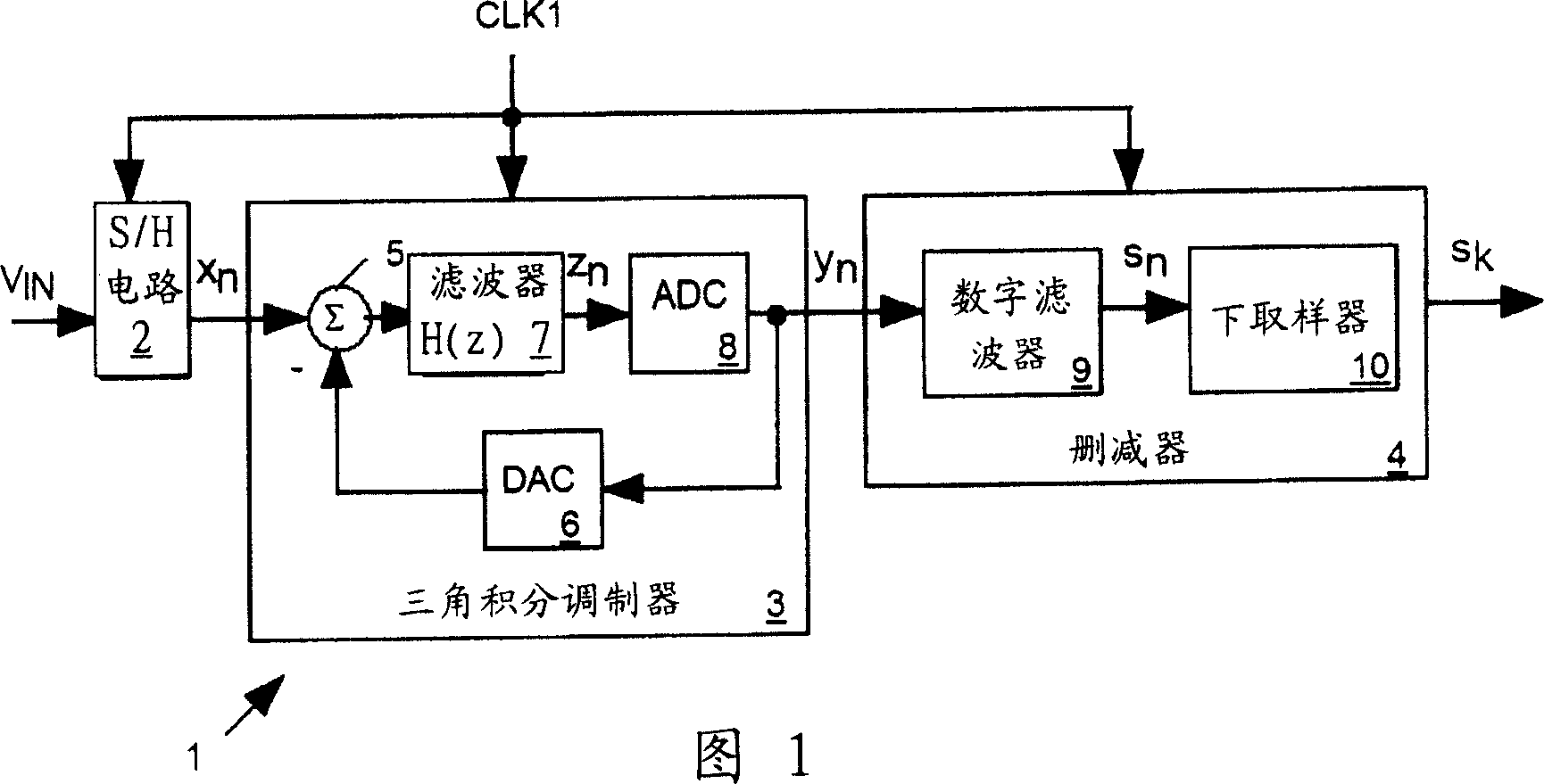

[0052] FIG. 4 is a block diagram of a delta-sigma ADC according to a preferred embodiment of the present invention. The delta-sigma ADC30 is used to generate a representative analog input signal V IN The time-varying behavior of the digital output sequence s k . ADC30 includes S / H circuit 31, according to the clock edge of sampling clock signal CLK1, and with much higher than V IN bandwidth sampling rate periodically on the input signal V IN samples to produce a sequence of discrete analog samples x n . Serial / parallel (Serial / parallel, S / P) converter 32 is to deinterleave sampling sequence x n (n=(1,2,...,}), to form two analog sampling sequences x 2m+1 and x 2m , where x 2m+1 is given by the sequence x n All elements in which n is an odd number, and x 2m T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More