Logic gate with a potential-free gate electrode for organic integrated circuits

A logic gate, organic technology, applied in logic circuits using specific components, logic circuits, circuits using semiconductor devices, etc., to achieve the effect of improving conversion properties, rapid and stable conversion or action, and space needs to be improved

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The same reference numerals are used for the same or similar elements in the specification and drawings.

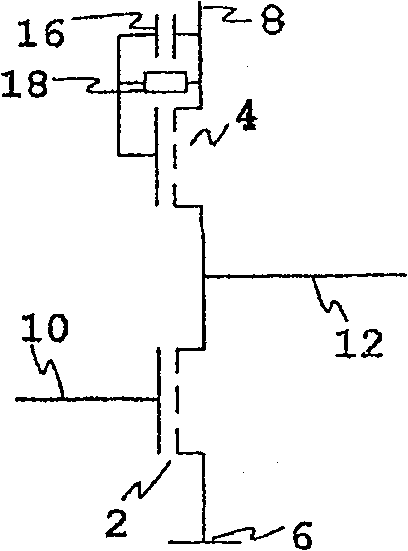

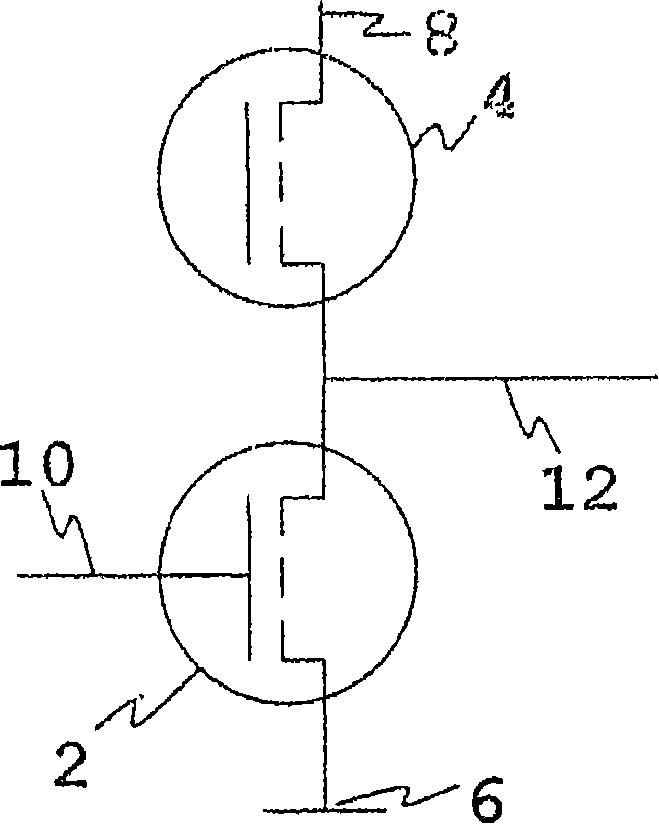

[0023] figure 1 One embodiment of a logic gate using a charge FET with a potential-free gate is illustrated. The selected logic gates are here embodied as inverters because the advantages of the invention are most clearly illustrated by inverters being the simplest components. figure 1 Two transistors 2 and 4 are shown connected in series to form an inverter. In this case, transistor 2 is a switching transistor and transistor 4 is a charging transistor. exist figure 1 , the source 6 of the switching FET 2 is grounded. The drain is connected to the output 12 of the inverter. The gate 10 of the switching transistor 2 forms the input of the inverter. The source and drain of the charging transistor 4 connect the output 12 of the inverter to the supply voltage 8 .

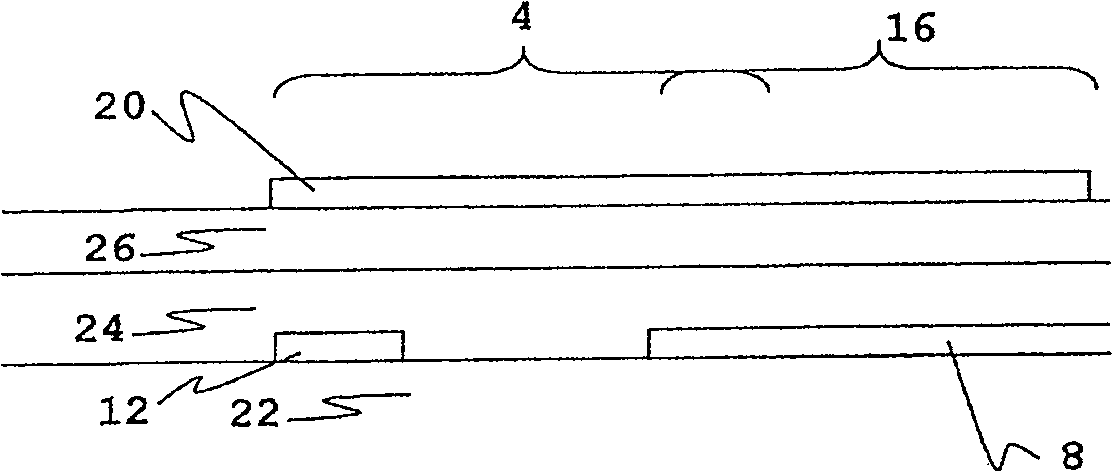

[0024] figure 2 One embodiment of an inverter using a charge FET with a gate capacitively cou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More