Causality-based memory access ordering in a multiprocessing environment

A processor and causal technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as increased memory sorting costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

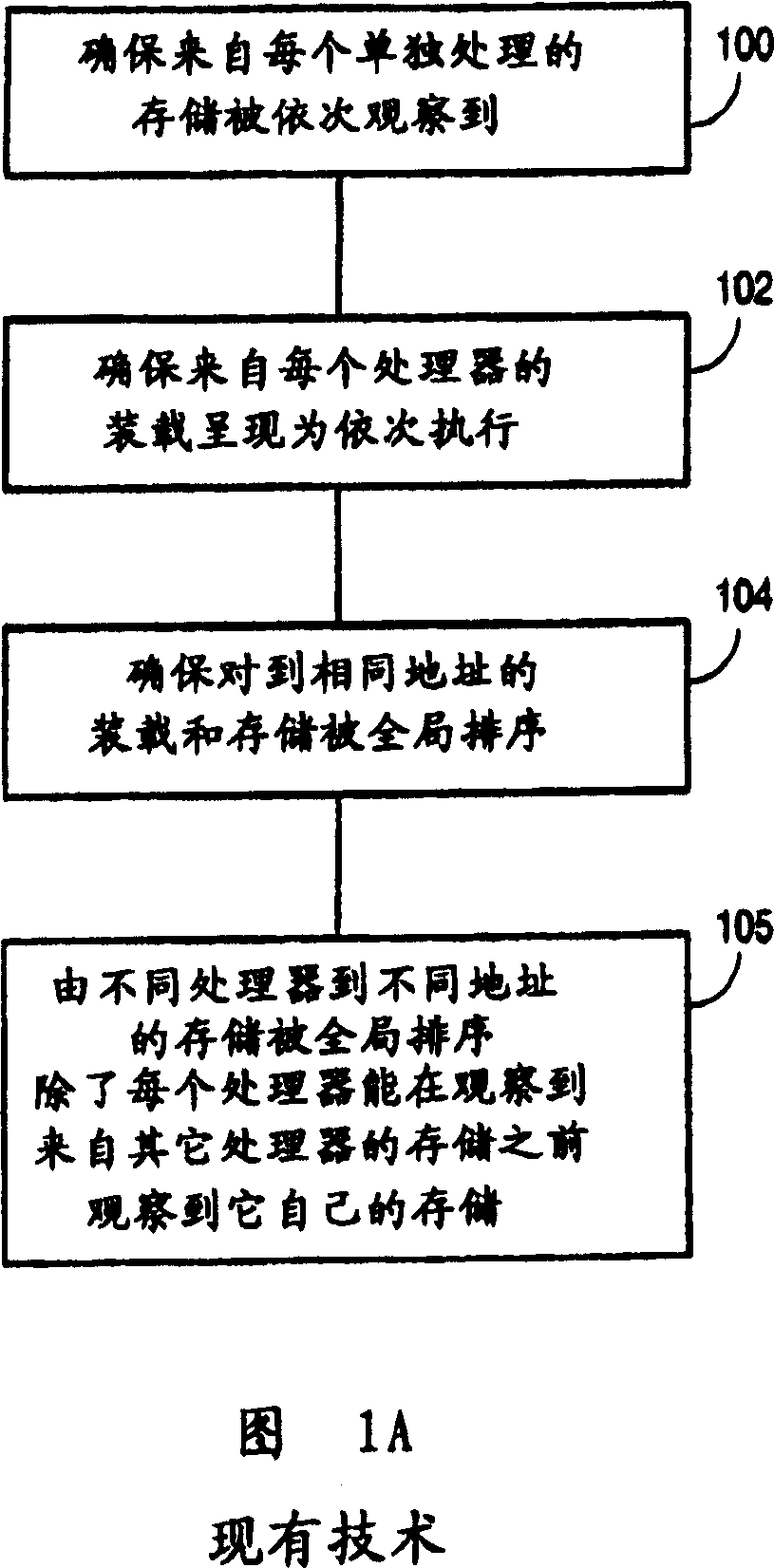

Problems solved by technology

Method used

Image

Examples

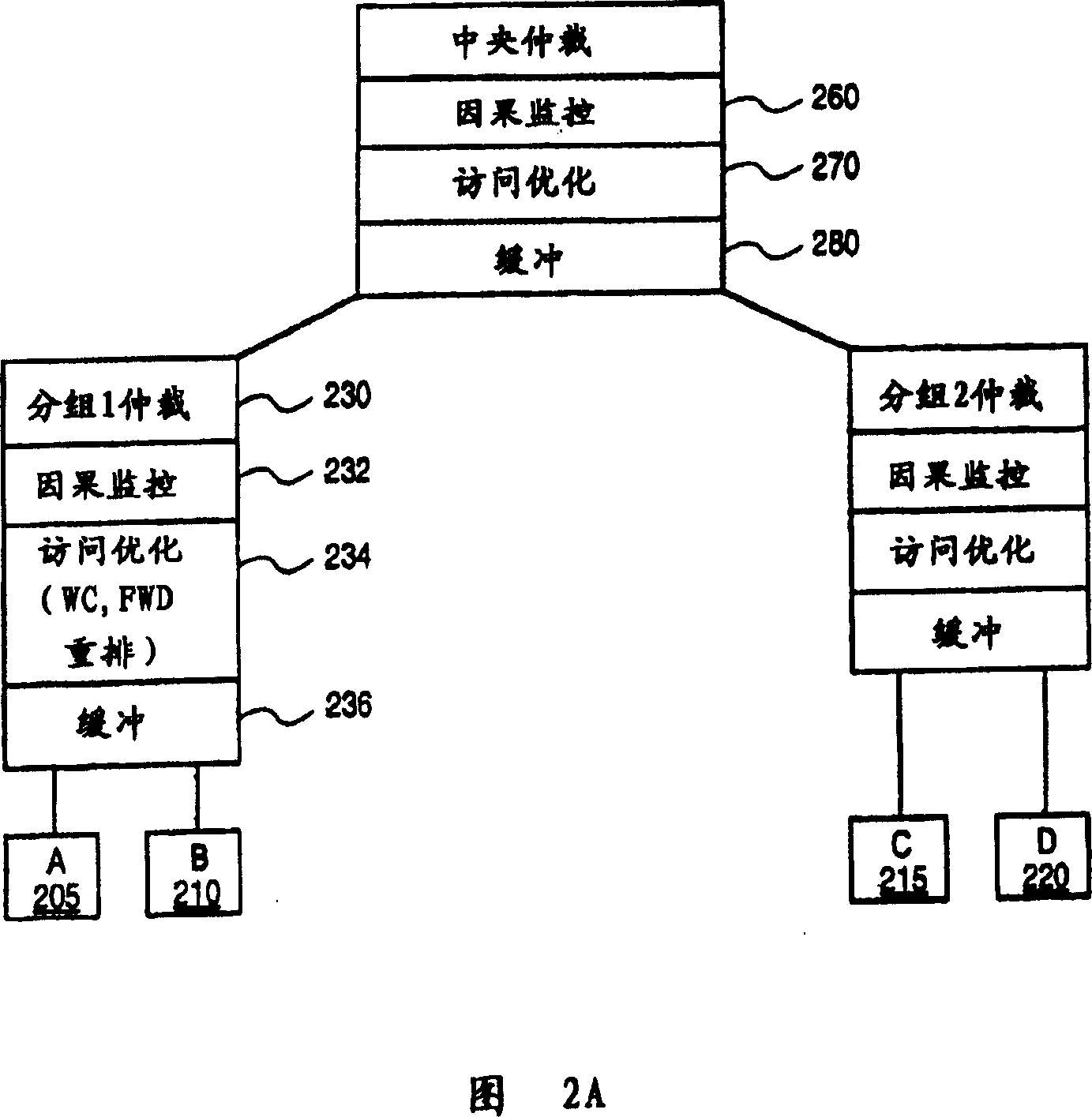

Embodiment Construction

[0021] The following description provides causality-based memory ordering in a multiprocessing environment. In the following description, numerous specific details are set forth, such as system arrangement and hierarchy, types of bus agents, and logic partitioning / integration options, to provide a thorough understanding of the present invention. However, one skilled in the art will recognize that the present invention may be practiced without these specific details. In other instances, control structures and gate level circuits have not been shown in detail in order not to obscure the invention. One of ordinary skill in the art, with the included description, will be able to implement the necessary logic circuits without undue experimentation.

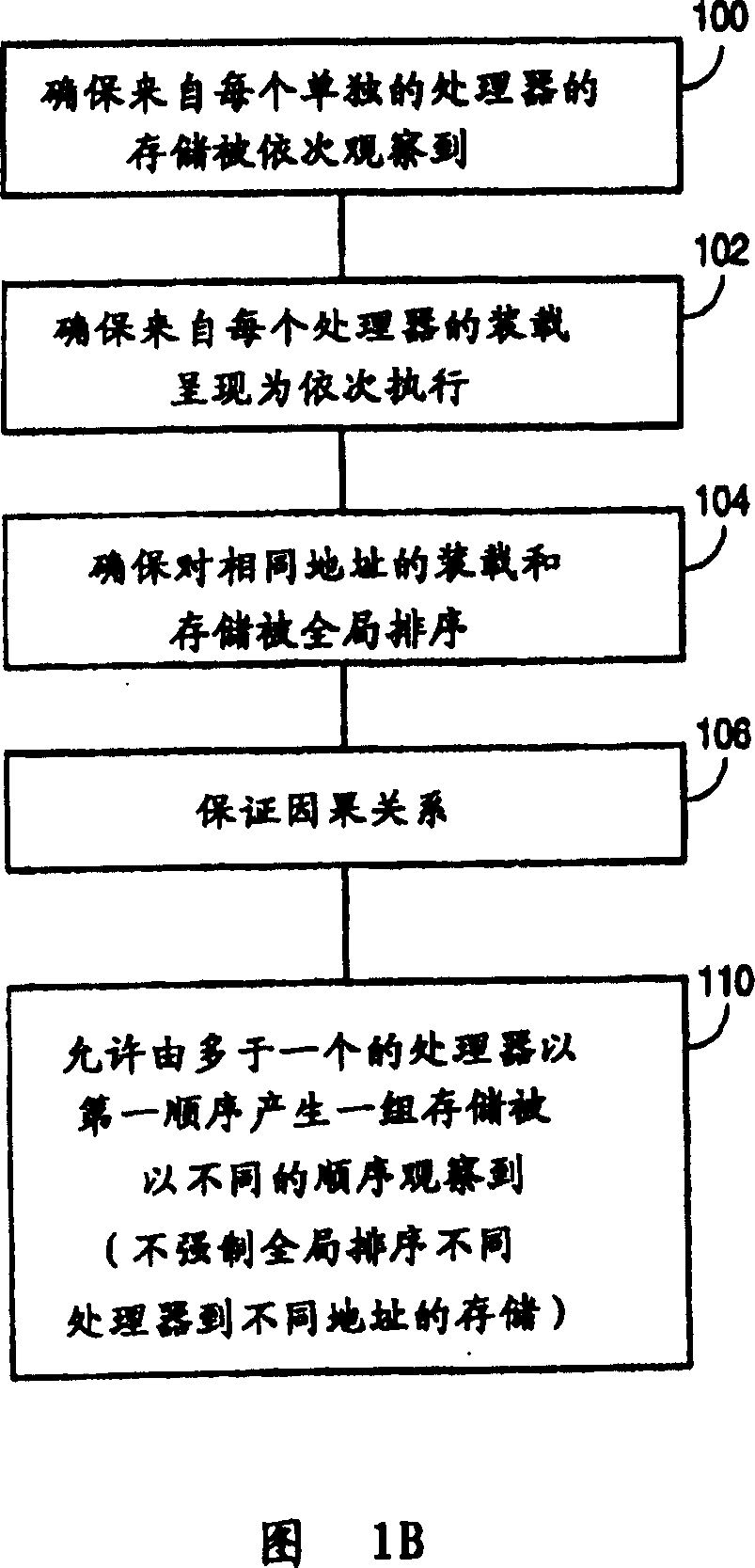

[0022] The disclosed memory ordering techniques may advantageously improve overall processing throughput in some systems. Improved throughput can be achieved by relaxing traditional memory ordering rules in a manner that allows the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More