Method for forming a semiconductor device having a strained channel and a heterojunction source/drain

a semiconductor device and heterojunction technology, applied in the field of semiconductor devices, can solve the problems of uneven device uniformity, different scaling challenges of transistor structures, and inability to adequately control implants with conventional semiconductor fabrication equipment,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

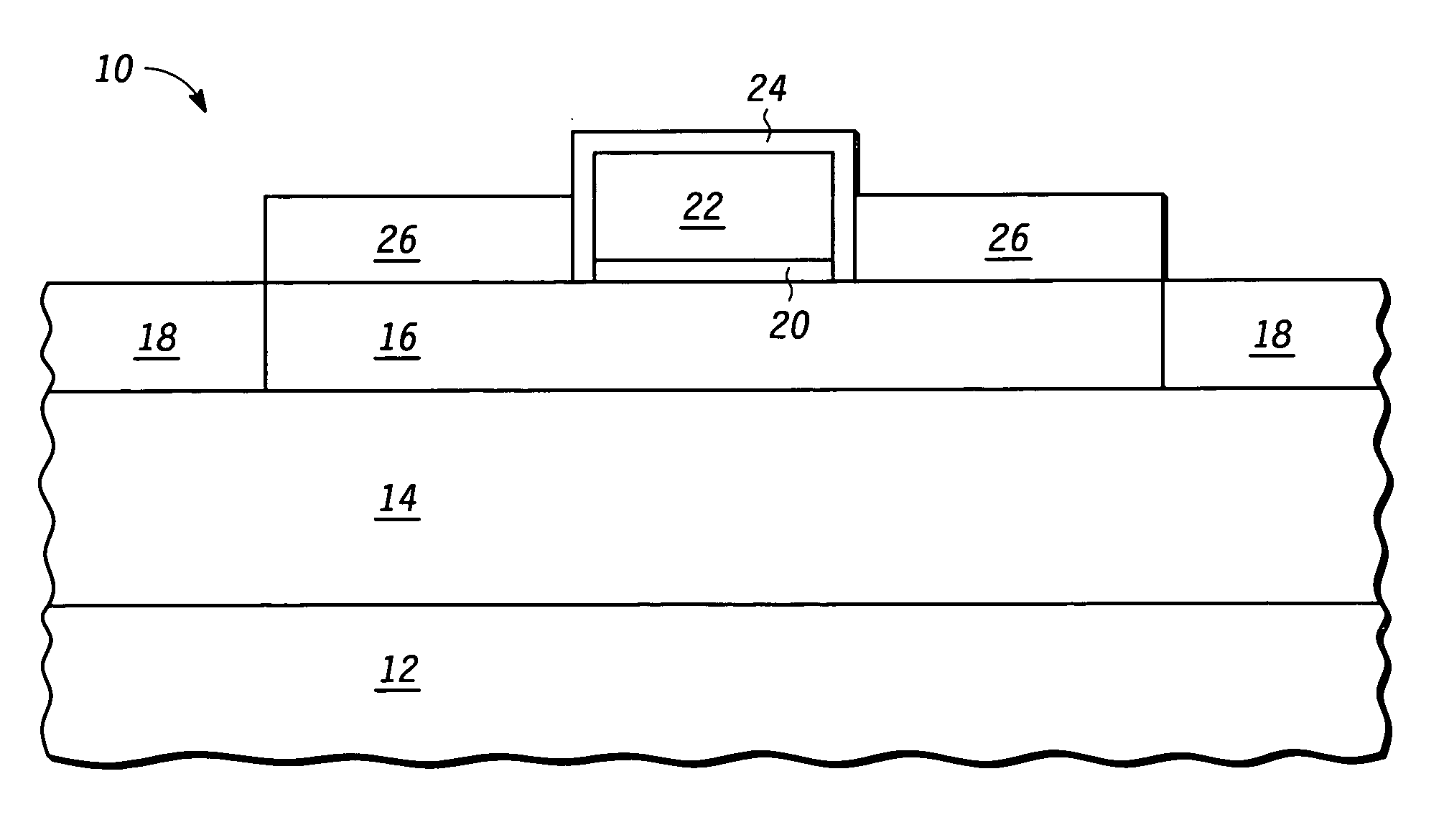

[0015] Illustrated in FIG. 1 is a semiconductor device 10 in accordance with the present invention. A substrate 12 is provided. In one form substrate 12 is silicon. However, any semiconductor material may be used. An overlying dielectric layer 14 is formed. Wafer bonding or implantation of an oxygen species material may be used to form the dielectric layer 14. In one form, the dielectric layer 14 is an oxide. A semiconductor layer 16 is formed and patterned overlying a portion of the dielectric layer 14. In one form the semiconductor layer 16 is silicon and has a thickness such that an aspect ratio that is equal to the gate length divided by the thickness of semiconductor layer 16 is at least three. Therefore, semiconductor layer 16 is relatively thin. Adjacent the semiconductor layer 16 is isolation region 18. It should be understood that isolation region 18 may either be a void of material or any dielectric material. Therefore, in one form the isolation region 18 is a void. A gate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More