Static Power Reduction in Caches Using Deterministic Naps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Example

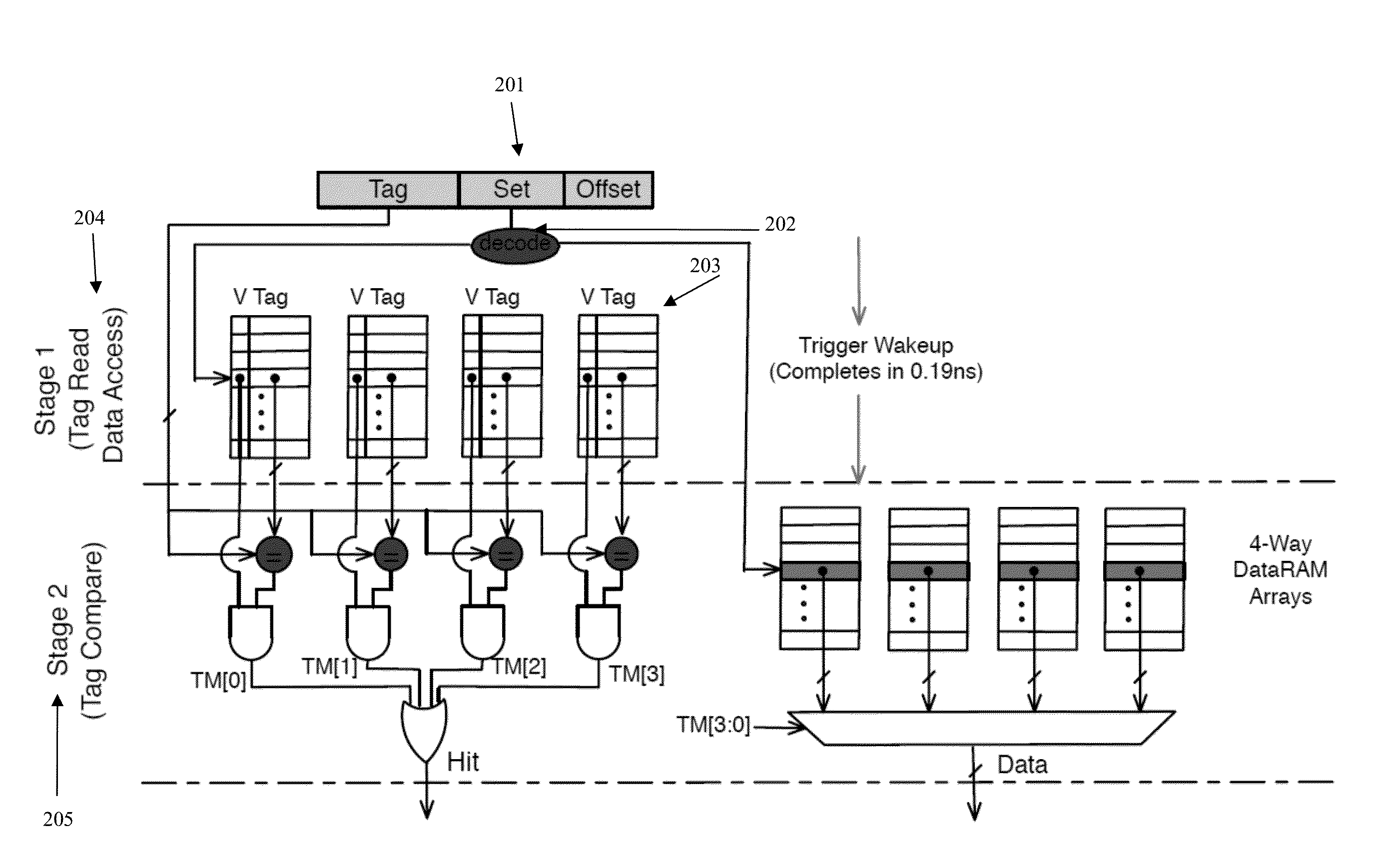

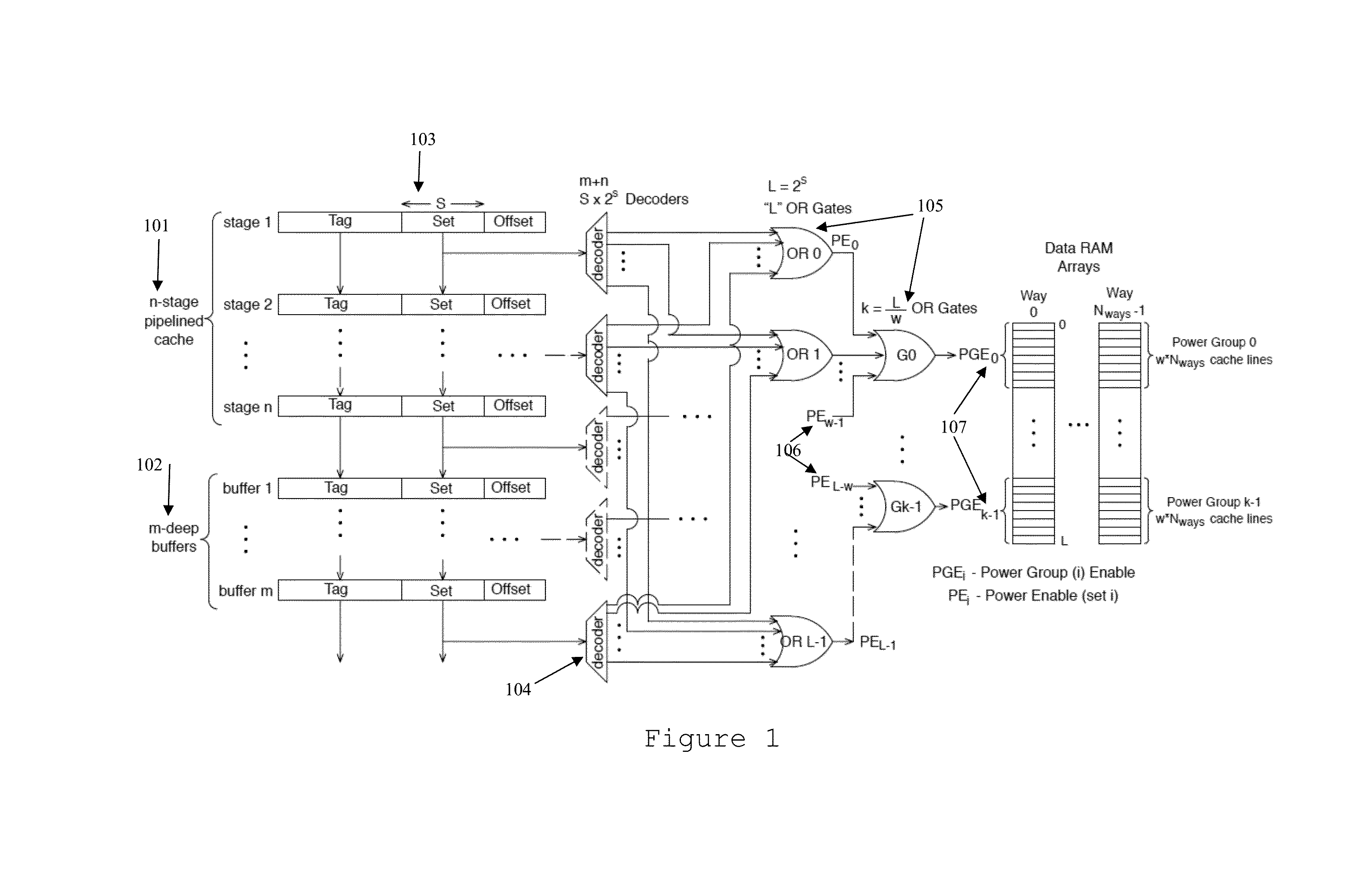

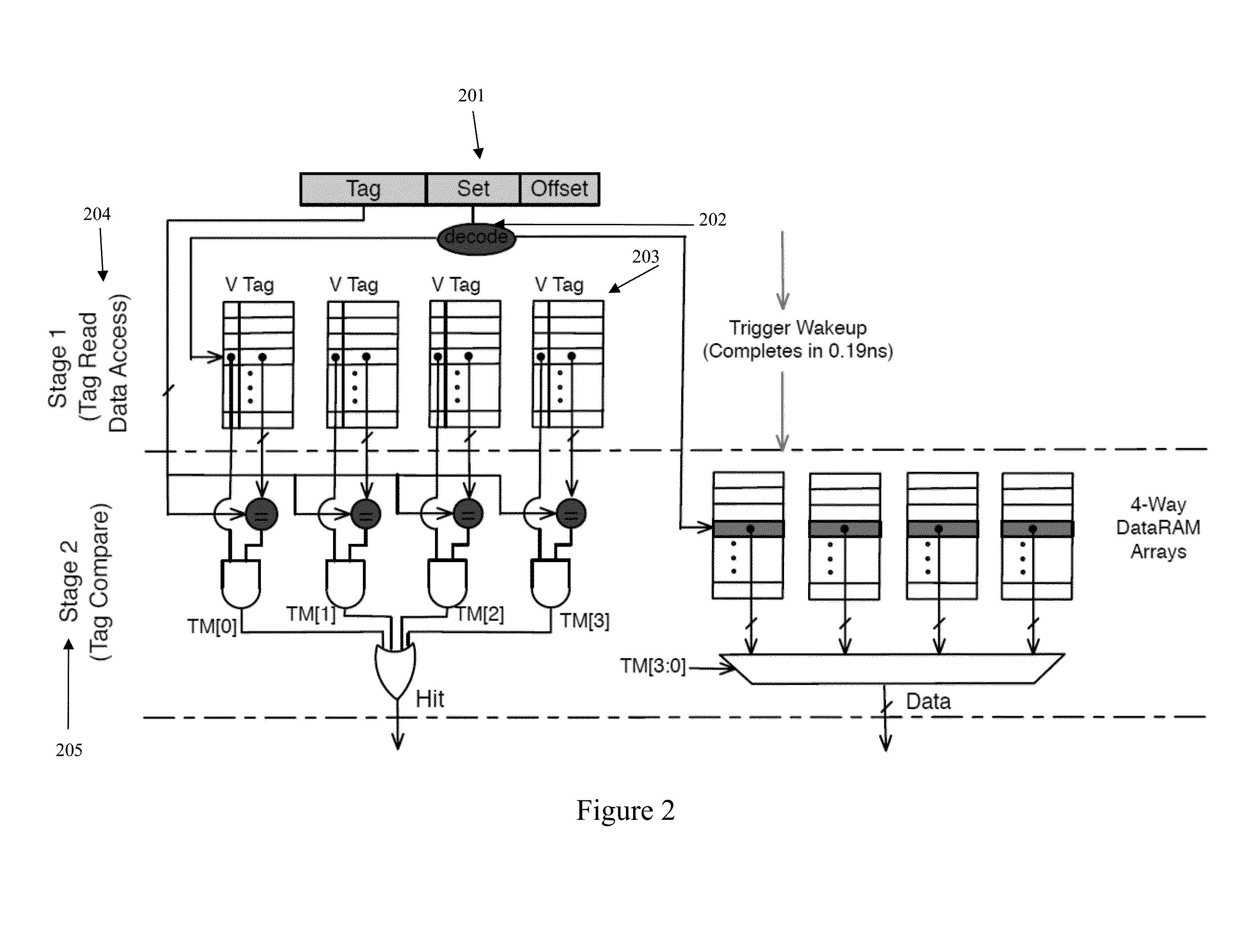

[0019]The deterministic napping technique shown in this invention reduces static / leakage power in caches by leveraging the ability to retain memory contents at low power states. This technique also takes advantage of the fact that data RAMs do not have to be read in the first cycle of cache access while the lines of the referenced set are being transitioned to full power state. These data RAM accesses can occur after tag RAM reads during hit / miss determination or even a cycle after as in phased cache architectures. Unlike conventional drowsy caches, which keep most lines of the data RAM in a low power state, and only restores full power when an access occurs to such low powered lines, the dNap architecture, maintains cache lines that will be accessed in the immediate future, in a fully powered state. This ensures accesses are never stalled while a wake up is being triggered. As a result, dNap caches do not suffer from the performance degradation incurred by conventional drowsy cache...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap