System and method for restricting increasing register addressing space in instruction width processor

A technology of registers and register groups, applied in memory systems, register devices, concurrent instruction execution, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

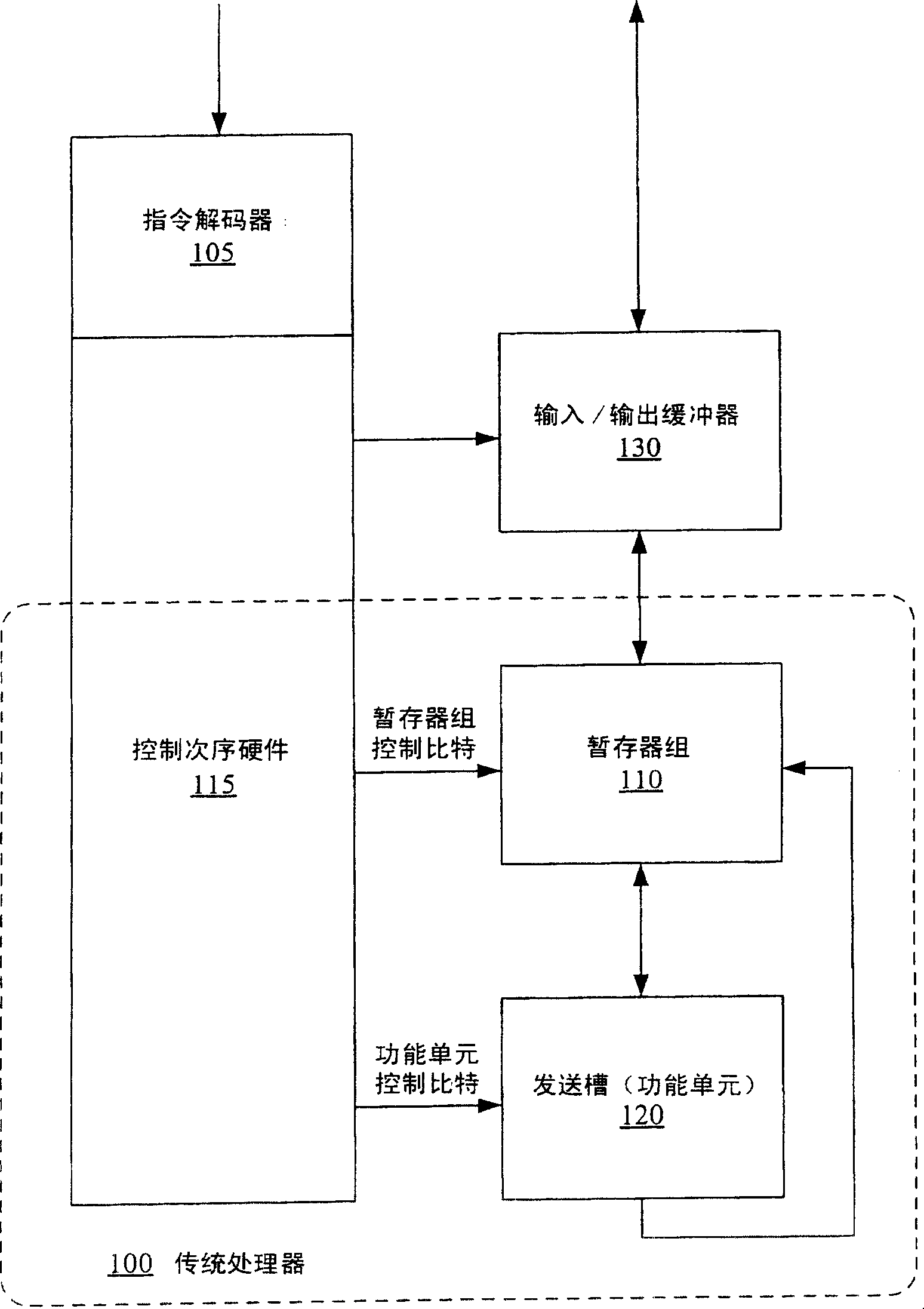

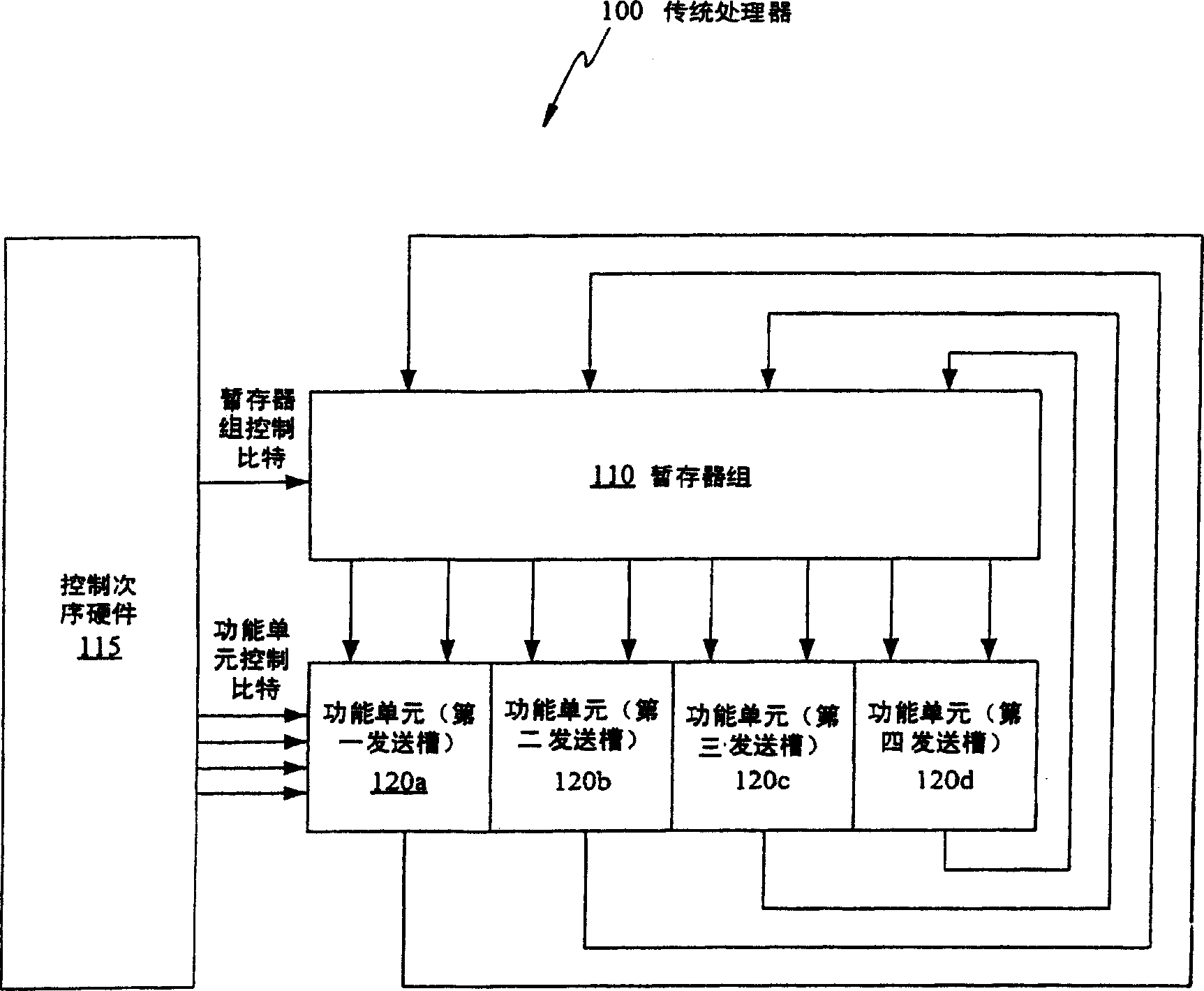

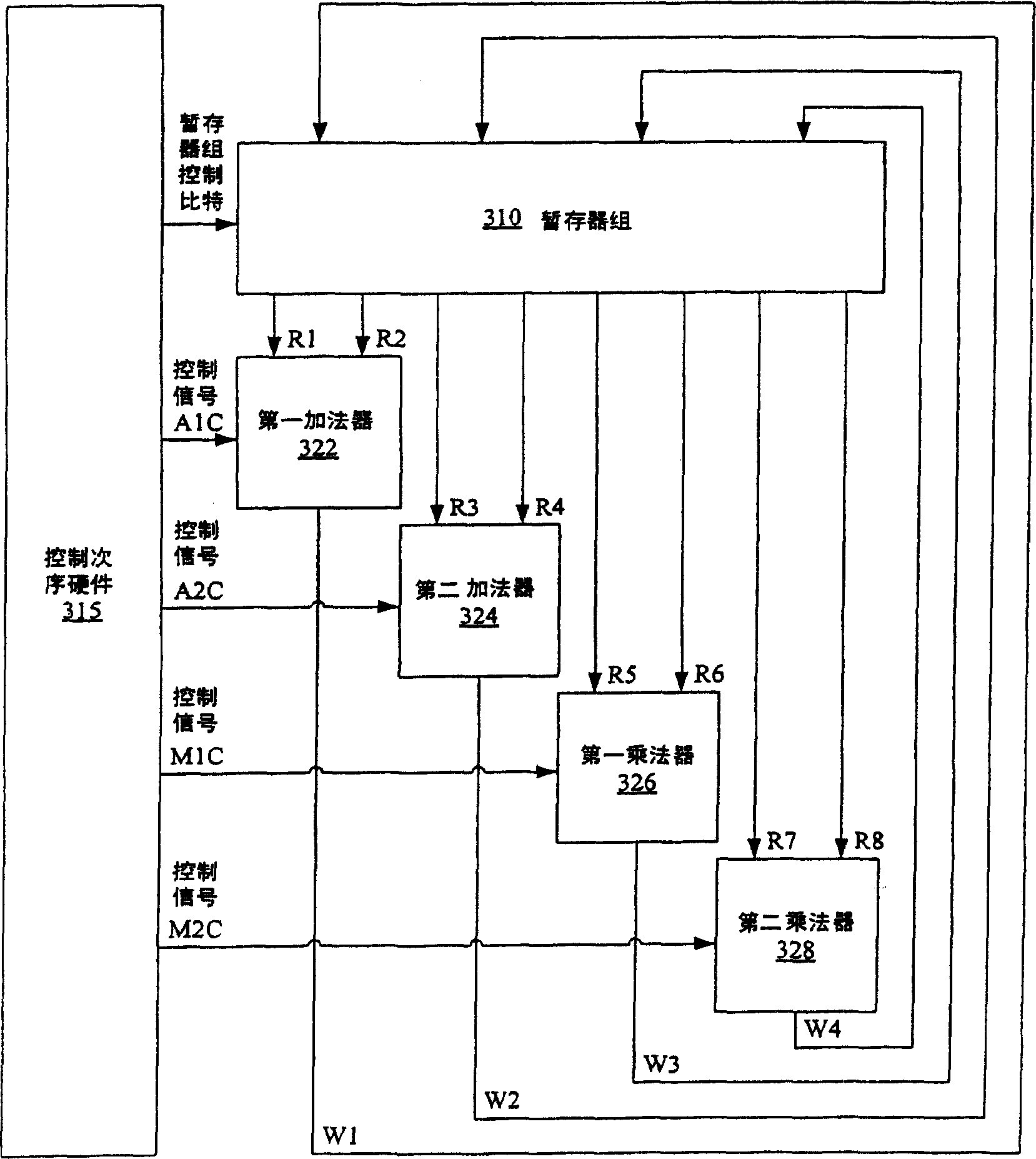

[0089] Instructions in Very Long Instruction (VLIW) processors, etc. often contain address fields for several operands per operation. These high instruction widths lead to increased on-chip storage costs for such instructions. And correspondingly, these high instruction widths also reduce system efficiency. This is often the major limiting factor in system performance.

[0090] Techniques are disclosed for arranging components within a specific architecture in processor space, thereby allowing multiple operations to be performed within a single pulse cycle with shorter instruction blocks. These shortened instruction words are provided by additional hardware components to the register space of the processor and an additional pre-processing step which may be performed by the compiler during code generation. Figure 4 and Figure 5 Several embodiments of processors configured to accommodate shortened instruction blocks are disclosed.

[0091] Such as Figure 4 As shown, the ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap