Relatively prime mode parallel counter based on congruence theory

A technology of counter and ring counter, applied in the direction of synchronous pulse counter, continuous cycle pulse counter, etc., can solve the problems of reduced maximum counting frequency, many hardware resources, and inconvenient description of the order of counter output states, so as to alleviate the pressure of time interpolation. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

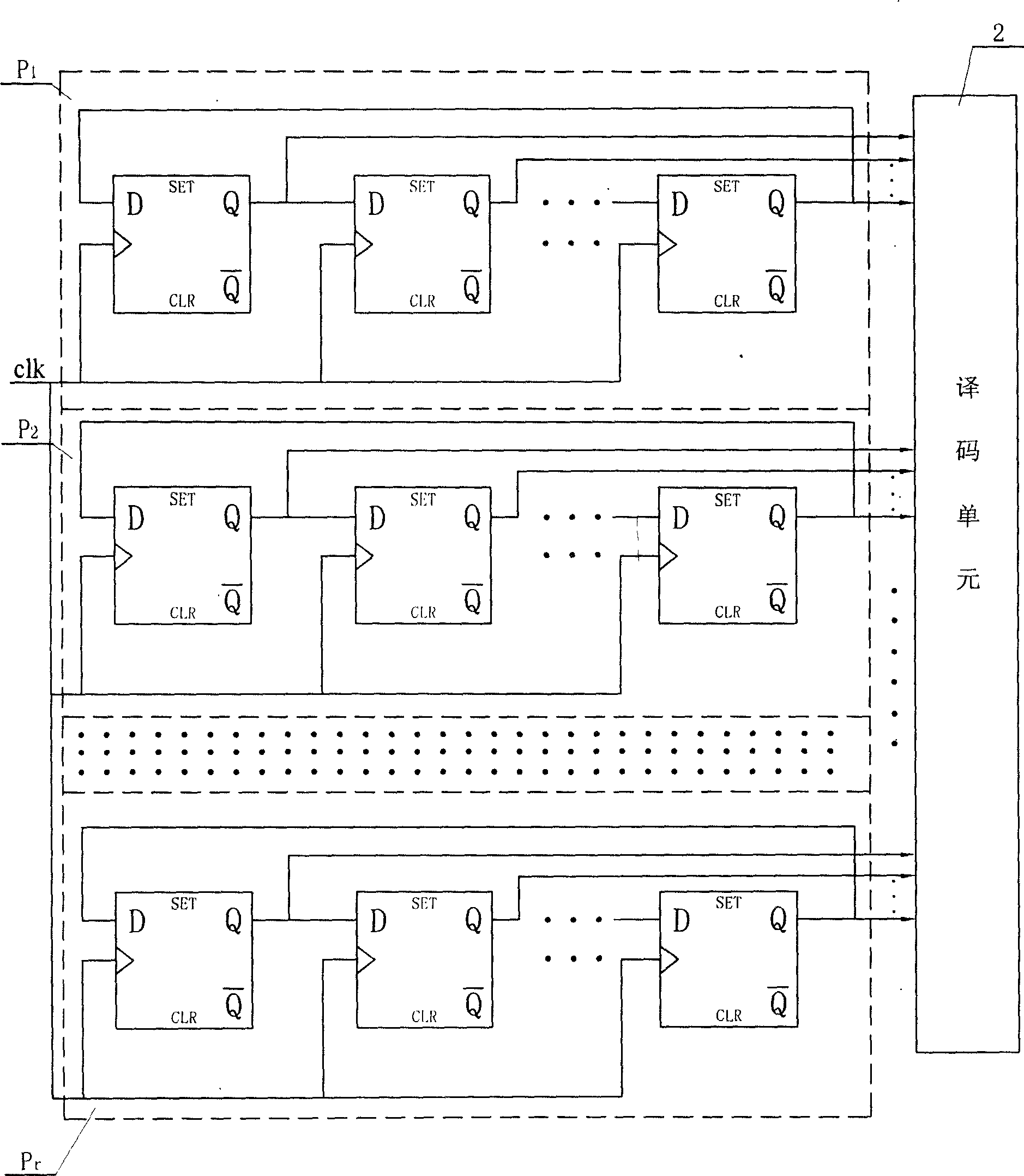

[0007] Specific implementation mode one: the following combination figure 1 This embodiment will be specifically described. It consists of a first synchronous ring counter P 1 , the second synchronous ring counter P 2 ...the rth synchronous ring counter P r Composed of decoding unit 2, the first synchronous ring counter P 1 ~rth synchronous ring counter P r The numbers of flip-flops in any two synchronous ring counters are prime numbers to each other, the clock pulse input terminals of the flip-flops in all synchronous ring counters are connected together and connected to the clock pulse signal clk, each trigger in all synchronous ring counters The positive output terminal or the negative output terminal of the converter are respectively connected to one input terminal of the decoding unit 2. All the flip-flops in this embodiment use "D" flip-flops, the input of the first flip-flop of each synchronous ring counter is connected with the output of the end flip-flop, and the...

specific Embodiment approach 2

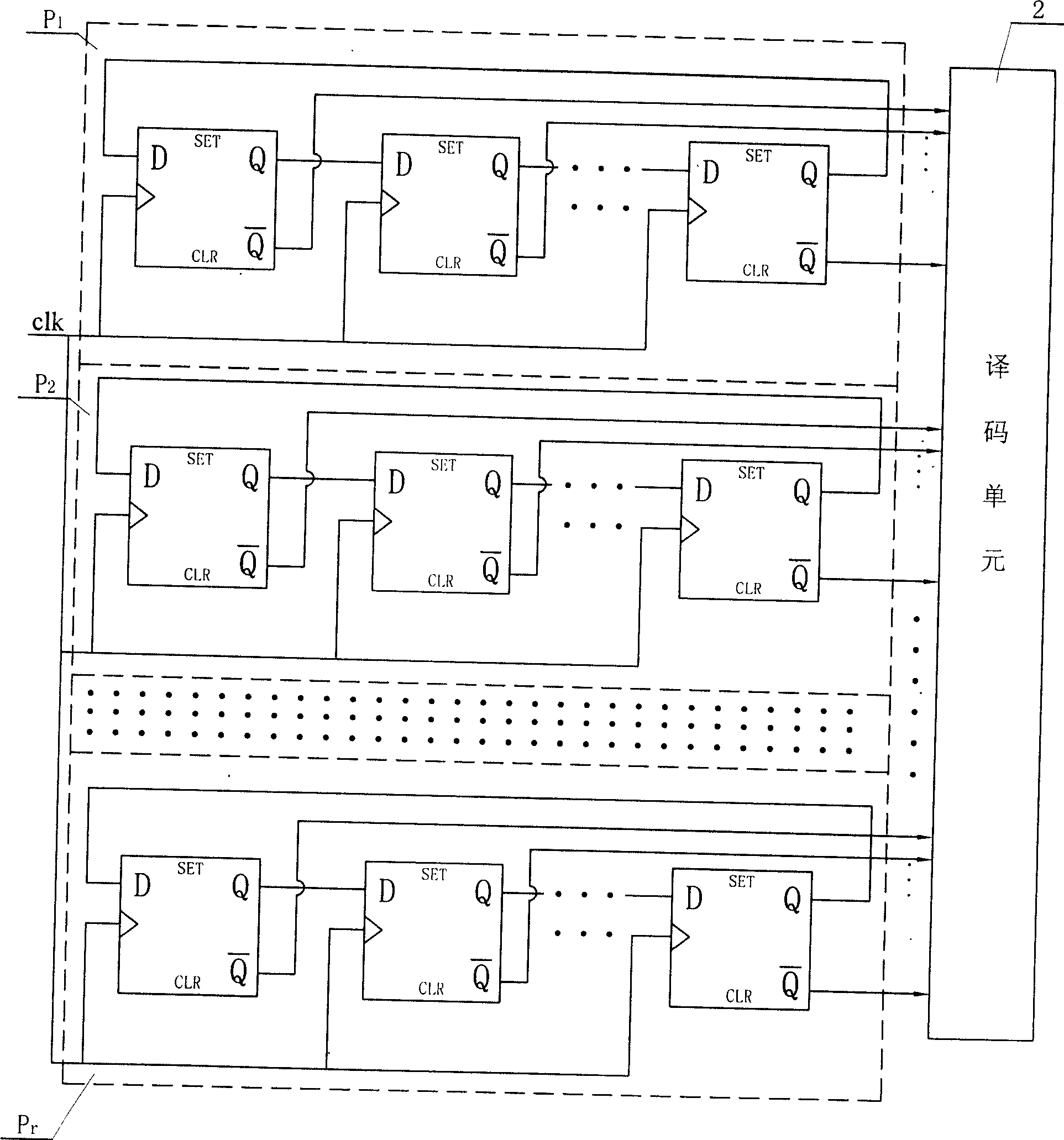

[0008] Specific implementation mode two: the following combination figure 2 This embodiment will be specifically described. It consists of a first synchronous ring counter P 1 , the second synchronous ring counter P 2 ...the rth synchronous ring counter P r Composed of decoding unit 2, the first synchronous ring counter P 1 ~rth synchronous ring counter P r The numbers of flip-flops in any two synchronous ring counters are prime numbers to each other, the clock pulse input terminals of the flip-flops in all synchronous ring counters are connected together and connected to the clock pulse signal clk, each trigger in all synchronous ring counters The inverting output ends of the switches are connected to one input end of the decoding unit 2 respectively. All the flip-flops in this embodiment are "D" flip-flops.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More