Method and apparatus for performing chip level equalization using joint processing

A device and joint channel technology, applied in multiplex communication, baseband system components, digital transmission systems, etc., can solve the problems of mutual channel interference performance, deterioration, etc.

Inactive Publication Date: 2008-10-22

INTERDIGITAL TECH CORP

View PDF0 Cites 4 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

However, these types of receivers often experience significant performance degradation due to cross-channel interference from one antenna to another that cannot be canceled or canceled out

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

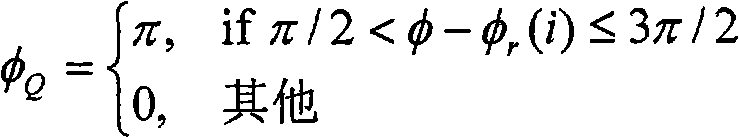

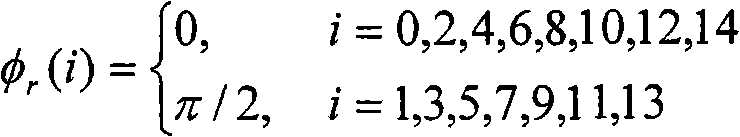

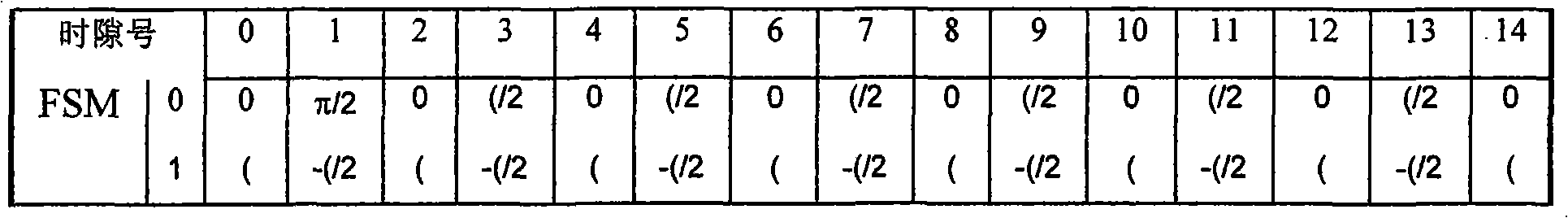

A method and apparatus for performing chip level equalization (CLE) using joint processing to enhance performance and system throughput using a transmitter having a plurality of transmit antennas and a receiver having a plurality of receive antennas. A channel response matrix is formed between the transmit antennas and the receive antennas to generate a joint channel correlation matrix between the transmit antennas and the receive antennas using a block-FFT (B-FFT) decomposition of the channel response matrix. Estimates of transmitted chip sequences from each of the transmit antennas are generated using minimum mean square error (MMSE) and the joint channel correlation matrix are combined. The combined estimate of the transmitted chip sequences are despread to recover transmitted data.

Description

Method and device for performing chip-level equalization using joint processing Technical field The present invention relates to a wireless communication receiver. More specifically, the present invention relates to processing space-time transmit diversity (STTD), closed-loop transmit diversity for transmitting adaptive antennas, and chip-level equalization (CLE) with oversampling and fast Fourier transform (FFT) based on joint processing using joint processing ) Receiver diversity receiver. Background technique CLE is a candidate for use in advanced receivers used in wireless communication systems for high data rate services such as High Speed Downlink Packet Access (HSDPA). Compared with Rake receivers, CLE-based receivers, such as those used in wireless transmit / receive units (WTRU), are used more in advanced receivers due to their superior performance. Reception diversity using two or more receiving antennas provides high performance by improving the reception quality of ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): H04B7/216H04J99/00

CPCH04B7/0854H04B1/71052H04B1/71055H04L25/0206H04L25/03171H04L2025/03426H04L25/0204H04L1/0618

Inventor 俊霖·潘罗伯特·A·迪费奇欧

Owner INTERDIGITAL TECH CORP