Lateral DMOS device and method for fabricating the same

A conductive type, deep well technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of increased on-resistance and unsuitability for improving the practicability of LDMOS devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Reference will now be made in detail to the preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like elements.

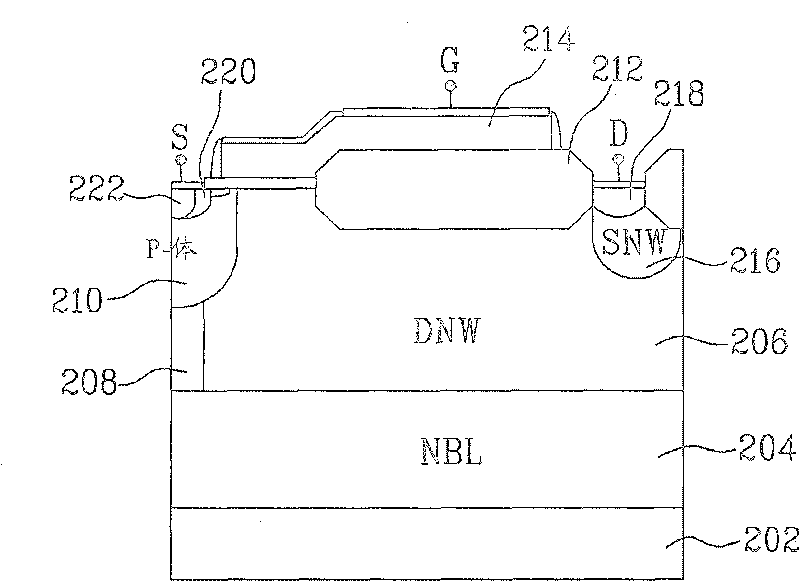

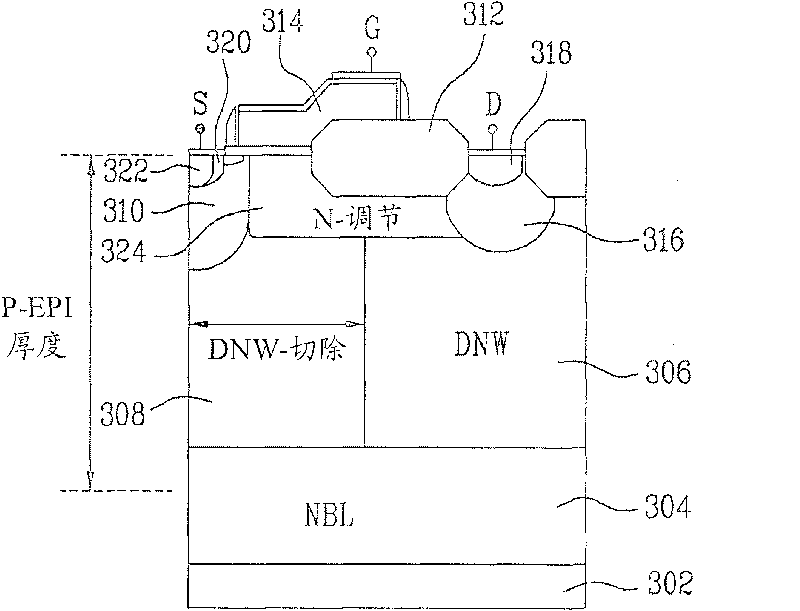

[0018] as example Figure 3A As shown in , according to an embodiment, a high-side LDMOS may include: a P-type semiconductor substrate 302 having an N-type buried layer 304 formed thereon and / or thereover; and a P-type epitaxial layer having a thickness of P- epi. The N-type buried layer 304 can be used to reduce the width of the depletion layer extending from the P-type body 310 , so that when a voltage is applied to the N+-type drain region 318 , the breakdown voltage can be substantially increased. The P-type epitaxial layer can be used to reduce the impedance of the substrate 302 .

[0019] N-type deep well 306 may then be formed on and / or over P-type semiconductor substrate 302 . When implement...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com