A Method for Analyzing Displacement Damage Effects of CMOS Devices

A technology of displacement damage and devices, applied in instruments, special data processing applications, calculations, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The preferred embodiment of the present invention is described in more detail below with reference to the accompanying drawings of the present invention.

[0031] The following is a detailed description of six sub-analysis modules of the present invention:

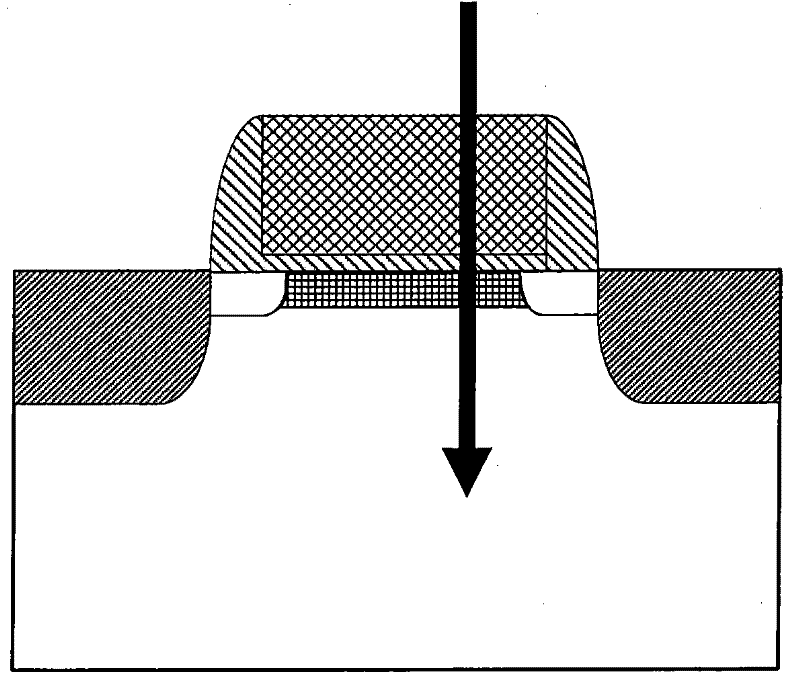

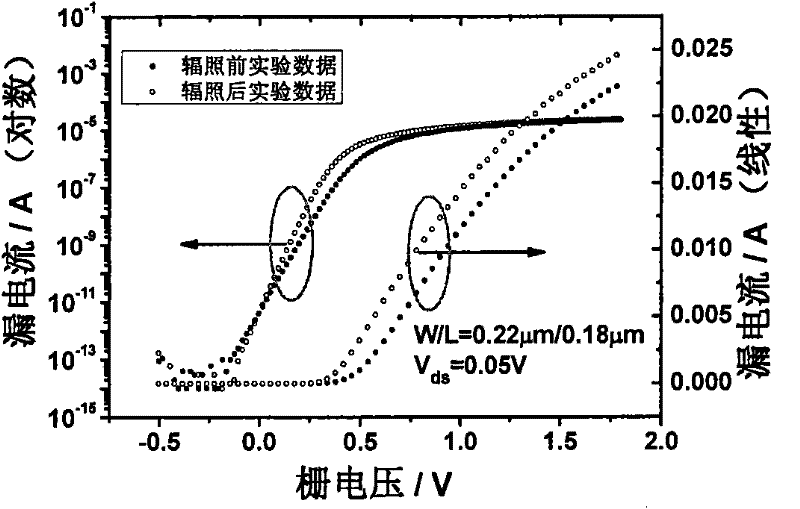

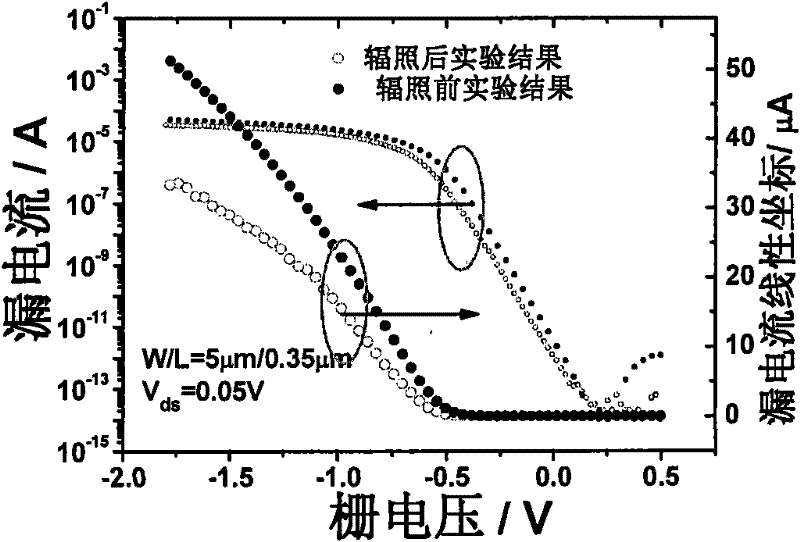

[0032]A drain and source displacement damage analysis module: displacement damage leads to effective gate-source voltage V gseff and the drain-source voltage V dseff reduce. With the shortening of the channel length of the MOS transistor, the intrinsic resistance of the channel decreases, but the parasitic resistance of the source and drain regions will not shrink in proportion, which makes the influence of the parasitic resistance larger. Since the heavy particles hit near the source and drain of the device, the displacement damage caused by the irradiation causes the parasitic resistance of the source and drain to increase, and the parasitic source and drain resistance makes the effective V gseff and V dseff d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More