Semiconductor device

A semiconductor, planar technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

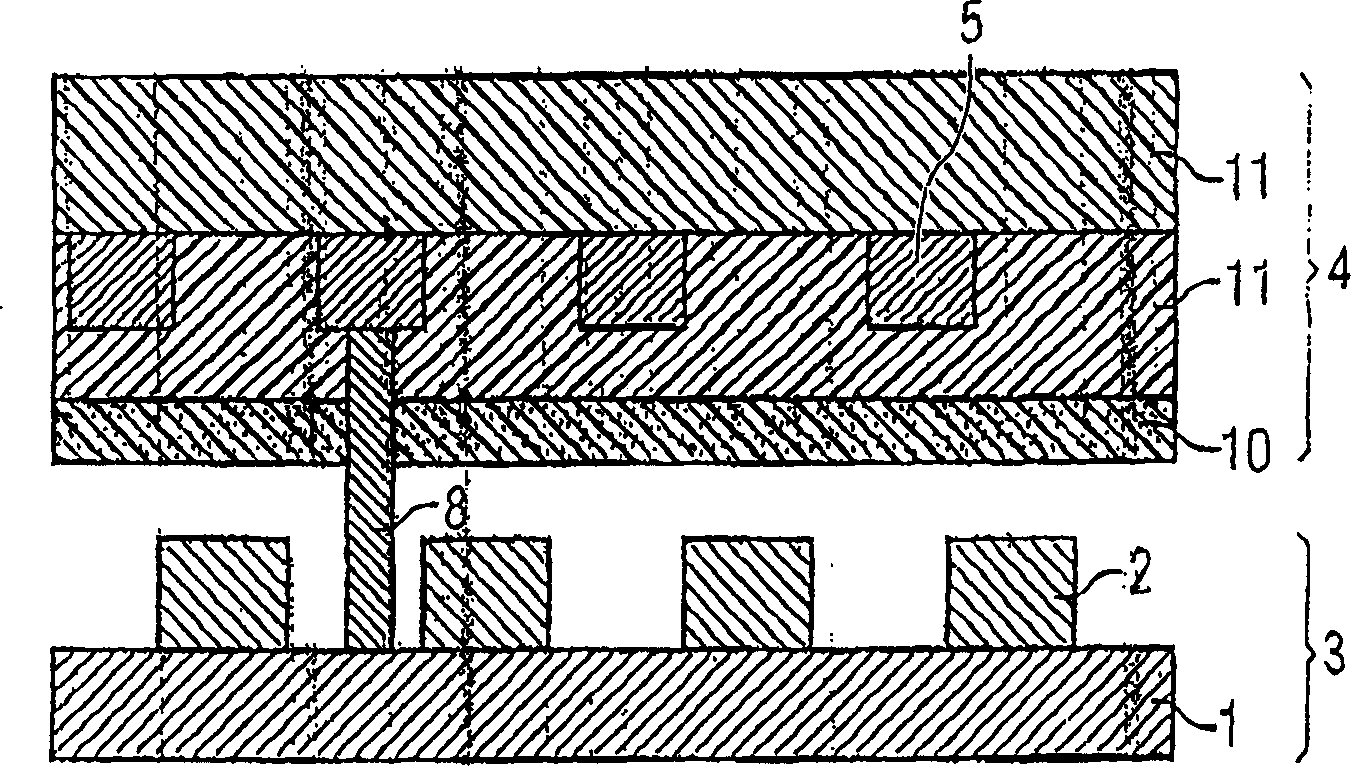

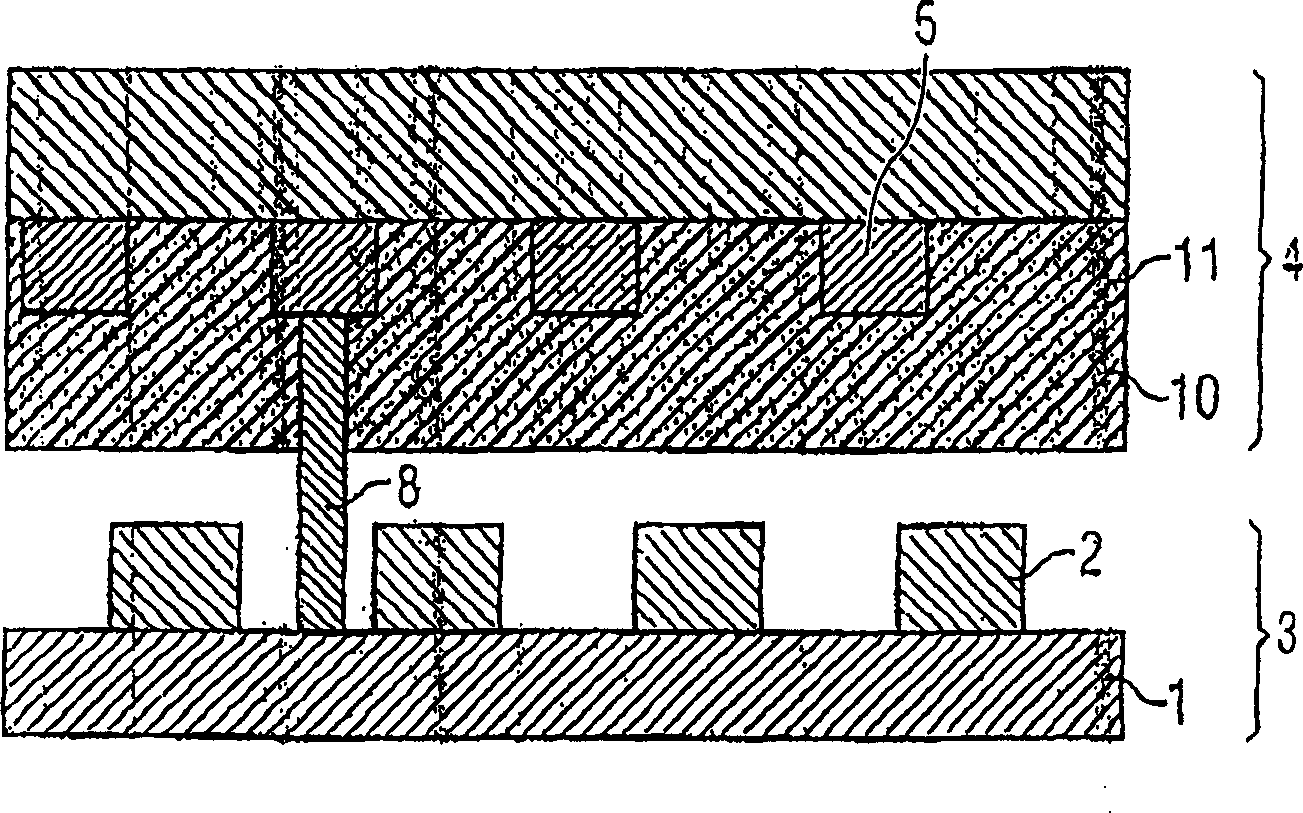

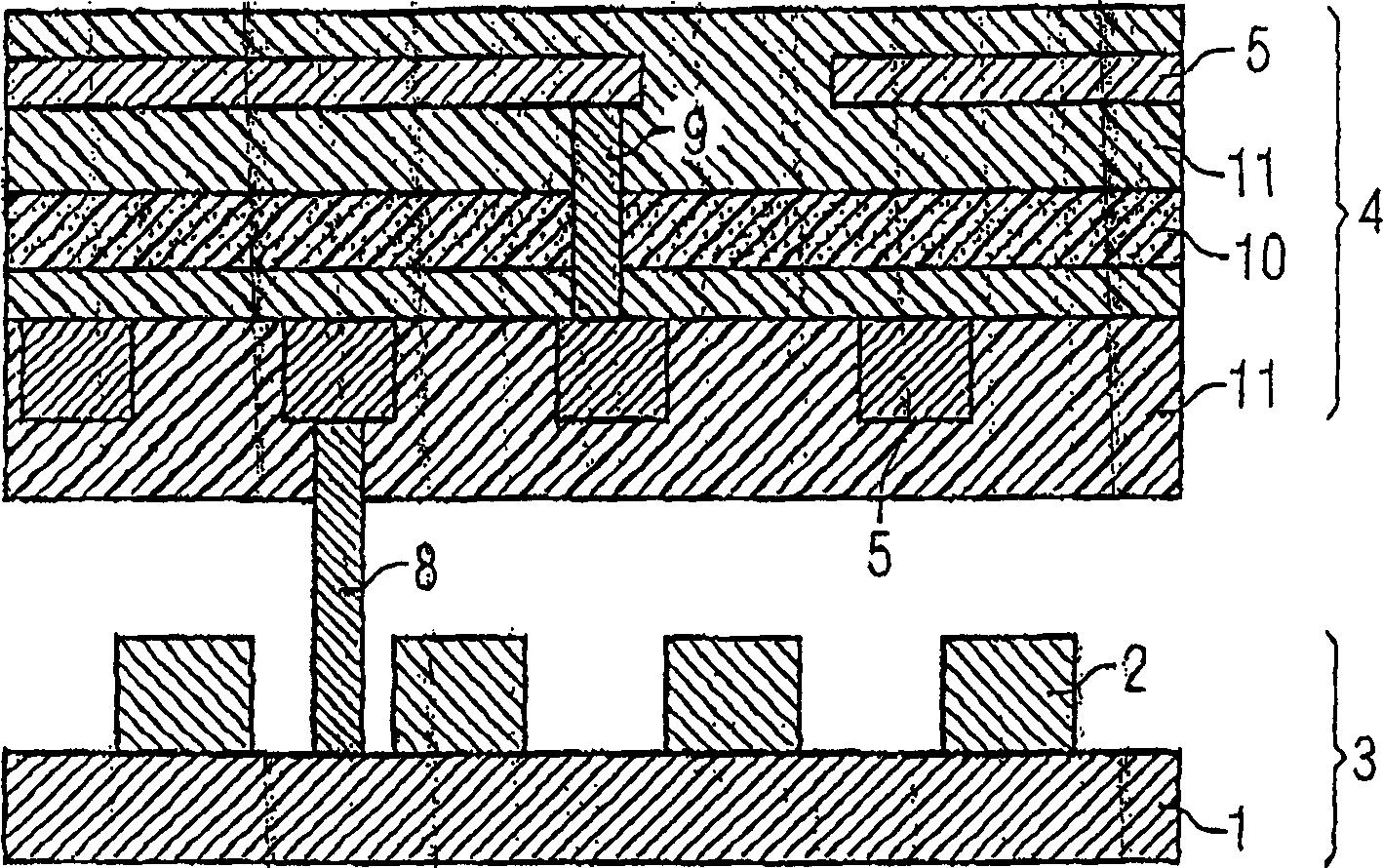

[0026] Figure 1 shows a semiconductor device consisting of an active region (3) and a metallization layer (4). The active area (3) is divided into two parts, the bit line (1) and the word line (2). The metallization layer (4) has at least one metal plane (5) and an intermetallic dielectric (11), if there are several metal planes (5), these metal planes (5) are stacked together in a layered manner and are The intermetallic dielectric (11) in between is electrically insulated.

[0027] Between the bit line (1) and the metal plane (5) there is a connecting line (8), the so-called "Vias". In the manufacturing process, the semiconductor device is constructed from the bottom to the top starting from the active area (3). Therefore, after the construction of the active region (3) is completed, a heating step is performed to eliminate and / or remove the carriers fixed by the ultraviolet rays from the memory layer.

[0028] Since the semiconductor device will be exposed to high-energy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More