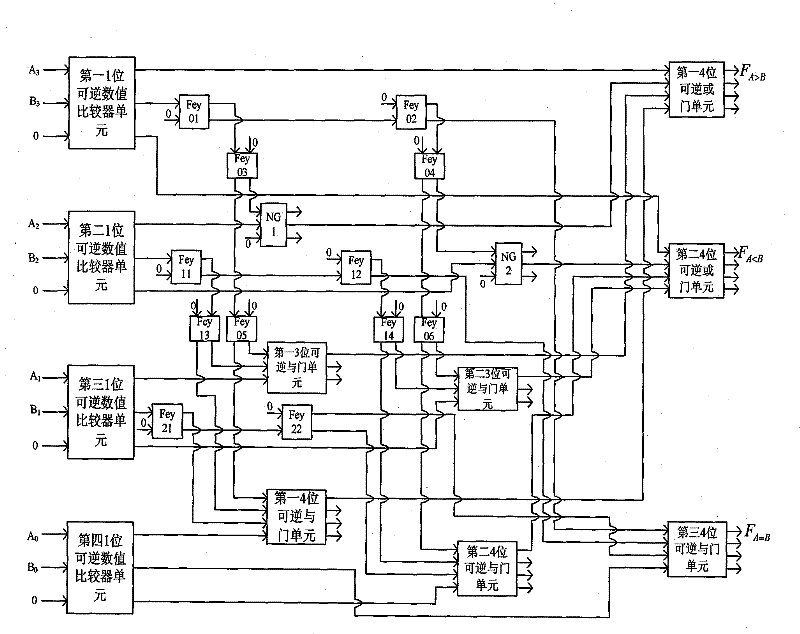

Four-bit reversible digital comparator

A numerical comparison, four-digit technology, applied in the field of four-digit reversible numerical comparators, can solve problems such as energy loss, and achieve the effect of reducing energy consumption and expanding the number of digits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to deepen the understanding of the present invention, the present invention will be further described below in conjunction with the embodiments and accompanying drawings. The embodiments are only used to explain the present invention and do not constitute a limitation to the protection scope of the present invention.

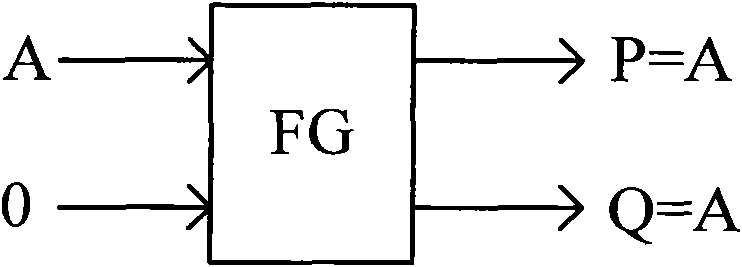

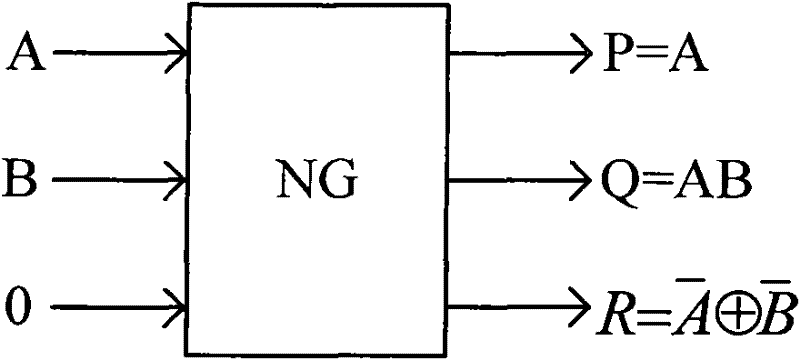

[0025] The four-bit reversible numerical comparator of the present invention comprises: a 1-bit reversible numerical comparator, a 3-bit reversible AND gate unit, a 4-bit reversible AND gate unit, a 4-bit reversible OR gate unit, a New gate and several Feynman gates.

[0026] The following describes the construction of each module:

[0027] 1. One-bit reversible numerical comparator. The function table of a reversible numerical comparator is shown in Table 1, and its structural block diagram is shown in Figure 5a .

[0028]

[0029]

[0030] Table 1 Function table of a reversible numerical comparator

[0031] Depend on Figure 5a It ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More