Main device for Ethernet system and relevant clock synchronization method thereof

A technology for network system and clock synchronization, which is used in transmission systems, synchronization devices, digital transmission systems, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

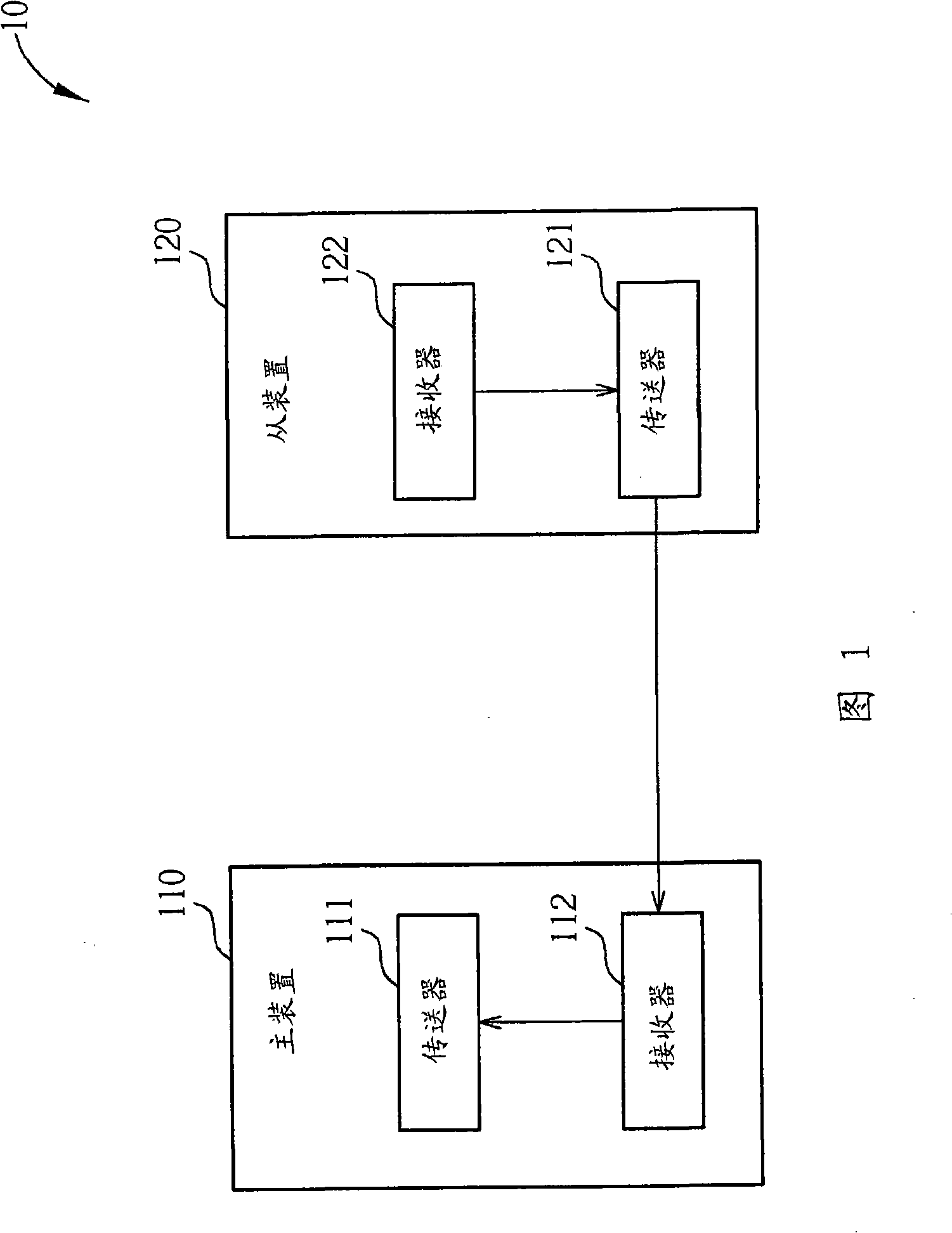

[0047] The Ethernet system 10 adopts a loop timing system (Loop Timing), and the clock recovery is performed by the slave device 120 according to the received signal. For example, the transmitter 111 of the master device 110 uses a free running clock (Free Running Clock) to transmit signals. After the receiver 122 of the slave device 120 receives the transmission signal, the slave device 120 performs a clock recovery (Timing Recovery) operation to generate a recovered clock identical to the free-running clock of the master device 110, the transmitter 121 and the receiver 122 transmits or samples signals according to the recovered clock, respectively. When the receiver 111 receives the signal transmitted by the slave device 120 according to the recovered clock, the receiver 111 performs synchronization so that the clock of the receiver 111 is the same as the recovered clock.

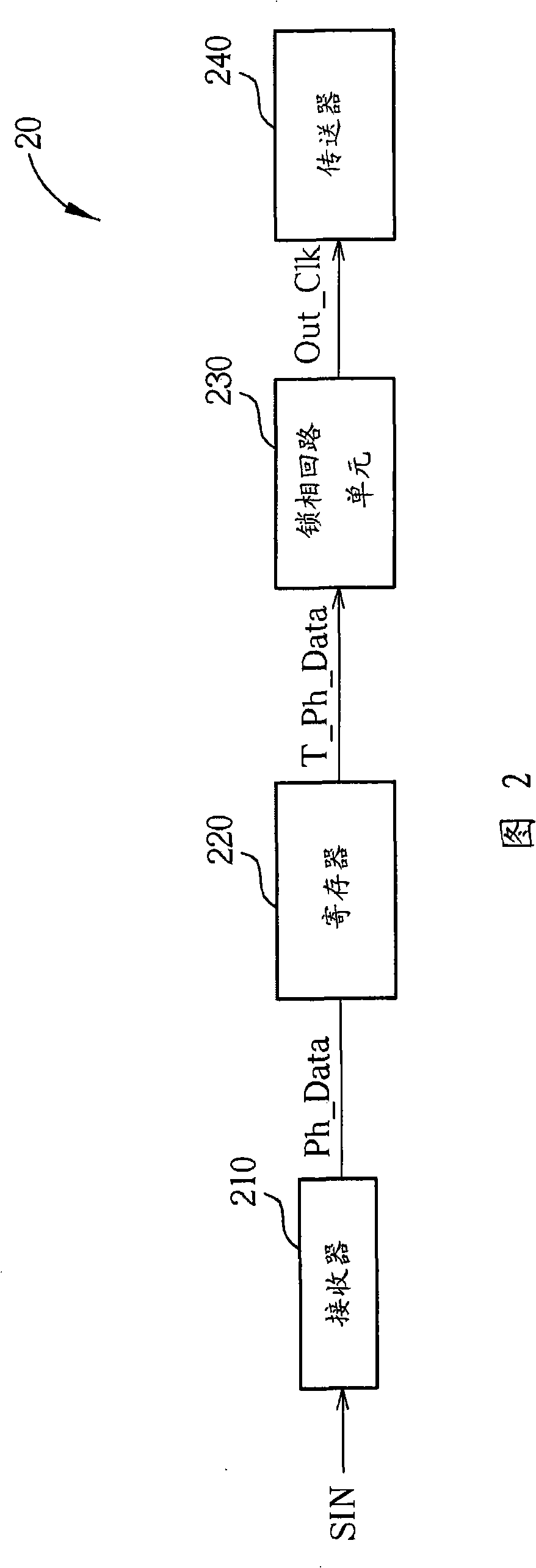

[0048] Please refer to figure 2 , figure 2 It is a schematic diagram of a master device 20 used i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More