Interfacing between differing voltage level requirements in an integrated circuit system

An integrated circuit, power supply voltage technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, fail-safe circuits, etc., can solve problems such as gate (G) oxide damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

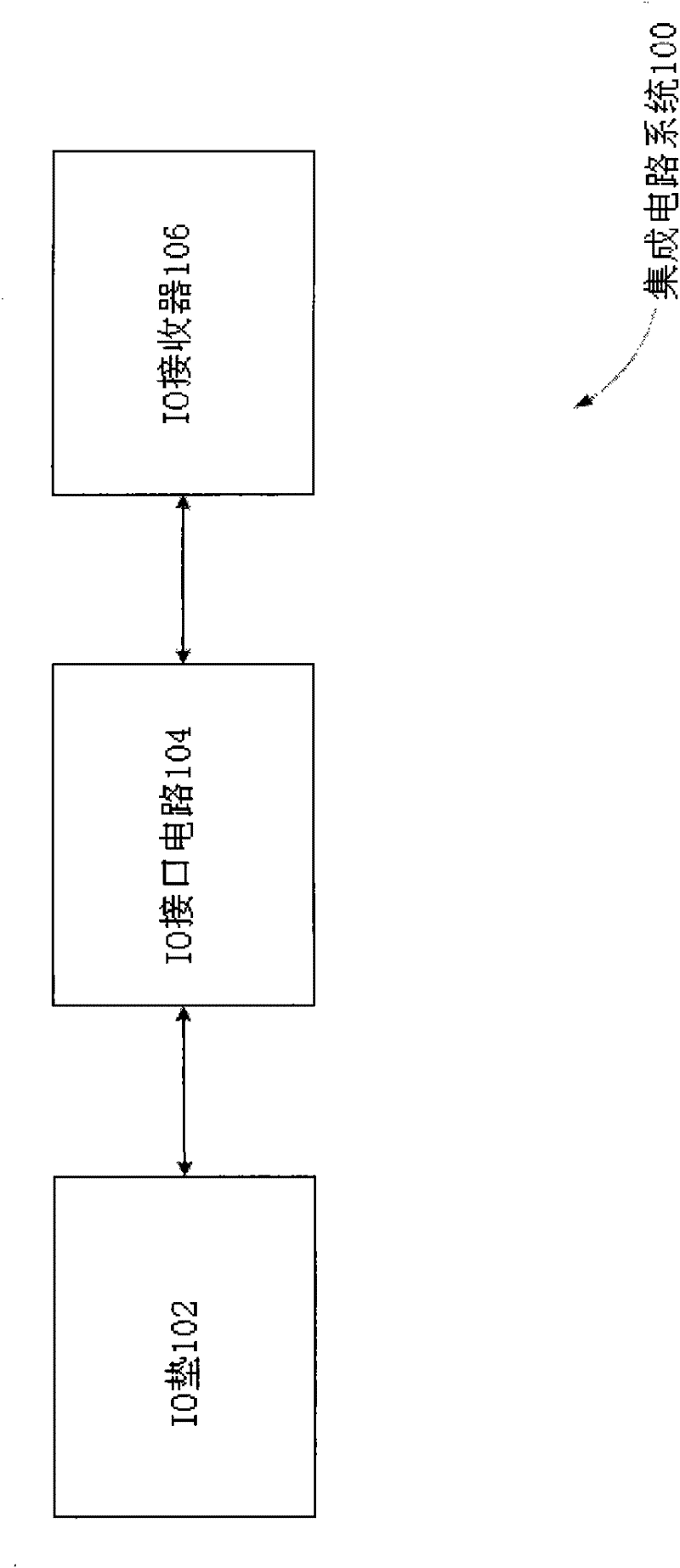

[0024] The exemplary embodiments described below may be used to implement input / output (IO) interface circuits capable of interfacing between different voltage level requirements. Although these embodiments have been described with reference to specific exemplary embodiments, it will be evident that various modifications and changes may be made to these embodiments without departing from the broad spirit and scope of the various embodiments.

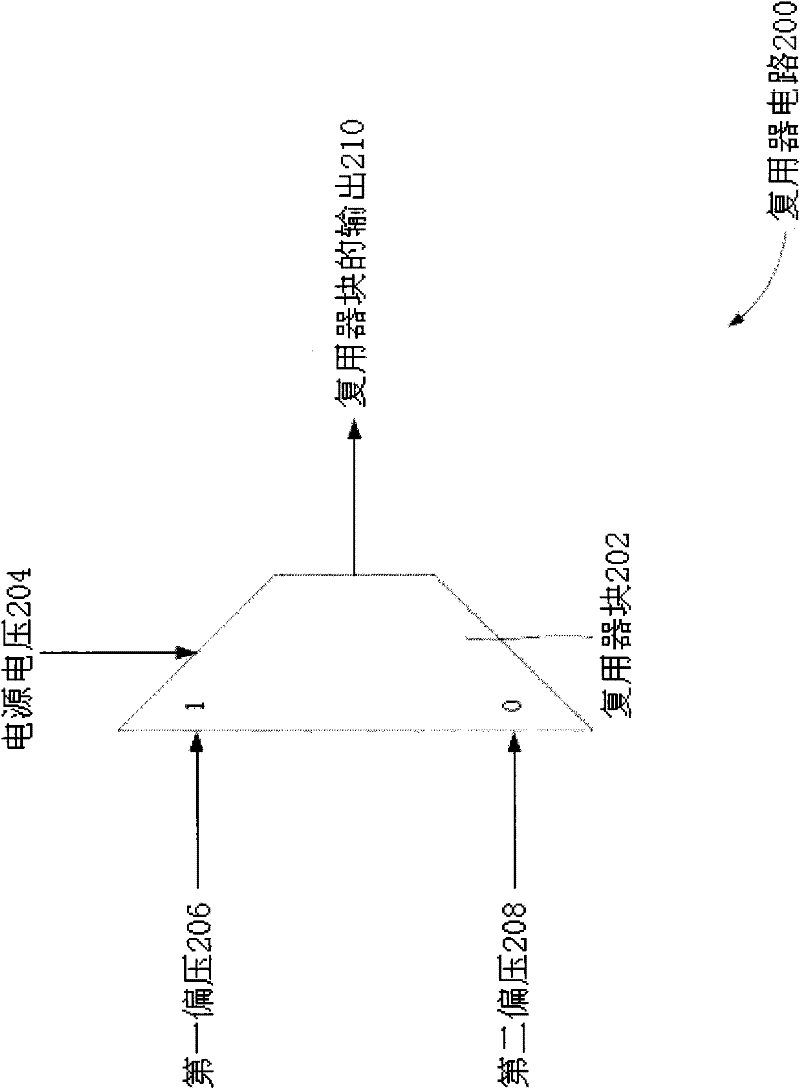

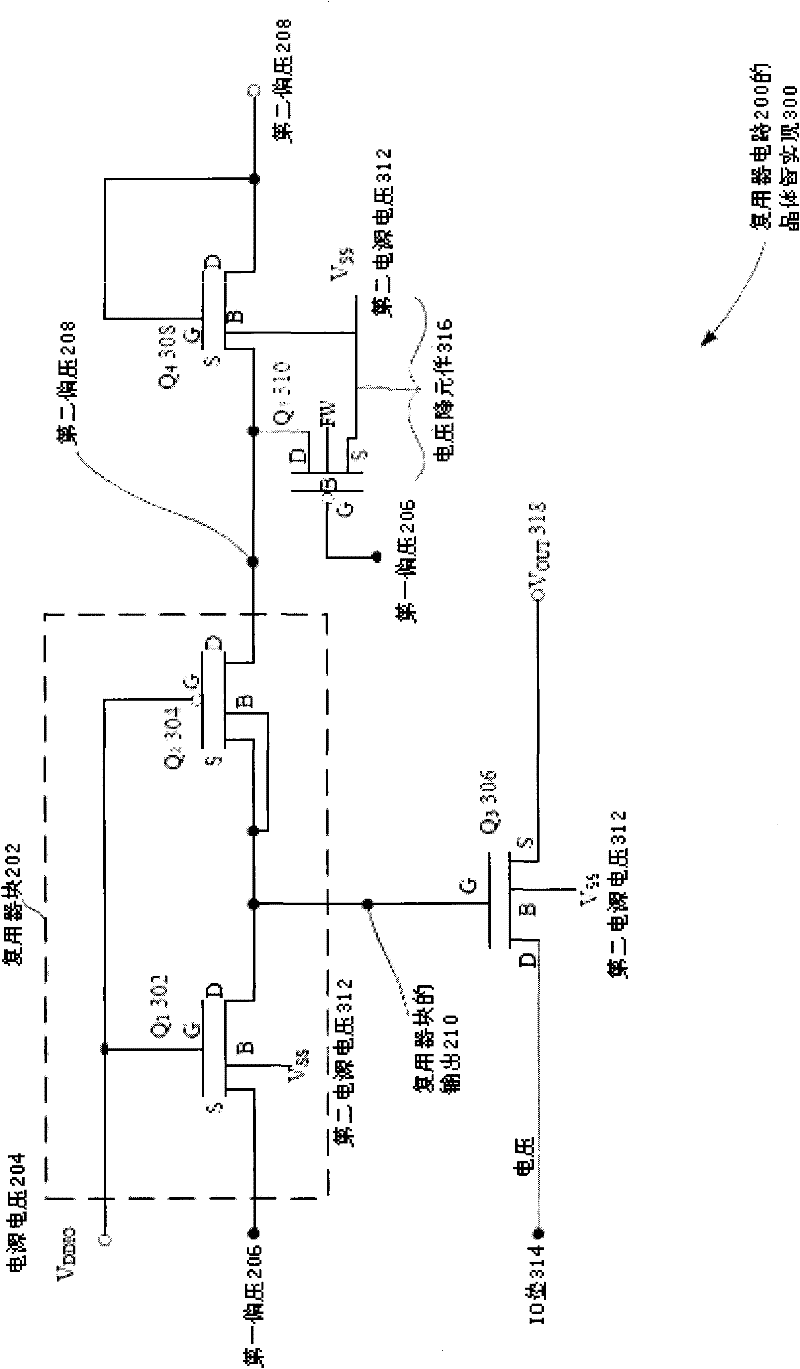

[0025] figure 2 A multiplexer circuit 200 is shown in accordance with one or more embodiments. In one or more embodiments, the multiplexer circuit 200 includes a multiplexer block 202 that can receive as inputs a first bias voltage 206 and a second bias voltage 208 . In one or more embodiments, the first bias voltage 206 can be controllably generated from a supply voltage 204 and the second bias voltage 208 can be controllably generated from an external voltage provided through an input / output (IO) pad. In one or more embodiments, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More