Apparatus and methods for speculative interrupt vector prefetching

A prefetching and instruction technology, applied in the direction of program control design, multi-program device, memory address/allocation/relocation, etc., can solve the problem of reducing processor performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

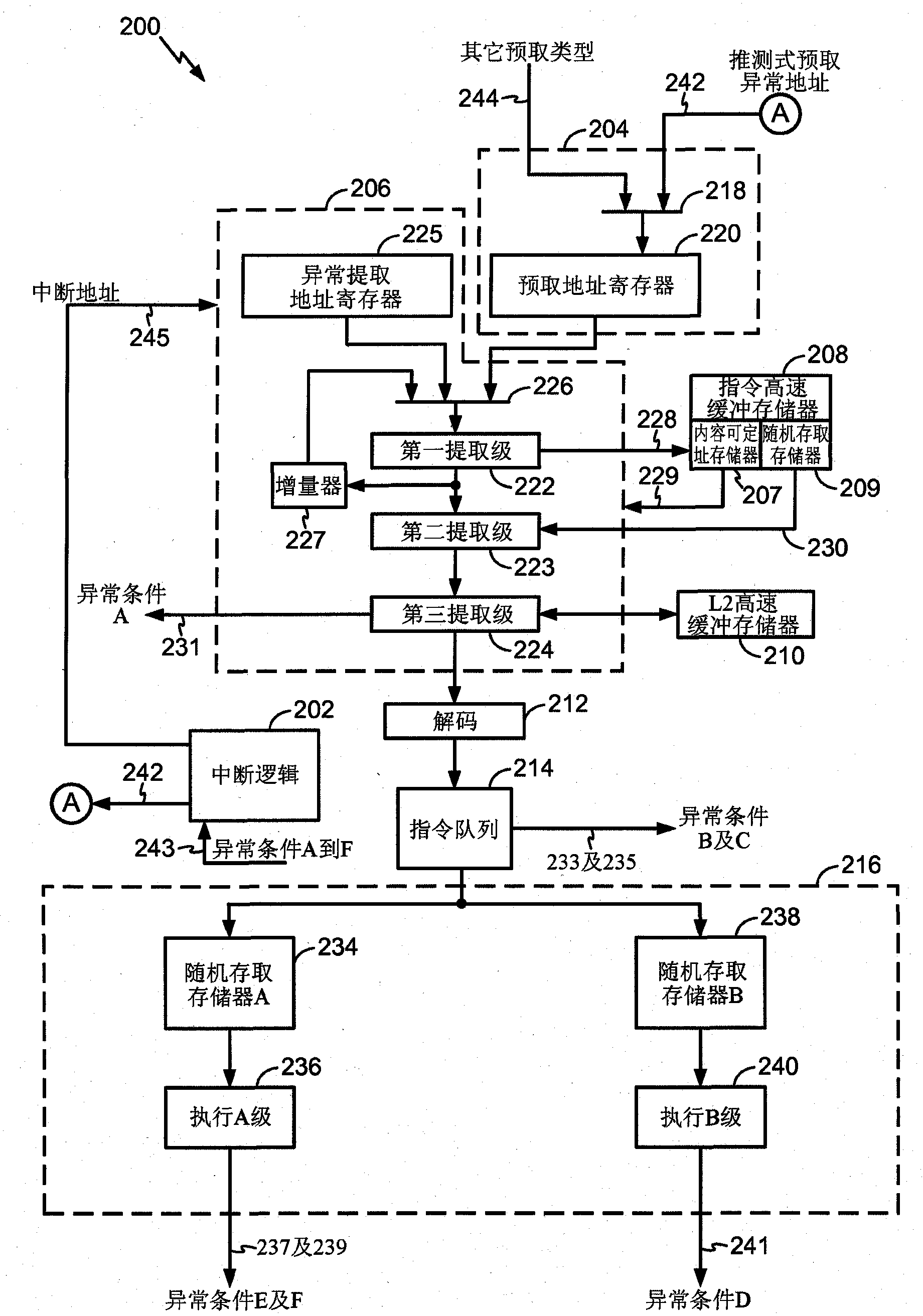

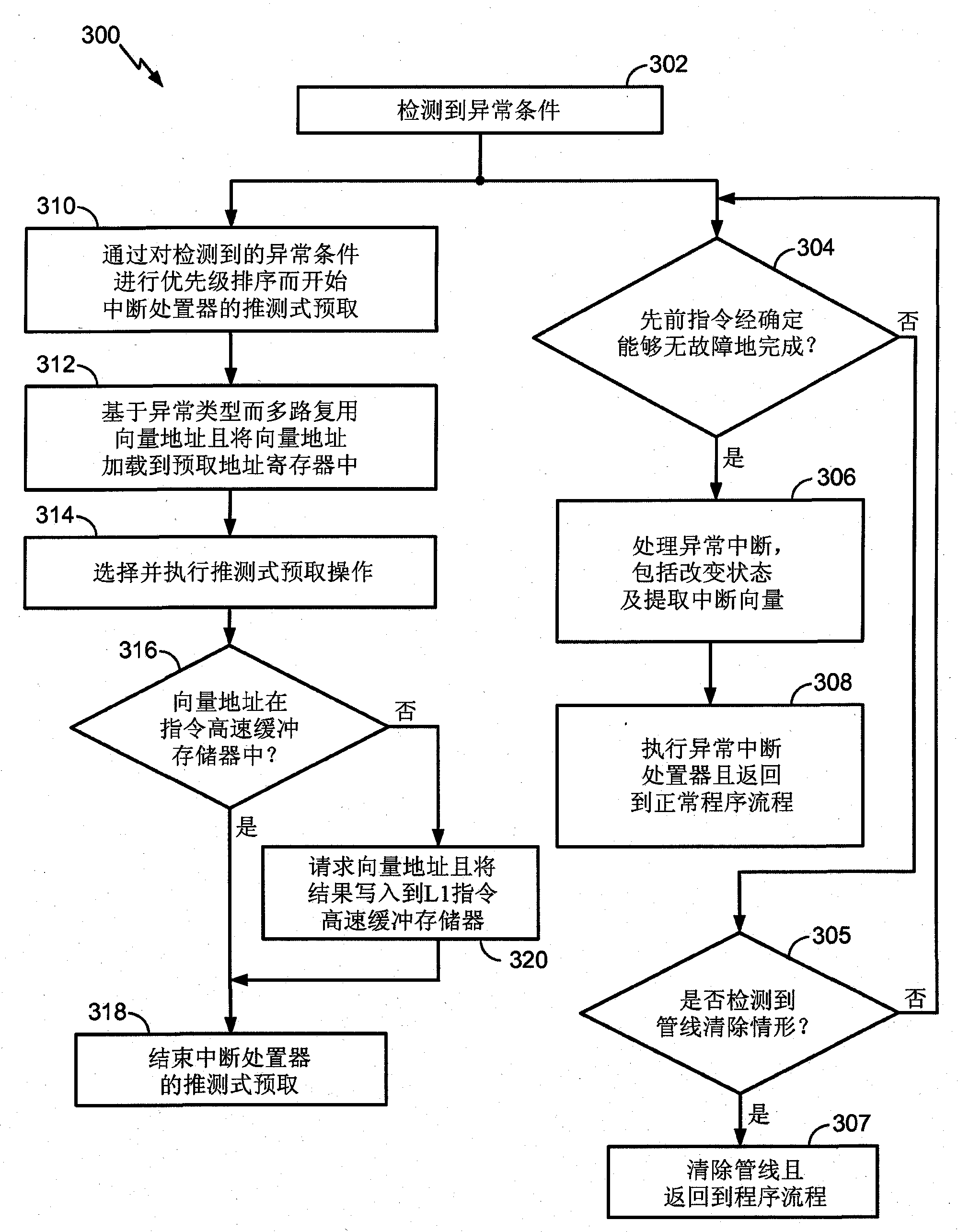

Embodiment Construction

[0016] The embodiments set forth below in conjunction with the appended drawings are intended as a description of various exemplary embodiments of the invention and are not intended to represent the only embodiments in which the invention may be practiced. The embodiments include specific details for the purpose of providing a thorough understanding of the invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without these specific details. In some instances, well-known structures and components are shown in block diagram form in order to avoid obscuring the concepts of the invention.

[0017] Computer program code or "program code" for being operated in accordance with the teachings of the present invention or for performing operations in accordance with the teachings of the present invention may be provided in a high-level programming language such as C, C++, JAVA , Smalltalk, JavaScript 、Visual Basic , TSQL, Per...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More