Patents

Literature

104 results about "Interrupt vector table" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An "interrupt vector table" (IVT) is a data structure that associates a list of interrupt handlers with a list of interrupt requests in a table of interrupt vectors. Each entry of the interrupt vector table, called an interrupt vector, is the address of an interrupt handler. While the concept is common across processor architectures, IVTs may be implemented in architecture-specific fashions. For example, a dispatch table is one method of implementing an interrupt vector table.

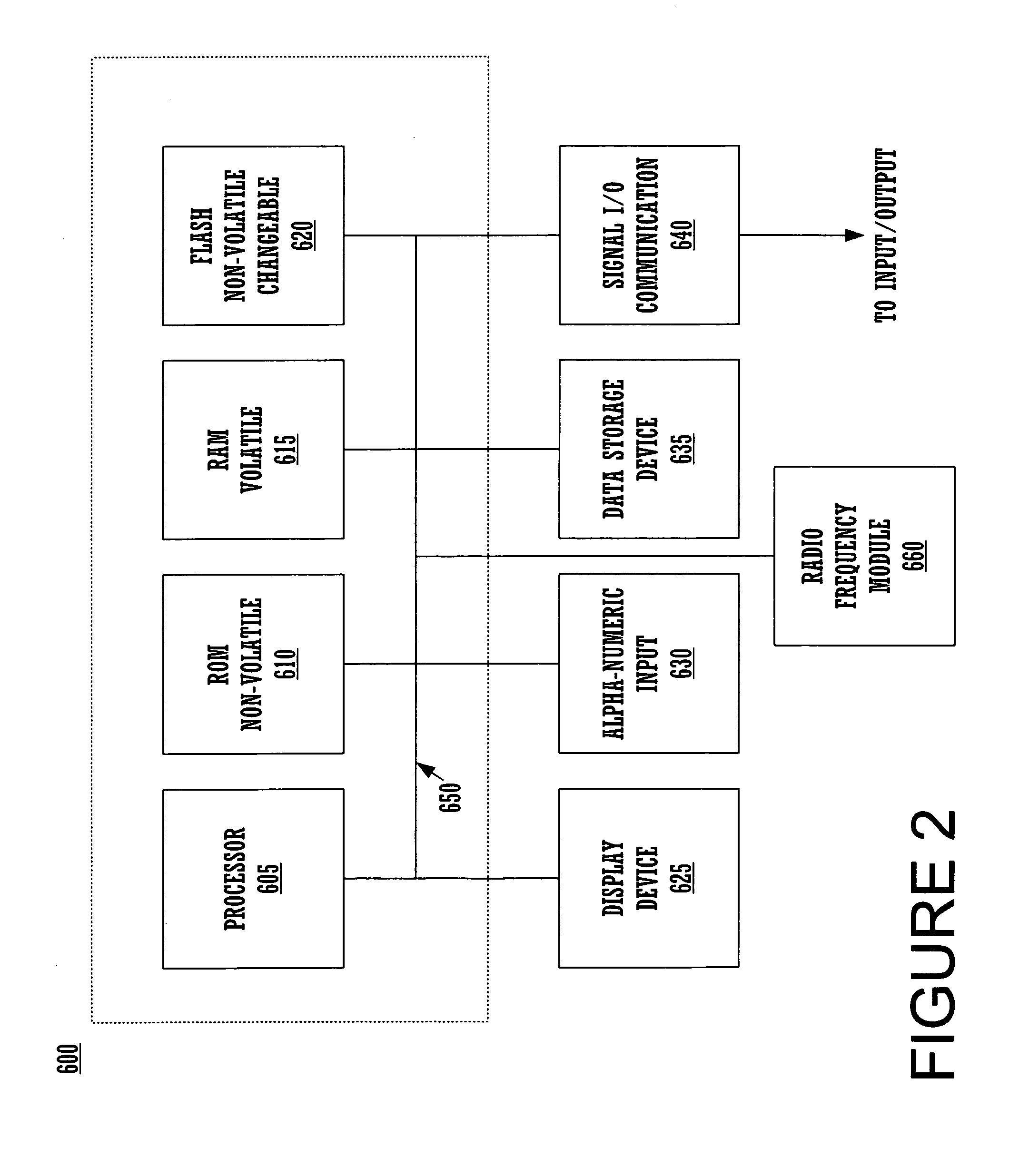

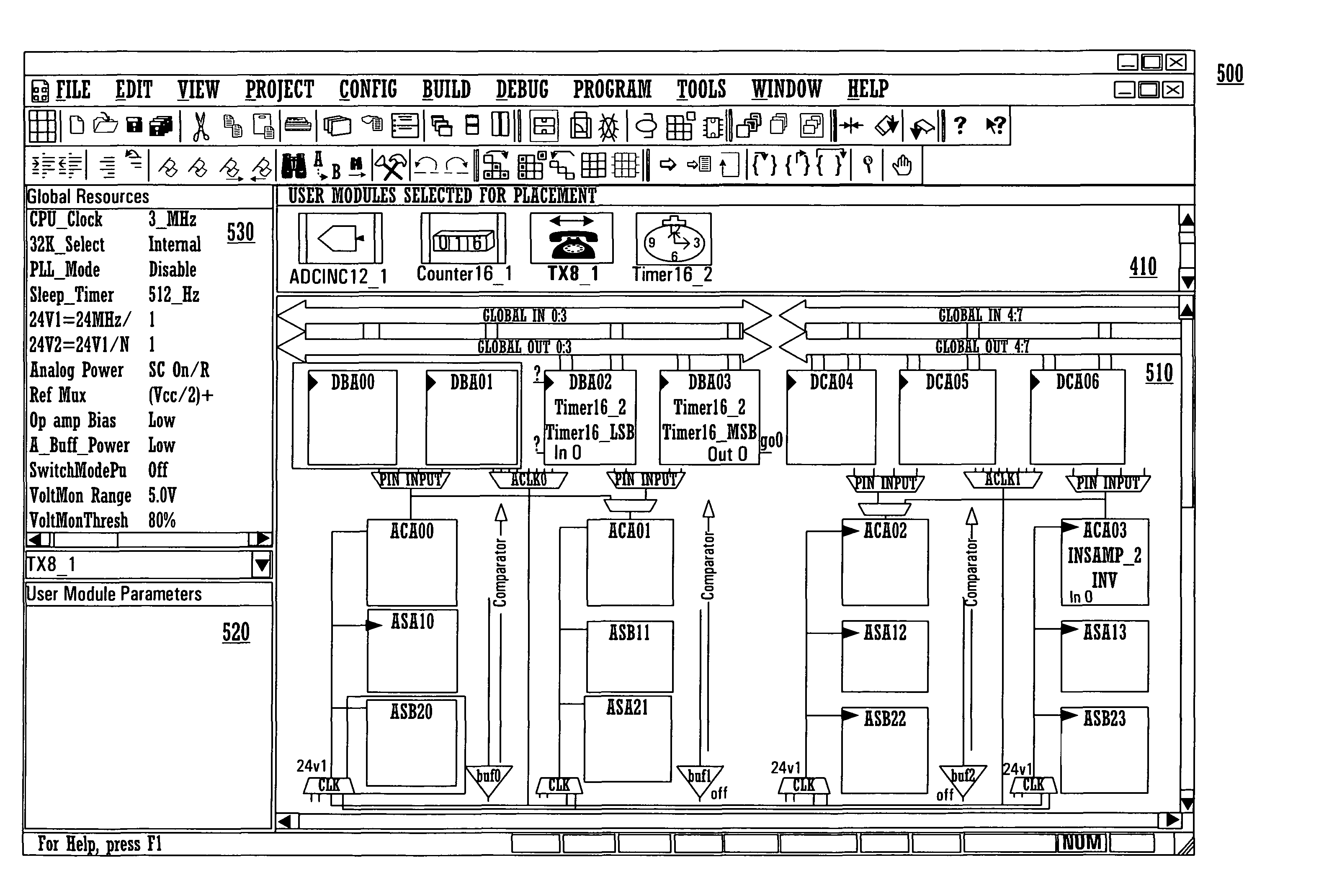

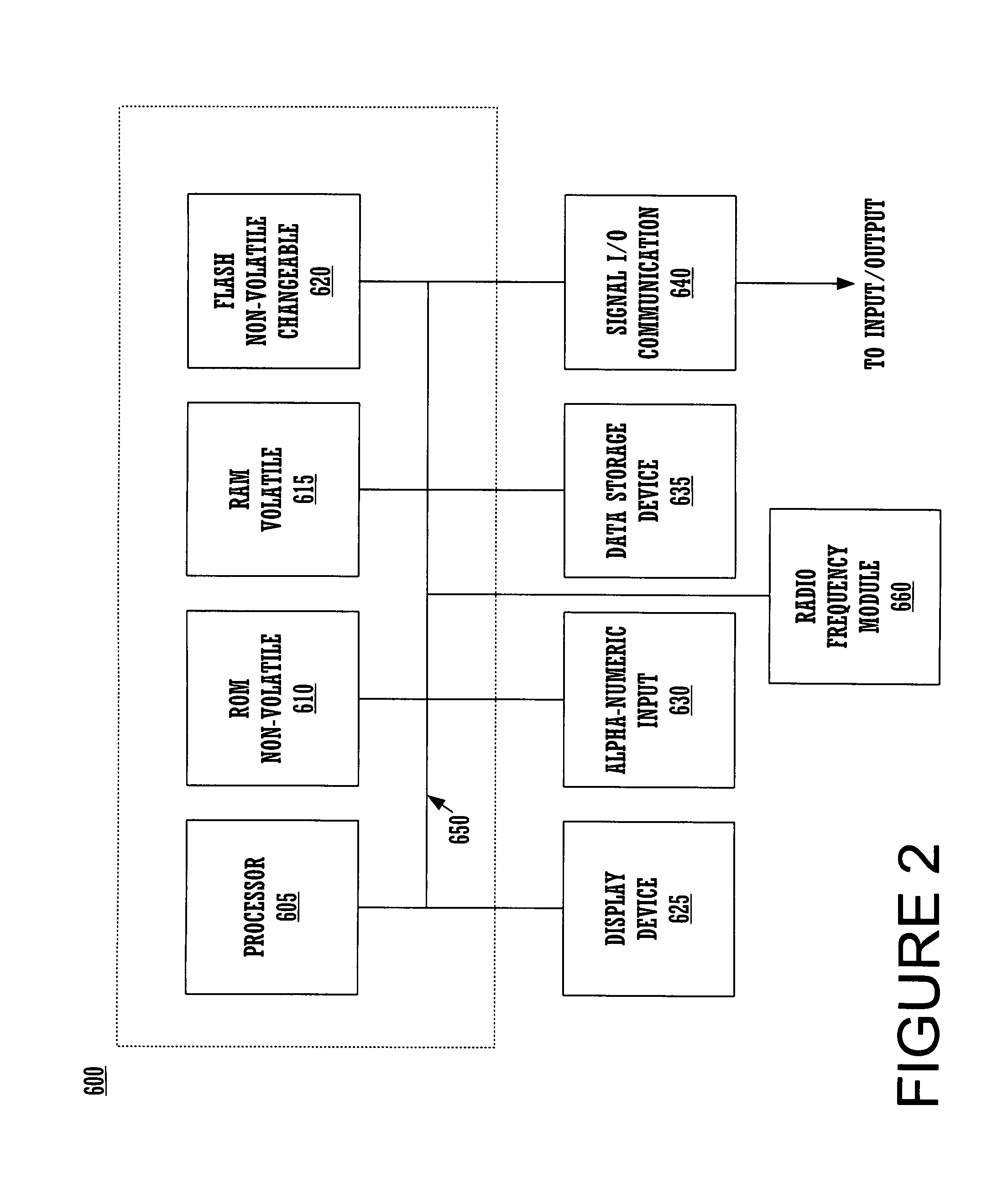

Method for facilitating microcontroller programming

InactiveUS6966039B1Easy programmingConvenient user-friendly interfaceComputer programmed simultaneously with data introductionCAD circuit designGraphicsMicrocontroller

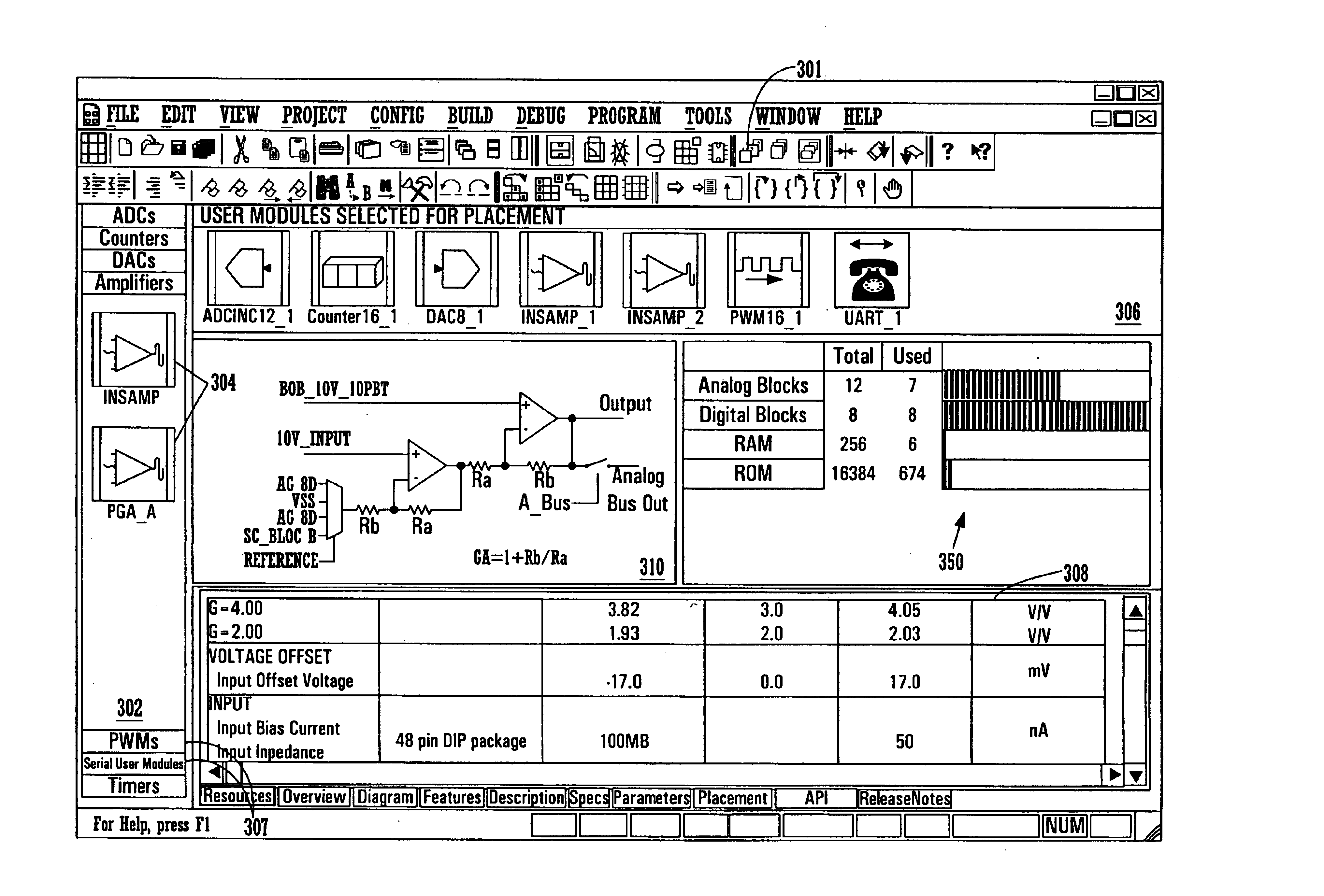

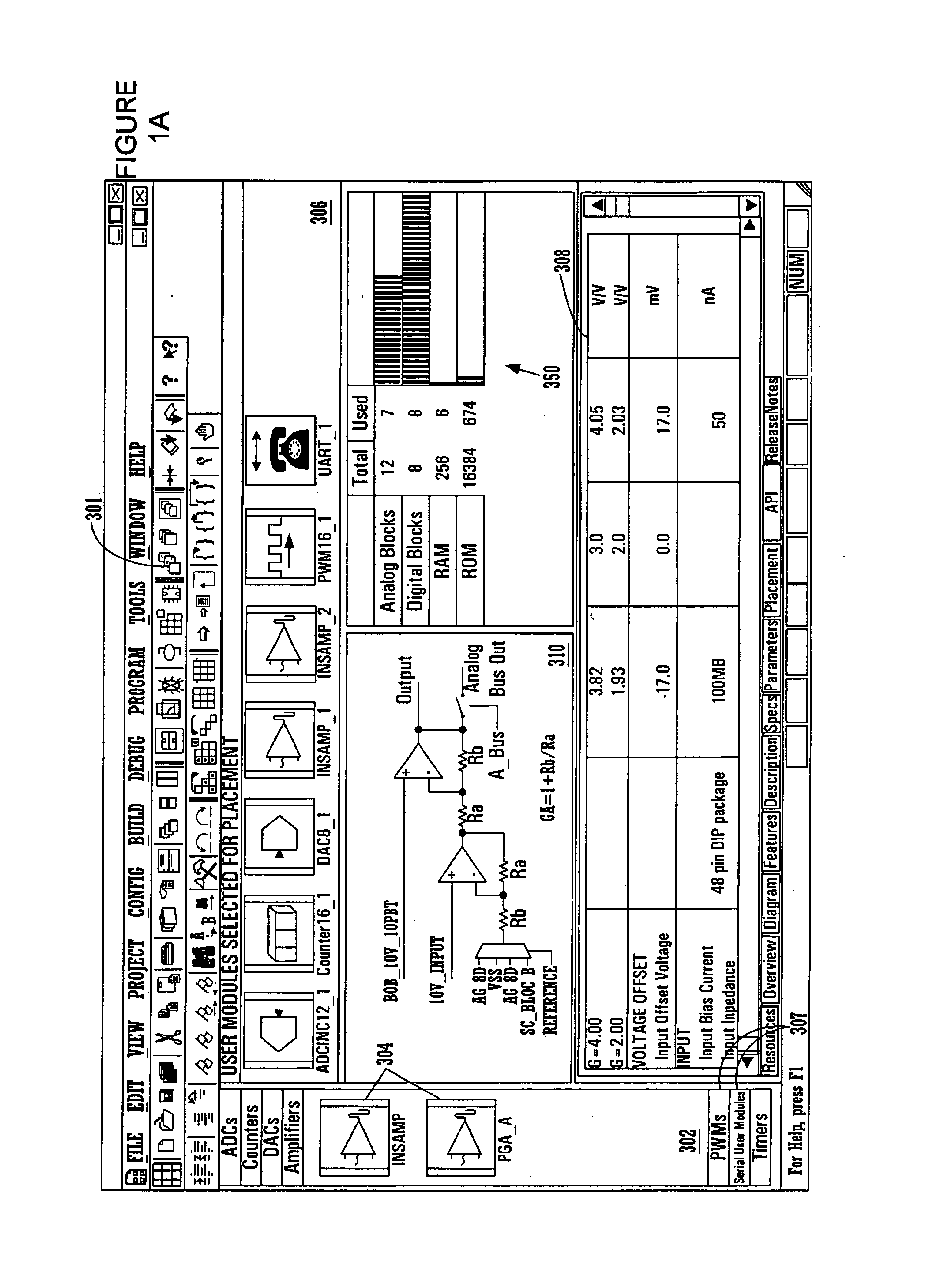

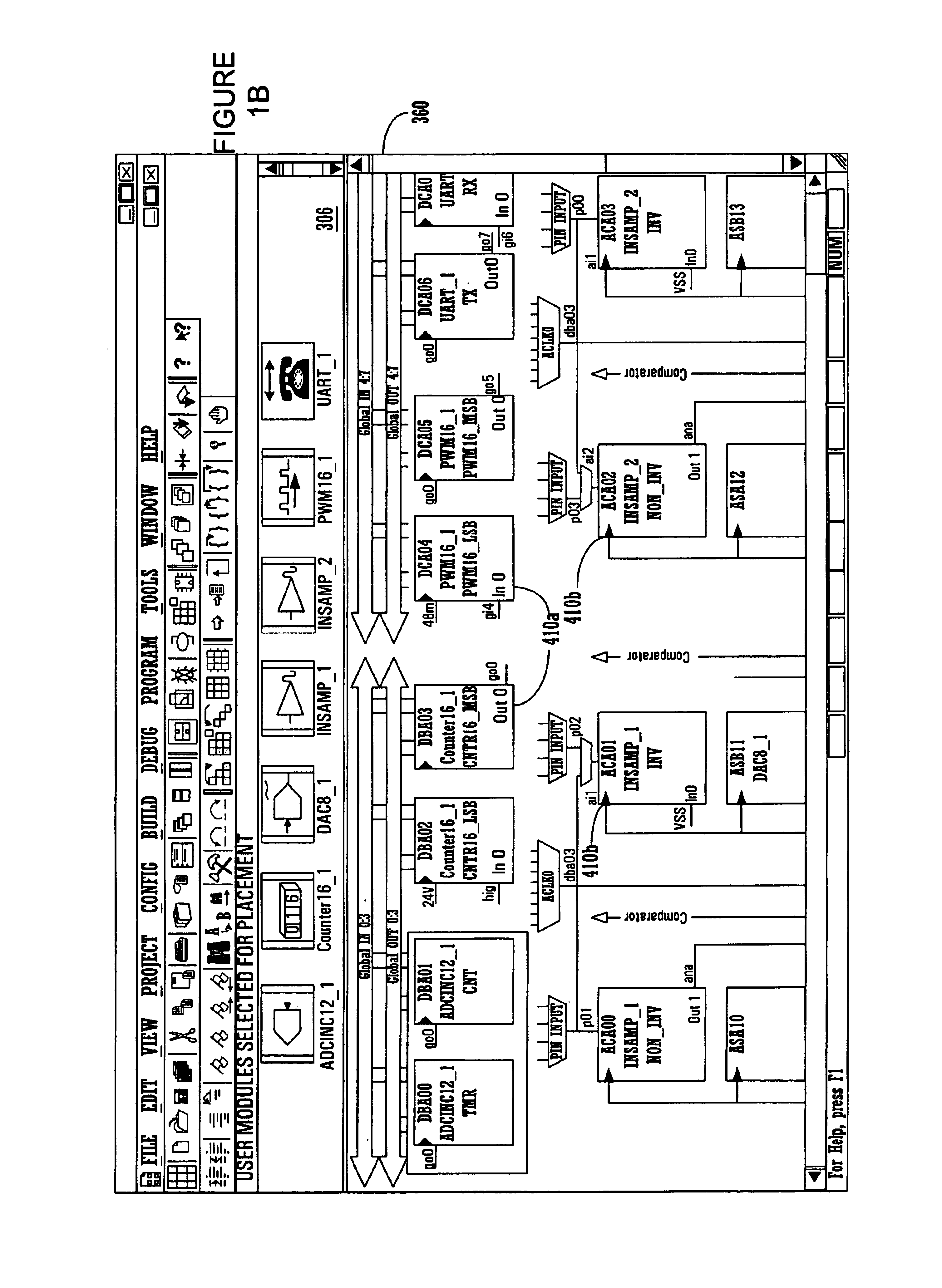

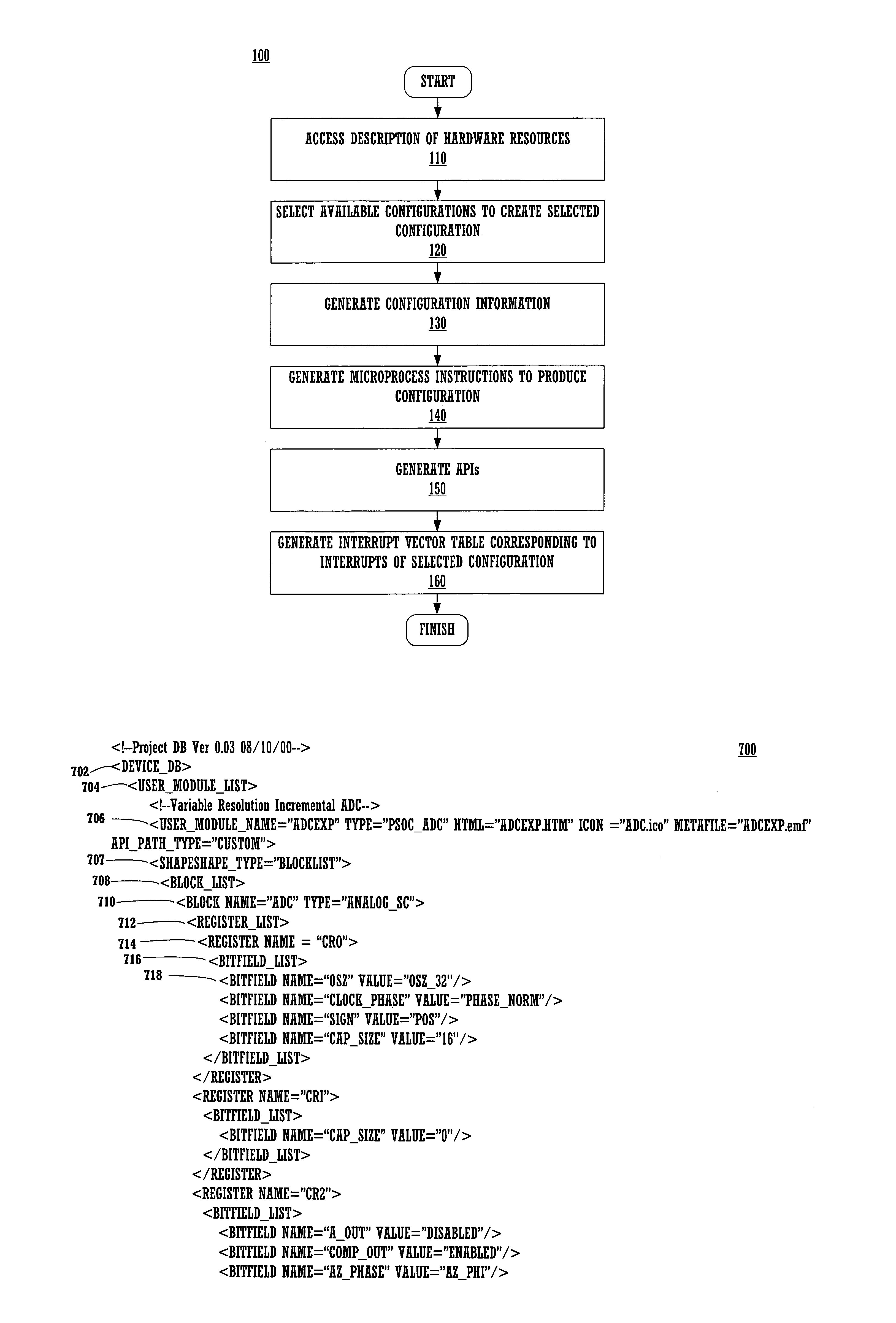

A method to facilitate circuit design. First, a schematic and data sheet for a selected module may be displayed. Next, in response to a request for a position for the module among available resources (e.g., programmable system blocks), a potential position for the module is computed. The position is displayed on a graphical user interface by mapping the module to one or more programmable system blocks. Additional user modules may then be selected and placed. After allowing the user to configure the circuit by selecting circuit parameters and pin-outs, various items are automatically generated to facilitate programming the target device. For example, application programming interfaces (APIs) for programming an operation of the modules, source code for realizing the modules in the resources, an interrupt vector table, and a data sheet for the circuit may be automatically generated.

Owner:MONTEREY RES LLC

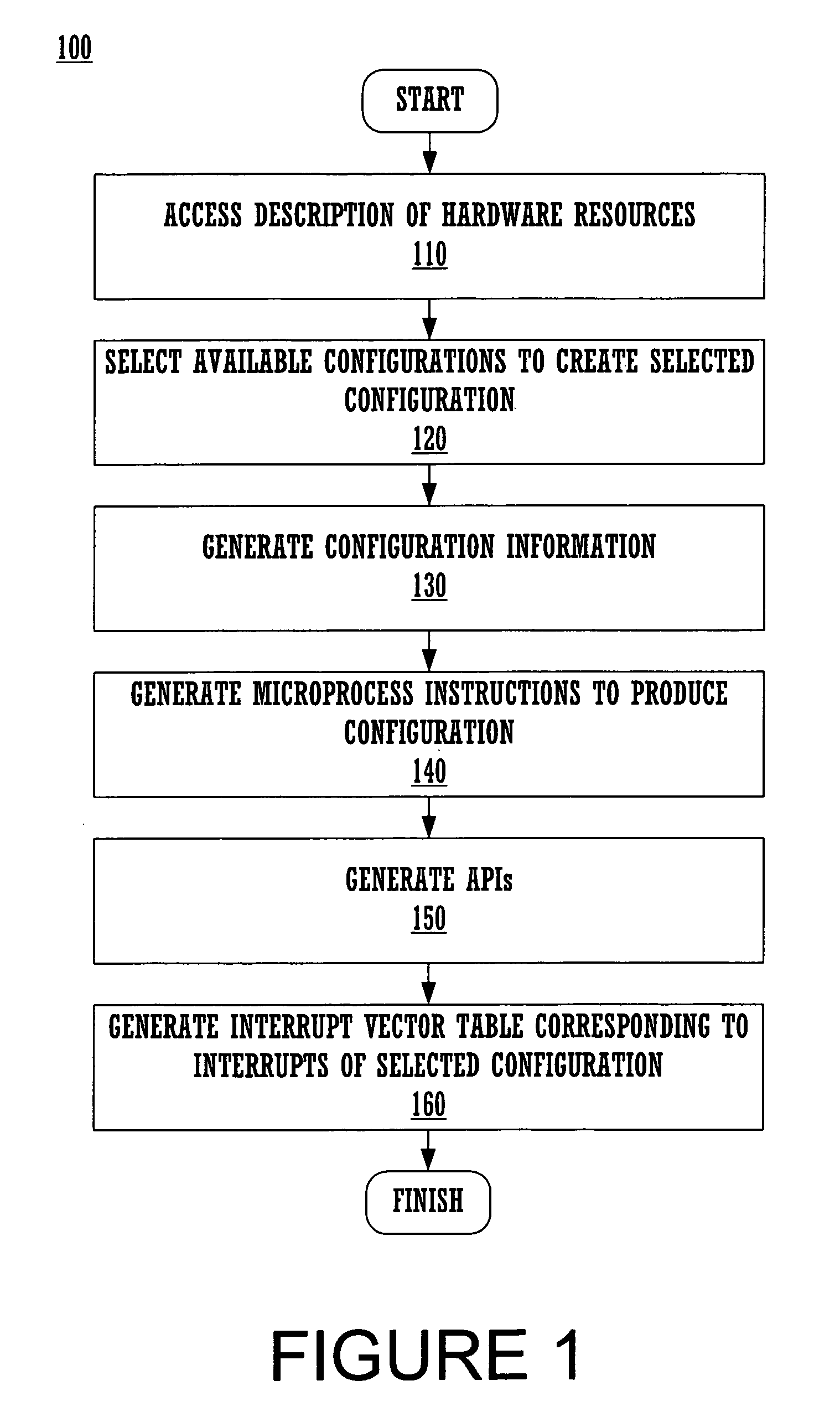

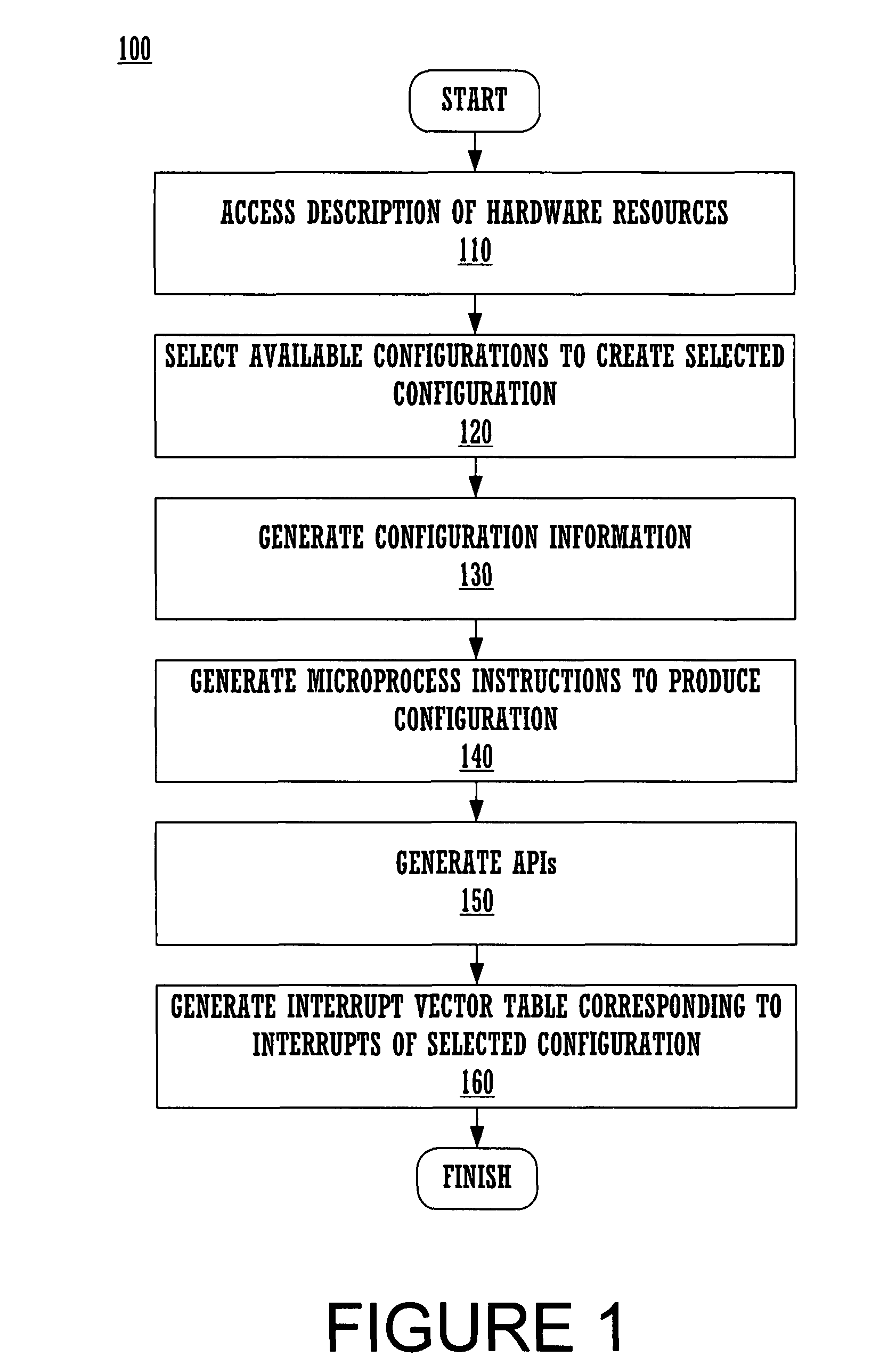

Method and apparatus for generating microcontroller configuration information

ActiveUS7406674B1Improve usabilityIncreased complexityCAD circuit designVisual/graphical programmingMicrocontrollerApplication programming interface

A method and apparatus for configuring a microcontroller. An XML description of the microcontroller's hardware resources may be accessed. A user may select from available hardware resources and pre-defined user modules to select a configuration. Configuration information, which may include register bit patterns and microprocessor instructions, may be automatically generated. Additionally, application programming interface calls and structure, as well as interrupt vector tables may be automatically generated. Embodiments of the present invention provide improved ease of use and the ability to manage greater complexity in the configuration of configurable microcontrollers.

Owner:CYPRESS SEMICON CORP

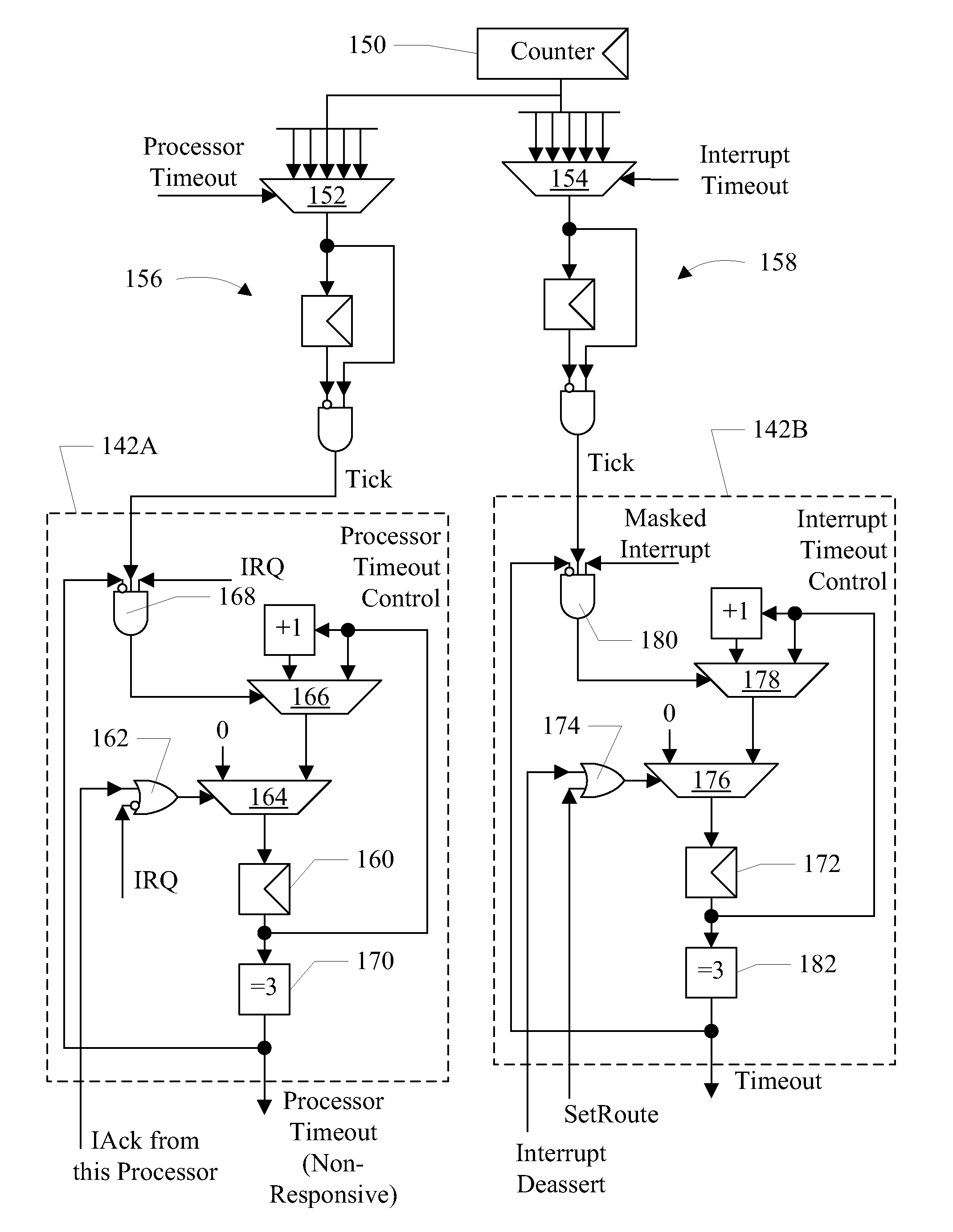

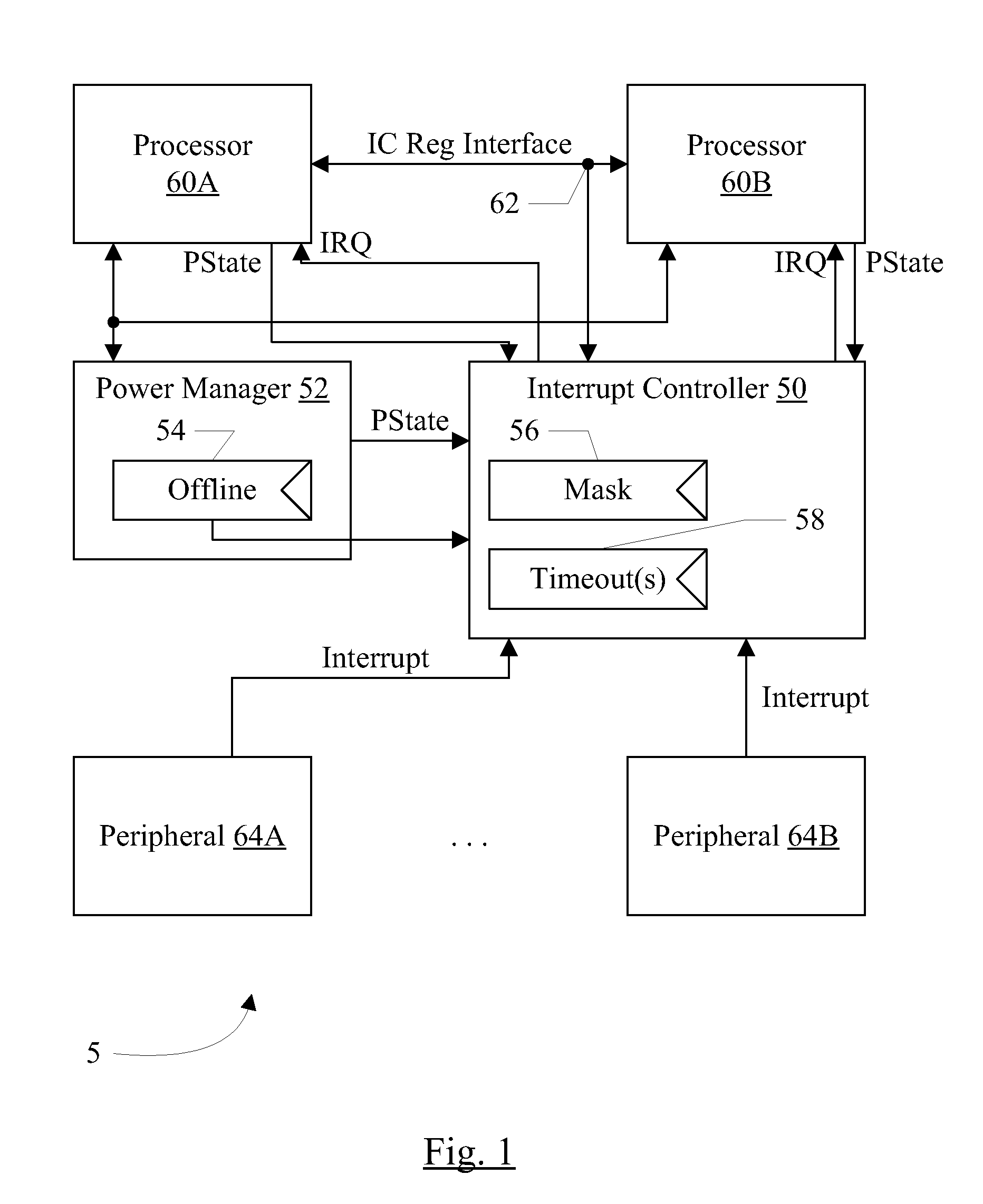

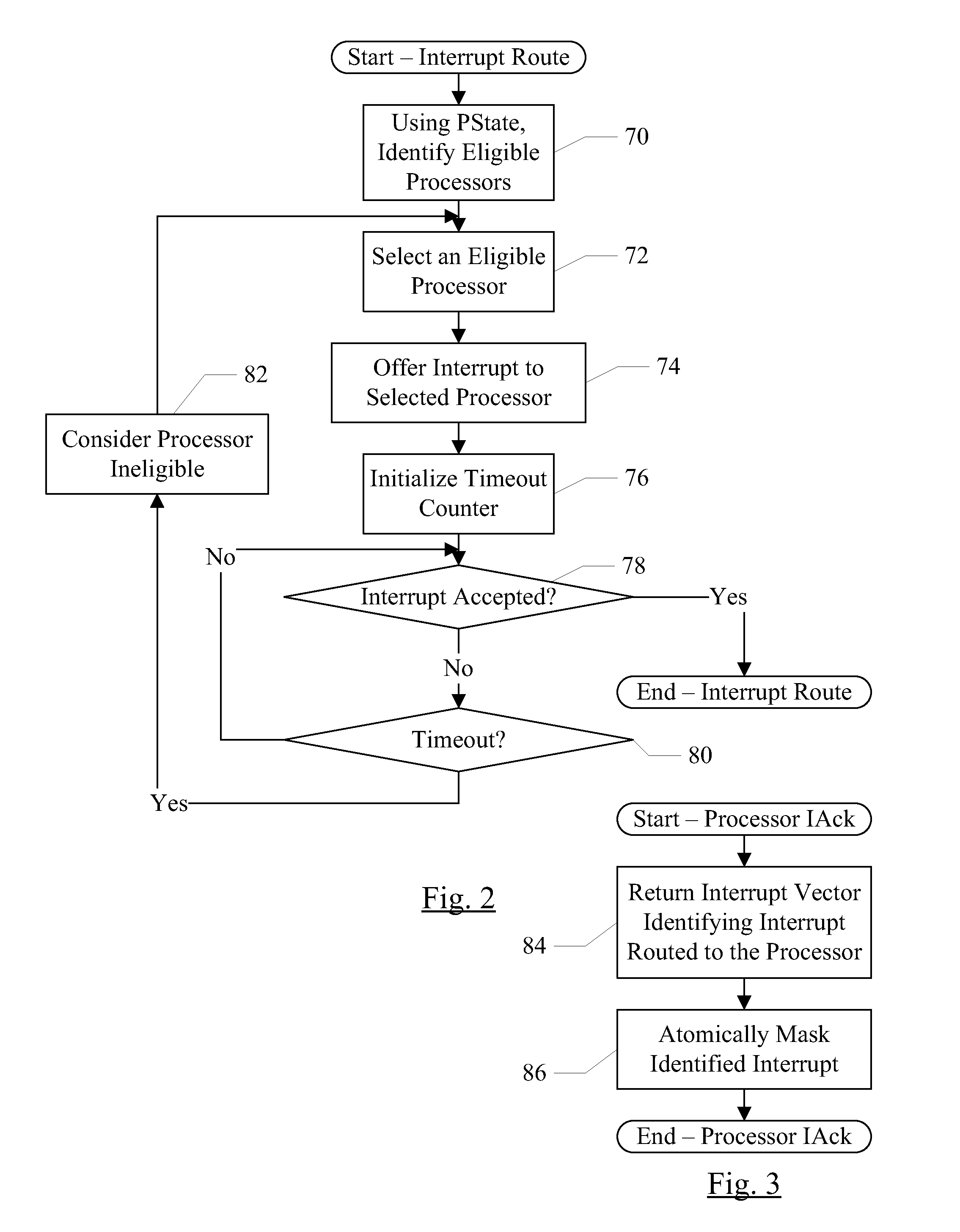

Interrupt Distribution Scheme

ActiveUS20120144172A1Reduce Interrupt LatencyEnergy efficient ICTProgram initiation/switchingSleep stateComputer science

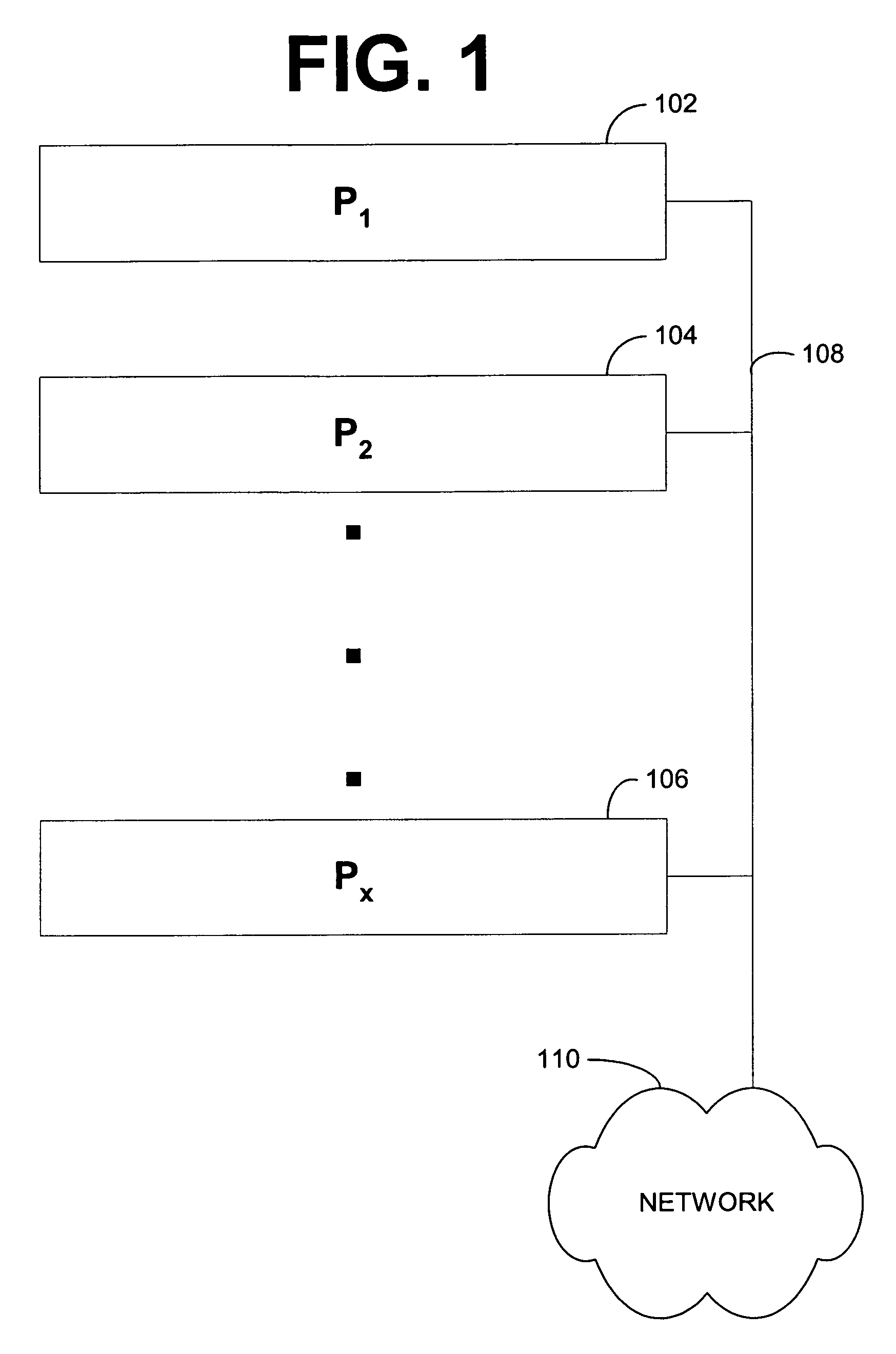

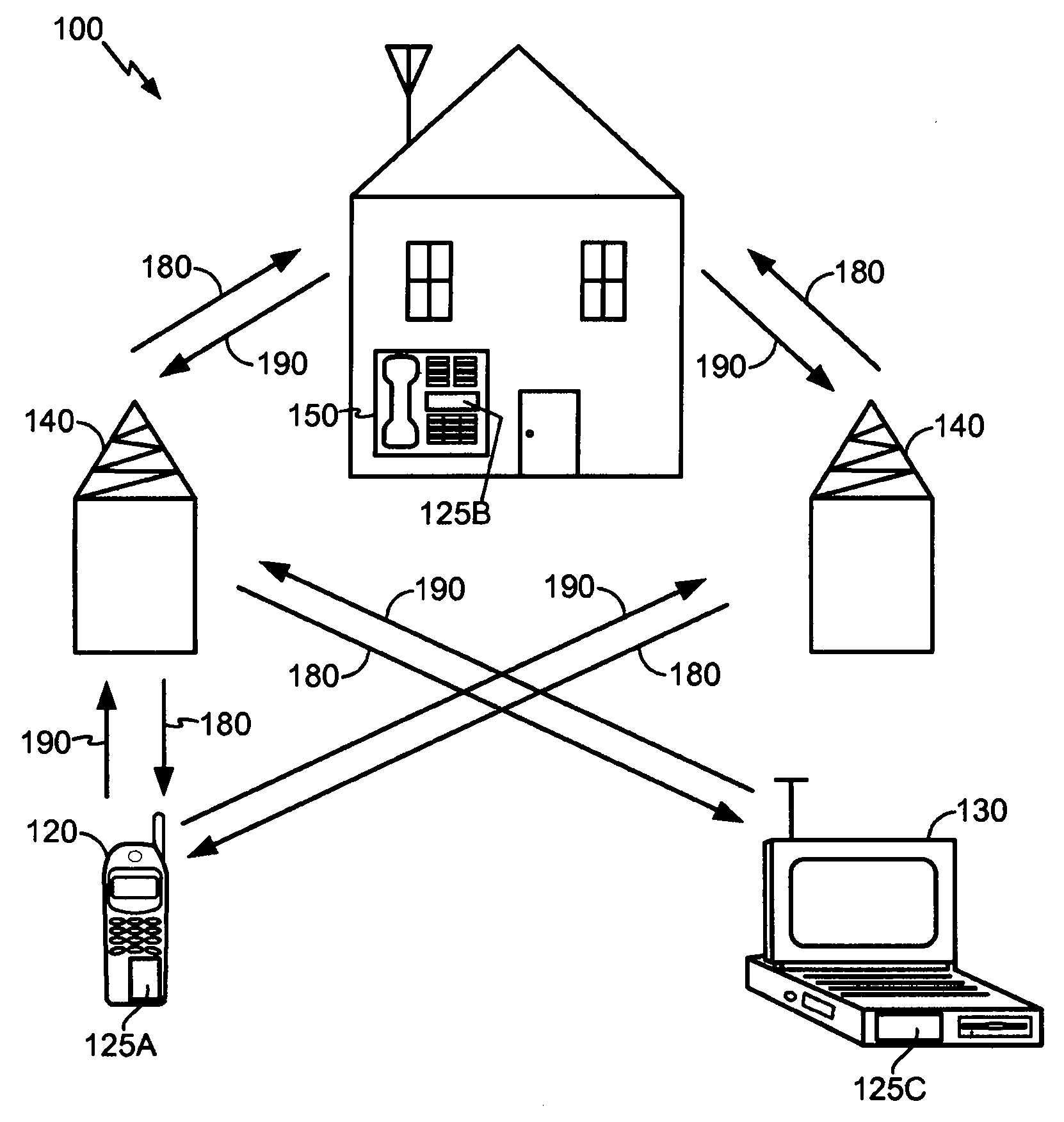

In one embodiment, an interrupt controller may implement an interrupt distribution scheme for distributing interrupts among multiple processors. The scheme may take into account various processor state in determining which processor should receive a given interrupt. For example, the processor state may include whether or not the processor is in a sleep state, whether or not interrupts are enabled, whether or not the processor has responded to previous interrupts, etc. The interrupt controller may implement timeout mechanisms to detect that an interrupt is being delayed (e.g. after being offered to a processor). The interrupt may be re-evaluated at the expiration of a timeout, and potentially offered to another processor. The interrupt controller may be configured to automatically, and atomically, mask an interrupt in response to delivering an interrupt vector for the interrupt to a responding processor.

Owner:APPLE INC

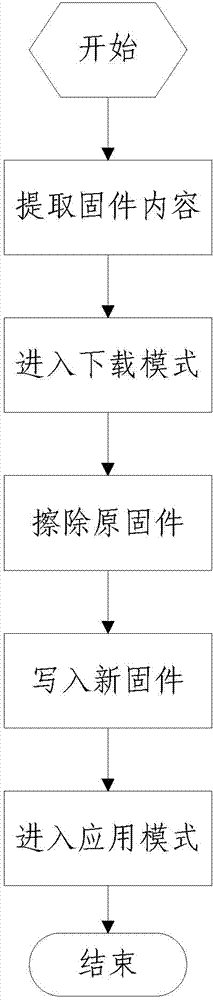

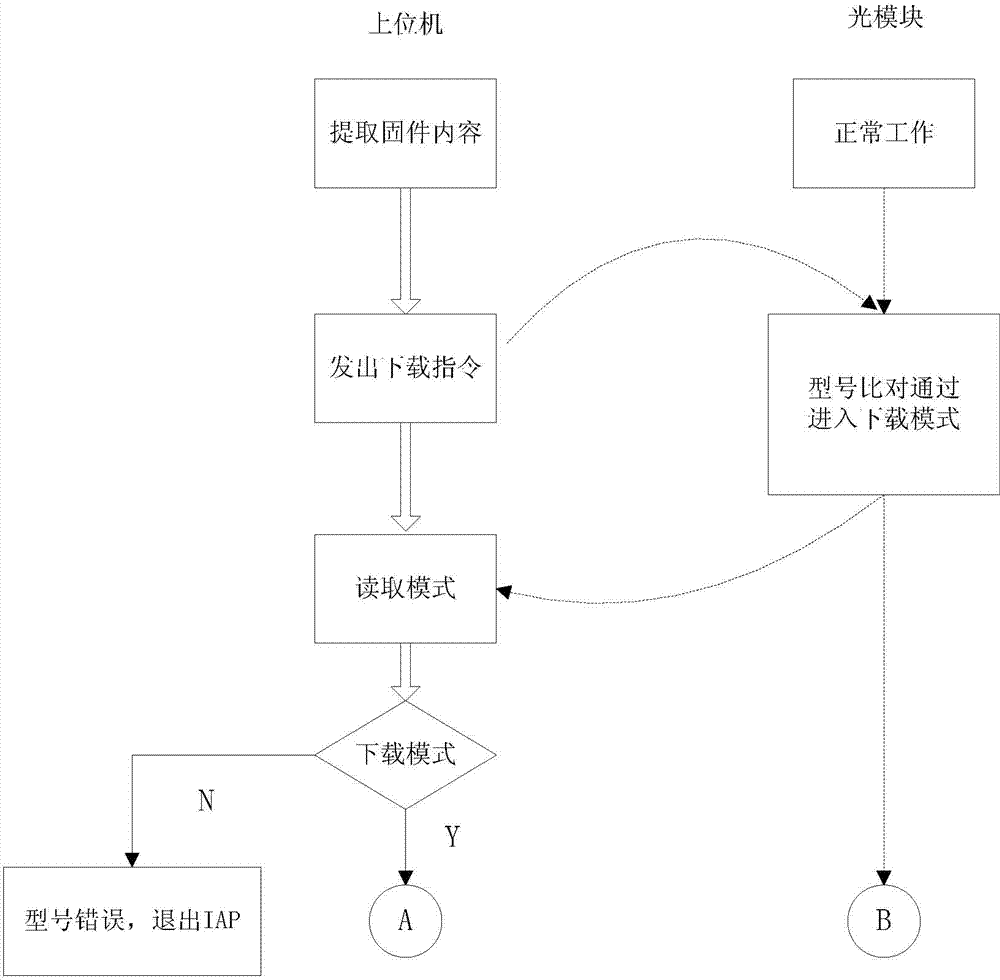

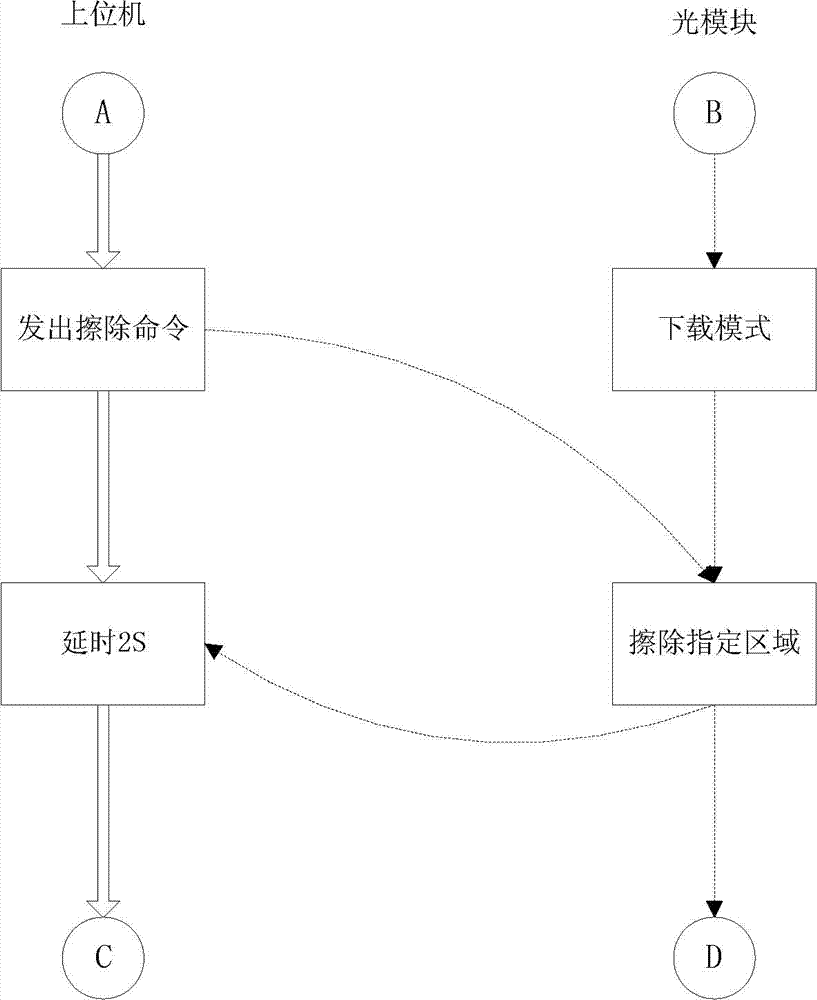

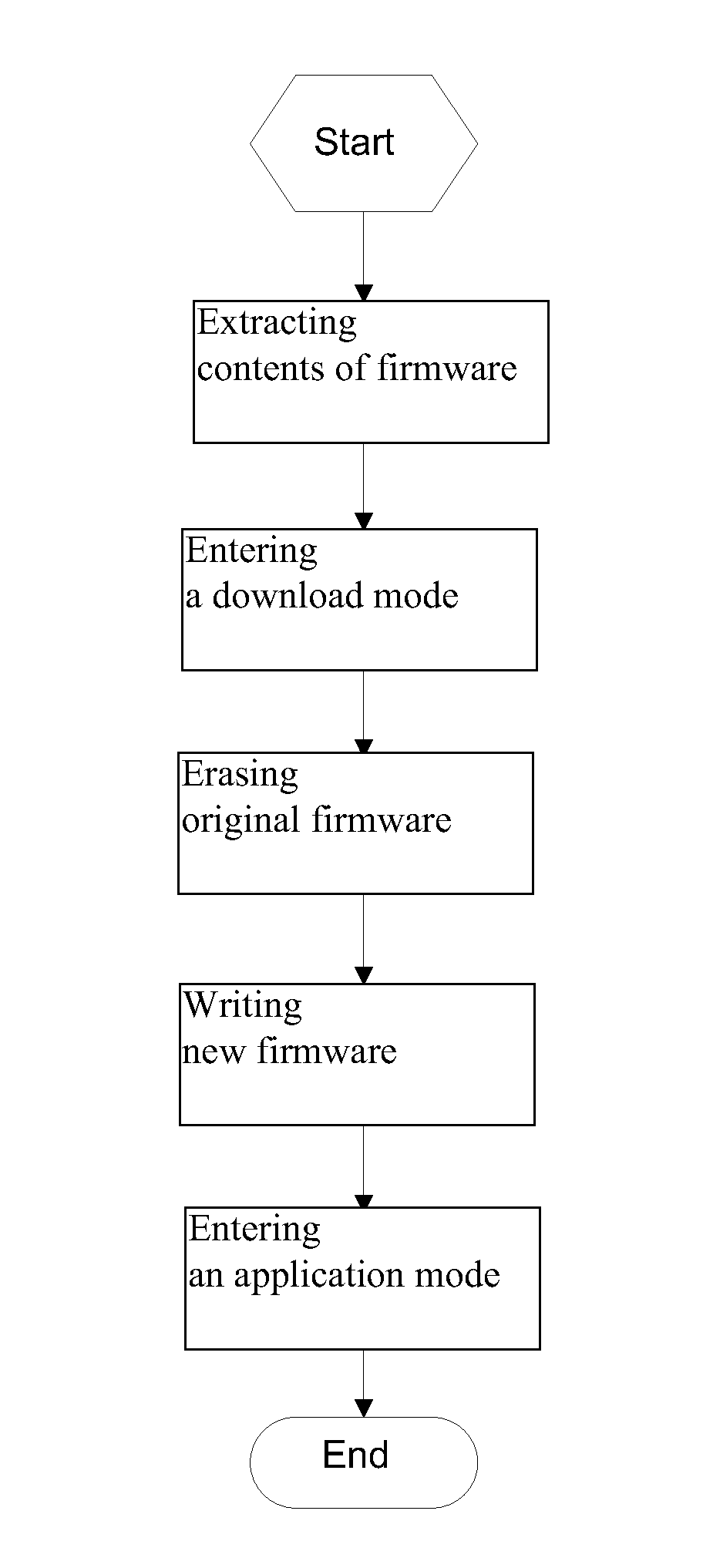

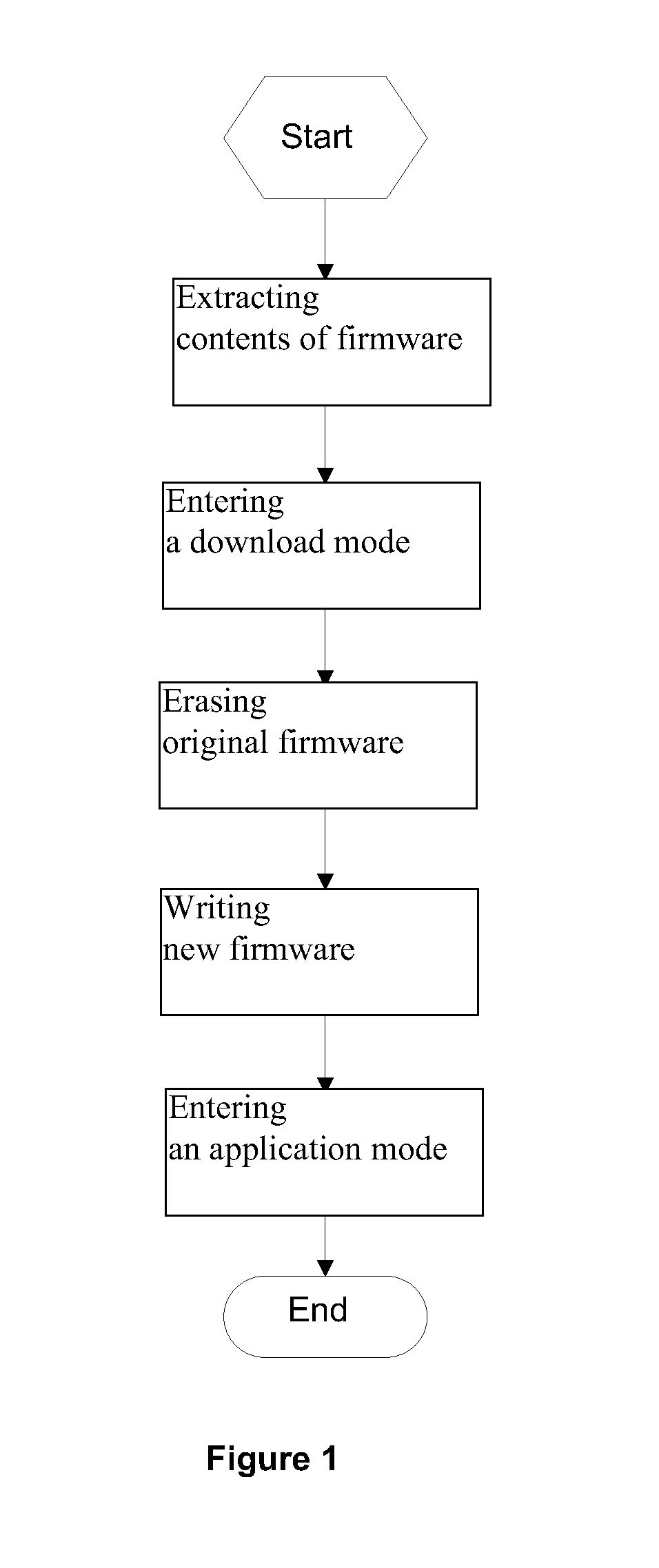

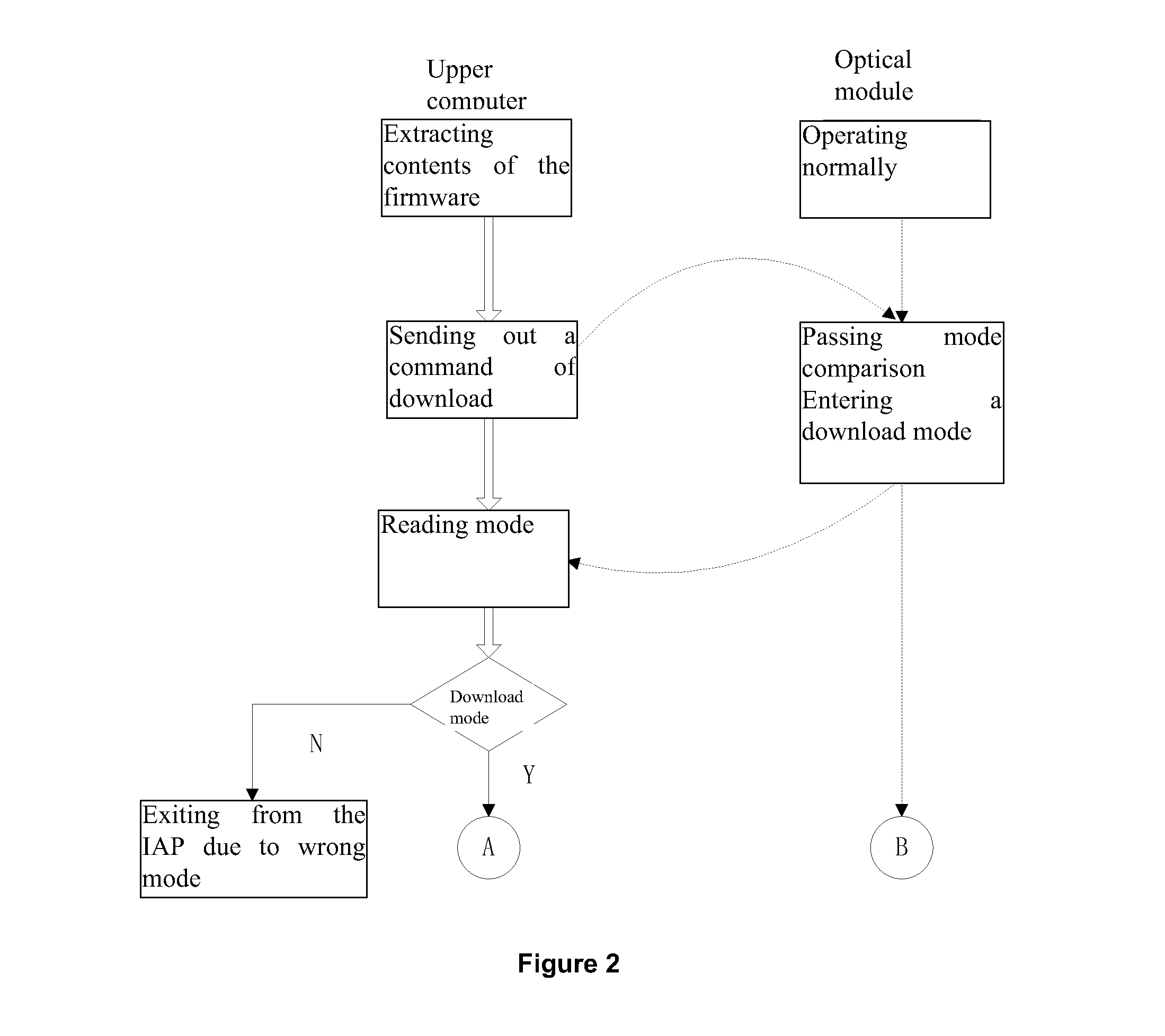

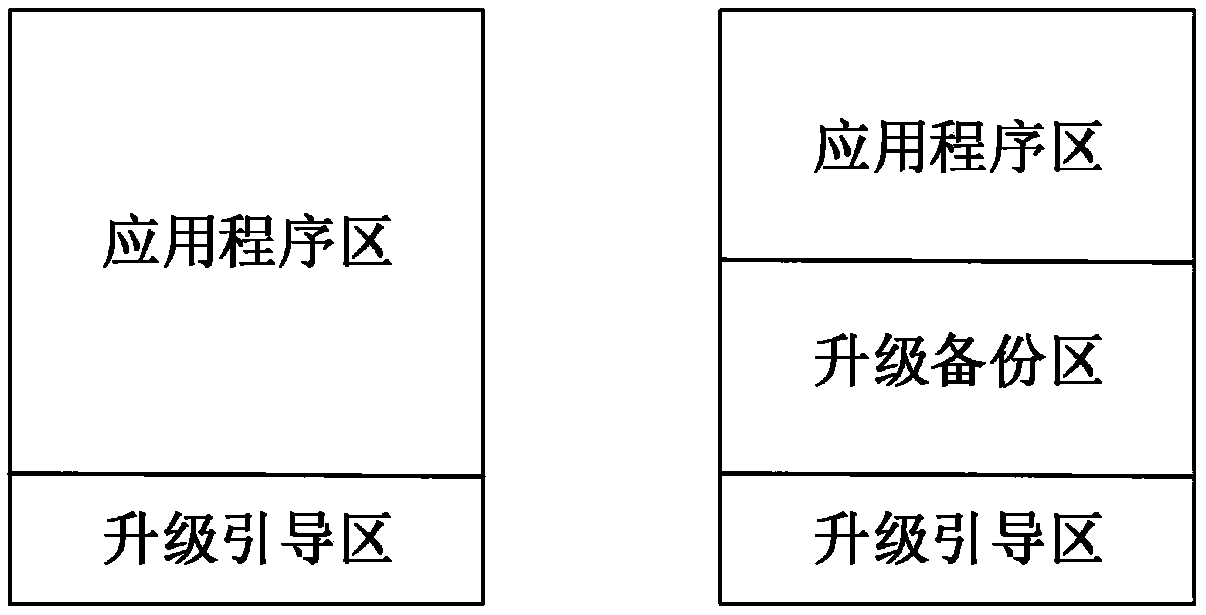

Optical module firmware in-application upgrading method capable of not interrupting service

The invention discloses an optical module firmware in-application upgrading method capable of not interrupting service. Two areas are set in an optical module internal program storage area and are respectively used for storing an upgrade program and an application program, a special area is set and used for backing up an interrupt vector table of a Boot program, an upper computer communicates with an optical module, the interrupt vector table is switched, and the skip between the Boot program and the application program is realized through a program pointer. The method specifically comprises the following steps of: 1) extracting firmware contents; 2) entering a download mode and upgrading a firmware; 3) erasing the original firmware; 4) writing a new firmware; and 5) entering an application mode, wherein after data and codes are verified, the upper computer transmits a download mode exit command, the optical module firmware exits from the upgrade program and is switched to execute the new application program, and the optical module works normally. By adopting the optical module firmware in-application upgrading method capable of not interrupting service, since the switching between the application program and the upgrade program is controlled by the command which is transmitted by the upper computer and an MCU (micro control unit) is not required to be reset, the situation that the work of the optical module is interrupted is not caused.

Owner:WUHAN TELECOMM DEVICES

Dynamic interrupt reconfiguration for effective power management

ActiveUS20130318334A1Digital computer detailsConcurrent instruction executionEffective powerActive core

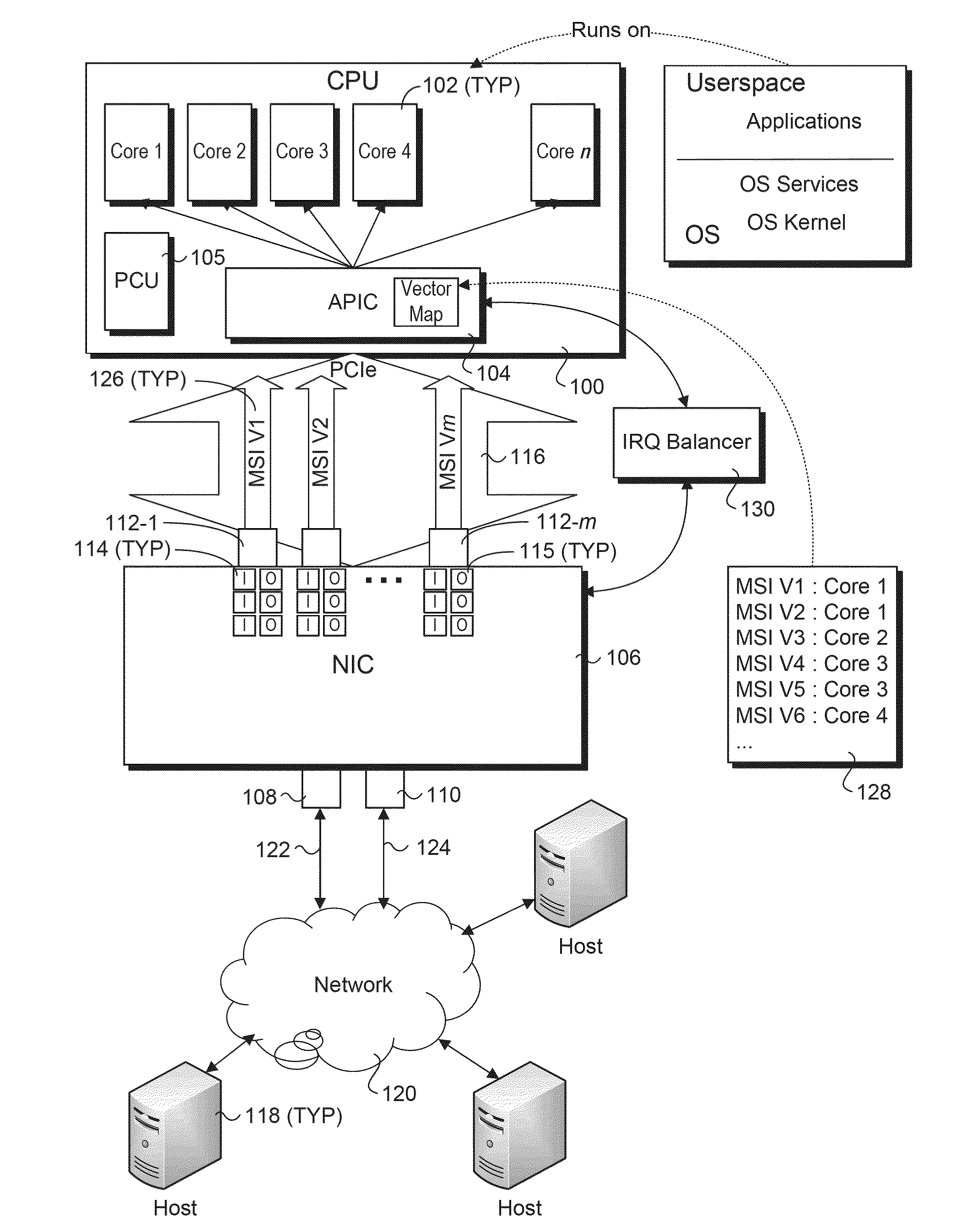

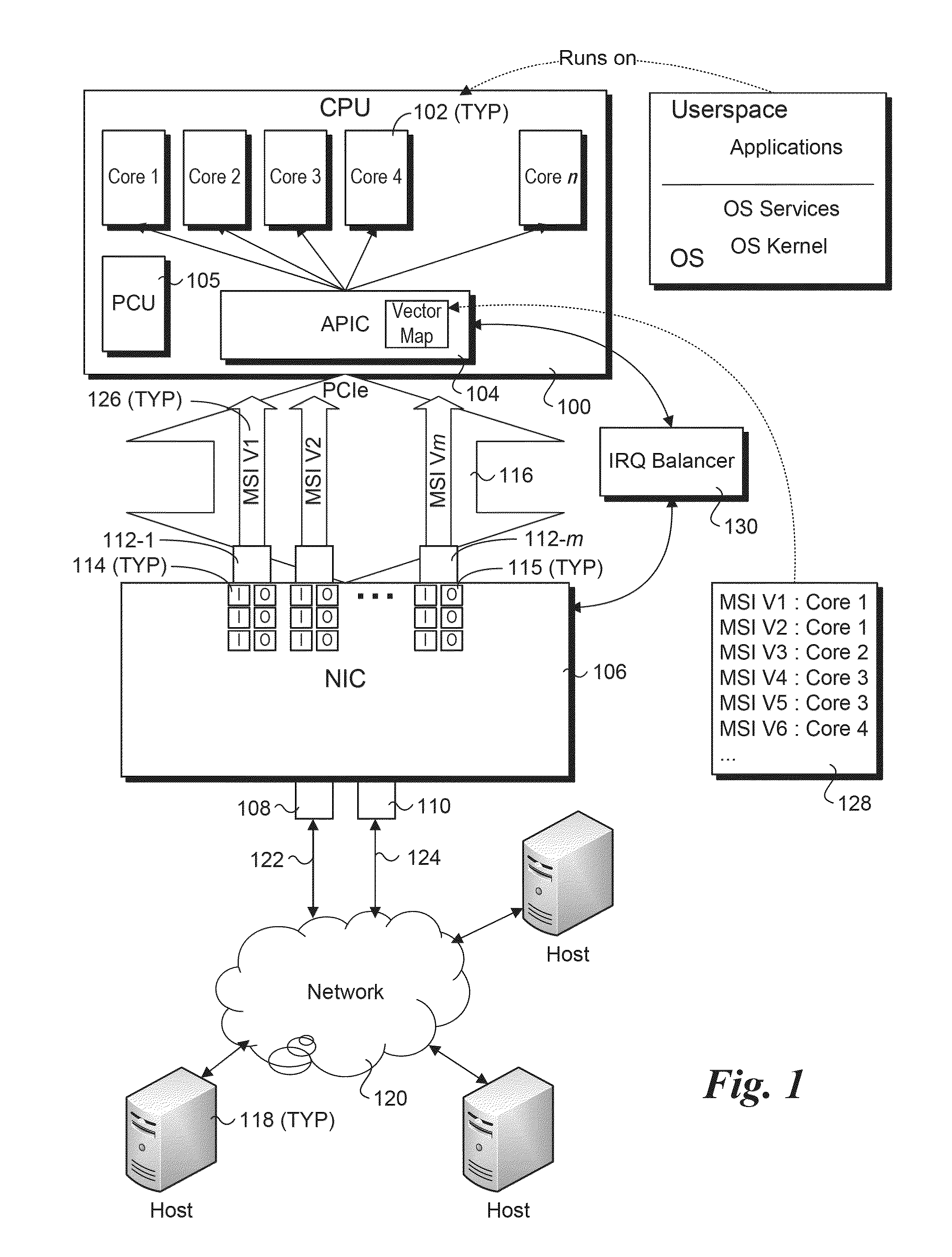

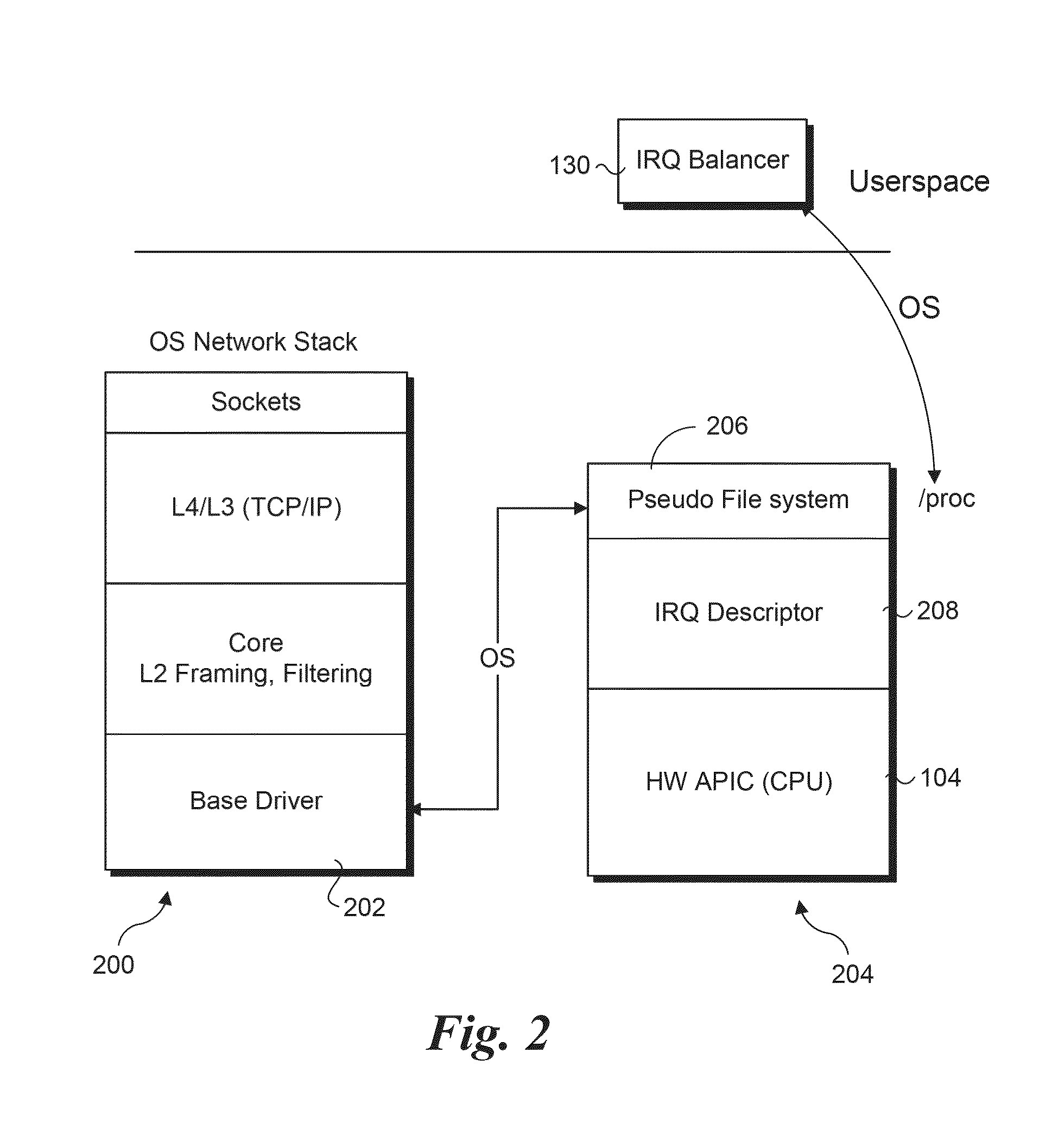

Methods, apparatus, and systems for facilitating effective power management through dynamic reconfiguration of interrupts. Interrupt vectors are mapped to various processor cores in a multi-core processor, and interrupt workloads on the processor cores are monitored. When an interrupt workload for a given processor core is detected to fall below a threshold, the interrupt vectors are dynamically reconfigured by remapping interrupt vectors that are currently mapped to the processor core to at least one other processor core, such that there are no interrupt vectors mapped to the processor core after reconfiguration. The core is then enabled to be put in a deeper idle state. Similar operations can be applied to additional processor cores, effecting a collapsing of interrupt vectors onto fewer processor cores. In response to detecting cores emerging from idle states, reconfiguration of interrupt vectors can be performed to rebalance the assignment of the vectors across active cores by remapping a portion of the vectors to those cores.

Owner:TAHOE RES LTD

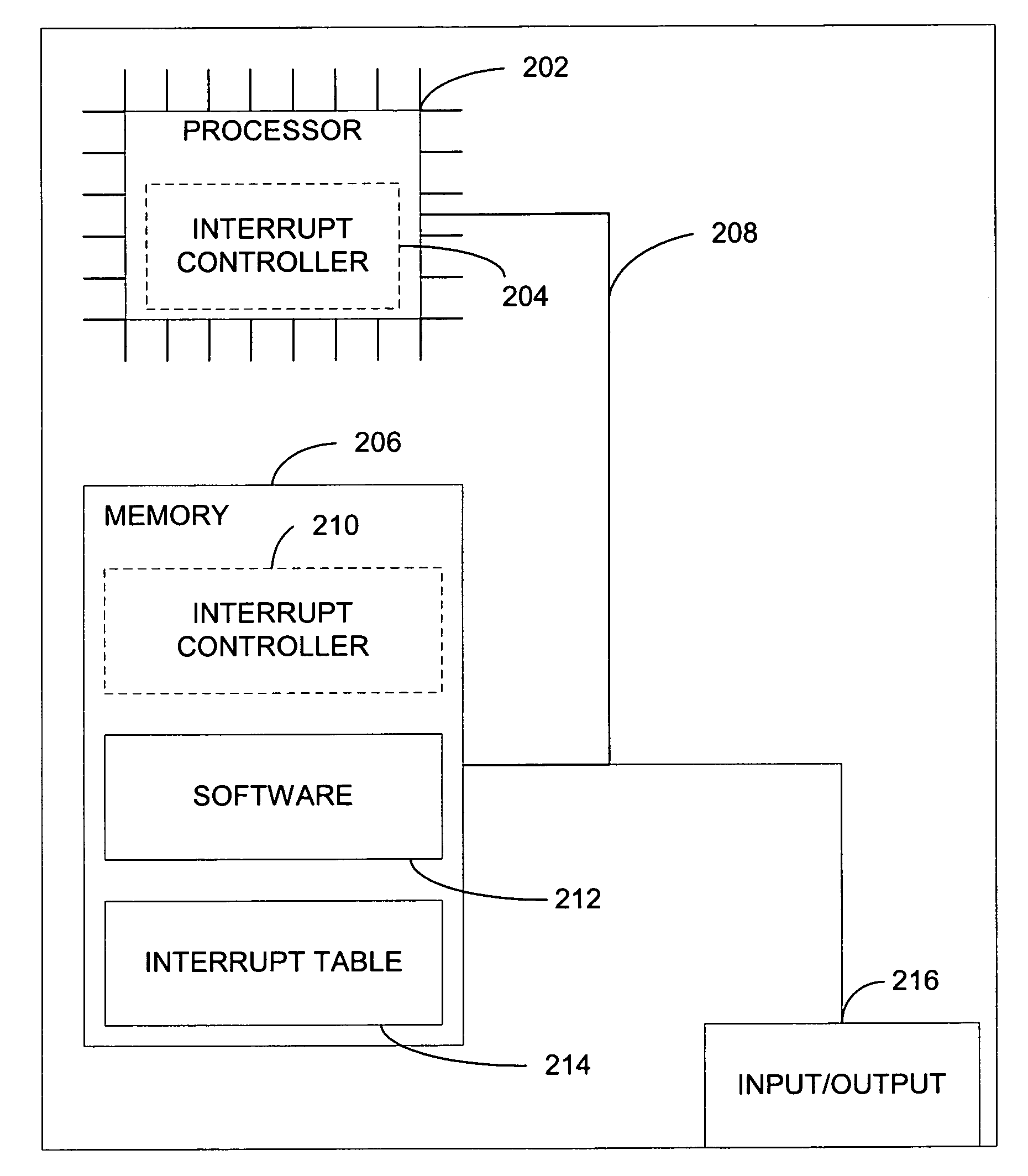

Message based interrupt table

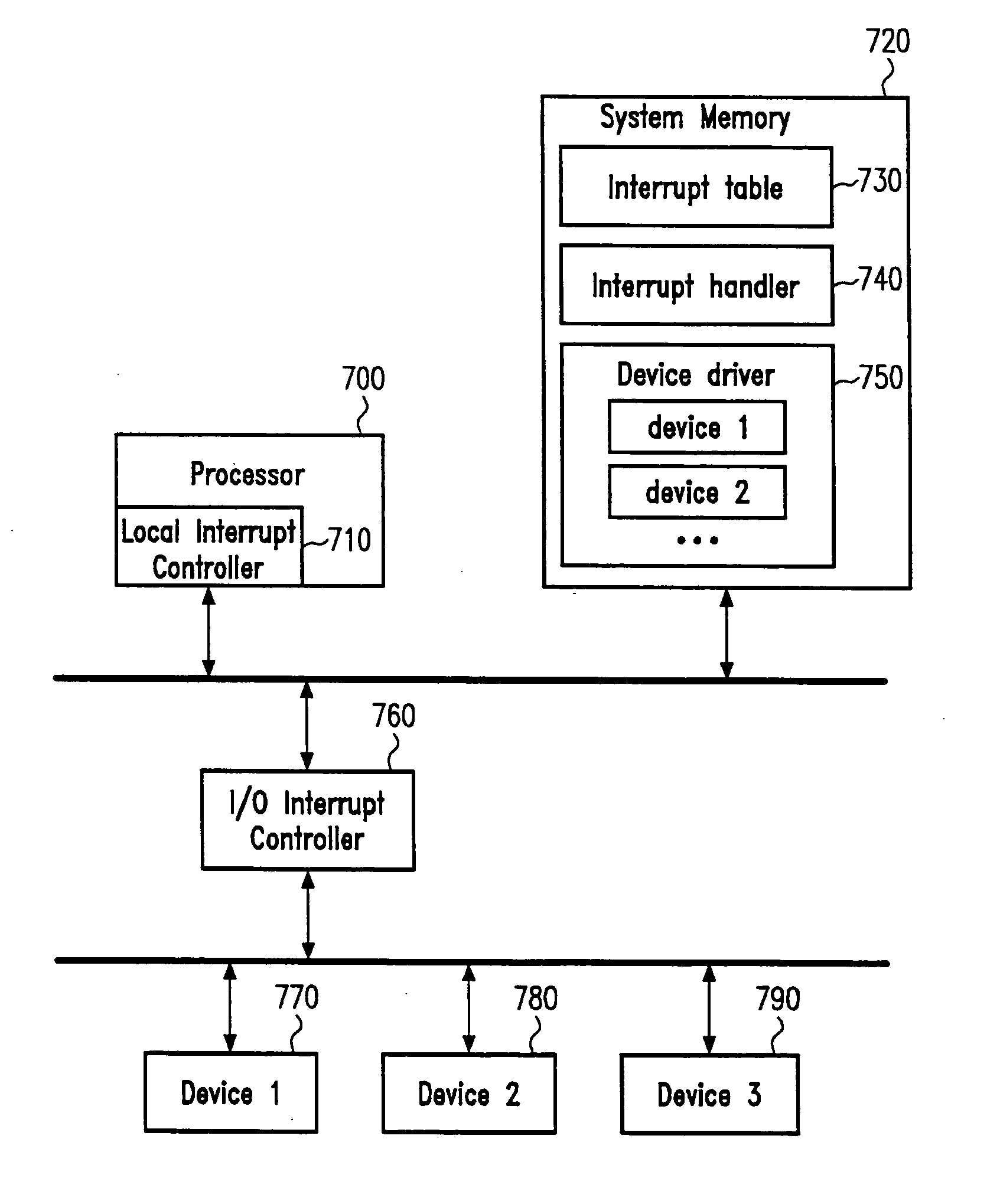

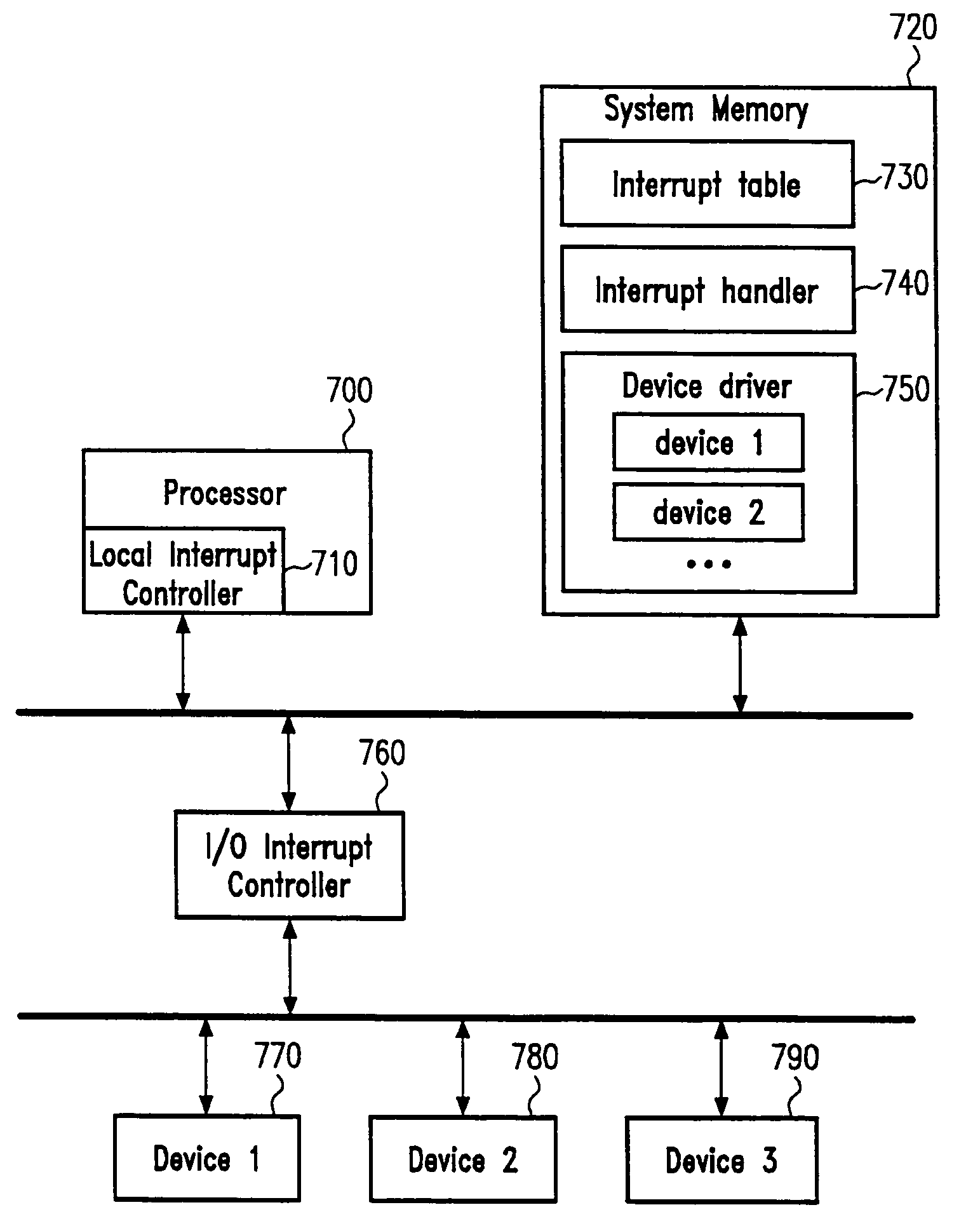

InactiveUS20060047877A1Reduce Interrupt LatencyHigh speedElectric digital data processingMemory addressInterrupt vector table

An interrupt processing technique is provided where an interrupt message is sent to an interrupt controller of a processor in response to an interrupt request from an individual device. The interrupt message comprises a memory address and interrupt status information. The memory address is specifically allocated to the device that has issued the interrupt request. The interrupt status information indicates an interrupt status of the device. An interrupt table that is stored in the memory is updated by the interrupt controller using the interrupt status information comprised in the interrupt message. The interrupt table holds device specific interrupt statuses. Updating the interrupt table comprises addressing the memory using the memory address in the interrupt message.

Owner:GLOBALFOUNDRIES INC

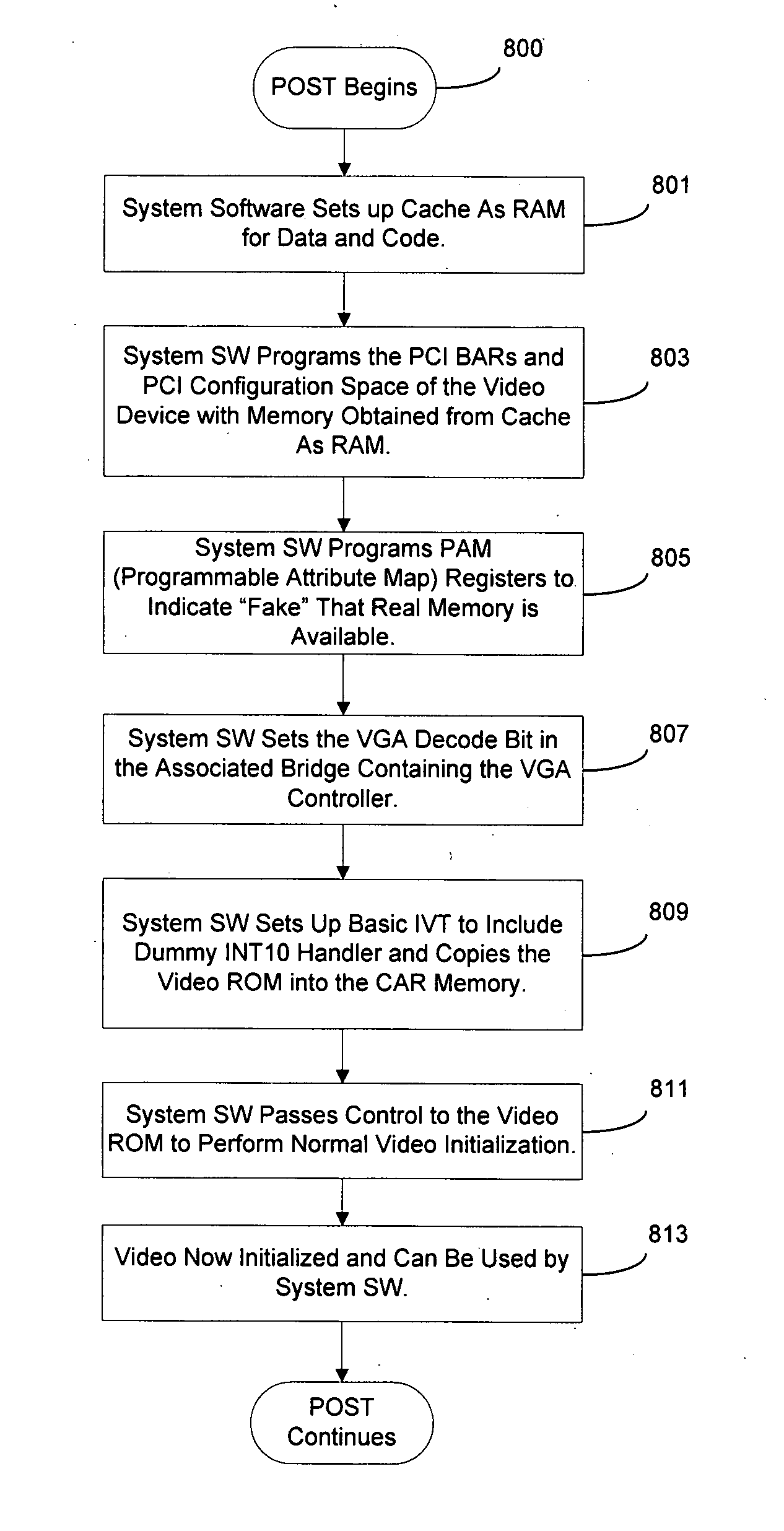

Instant on video

In some embodiments, the invention involves speeding boot up of a platform by initializing the video card early on in the boot process. In an embodiment, processor cache memory is to be used as cache as RAM (CAR). Video graphics adapter (VGA) card initialization uses the CAR instead of system RAM to perform initialization. A portion of the firmware code, interrupt vector tables and handlers are mirrored in the CAR, from flash memory to mimic the behavior of system RAM during the video initialization. VGA initialization may occur before system RAM has initialized to enable early visual feedback to a user. Other embodiments are described and claimed.

Owner:INTEL CORP

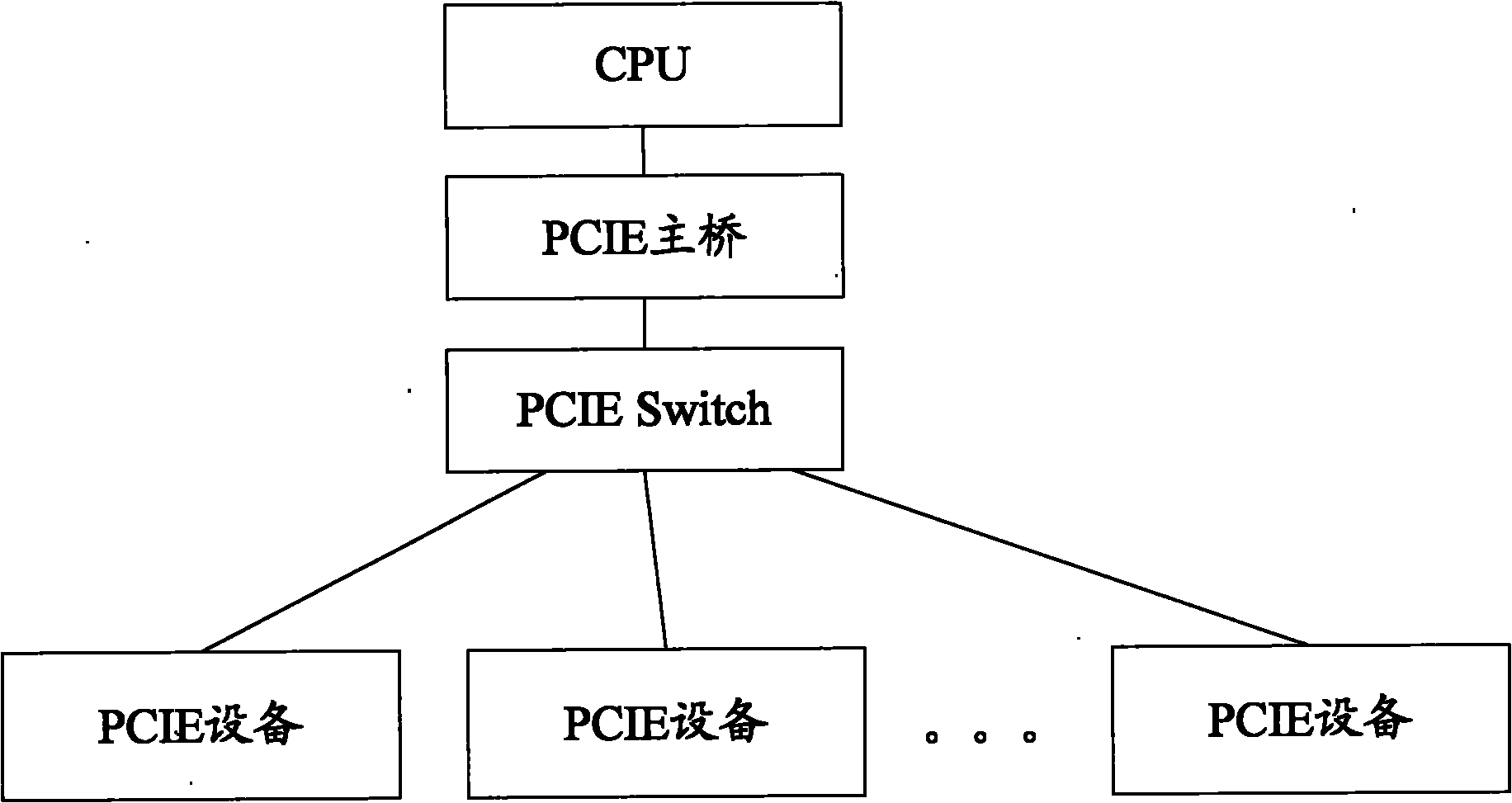

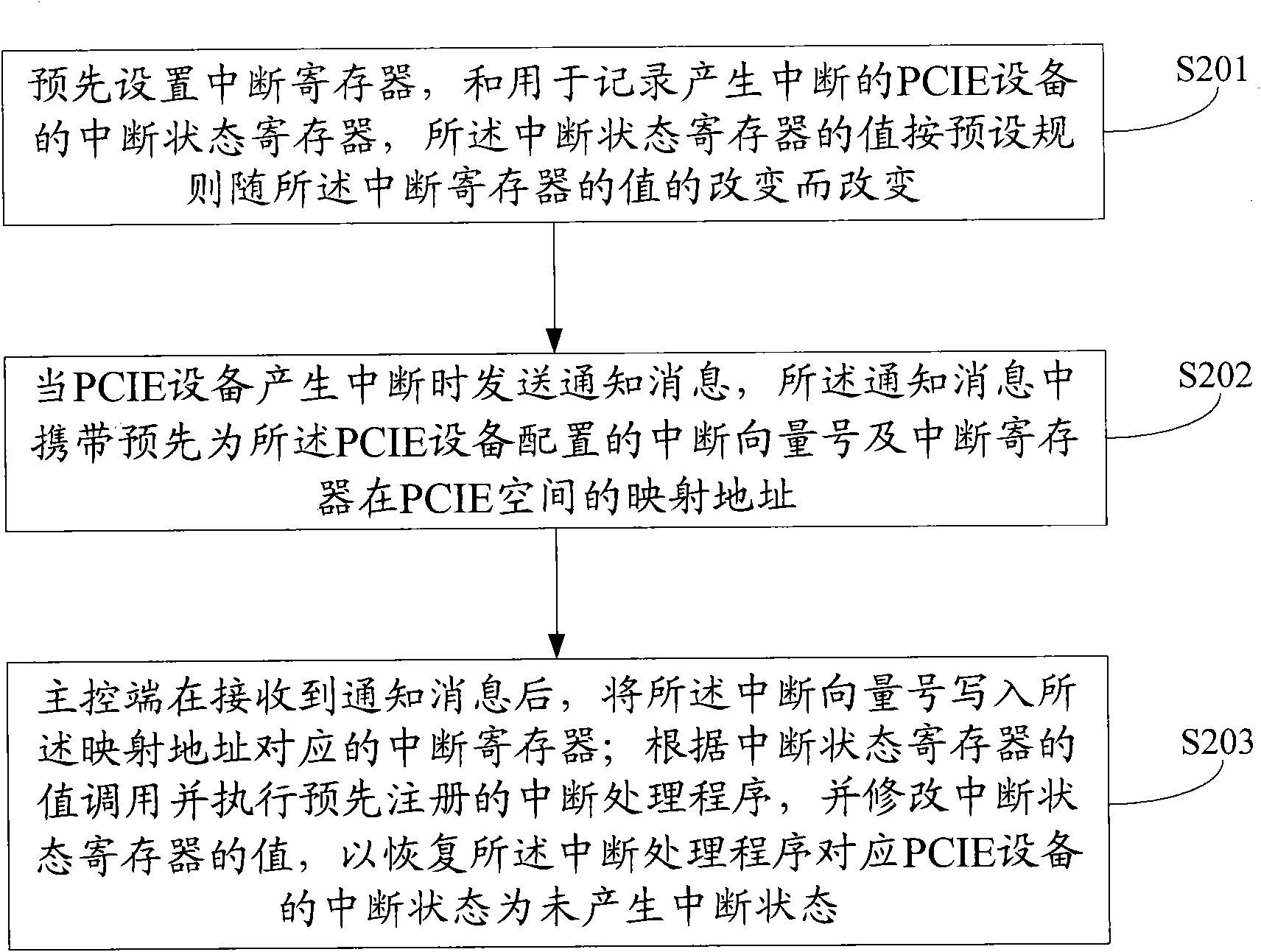

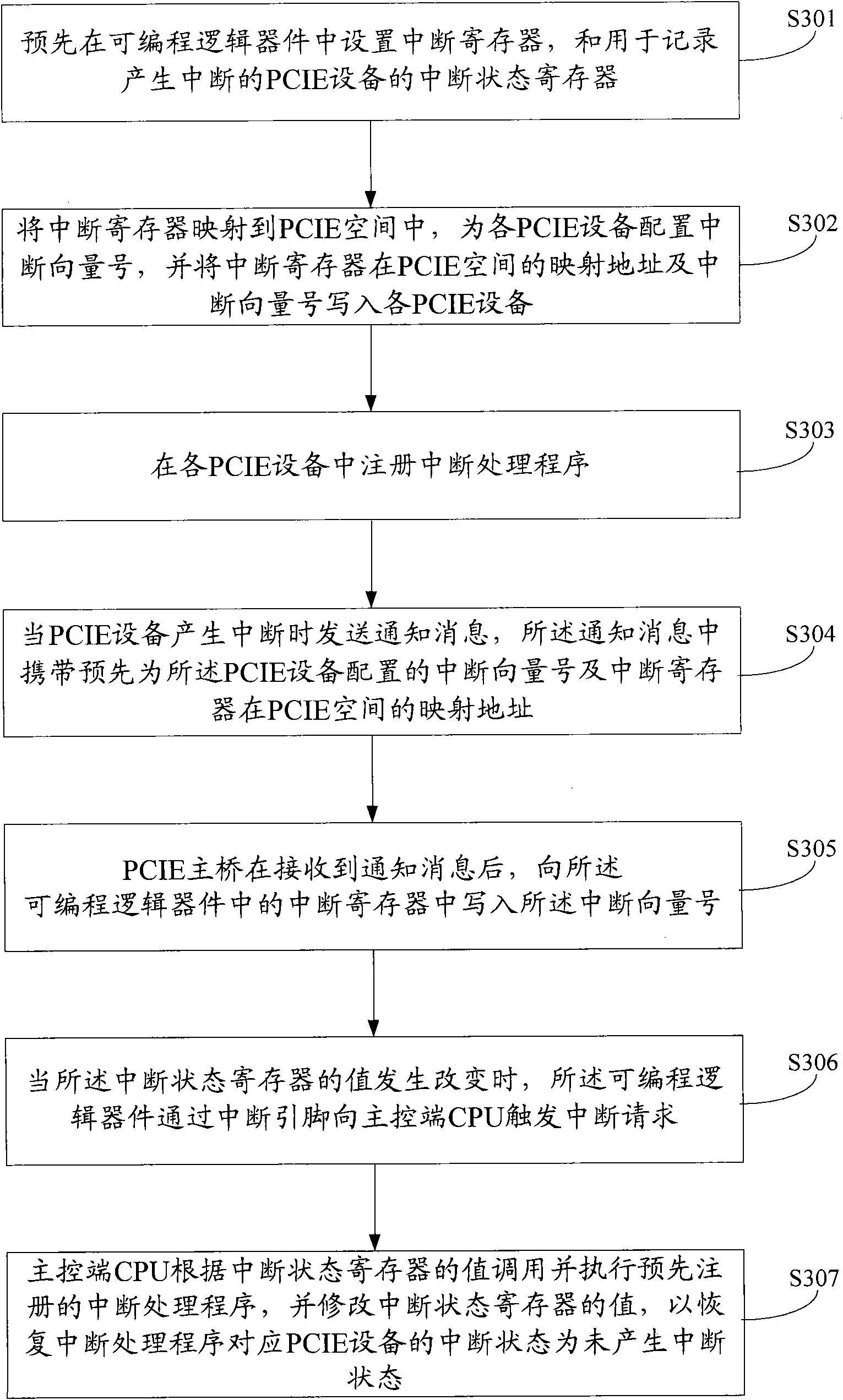

Interrupt processing method of multi-PCIE (Peripheral Component Interface Express) equipment system

ActiveCN101872330AReduce Interrupt LatencyImprove interrupt handling efficiencyElectric digital data processingAutomatic controlMedium scale integration

The invention discloses an interrupt processing method of a multi-PCIE (Peripheral Component Interface Express) equipment system, relating to the field of automatic control. In the invention, an interrupt register and an interrupt state register are arranged in advance, and the value of the interrupt state register changes along with the variation of a value of the interrupt register based on a preset rule; a notification message is sent when PCIE equipment generates interrupt, and an interrupt vector number and an interrupt register address which are configurated to the PCIE equipment in advance are carried in the message; after receiving the notification message, a main control end writes the interrupt vector number into the interrupt register corresponding to a mapping address; and an interrupt processing program which is registered in advance is called and executed based on the value of the interrupt state register, and the value of the interrupt state register is revised to restore an interrupt state of the PCIE equipment corresponding to the interrupt processing program into a non-interrupt state. The invention can process interrupt simultaneously generated by a plurality of PCIE equipments, and PCIE equipment which does not support an MSI (Medium-scale Integration) interrupt mode can apply the invention, therefore, the interrupt processing efficiency of the system is improved.

Owner:HANGZHOU HIKVISION DIGITAL TECH

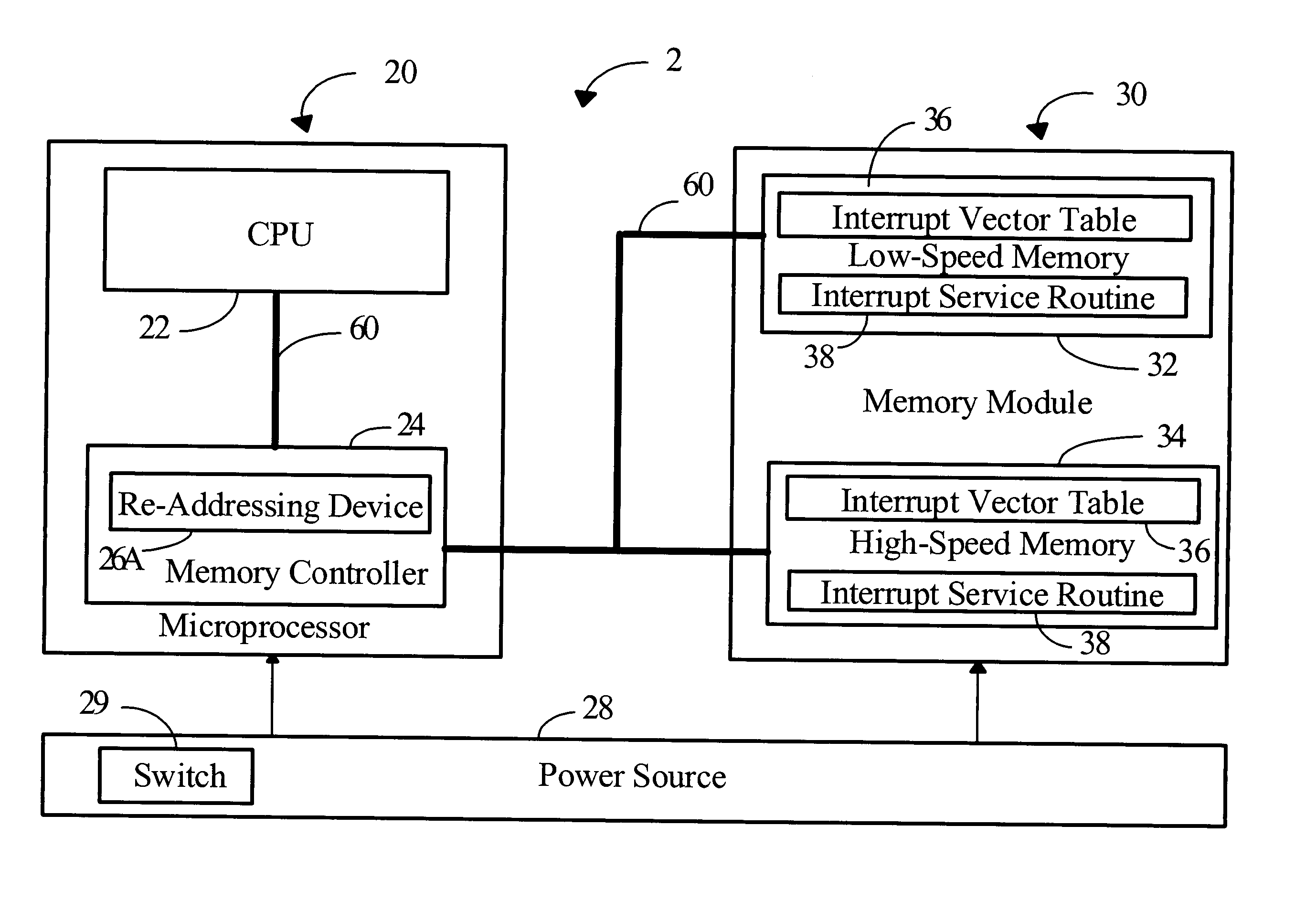

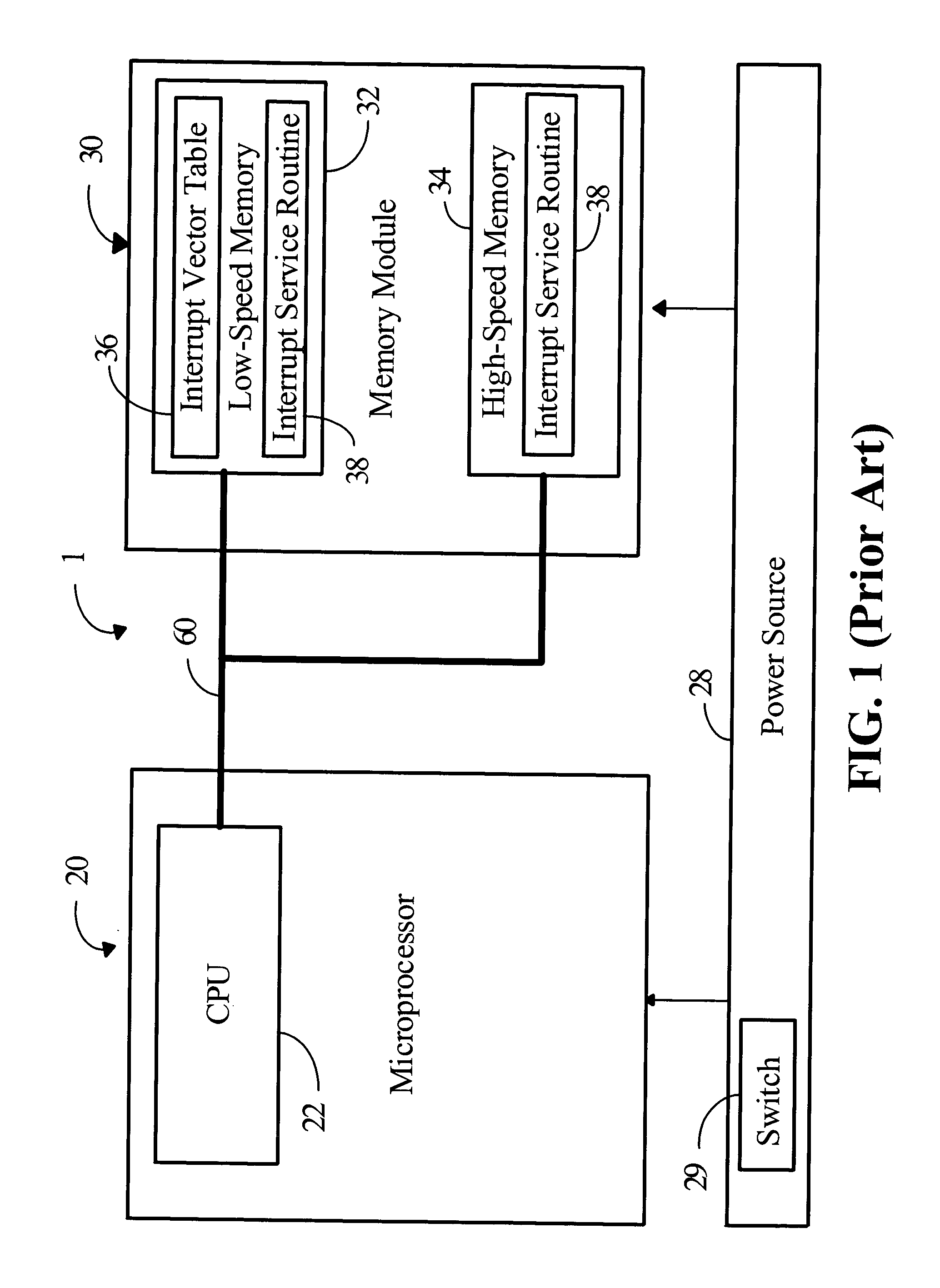

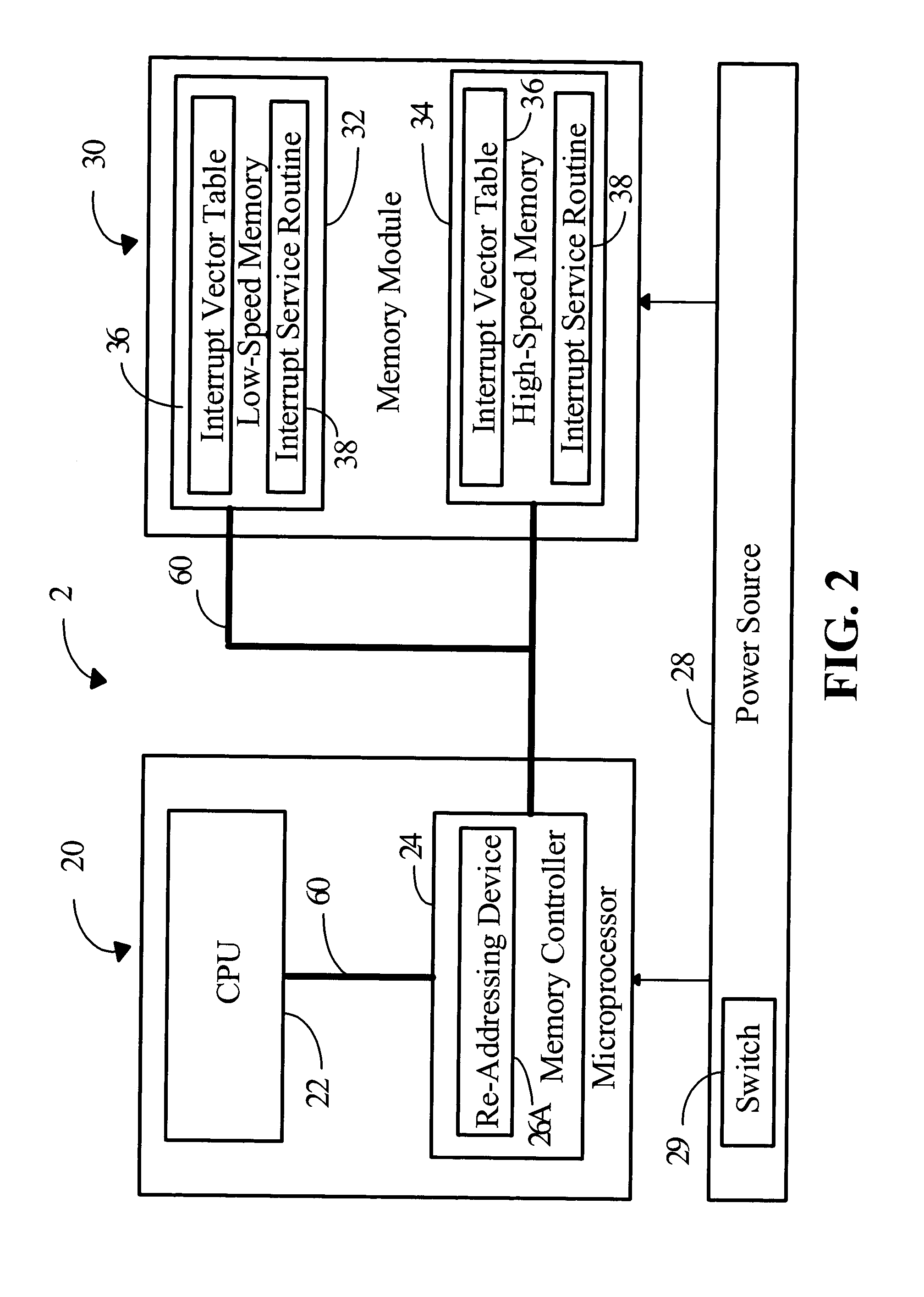

Interrupt-processing system for shortening interrupt latency in microprocessor

ActiveUS20050060461A1Reduce Interrupt LatencyIncrease interrupt service efficiencyMemory systemsMicro-instruction address formationHigh speed memoryLow speed

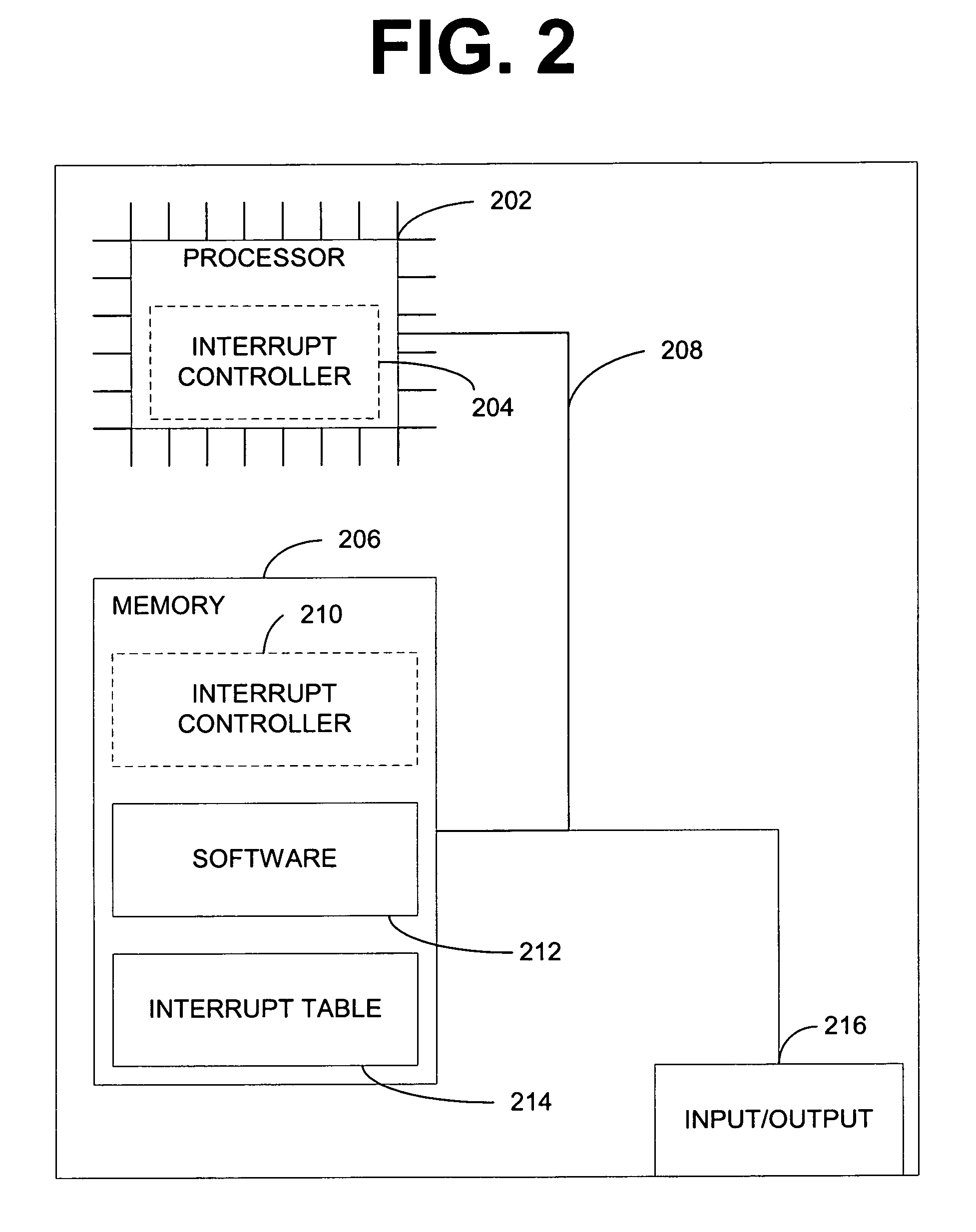

The invention relates to a data processing system which comprises a memory module and a microprocessor. The memory modules comprise at least one low-speed memory and one high-speed memory; both store an interrupt vector table individually for recording the entry instruction of interrupt service routines. The microprocessor comprises a central processing unit (CPU) and a memory controller with a re-addressing device. Once an interruption occurs, the CPU generates and sends an interrupt vector address to the memory controller. If the vector is located in the range of interrupt vector table, the re-addressing device sends an enable signal to the high-speed memory to enable the CPU to fetch the entry instruction of interrupt service routines from the high-speed memory, not from the pre-determined low-speed memory. Hence, the interrupt latency is reduced.

Owner:NOVATEK MICROELECTRONICS CORP

In-application upgrade method for optical module firmware not breaking service

An in-application upgrade method is used for optical module firmware not breaking a service. A storage area for internal programs of an optical module is divided into two areas which are respectively used for storing upgrade and application programs, and is divided into an area for backing up an interrupt vector table of a Boot program. An upper computer is in communication with the optical module. The interrupt vector table is switched, and the jump between the Boot program and the application program is achieved. The method includes extracting the contents of firmware, entering a download mode and updating the firmware. The original firmware is erased, and new firmware is written. An application mode is entered, the upper computer sending an exit command from the download mode. The upgrade program exits and a new application program is executed. The optical module operates normally without interruption.

Owner:WUHAN TELECOMM DEVICES

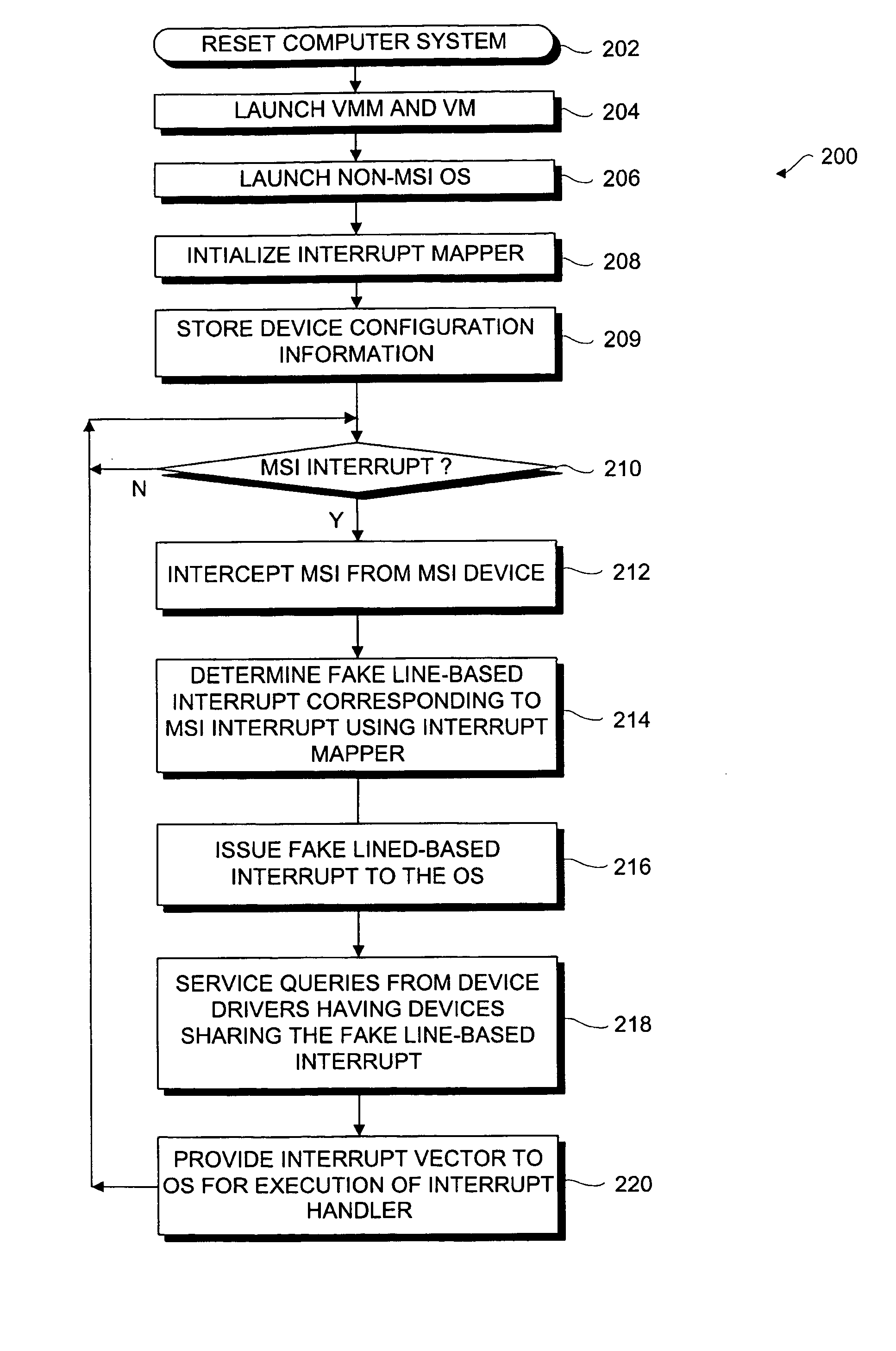

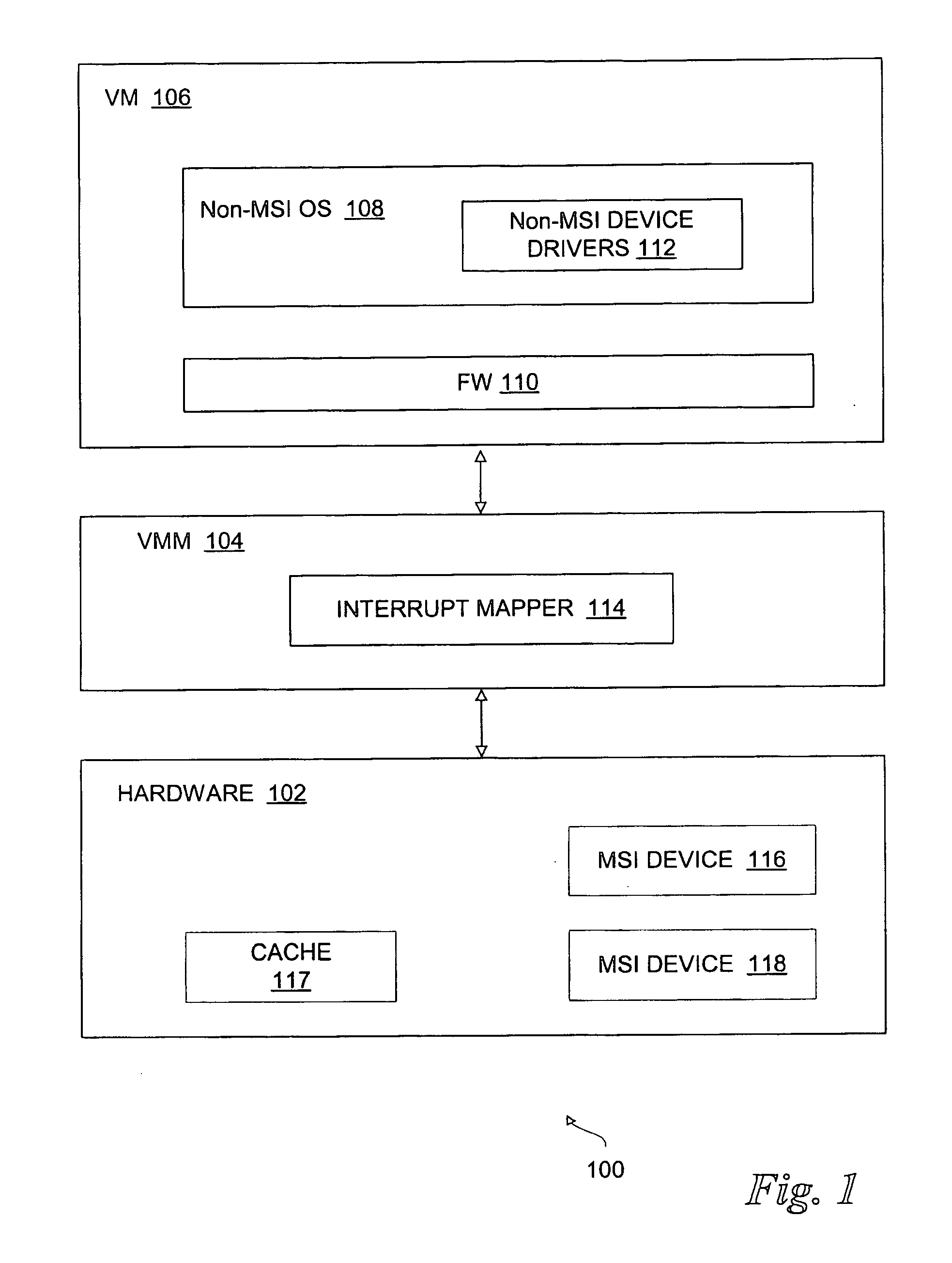

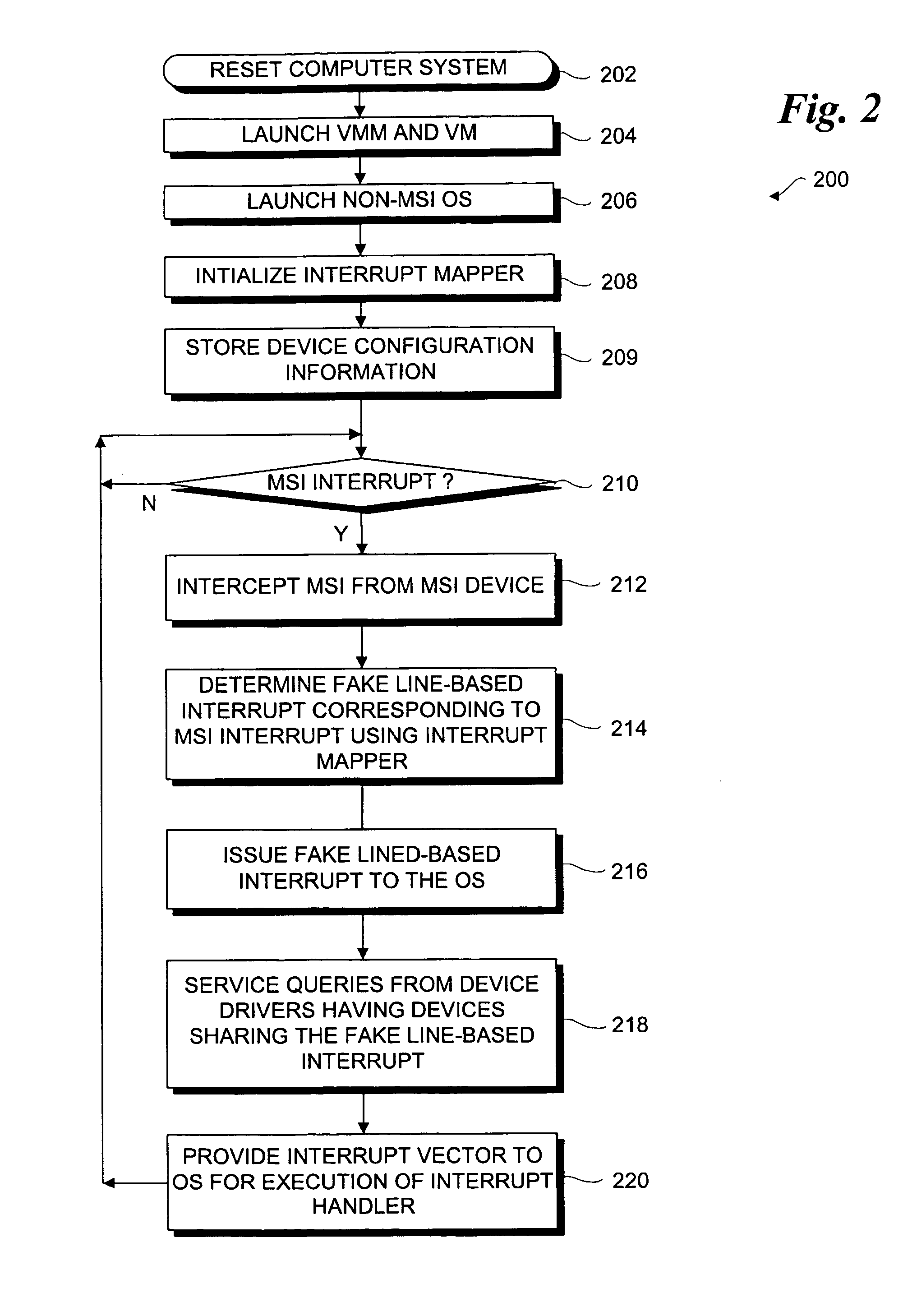

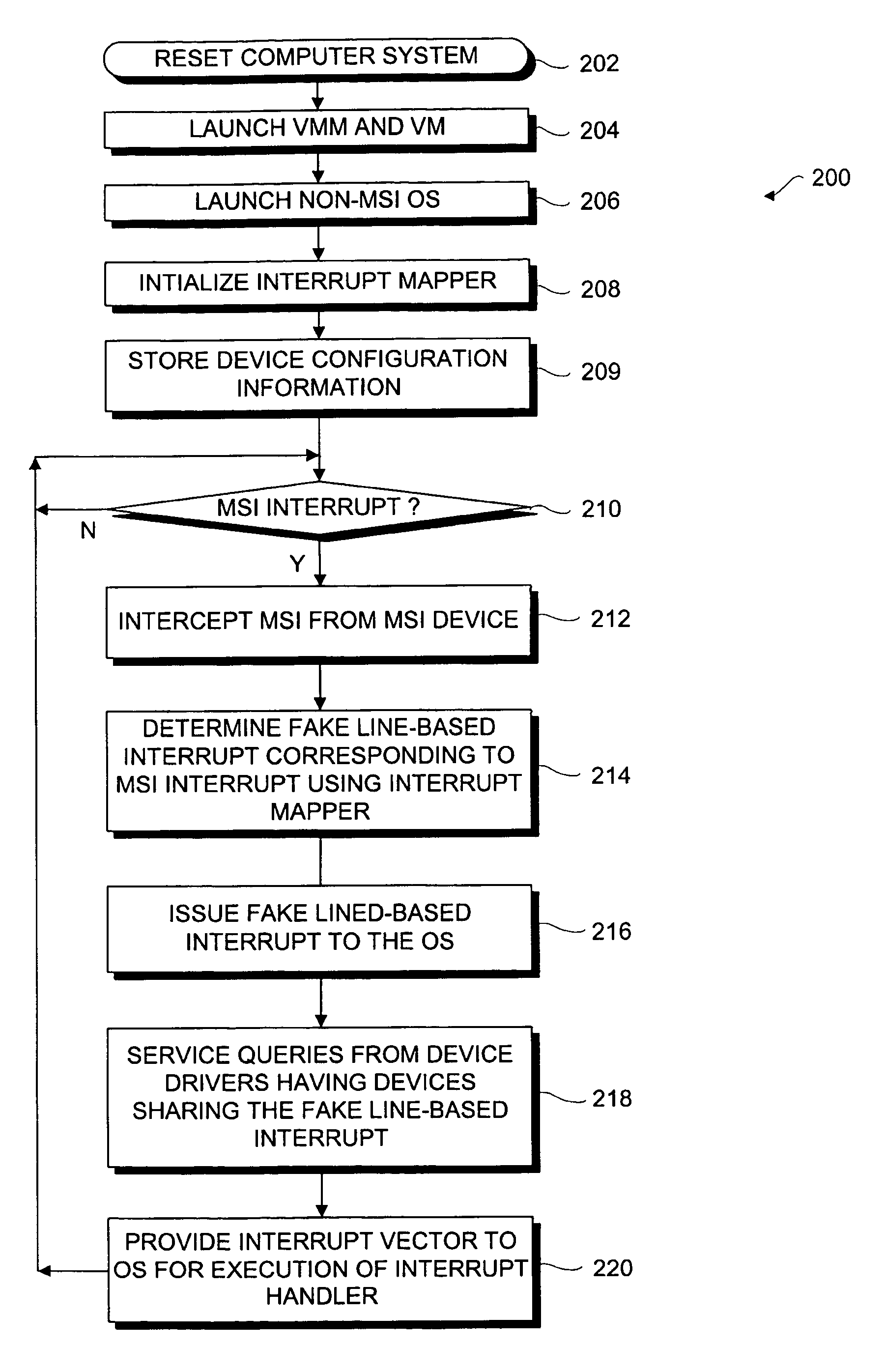

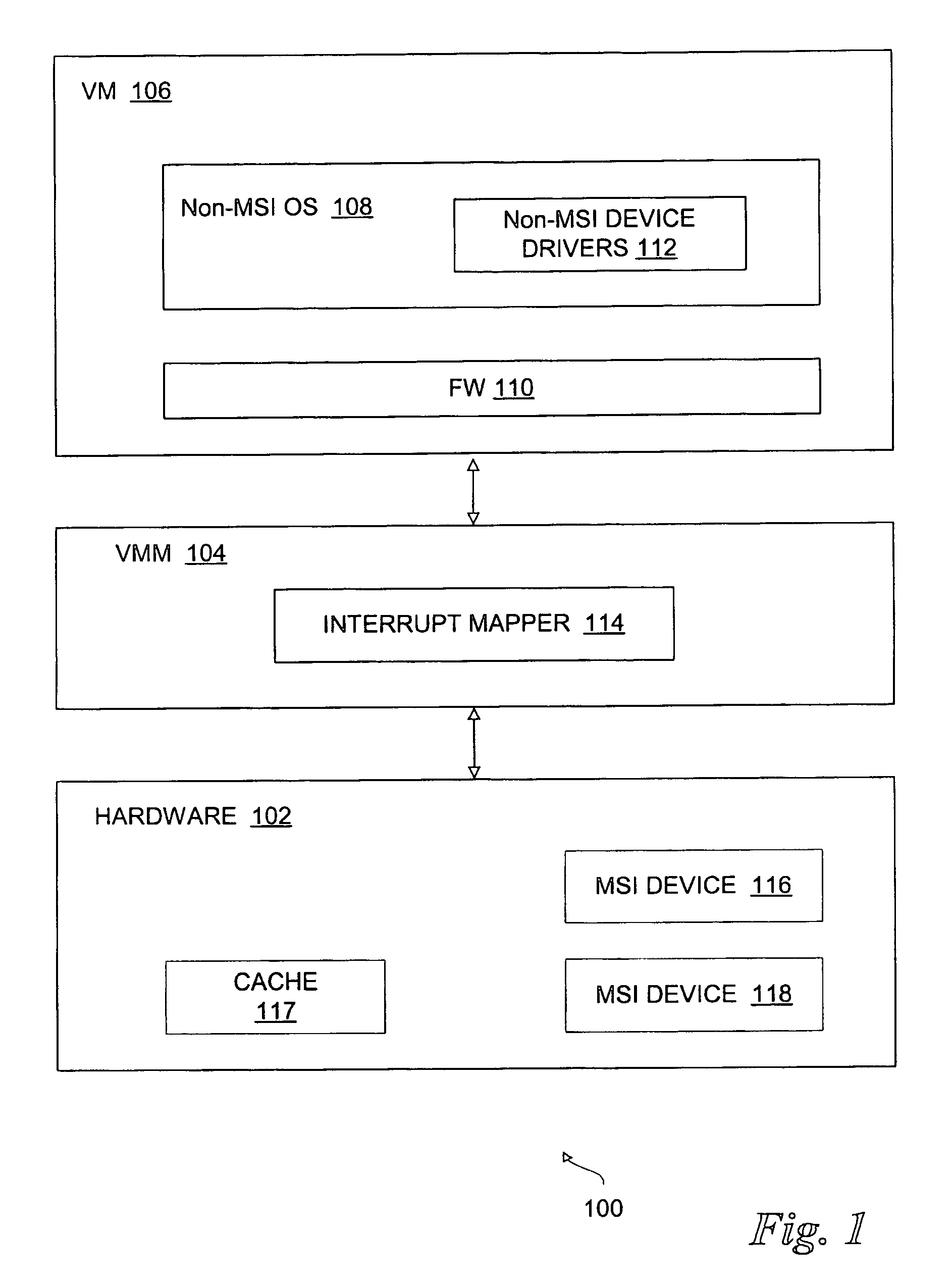

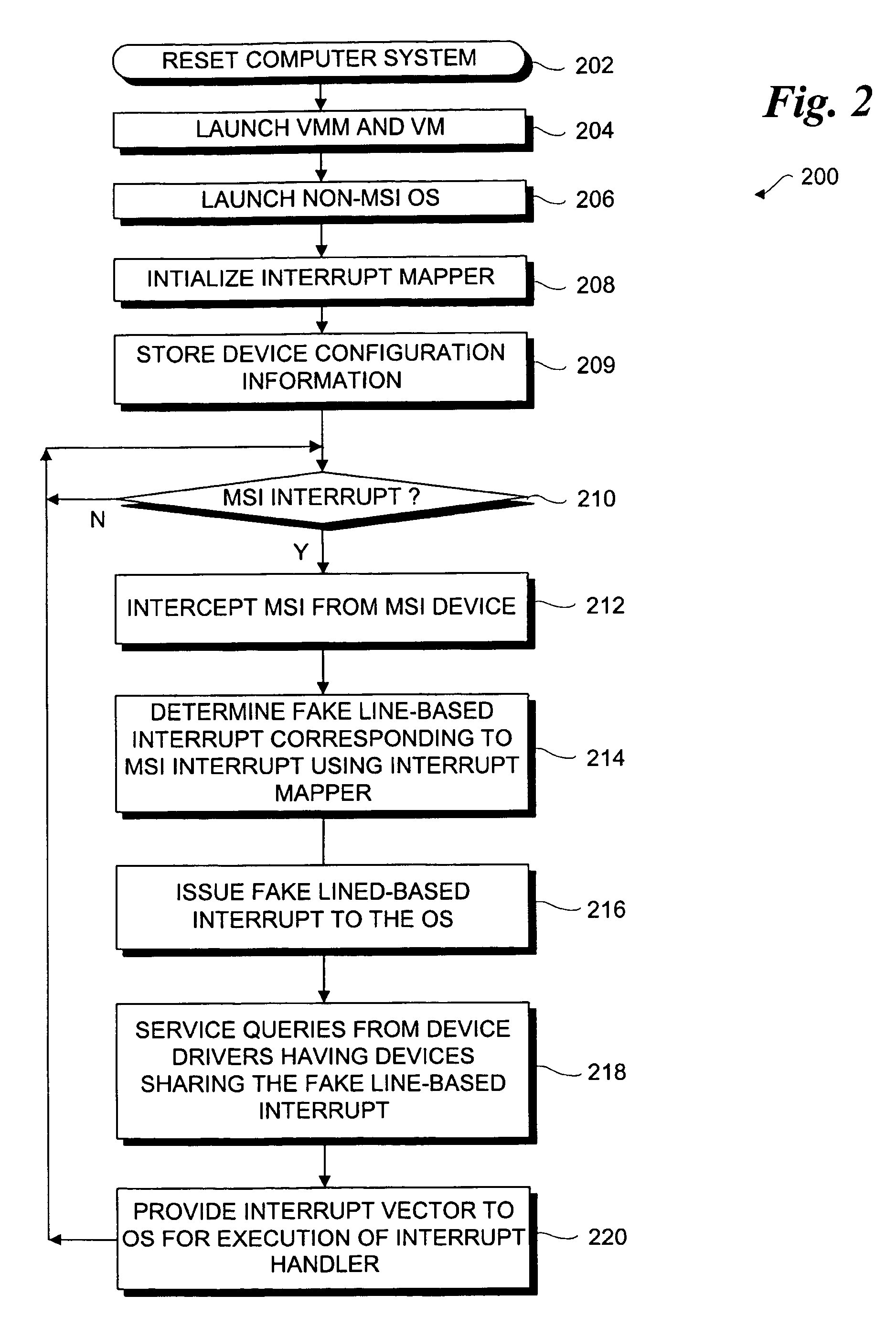

Efficiently supporting interrupts

A method, system, and article of manufacture to efficiently support interrupts of a computer system. A message-based interrupt from a device of the computer system is intercepted. A fake line-based interrupt for the device corresponding to the message-based interrupt is determined, wherein an operating system (OS) of the computer system is not message-based interrupt capable. The fake line-based interrupt is issued to the OS. A query from the OS regarding the fake line-based interrupt is serviced, the query to determine if the fake line-based interrupt was from the device. An interrupt vector associated with the message-based interrupt is provided to the OS.

Owner:INTEL CORP

Techniques for generating microcontroller configuration information

InactiveUS8069428B1Increased complexityImprove usabilityComputer programmed simultaneously with data introductionCAD circuit designMicrocontrollerApplication programming interface

Owner:CYPRESS SEMICON CORP

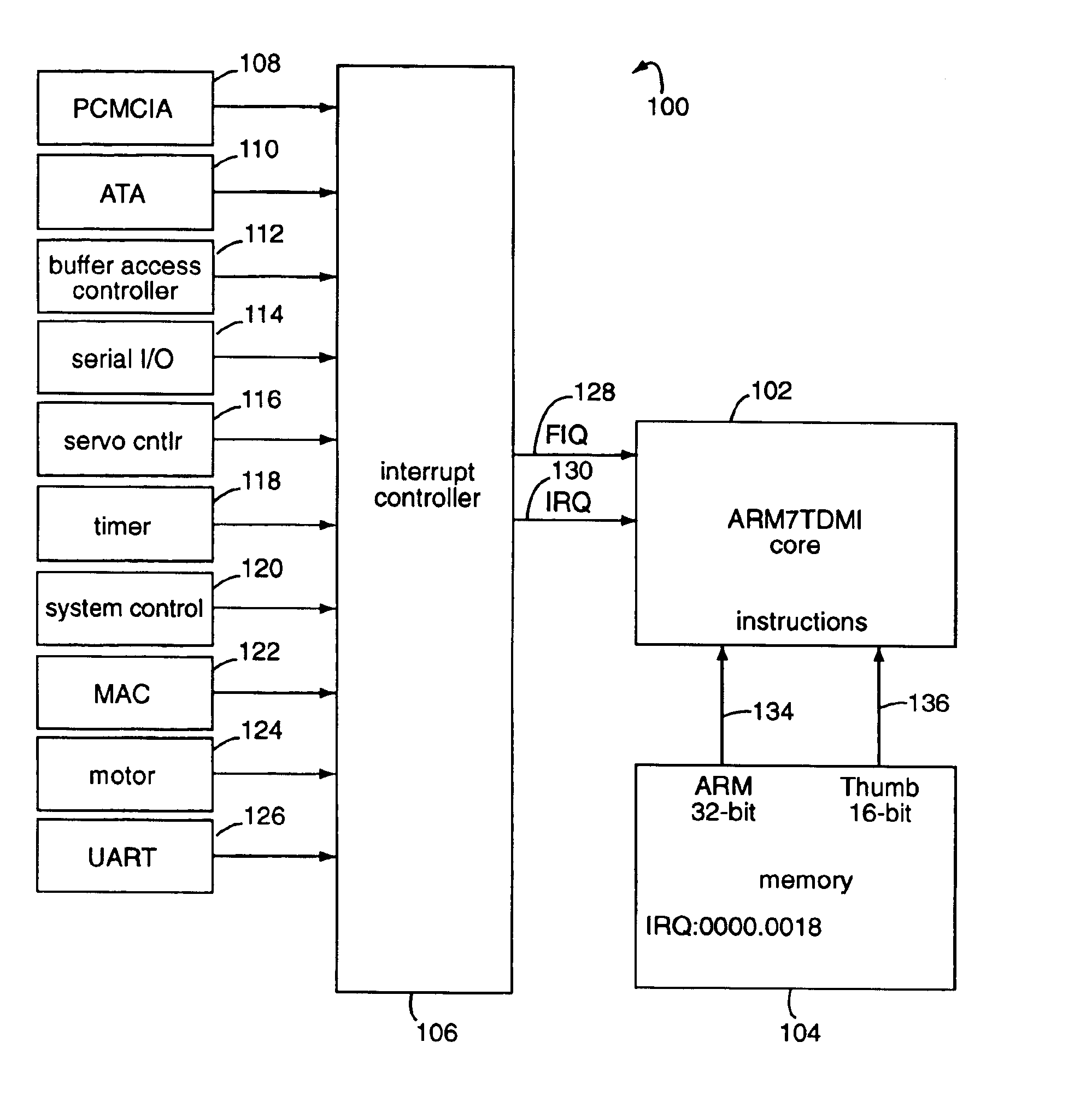

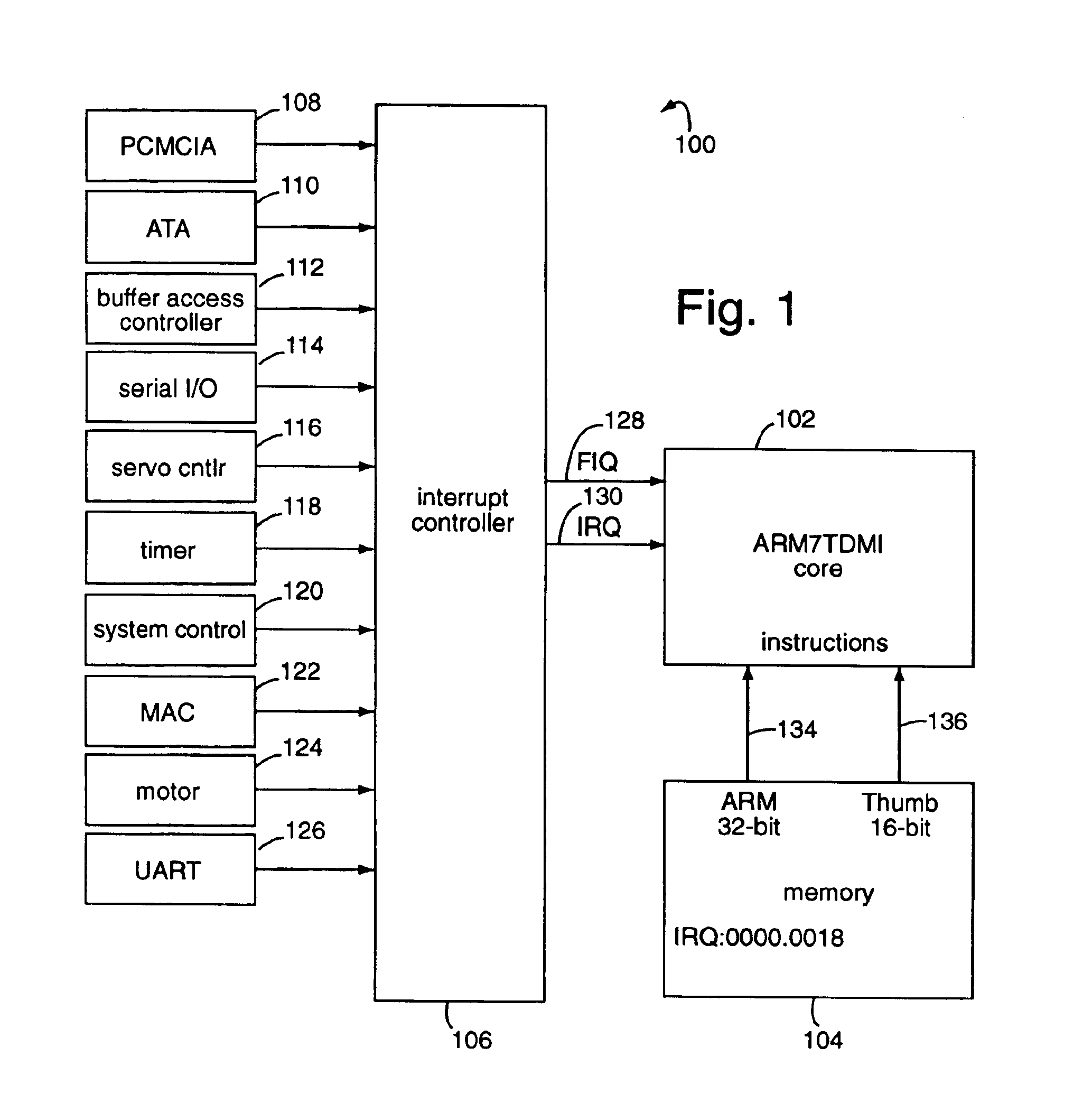

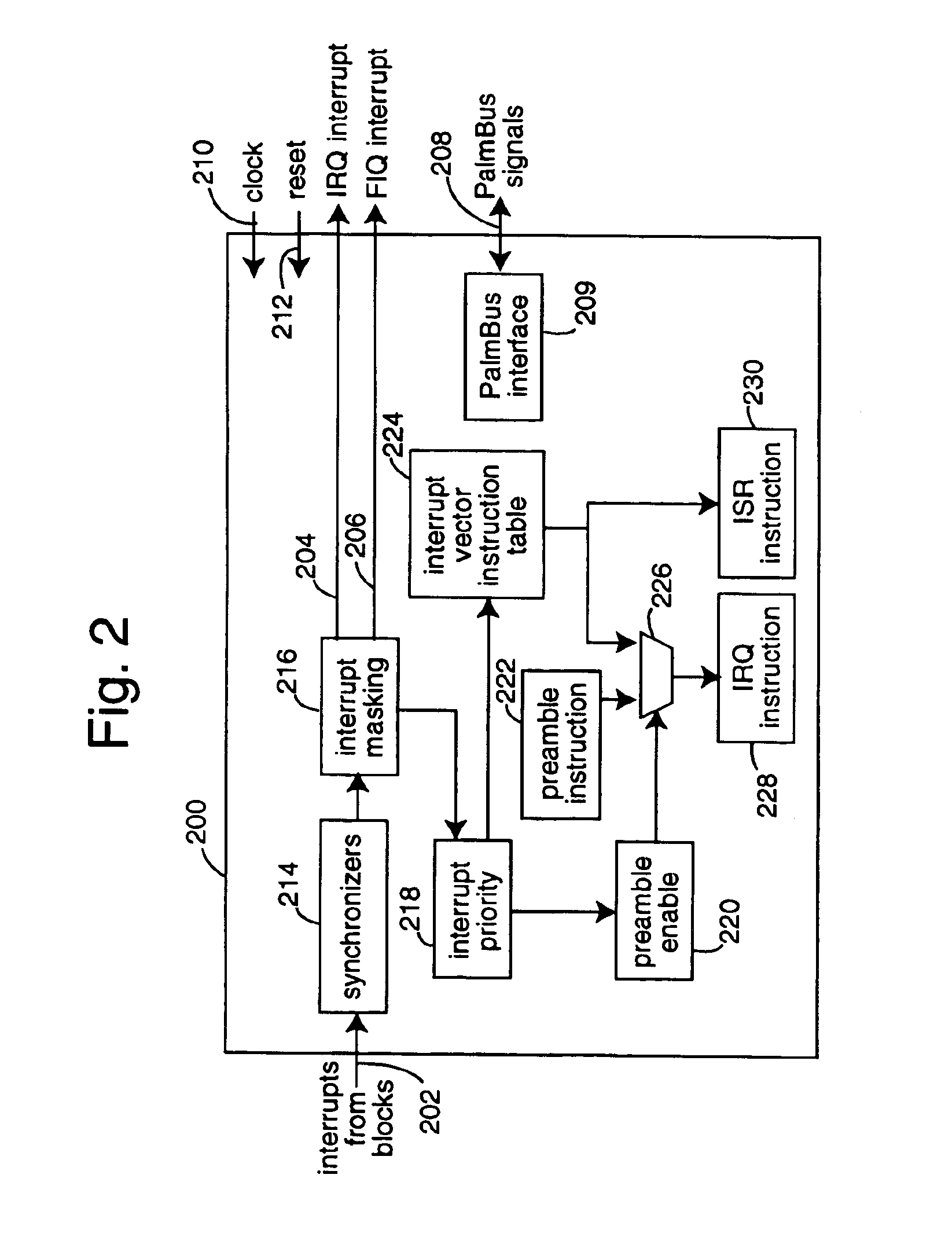

Integrated circuit including interrupt controller with shared preamble execution and global-disable control bit

InactiveUS6917997B2General purpose stored program computerElectric digital data processingMicrocontrollerInterrupt vector table

A interrupt controller includes specialized interfaces and controls for ARM7TDMI-type microcontroller cores. Such sends interrupt vectors and IRQ or FIQ interrupt requests to the processor depending on particular interrupts received. Wherein, THUMB program execution is more economical with program code space, and an interrupt service routine preamble is coded in ARM program code to cause a switch to THUMB program execution. The interrupt service routine preamble is shared amongst all the interrupt service routines to further economize on program code space.

Owner:NETVINCI

Message based interrupt table

InactiveUS7257658B2Reduce Interrupt LatencyHigh speedElectric digital data processingMemory addressInterrupt vector table

An interrupt processing technique is provided where an interrupt message is sent to an interrupt controller of a processor in response to an interrupt request from an individual device. The interrupt message comprises a memory address and interrupt status information. The memory address is specifically allocated to the device that has issued the interrupt request. The interrupt status information indicates an interrupt status of the device. An interrupt table that is stored in the memory is updated by the interrupt controller using the interrupt status information comprised in the interrupt message. The interrupt table holds device specific interrupt statuses. Updating the interrupt table comprises addressing the memory using the memory address in the interrupt message.

Owner:GLOBALFOUNDRIES INC

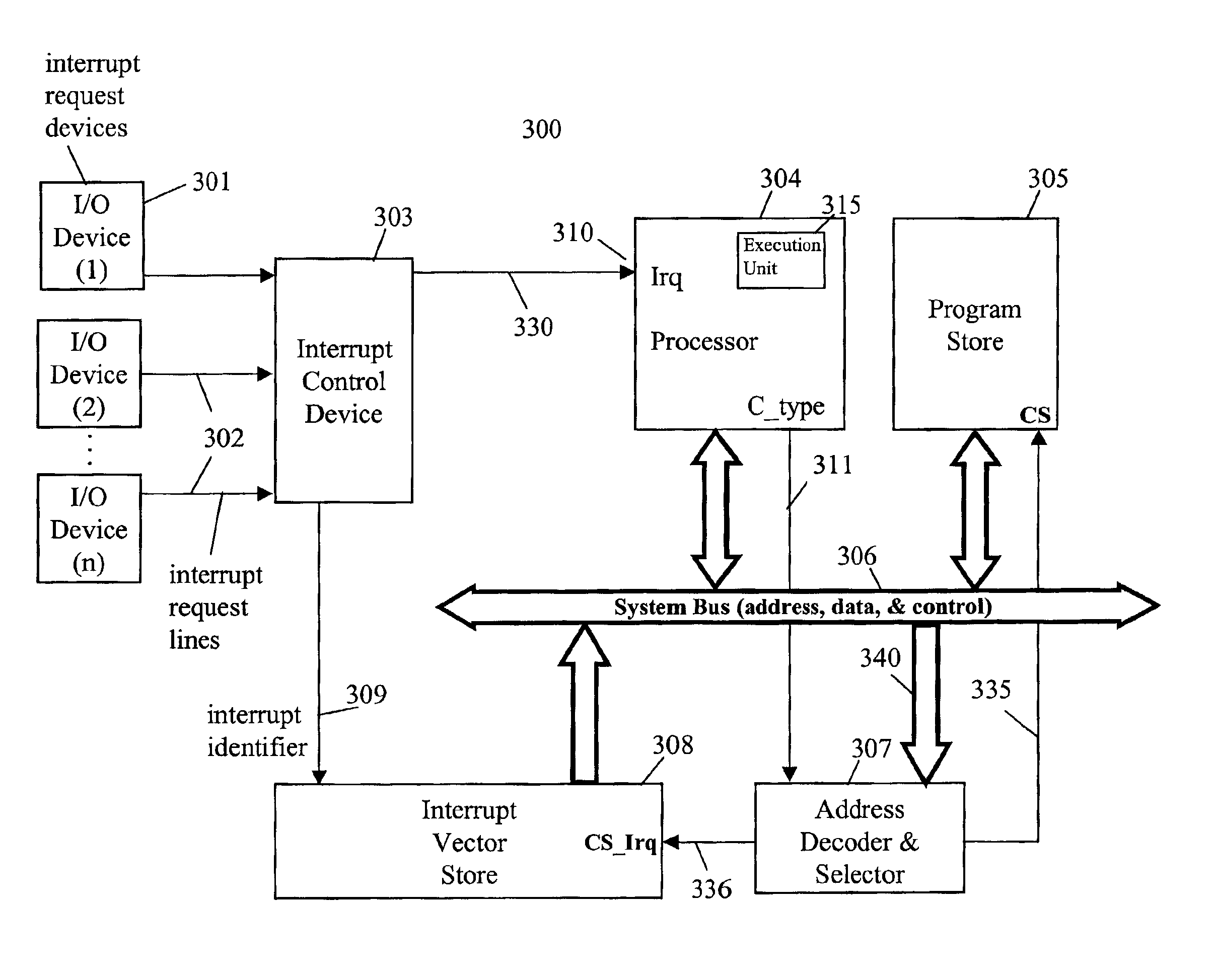

Pre-stored vector interrupt handling system and method

InactiveUS6889279B2Reduced interrupt-processing latencySave overheadProgram initiation/switchingNext instruction address formationChip selectInstruction cycle

A pre-stored vector interrupt handling system for rapidly processing interrupt requests from input / output (I / O) devices in processor-based systems includes selection logic and an interrupt vector store to quickly deliver a branch instruction from the interrupt vector store directly to the execution unit of a processor. The interrupt vector store is either pre-loaded with a table of the processor's branch instructions during system initialization or implemented in ROM. During normal operation, when an interrupt is received, a master interrupt signal is issued to the processor, which asserts an instruction cycle mode signal to external chip select logic. The chip select logic deselects the program store and selects the interrupt vector store. An interrupt vector from the vector store is loaded onto the data bus and then directly into the execution unit of the processor.

Owner:CADENCE DESIGN SYST INC

Multi-task master control system for remote sensing satellite image processing load

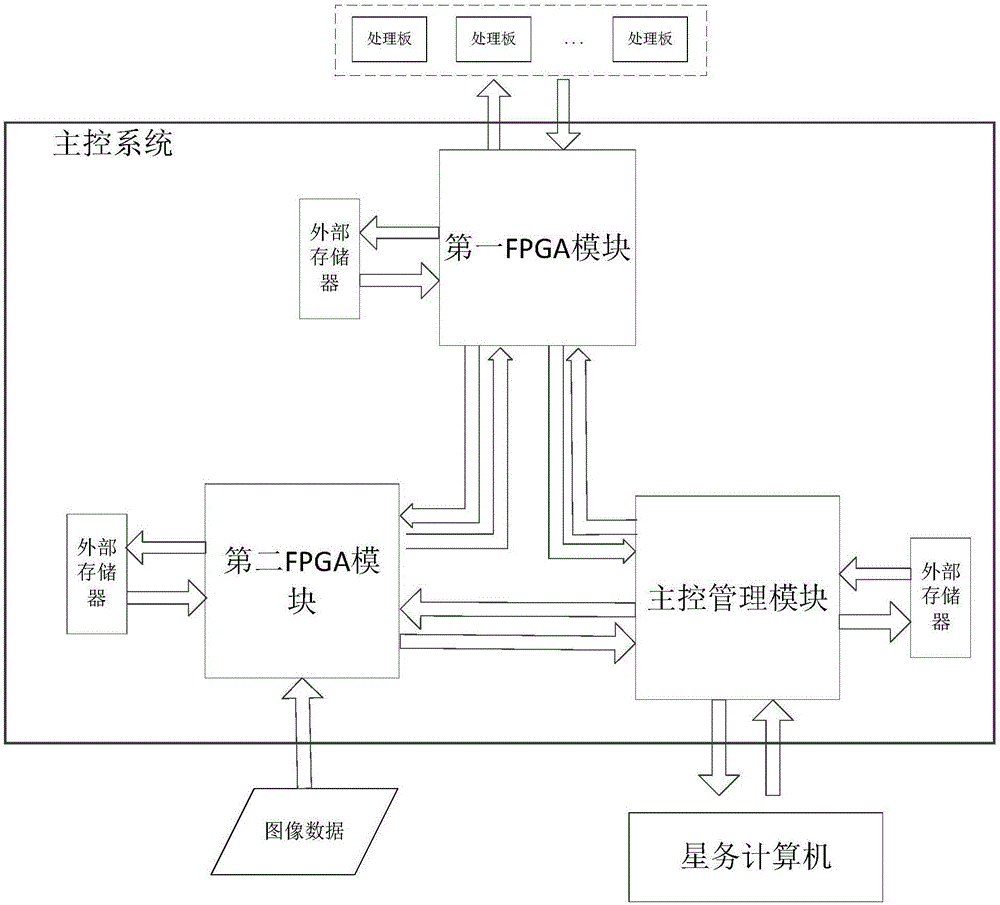

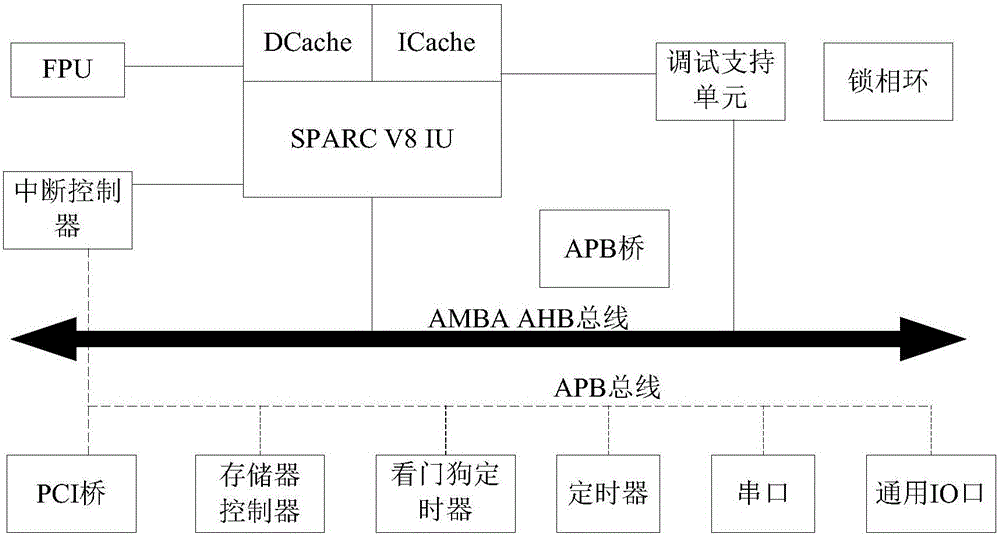

ActiveCN106843038ARealize monitoringRealize managementProgramme controlImage analysisSatellite image processingStructure of Management Information

The invention discloses a multi-task master control system for a remote sensing satellite image processing load. A CPU+2FPGA framework is adopted, wherein an embedded real-time operating system is transplanted into a CPU to serve as a master control management module for completing state monitoring and task scheduling of the remote sensing satellite image processing load, which has high flexibility, safety and stability; an FPGA can overcome the defects of the CPU with different interrupt priority levels and limited interrupt vector tables under multiple time sequence interfaces when used for integrating and issuing communication information, and can meet the requirements for real-time performance and low delay under a large data size when used for preprocessing images. The system structure design can effectively achieve the master control management function, meet the requirements for highly parallel processing of images and operation of complex floating-point numbers, and meet the requirements for safety, reliability and high flexibility of the system.

Owner:HUAZHONG UNIV OF SCI & TECH

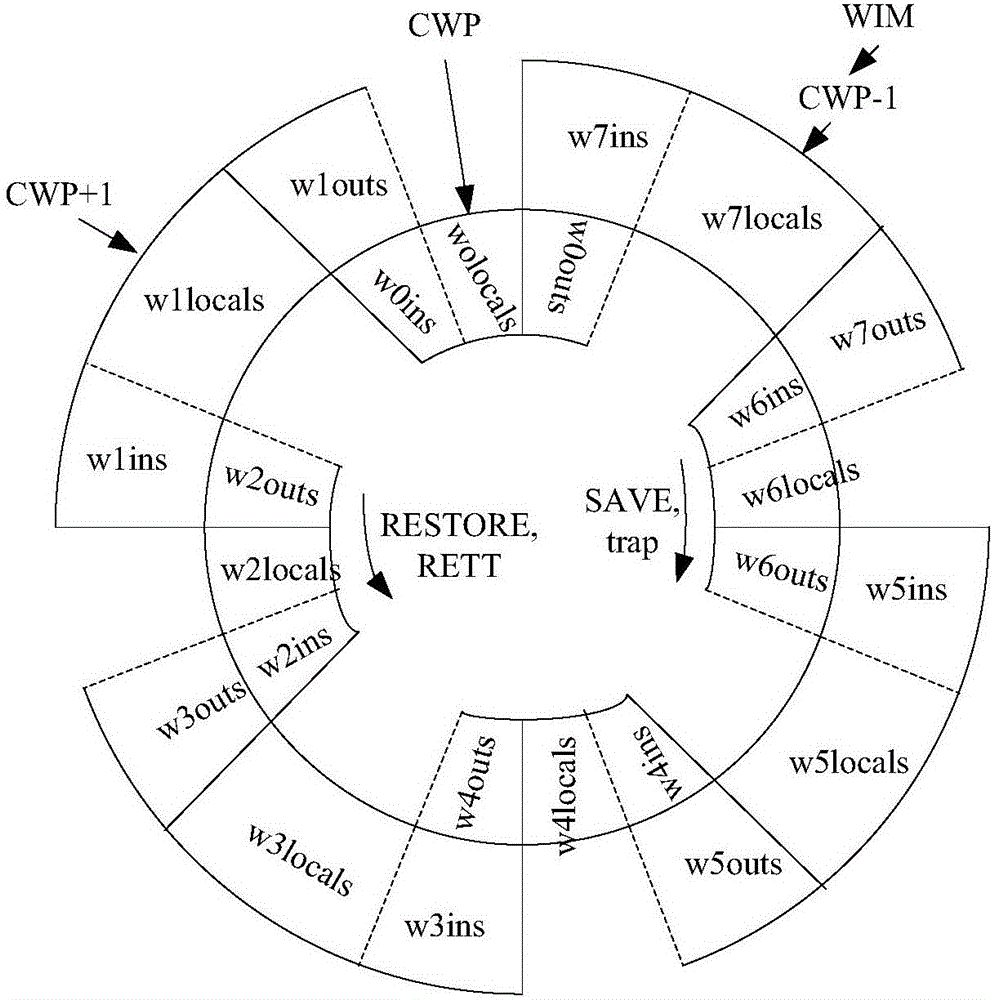

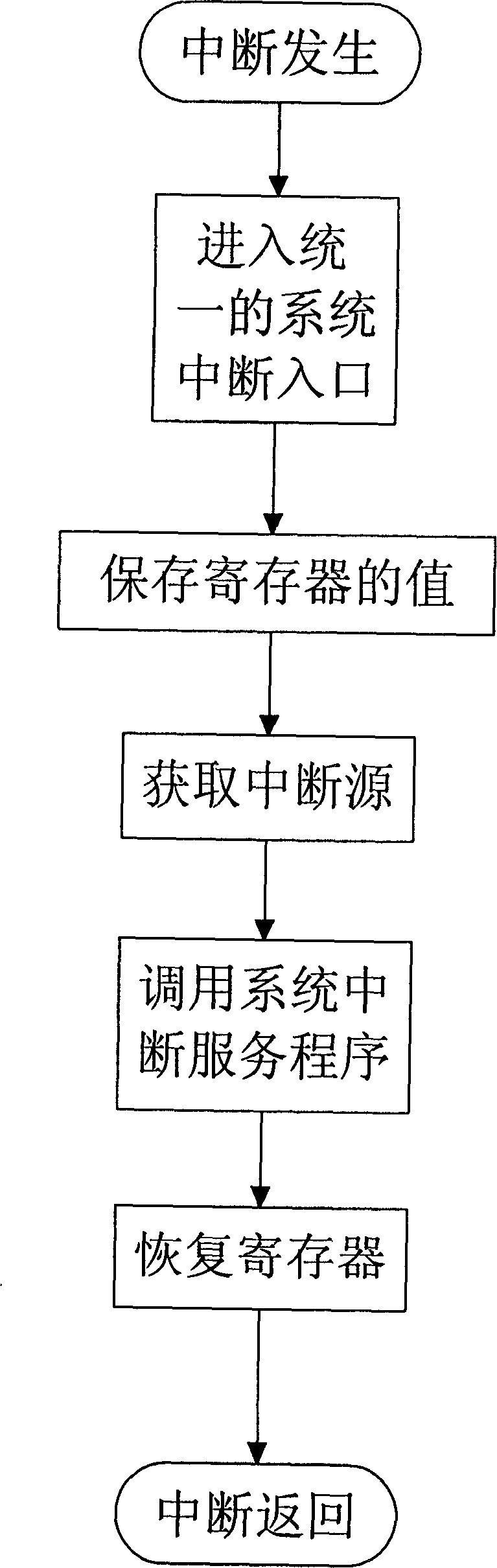

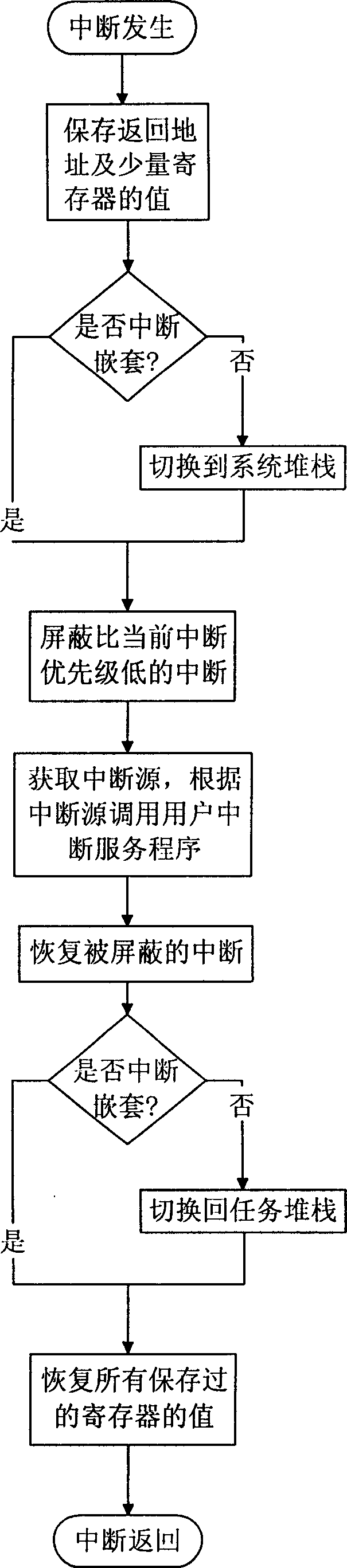

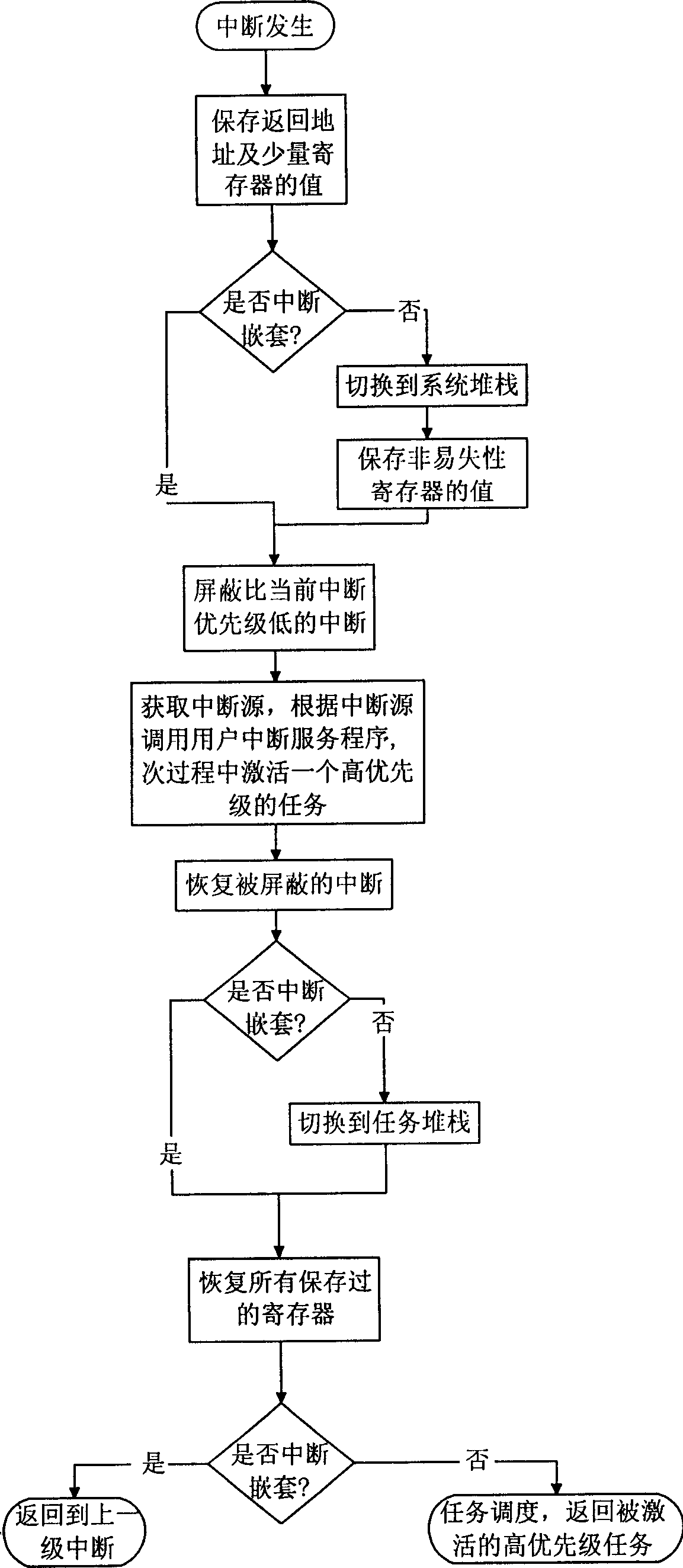

Interrupt managing method for embedded operation system based on PowerPC system structure

InactiveCN1783020APrevent executionImprove execution efficiencyProgram initiation/switchingOperational systemPowerPC

The interrupt management method for embedded operation system based on PowerPC system structure includes the following steps: dividing interrupts into two classes of system interrupt and user interrupt and dividing user interrupt service programs into class-I interrupt service program and class-II interrupt service program; first hardware responding the user interrupt; then, maintaining the context, stack switching and interrupt nesting for resuming the interrupted task after interrupt treatment; finding out and calling corresponding interrupt service program from the user interrupt vector list via the interrupt source; and maintaining the interrupt nesting and stack switching, restoring the context for the treater to resume the interrupted task. The present invention has the advantages of raised interrupt executing efficiency, raised interrupt utilizing efficiency, convenient interrupt control and use, raised user stack size controllability and predicting property.

Owner:ZHEJIANG UNIV

Retargeting of platform interrupts

Systems, methods, and apparatus to retarget platform interrupts in a reconfigurable system. Some embodiments include identifying each processor of a multiprocessor system capable of processing Corrected Platform Error Interrupts, adding each processor capable of processing Corrected Platform Error Interrupts to a list of potential Corrected Platform Error Interrupt targets, and updating an interrupt table with a target processor for an interrupt, wherein the interrupt table is accessible by an interrupt controller to target platform interrupts. Another embodiment includes receiving a request to disable the first processor in a multiprocessor apparatus, determining if the first processor is a Corrected Platform Error Interrupt destination, and determining if the second processor is capable of processing Corrected Platform Error Interrupts. This embodiment also includes reprogramming an interrupt controller to route interrupts to the second processor instead of the first processor and disabling the first processor.

Owner:INTEL CORP

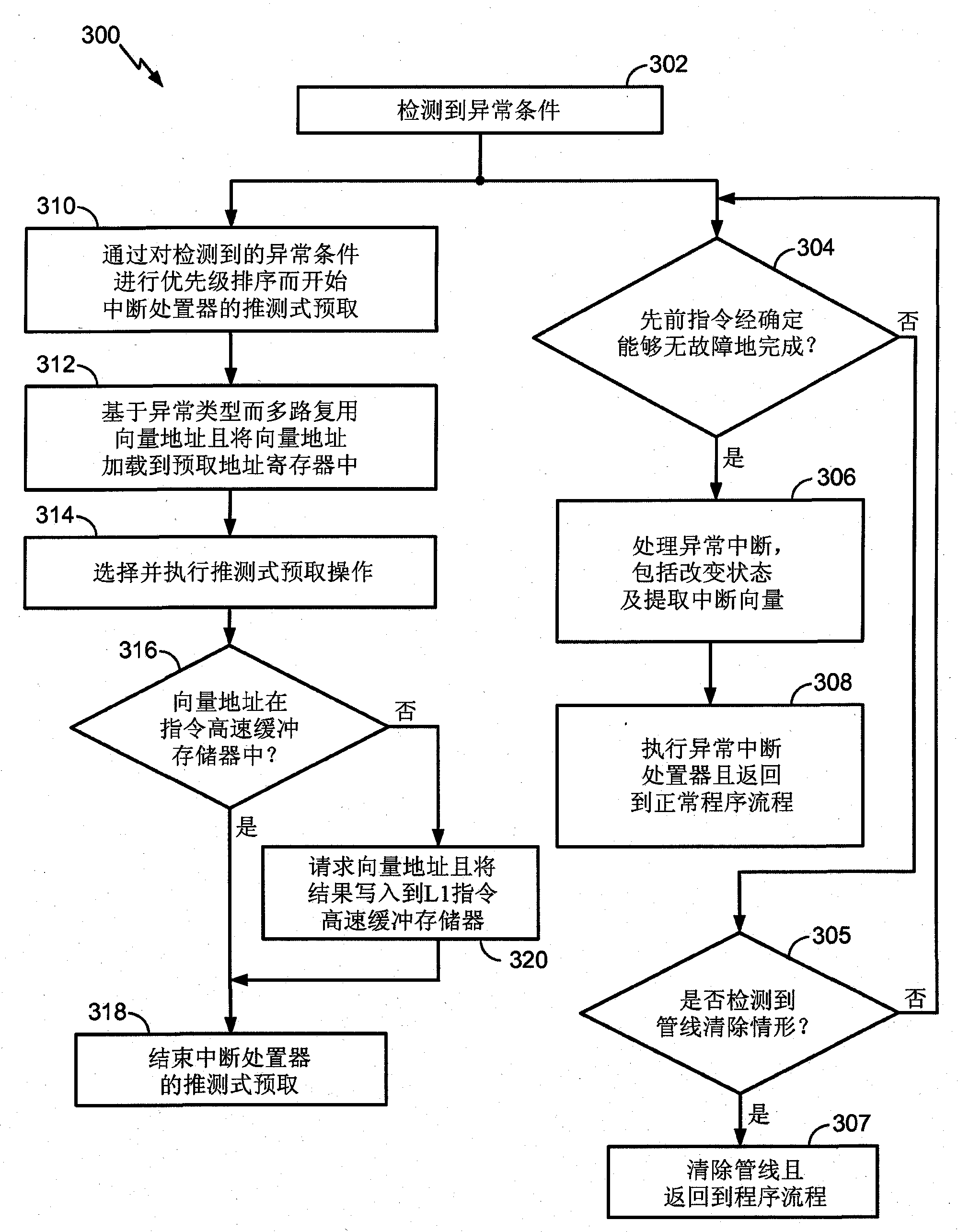

Apparatus and methods for speculative interrupt vector prefetching

InactiveCN102112966AProgram initiation/switchingMemory adressing/allocation/relocationInstruction pipelineInterrupt vector table

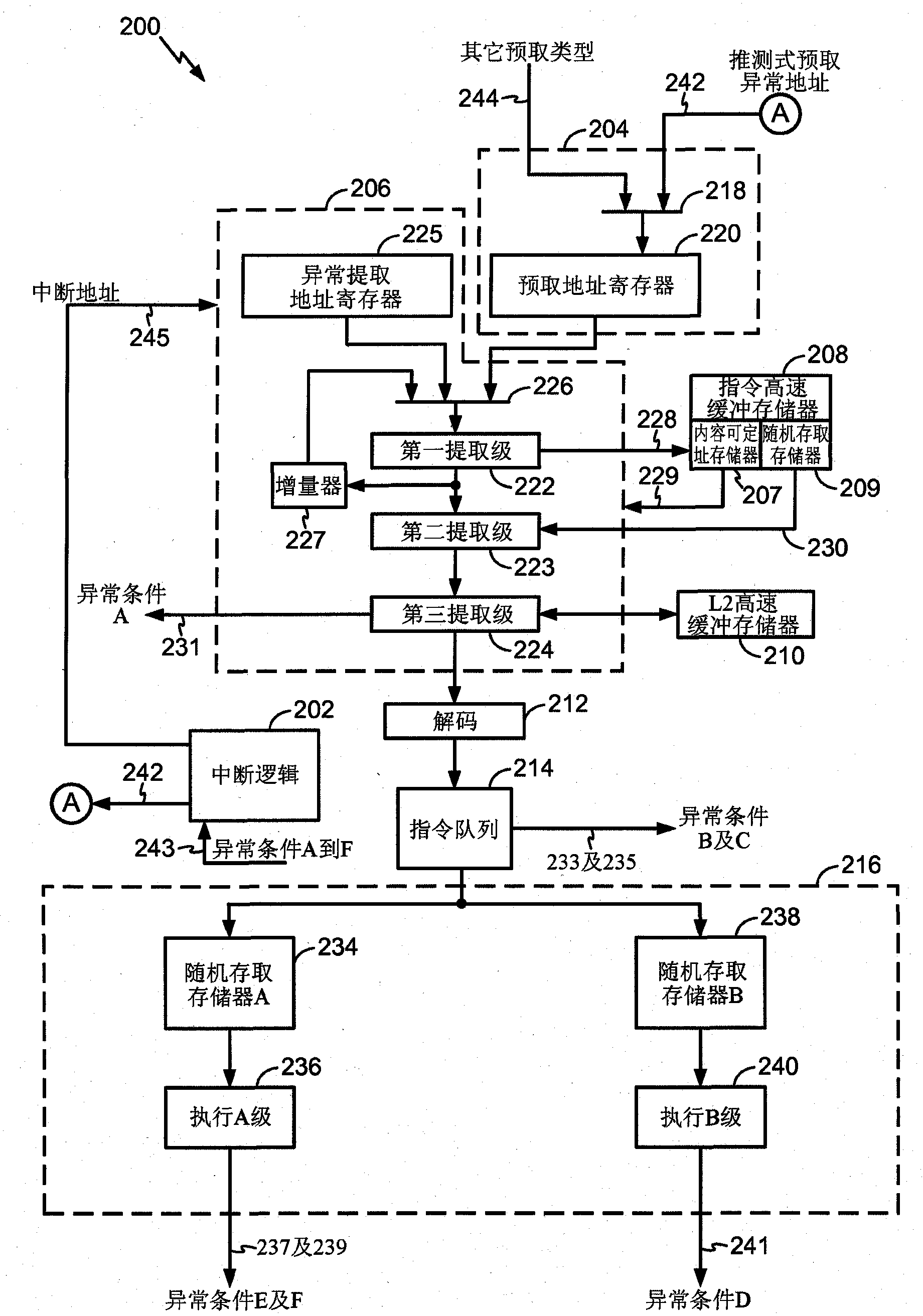

Techniques for interrupt processing are described. An exceptional condition is detected in one or more stages of an instruction pipeline in a processor. In response to the detected exceptional condition and prior to the processor accepting an interrupt in response to the detected exceptional condition, an instruction cache is checked for the presence of an instruction at a starting address of an interrupt handler. The instruction at the starting address of the interrupt vector table is prefetched from storage above the instruction cache when the instruction is not present in the instruction cache to load the instruction in the instruction cache, whereby the instruction is made available in the instruction cache by the time the processor accepts the interrupt in response to the detected exceptional condition.

Owner:QUALCOMM INC

Efficiently supporting interrupts

Owner:INTEL CORP

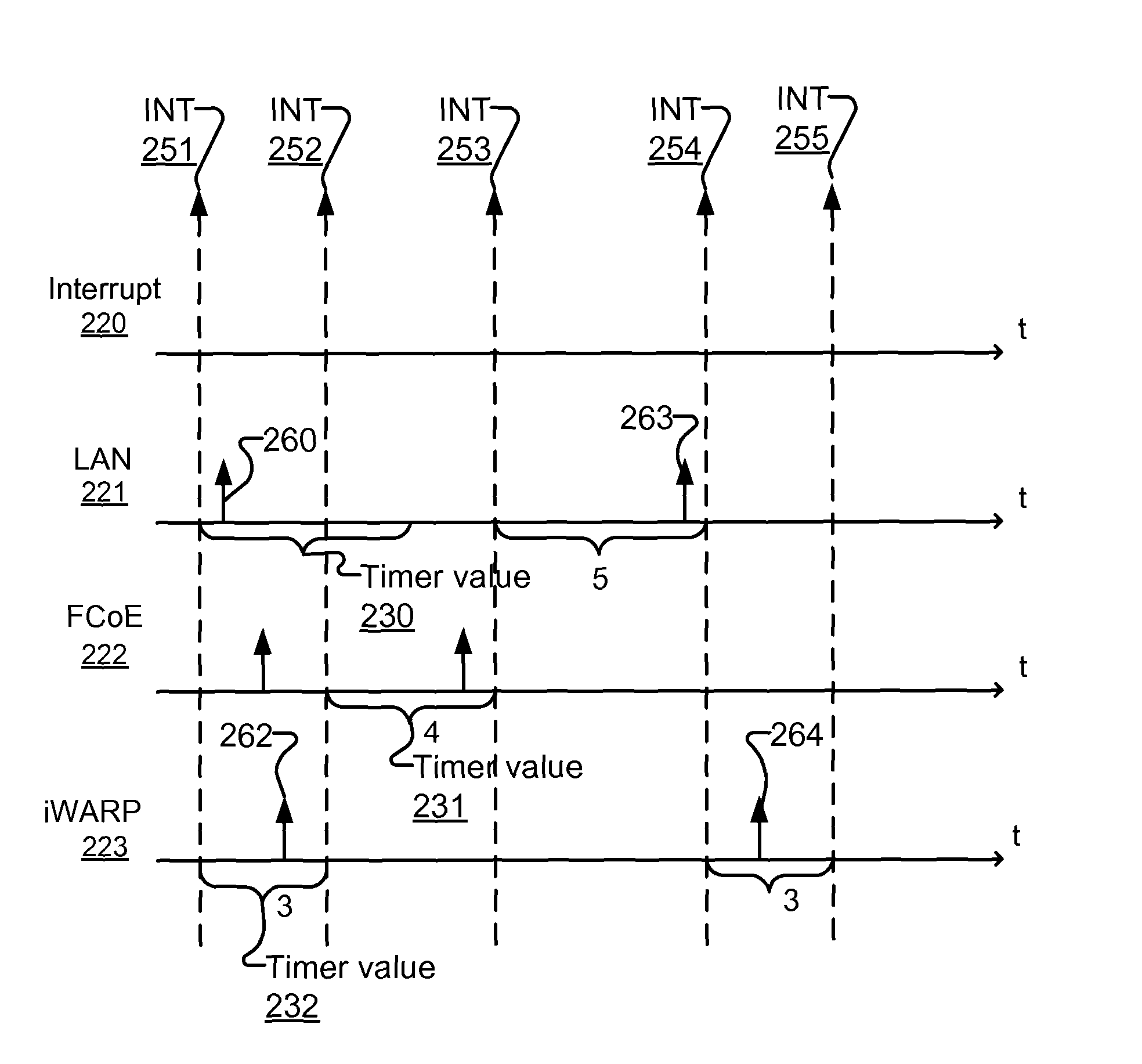

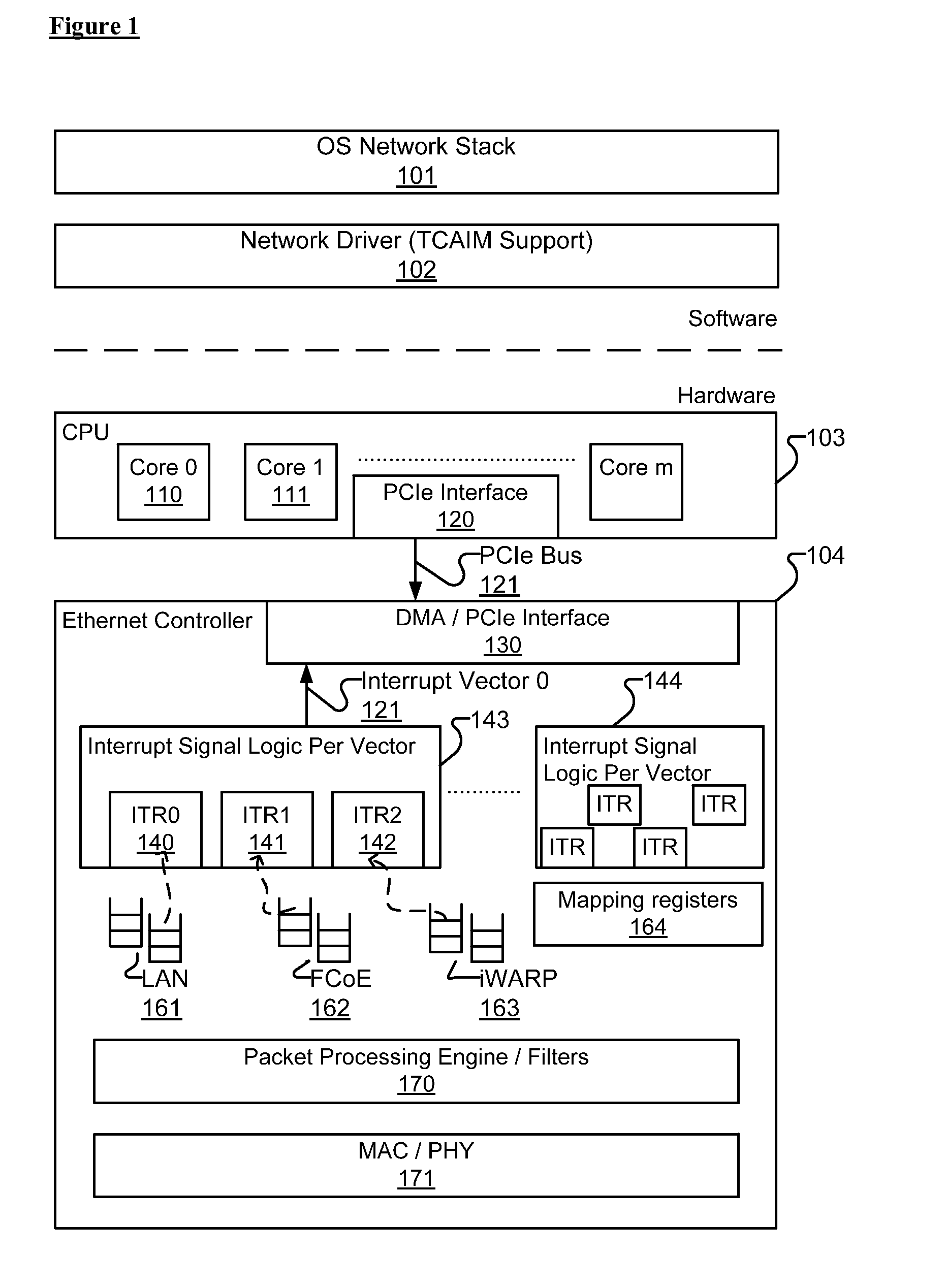

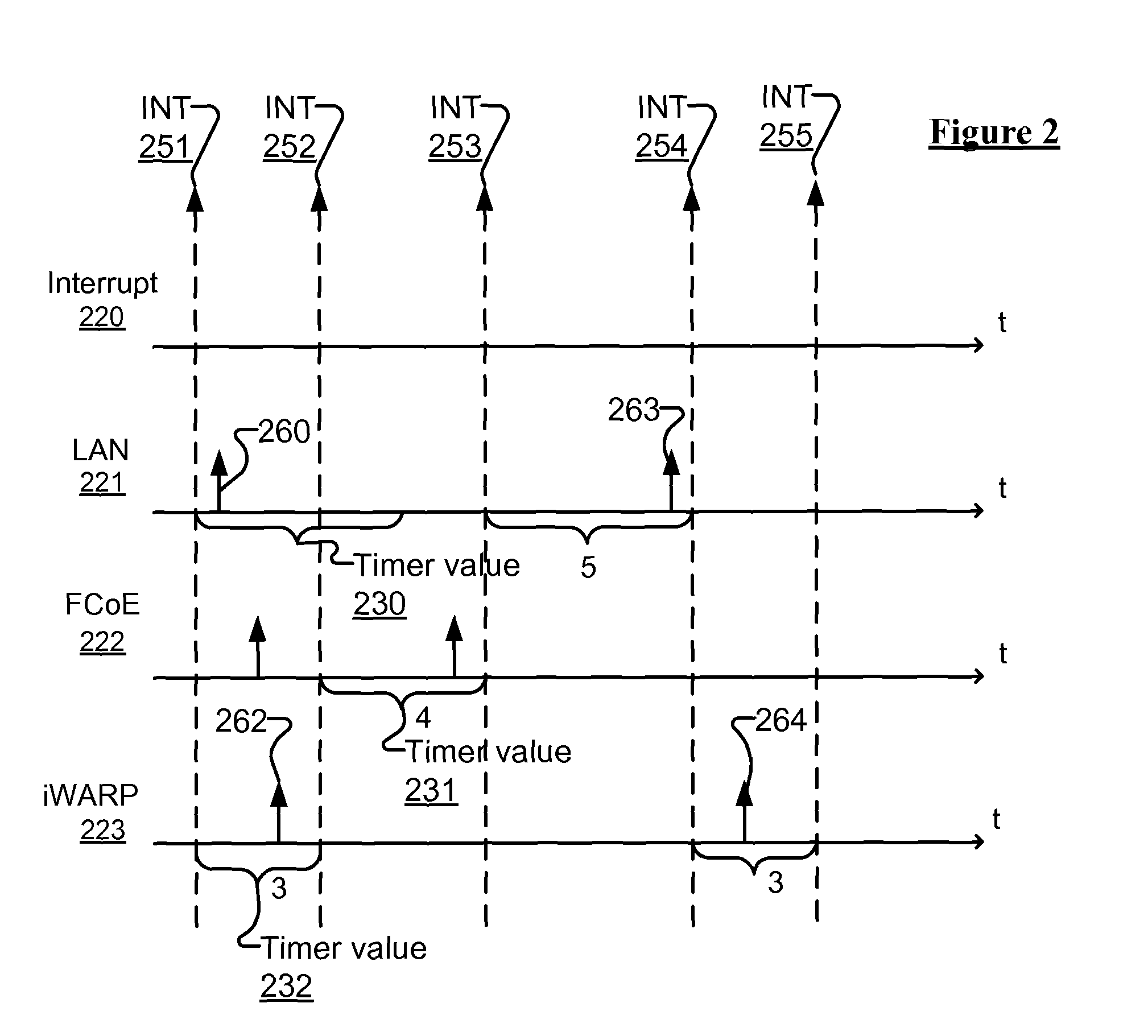

Traffic class based adaptive interrupt moderation

An apparatus which comprises two or more moderation timers associated with an interrupt vector is presented. In one embodiment, the apparatus comprises two or more interrupt vectors and moderation timers are set with different interrupt rates. An interrupt vector logic unit sends an interrupt vector if there is an interrupt event from the queue associated with a moderation timer and the moderation timer expires.

Owner:INTEL CORP

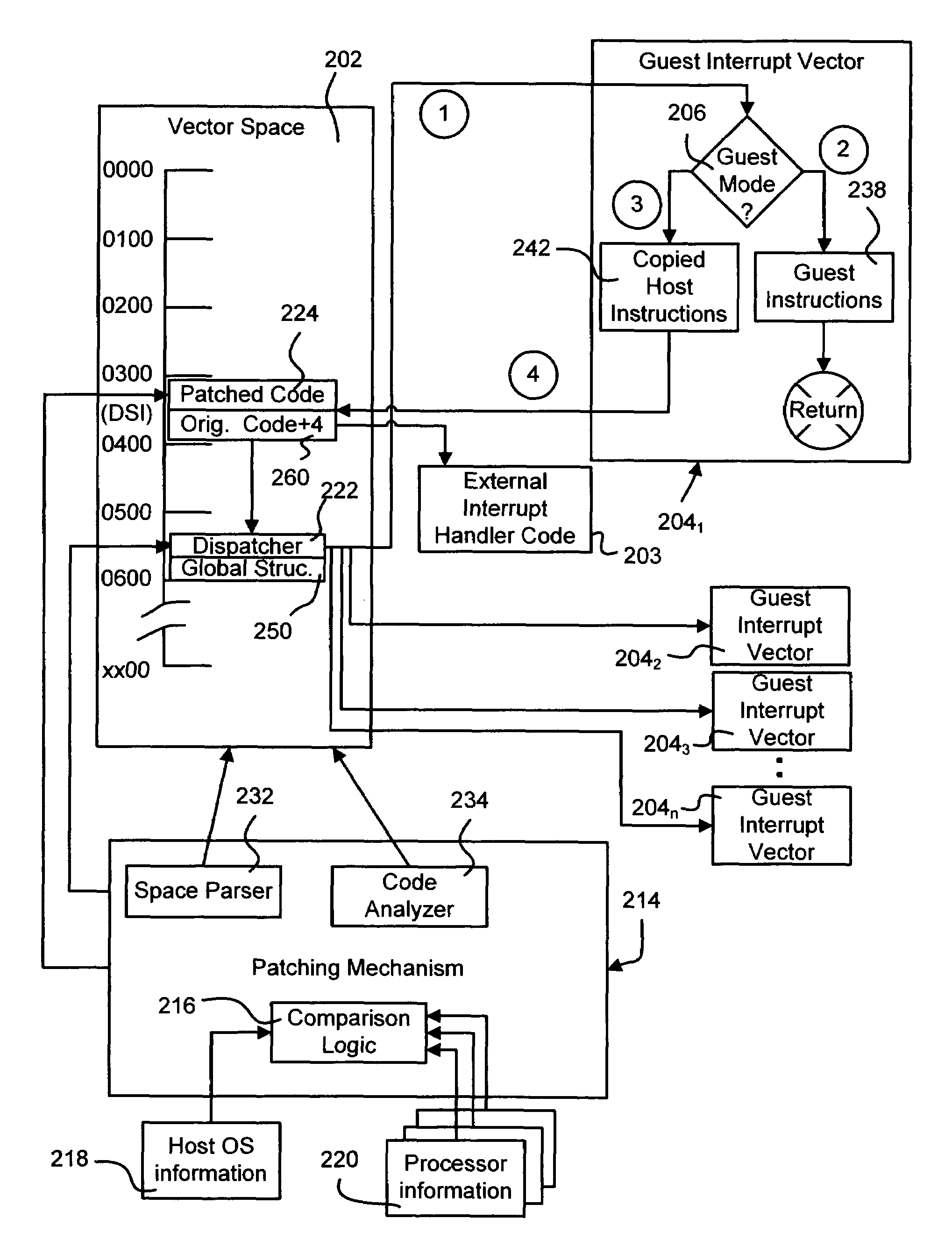

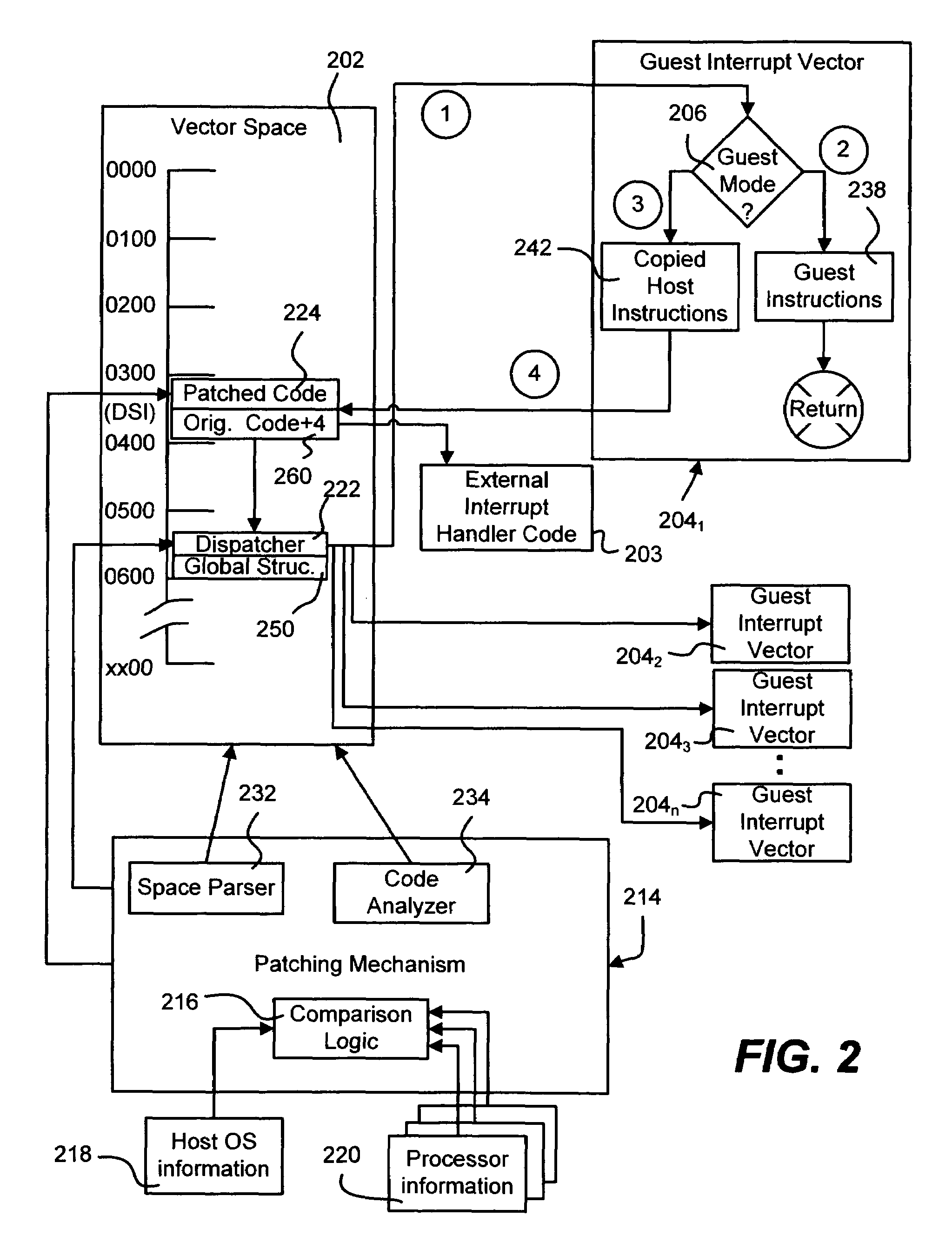

Method and system for dynamically patching an operating system's interrupt mechanism

InactiveUS7373446B2Improve performanceMaximum performanceSoftware simulation/interpretation/emulationMemory systemsOperational systemVirtual computing

In a virtual computing machine, a system and method that dynamically patches the interrupt mechanism (in interrupt vector space) of a host computing architecture with guest mode software. Significant increases in performance are achieved without depending on the host code. A patching mechanism evaluates the operating system version, processor, and code to be patched. If patchable, low-level interfaces are created dynamically; a dispatcher is written into an unused location in vector space, and instructions copied from each interrupt vector to be patched to a guest interrupt vector. For an interrupt, the new, patched instructions branch to the dispatcher, which then branches to the appropriate patched interrupt guest code. If the processor is operating as a virtual machine, the guest interrupt code handles the interrupt, otherwise the original copied instructions are replayed, followed by execution at the original host instruction in vector space that exists after the copied and patched instructions.

Owner:MICROSOFT TECH LICENSING LLC

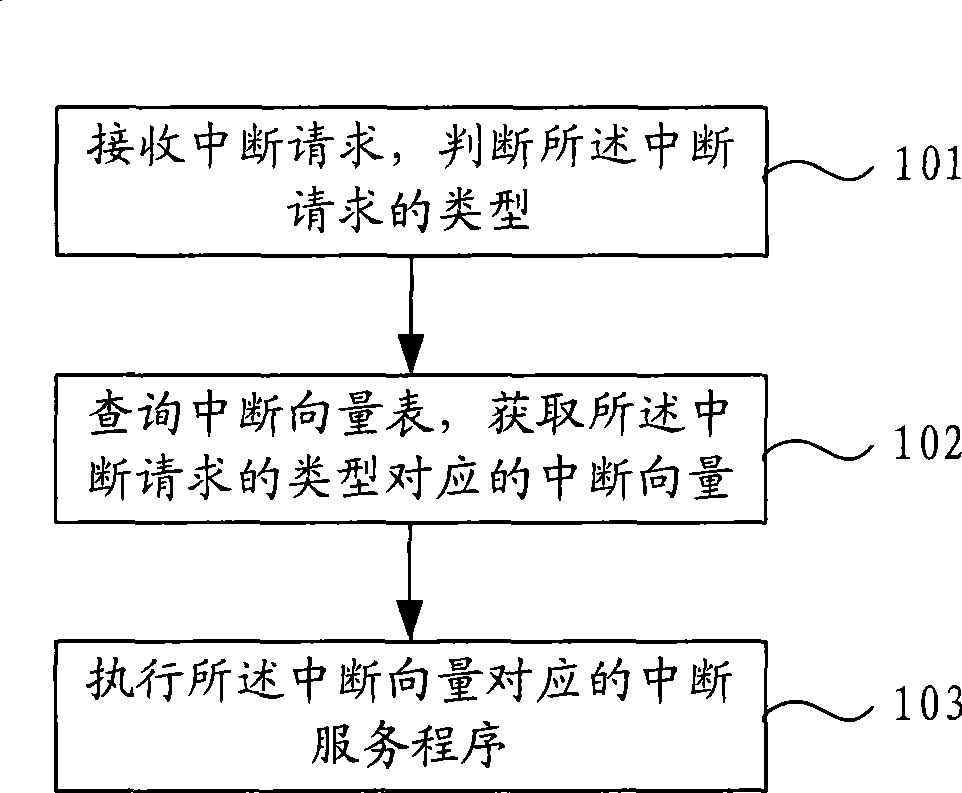

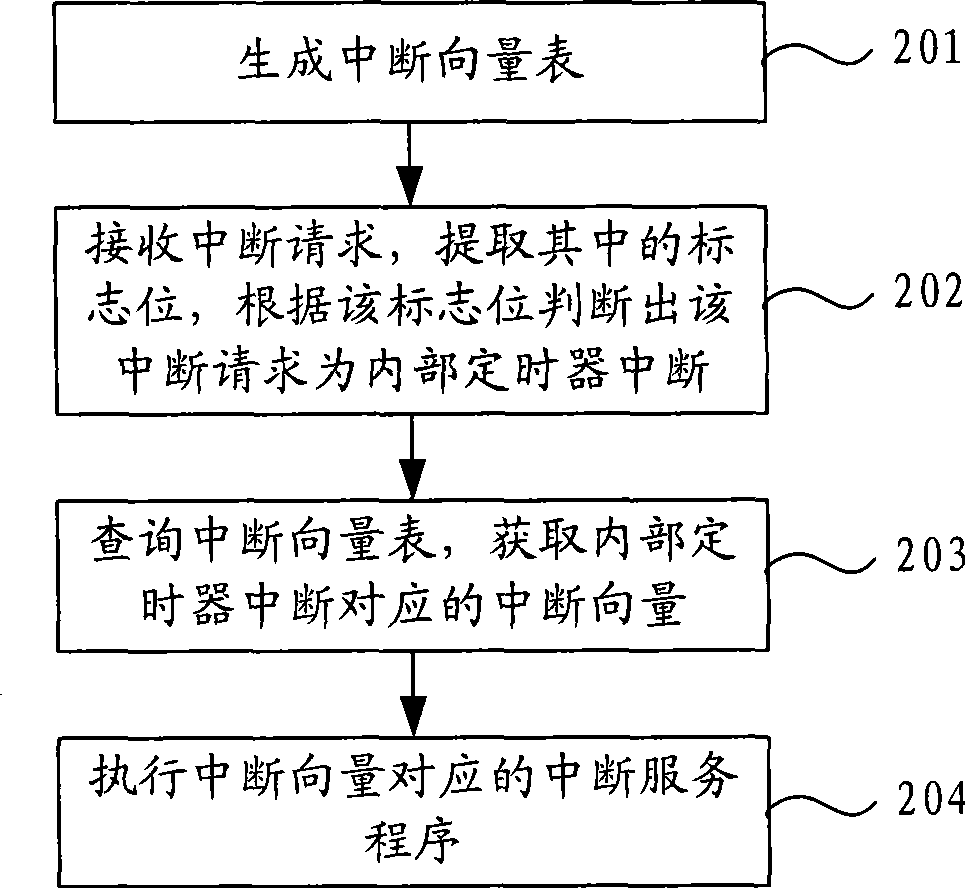

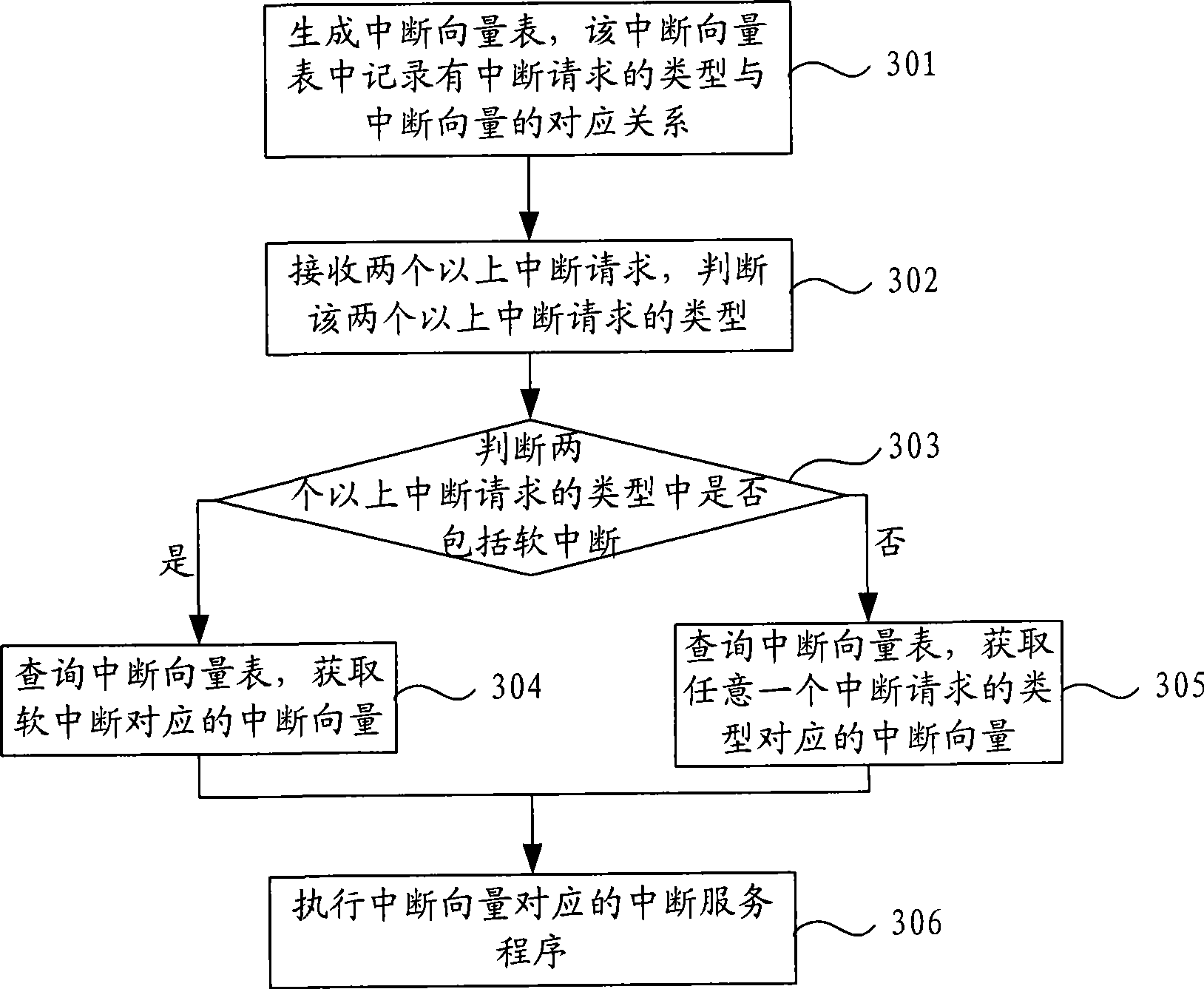

Interruption system implementing method and device

ActiveCN101488100AImprove playbackOptimized interrupt handlingProgram initiation/switchingArchitecture with single central processing unitInterrupt vector tableEmbedded system

The invention relates to an interrupt system realization method and a device thereof, wherein, the method comprises the steps as follows: an interrupt request is received, and the type of the interrupt request is judged; an interrupt vector table is referred to for obtaining the interrupt vector corresponding to the type of the interrupt request; and an interrupt service program corresponding to the interrupt vector is executed. The device comprises a receiving module, a reference module and an executing module. The interrupt system realization method and the device thereof realize the execution of the corresponding interrupt service program according to the type of the interrupt request by judging the type of the interrupt request, referring to the interrupt vector table, obtaining the interrupt vector corresponding to the type of the interrupt request and executing the interrupt service program corresponding to the interrupt vector, and overcomes the disadvantage that the interrupt processing manner is single, thus better optimizing the interrupt processing manner and ensuring that the resource of an interrupt system is brought into better play in the aspect of industrial control.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

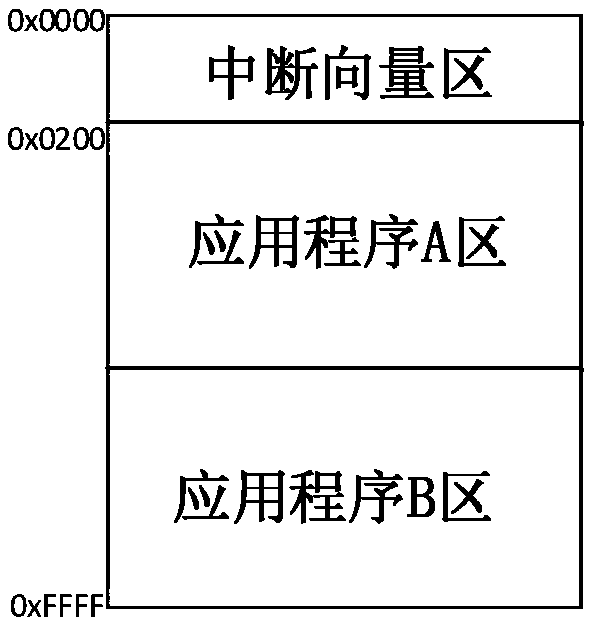

A single chip microcomputer online upgrading method and system

ActiveCN109240730ASave moving timeSuccessful online upgradeSoftware engineeringMicrocomputerMicrocontroller

The invention relates to the technical field of single chip microcomputer, especially relates to a single chip microcomputer online upgrading method and system, wherein the method comprises the following steps: the single chip microcomputer initializes the upgrading variable after receiving the upgrading start command, and replies the current running area to the upgrading software of the upper computer, so that the upgrading software of the upper computer decides to generate the upgrading Bin file to be transmitted according to the current running area; The single chip microcomputer receives the upgraded Bin file and stores the upgraded Bin file in the unrunning area of the single chip microcomputer. After receiving the upgrade jump command, MCU shuts down the interrupt, copies the interrupt vector area of upgrade program to the interrupt vector area of MCU, runs the new program after the soft restart, and completes the upgrade. The invention divides the FLASH of the single chip microcomputer into an interrupt vector area, an application program A area and an application program B area. The interrupt vector area occupies small bytes, and only the interrupt vector area needs to be copied when upgrading, thereby saving the FLASH space and the program moving time. At that same time, the upgrade Bin file can be converted into region, and the online upgrade can be realized without interrupting the service.

Owner:GUANGXUN SCI & TECH WUHAN

Method and apparatus for counting interrupts by type

InactiveUS7082486B2Memory adressing/allocation/relocationHardware monitoringInterrupt vector tableSoftware

A method, apparatus, and computer instructions for counting interrupts by type. An interrupt count is incremented when a particular type of interrupt occurs. The count may be stored in the IDT or an interrupt count table outside the IDT. The interrupt unit increments the count each time a particular type of interrupt occurs. In the event of a potential count overflow, the mechanism of the present invention provides logic necessary to notify software in order to handle the overflow.

Owner:INT BUSINESS MASCH CORP

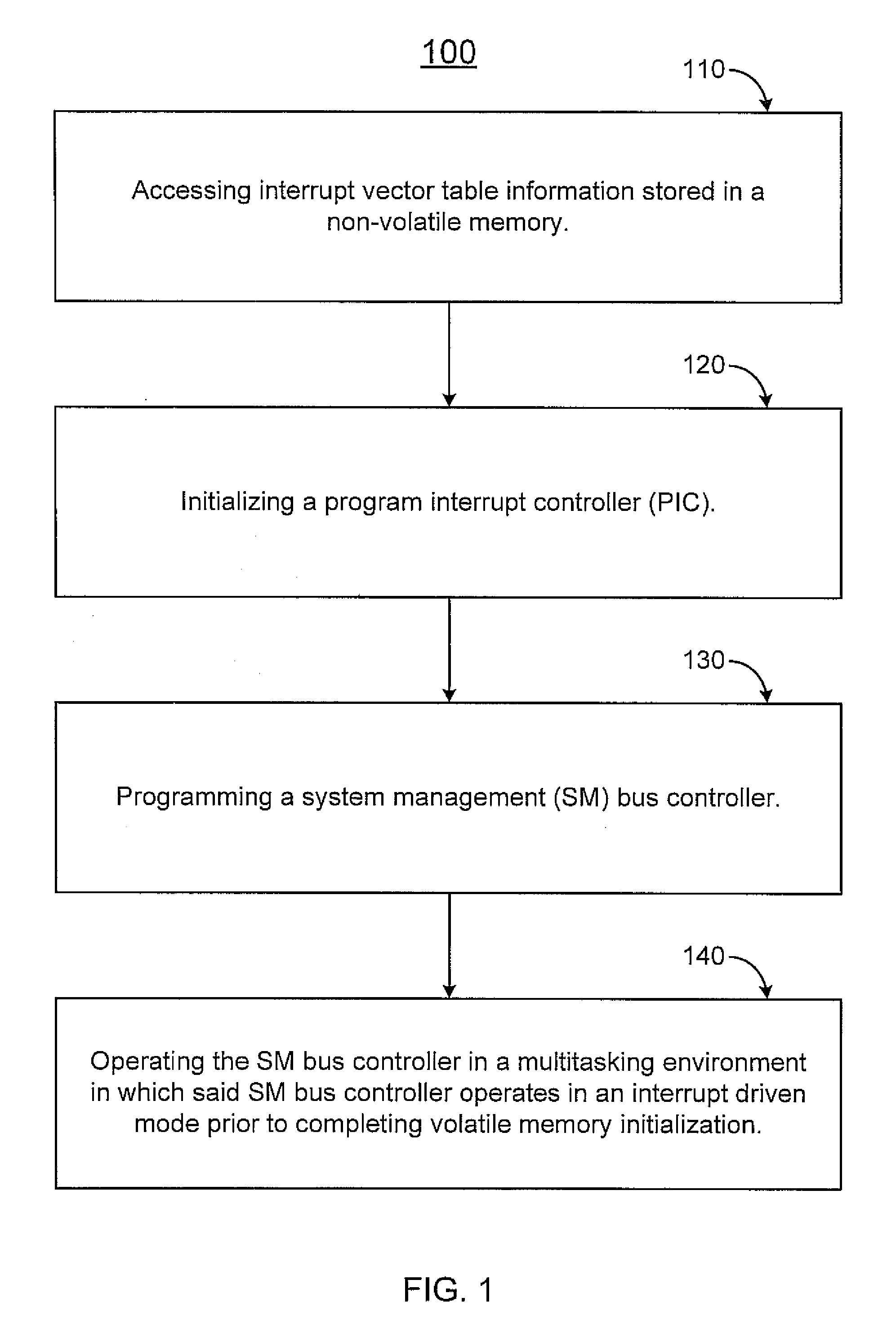

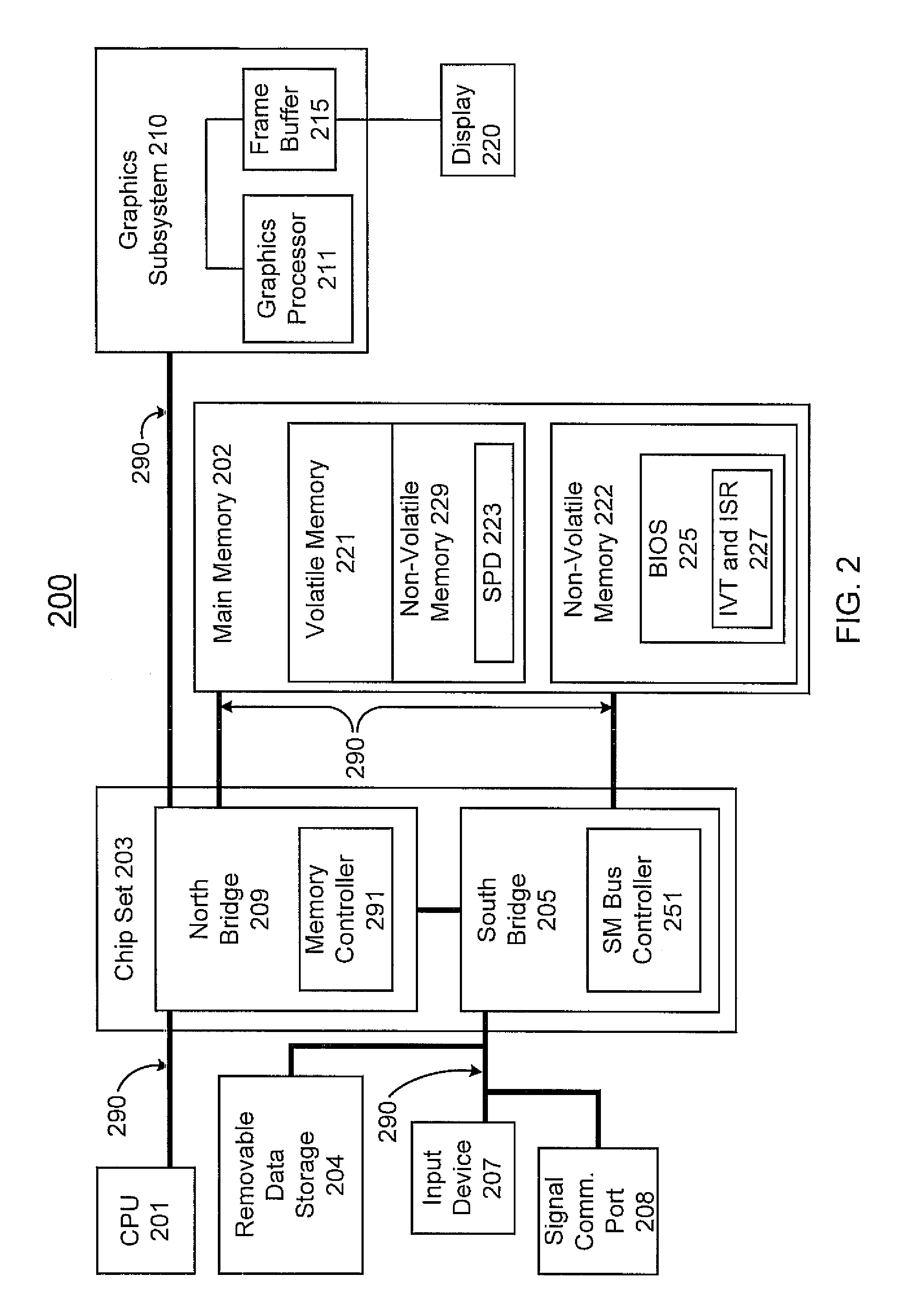

Multi-tasking bootstrap system and method

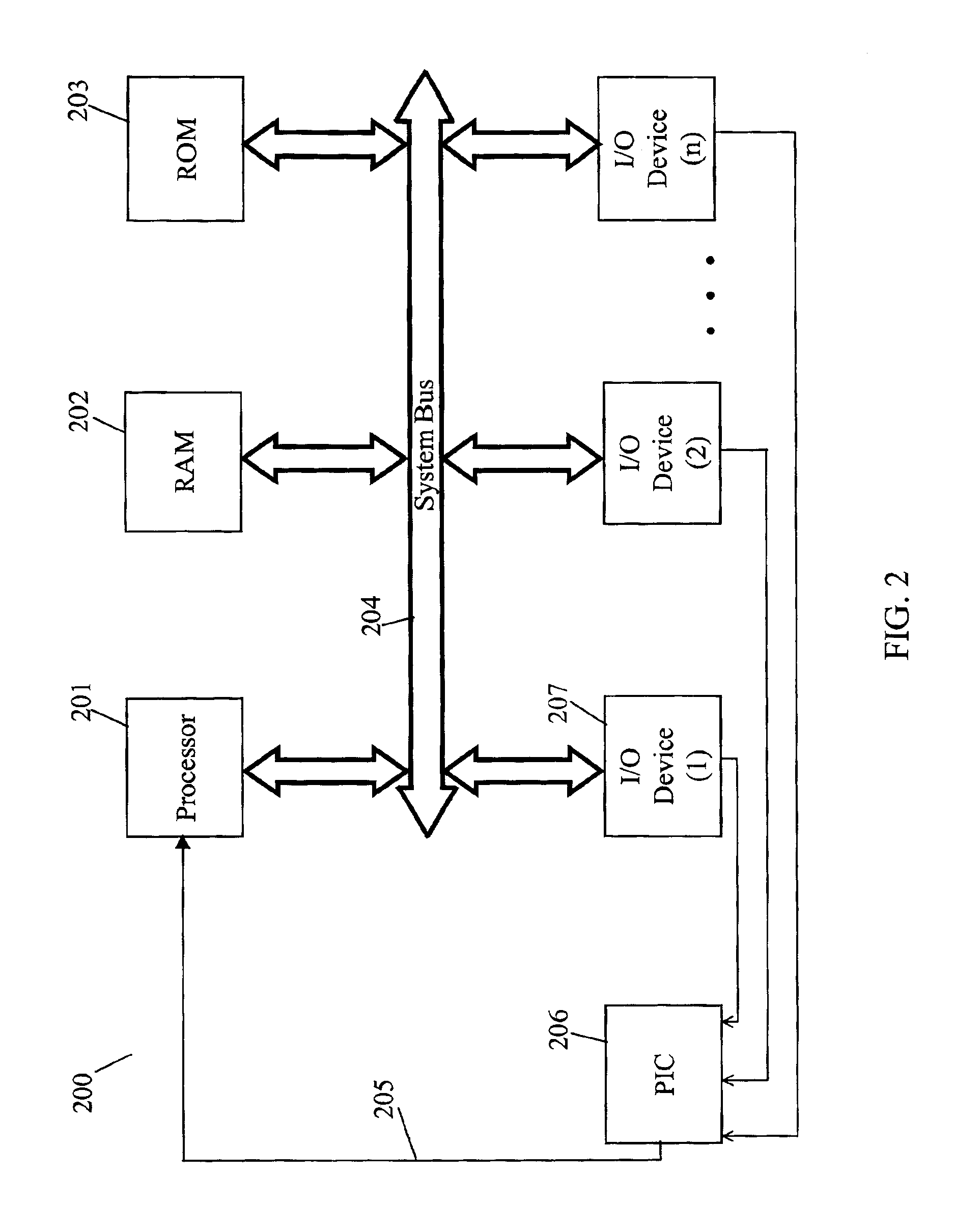

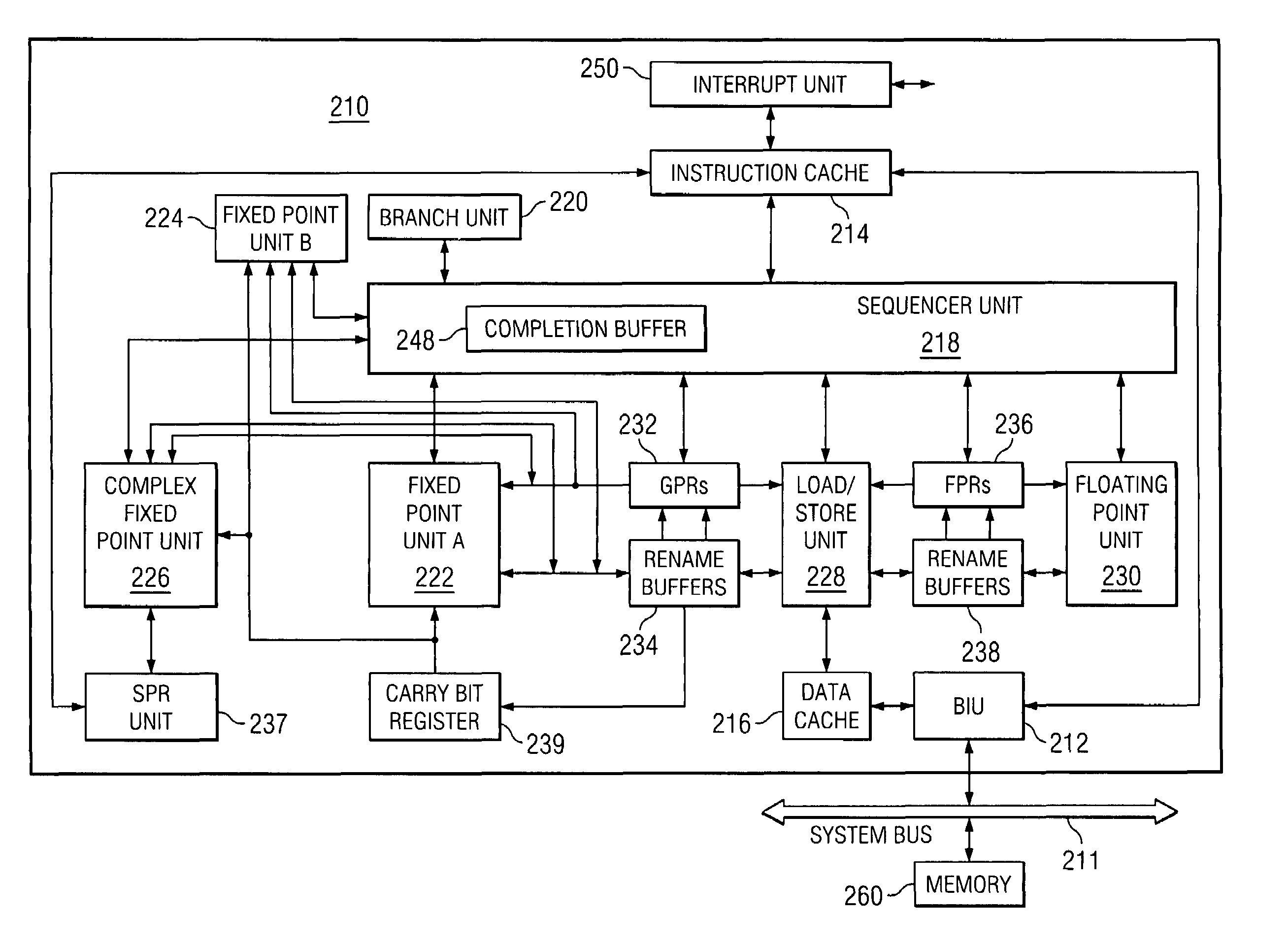

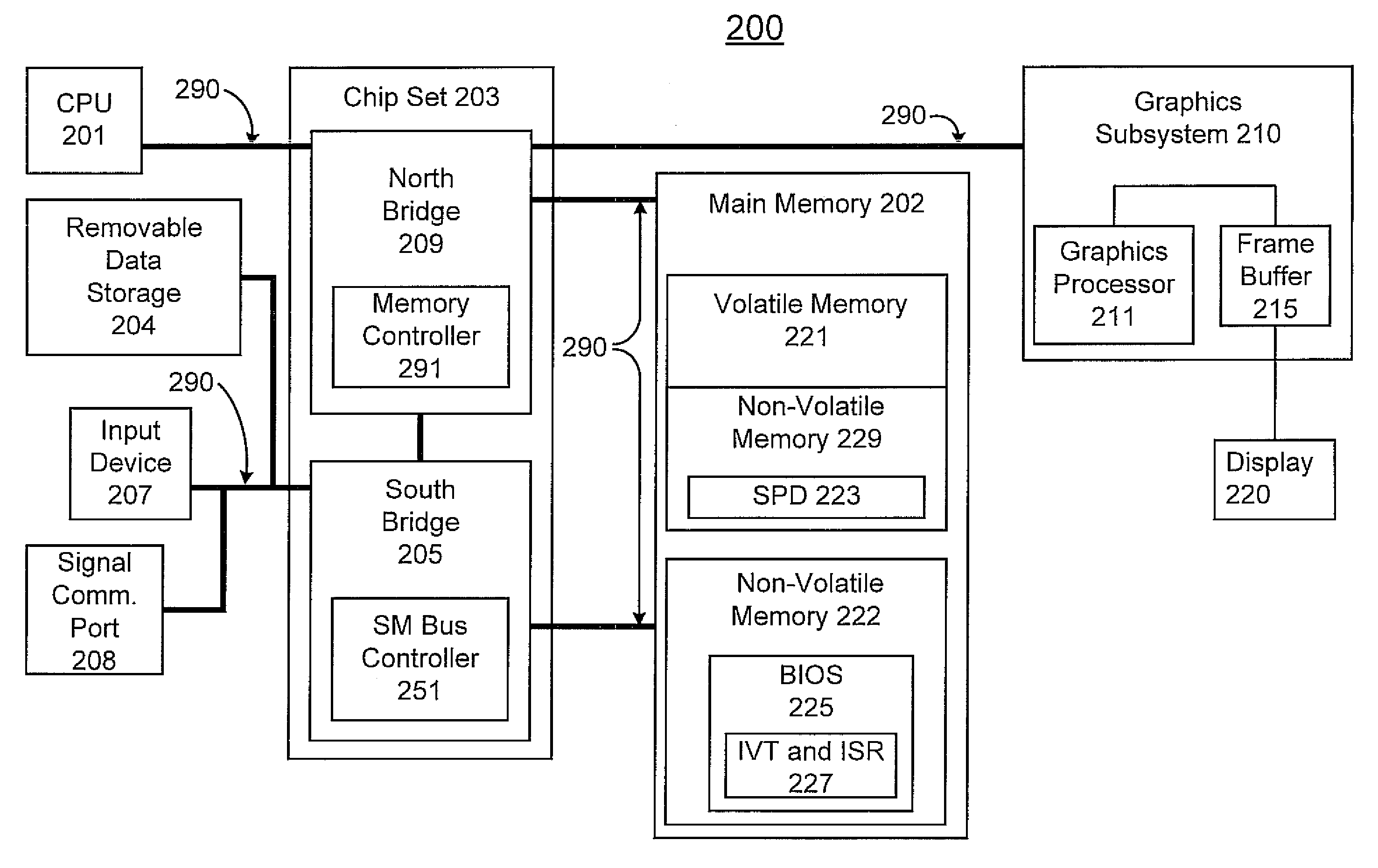

A multi-task boot strap system and method for expediting boot up initialization processes are presented. In one embodiment, a multi-task boot strap method includes accessing interrupt vector table information stored in a non-volatile memory. For example, an interrupt vector table and corresponding interrupt service routine information associated with a system management (SM) bus controller operation are accessed from a read only memory (ROM). A program interrupt controller (PIC) is initialized to interpret the interrupt information from the non-volatile memory. This permits the operation of the system management bus controller to be performed in a multi-tasking environment (e.g., operating the SM bus controller in an interrupt mode). A processor can be configured to retrieve the boot up information (e.g., serial presence detect data) and process interrupts with interrupt service routine information retrieved from non-volatile memory. The processor can performing other multi-task operations while waiting for an interrupt during boot up operations.

Owner:NVIDIA CORP

Method and apparatus for testing hardware interrupt service routines in a microprocessor

A read / writable memory formed in the same semiconductor chip as a microprocessor is employed in testing a plurality of hardware interrupt service routines initiated by corresponding devices (and components of devices) during a power-on, self-test(POST) of a computer system. The POST is set in the read-only memory(ROM) of the computer system. The read / writable memory, which is ordinarily inoperative during the POST, is used for storing a diagnostic interrupt vector table, which has a list of interrupt numbers and corresponding addresses of the respective interrupt routines. This table is normally subject to change because each device and each of its components have different interrupt service routines, requiring different addresses for the same interrupt number. The random access memory(RAM) has not yet been tested in the POST, and is not regarded as reliable for the hardware interrupt testing and therefore the read / writable memory is used for such testing.

Owner:ADVANCED MICRO DEVICES INC

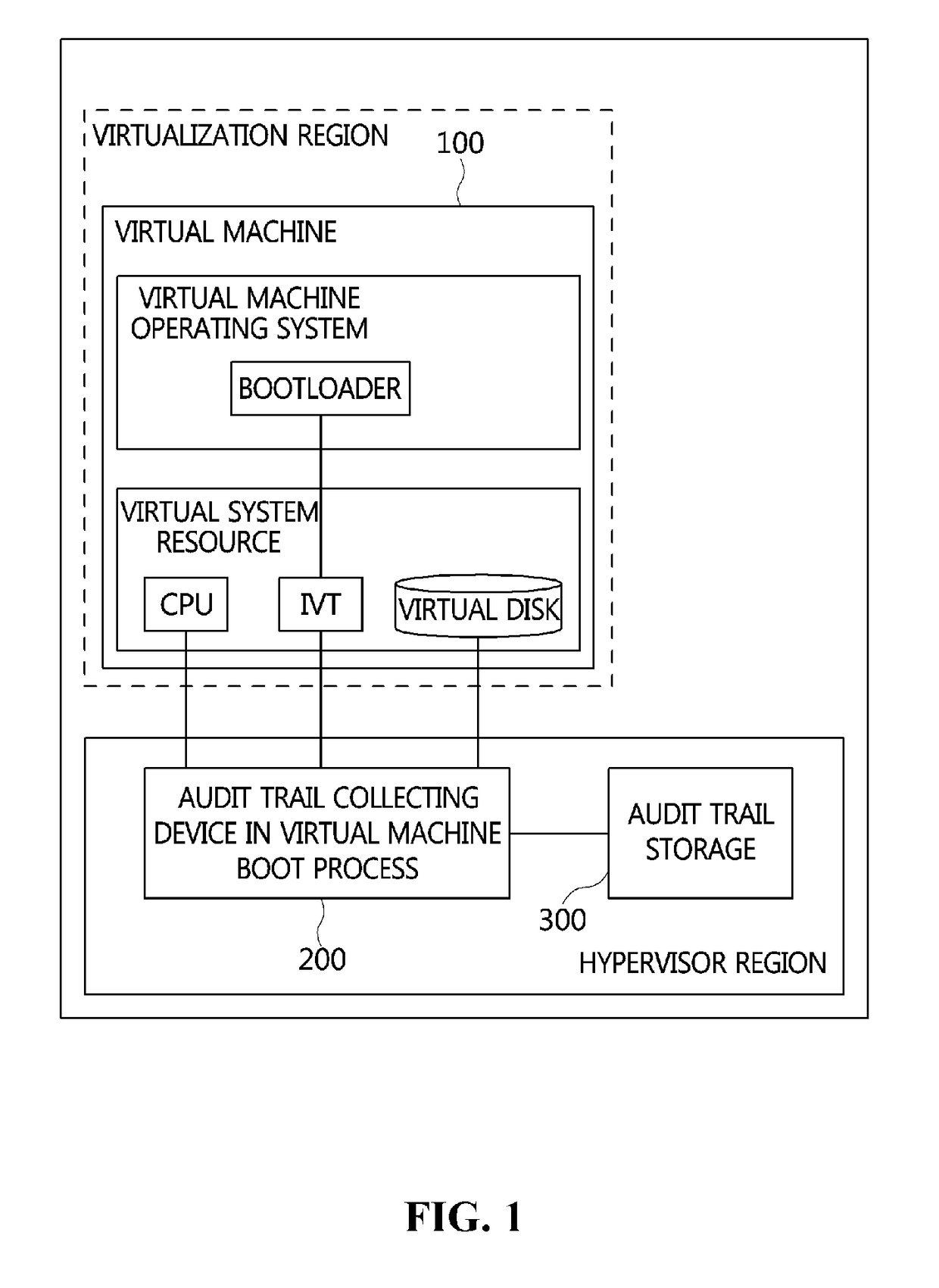

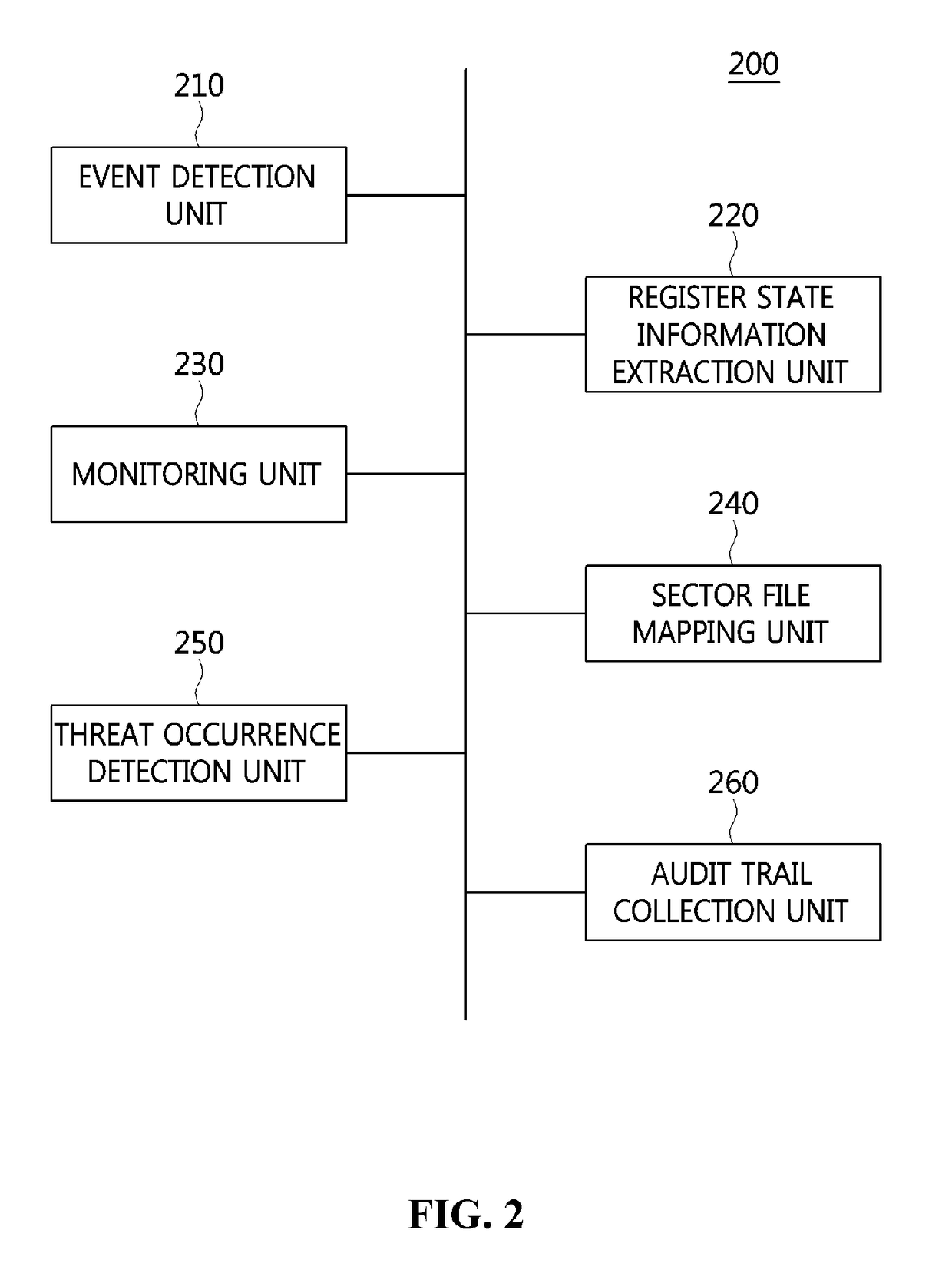

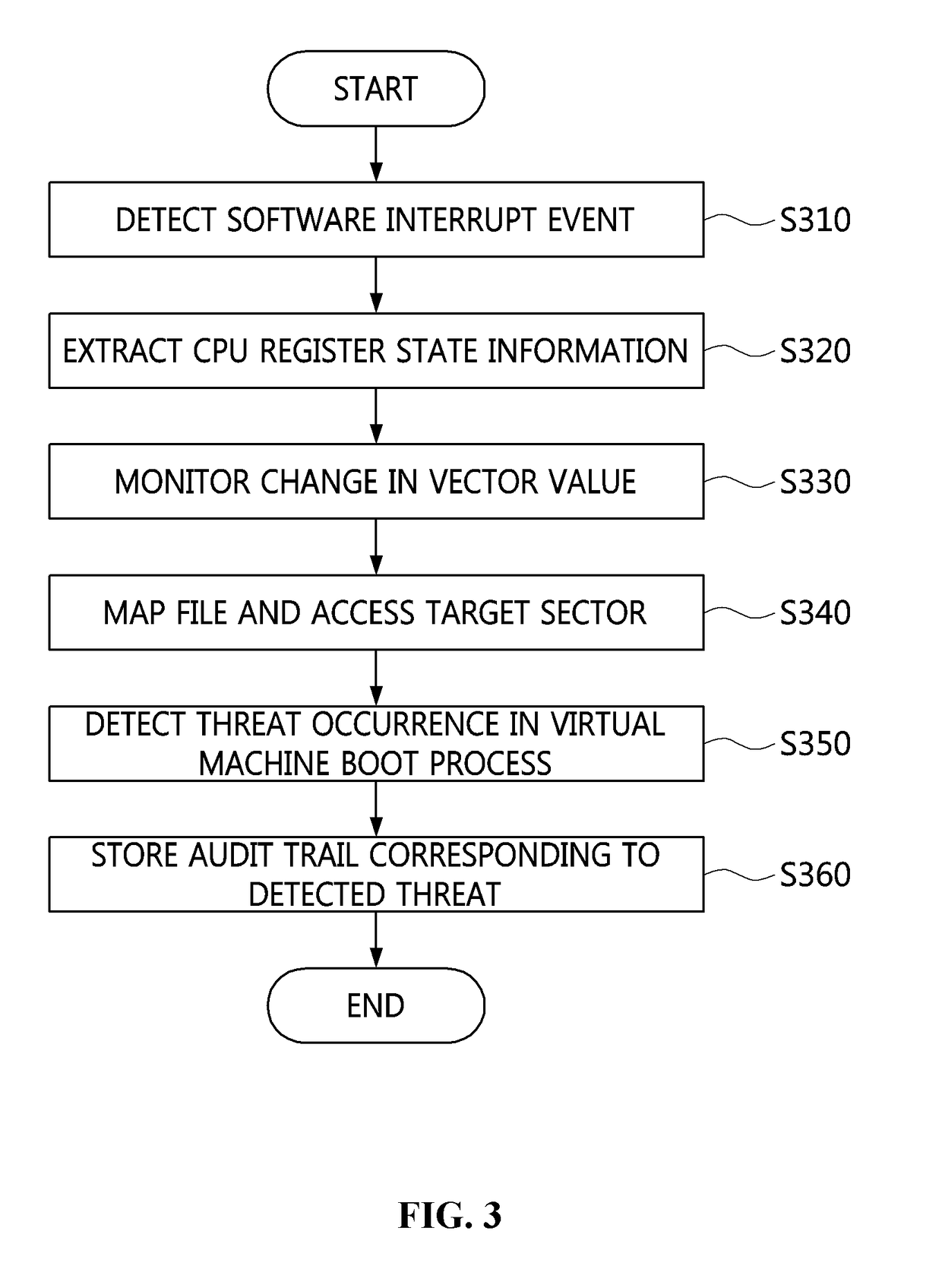

Apparatus and method for collecting audit trail in virtual machine boot process

ActiveUS20190012465A1Accurate judgmentPlatform integrity maintainanceSoftware simulation/interpretation/emulationProcessor registerInterrupt vector table

An apparatus and method for collecting an audit trail in a virtual machine boot process, the audit-trail-collecting apparatus including an event detection unit for detecting a software interrupt event, a register state information extraction unit for extracting state information of a CPU register corresponding to a detection time of the software interrupt event, a monitoring unit for monitoring a change in a vector value corresponding to the software interrupt event in an interrupt vector table, a threat occurrence detection unit for detecting a threat occurrence in a virtual machine boot process based on at least one of the CPU register state information and a monitored result, and an audit trail collection unit for storing an audit trail corresponding to at least one of the CPU register state information and the monitored result when the threat occurrence is detected in the virtual machine boot process.

Owner:ELECTRONICS & TELECOMM RES INST

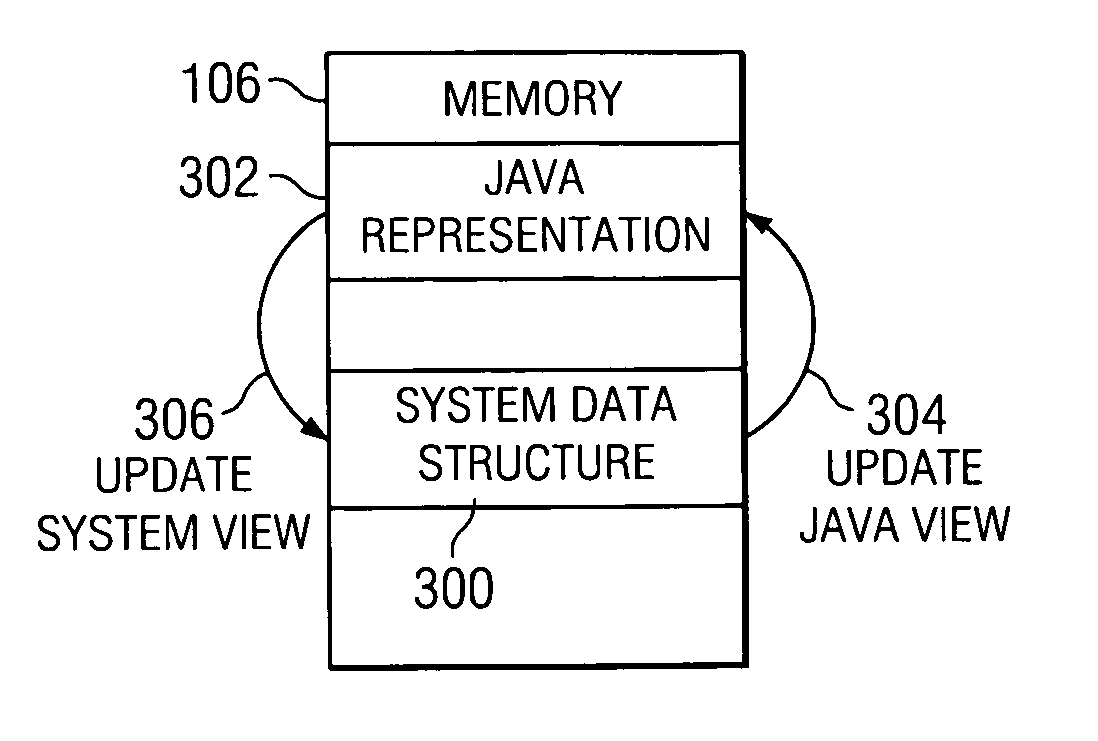

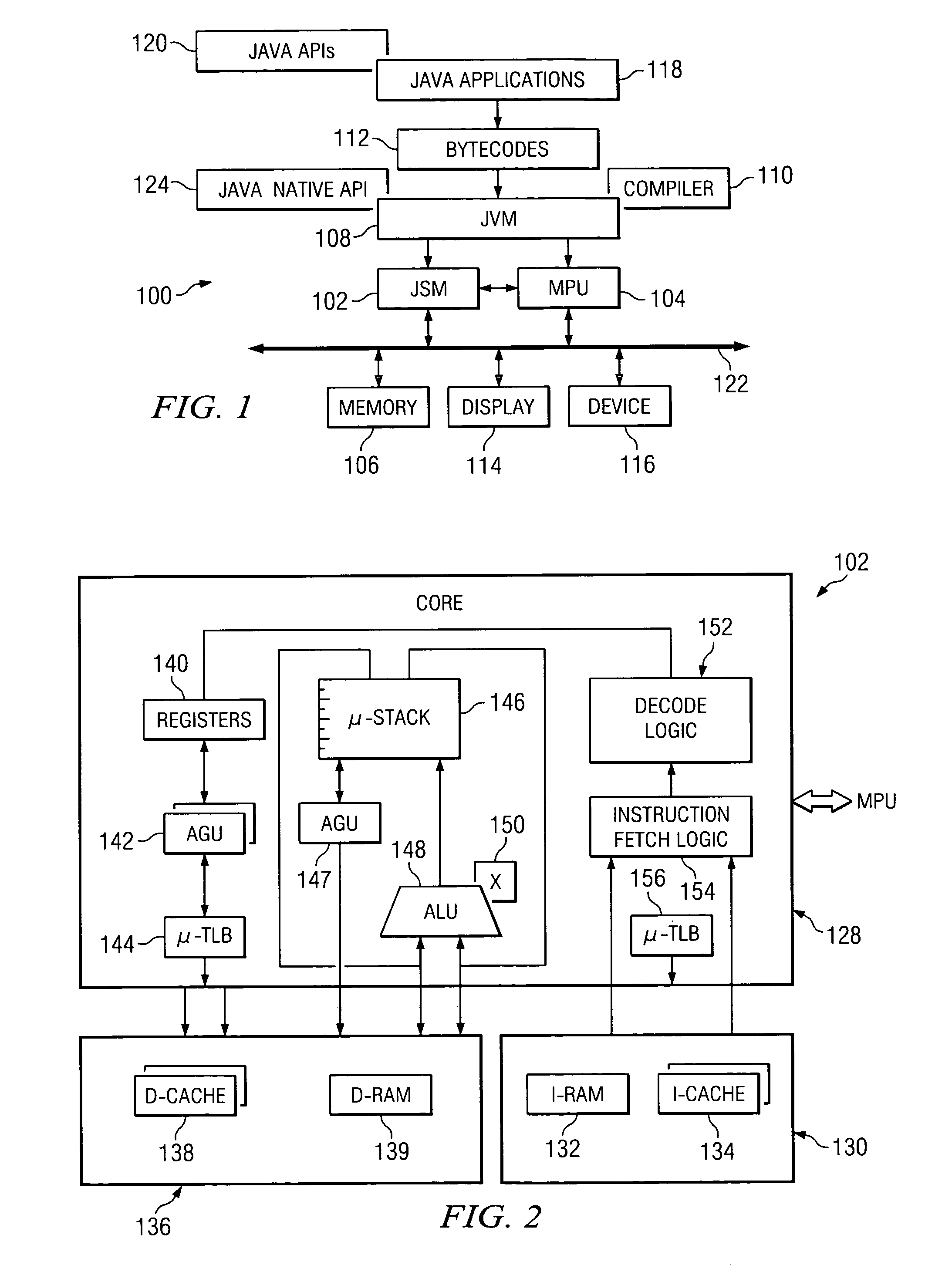

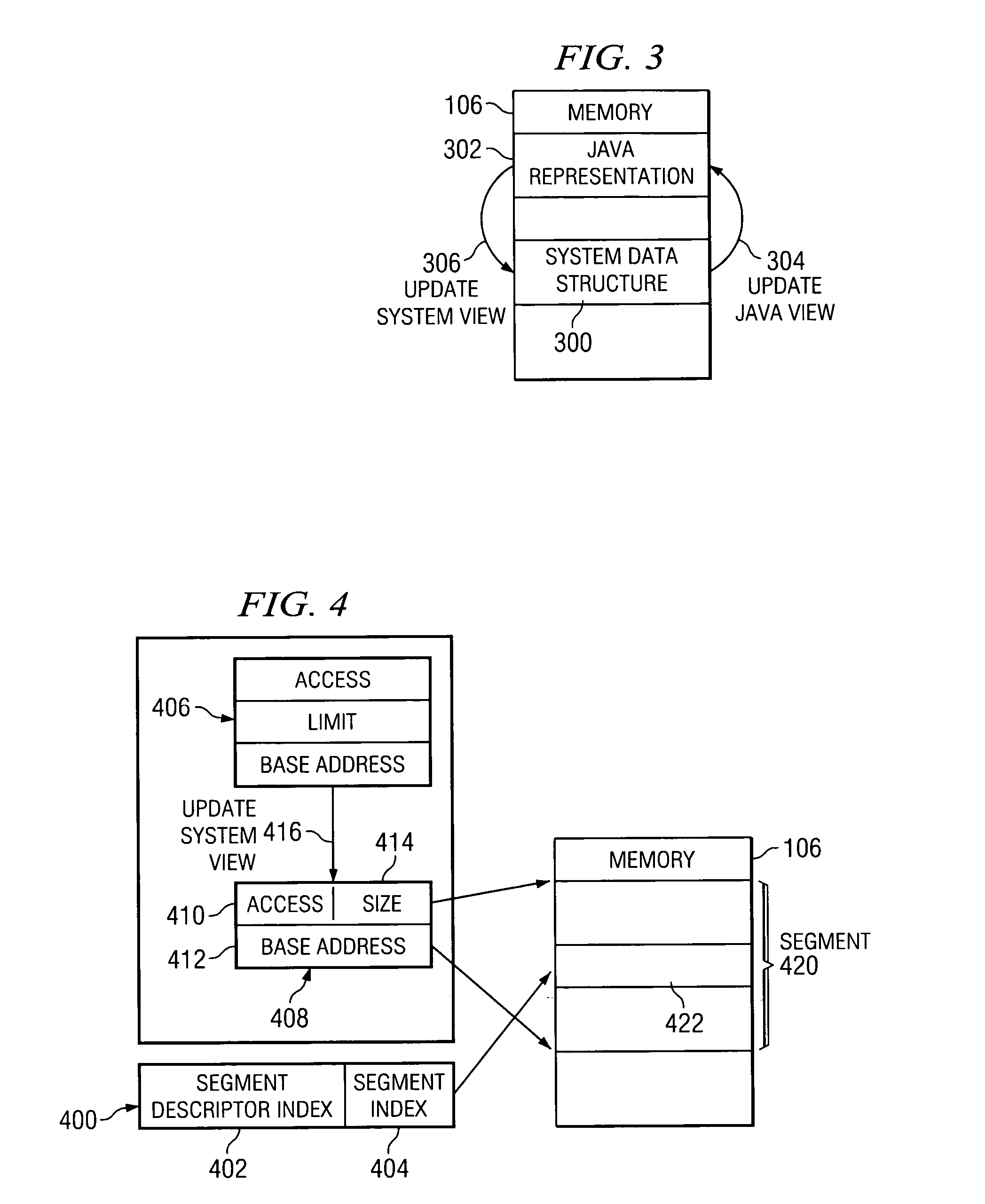

Method and system for implementing interrupt service routines

ActiveUS20060026564A1Memory architecture accessing/allocationEnergy efficient ICTInterrupt vector tableEmbedded system

Methods, computer-readable media, and systems for interrupt handling in Java™ are provided. In some illustrative embodiments, a method for interrupt handling in Java software that executes on a processor comprising creating a Java representation of an interrupt vector table, instantiating a first Java object comprising a first Java method for handling an interrupt, inserting a reference to the first Java object in the Java representation of the interrupt vector table at a location corresponding to a level of the interrupt, and updating a location in the system level interrupt vector table corresponding to the level of the interrupt using the contents of the location in the Java representation.

Owner:TEXAS INSTR INC

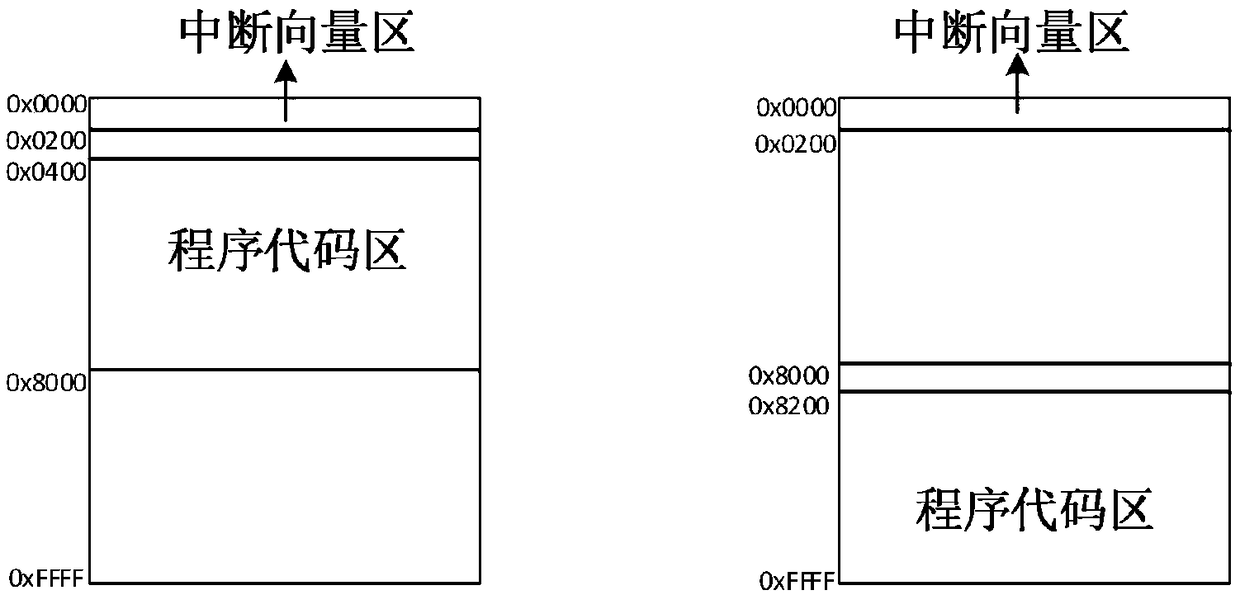

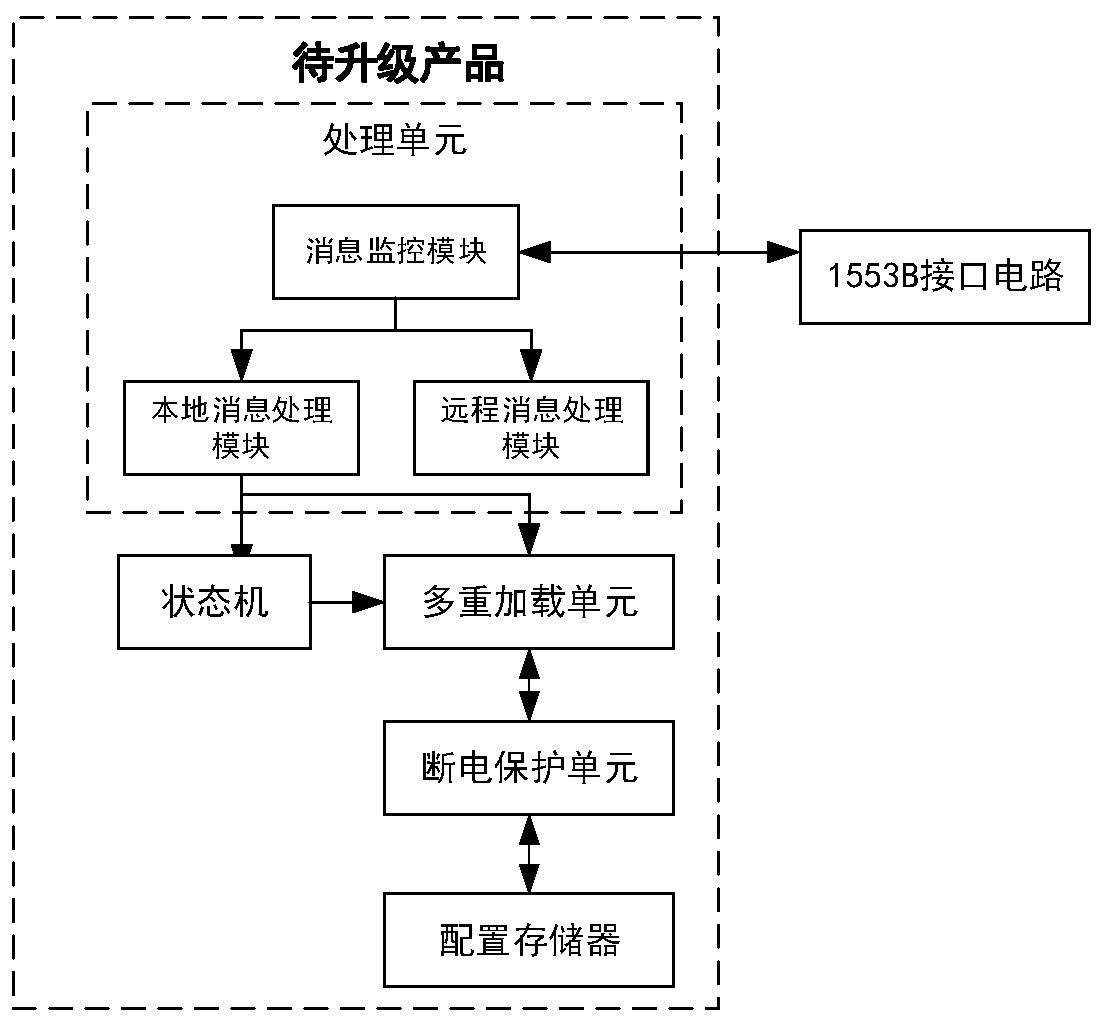

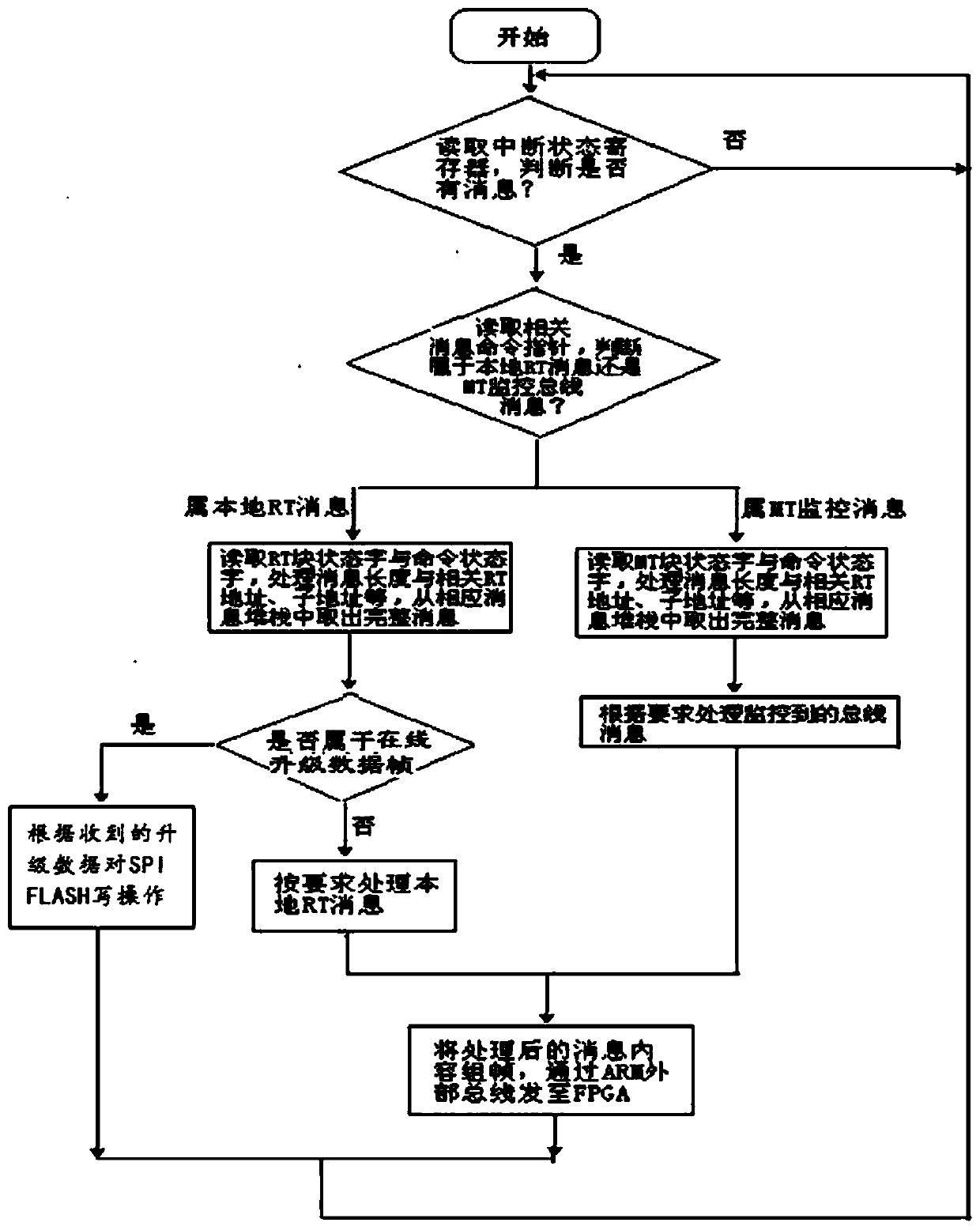

Product online upgrading system and method based on multiple loading

PendingCN110244971AAchieve another upgradeAvoid disassemblySoftware engineeringProgram loading/initiatingApplication softwareInterrupt vector table

The invention discloses a product online upgrading system and method based on multiple loading. The system comprises a configuration memory, a processing unit and a multi-loading unit, wherein a basic program and an application program are stored in the configuration memory in a partitioned manner; the processing unit receives an on-line upgrading data frame sent from the outside, and writes the on-line upgrading data frame into an application program partition in the configuration memory through a reloading unit; the multi-loading unit writes the online upgrade data frame into an application program partition and then skips to a first interrupt vector table in a newly written application program; when the upgrading fails, the multi-loading unit forcibly jumps from the first interrupt vector table to the second interrupt vector table of the basic program to reload the basic program, and an online upgrading data frame is written into the configuration memory again. According to the invention, the re-upgrading of the application program after upgrading failure is realized based on the multiple loading units, so that the reliability and safety of the system upgrading are ensured.

Owner:HUBEI SANJIANG SPACE XIANFENG ELECTRONICS&INFORMATION CO LTD