Interrupt-processing system for shortening interrupt latency in microprocessor

a technology of interrupt latency and interrupt processing, which is applied in the field of data processing system, can solve the problems of restricted interrupt service efficiency of the cpu, and achieve the effect of reducing interrupt latency and increasing interrupt service efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

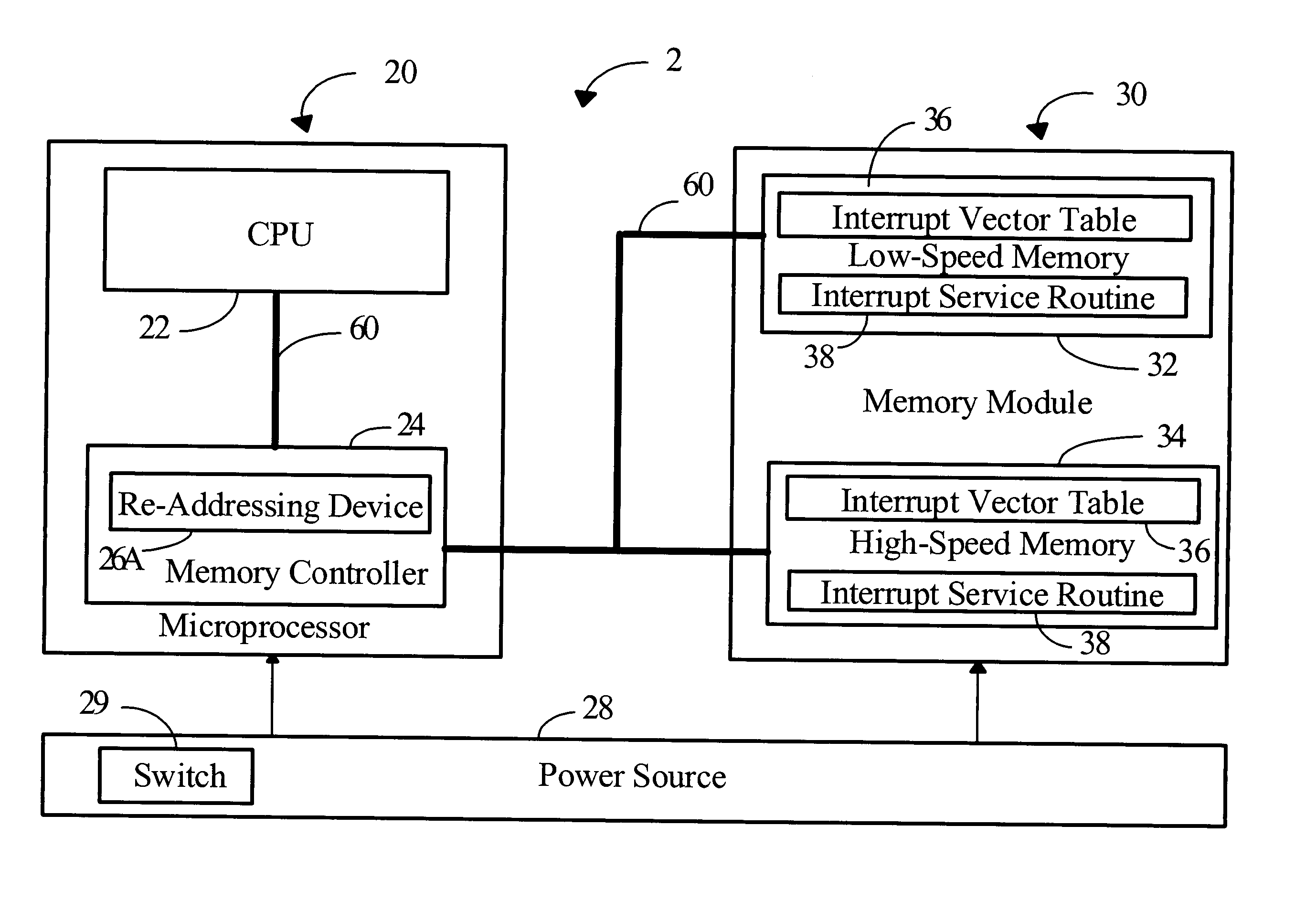

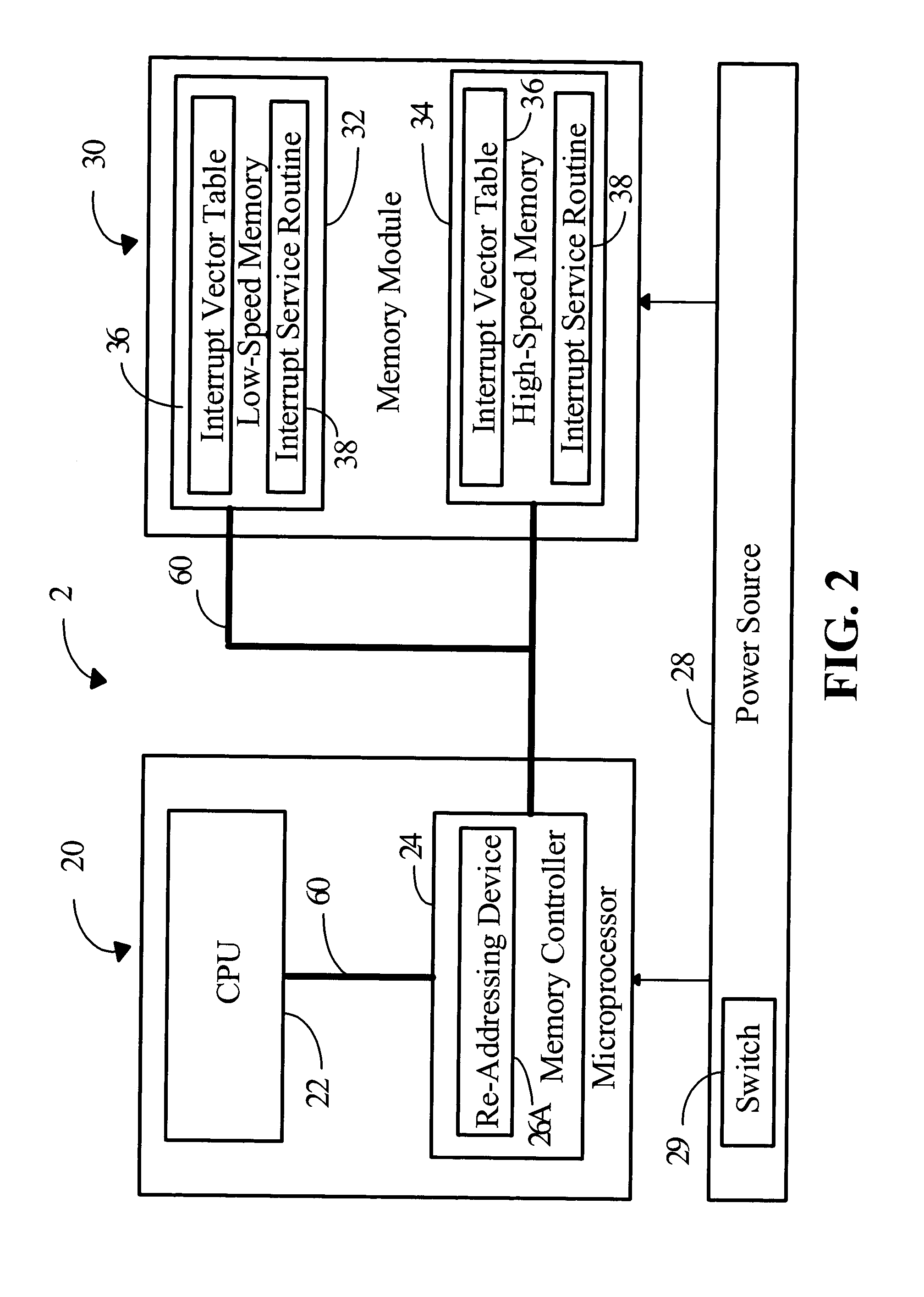

[0029] Referring to FIG. 2, FIG. 2 is a function block diagram of a data processing system 2 according to the present invention. The data processing system 2 comprises a set of memory modules 30 for storing program instructions and data, a microprocessor 20, a power source 28 for providing electrical power to the data processing system 2, and a bus 60.

[0030] The set of memory modules 30 comprise a low-speed memory 32 and a high-speed memory 34. Both the low-speed memory 32 and the high-speed memory 34 store an interrupt vector table 36 individually for recording at least one entry instruction of an interrupt service routine 38. In this embodiment, there is one interrupt service routine 38. The entry instruction is the first instruction of the whole interrupt service routine 38.

[0031] The power source 28 comprises a switch 29. When the power source 28 is shut down, program instructions and data stored in the high-speed memory 34 are lost; however, program instructions and data stor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More