Patents

Literature

51 results about "Serial presence detect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

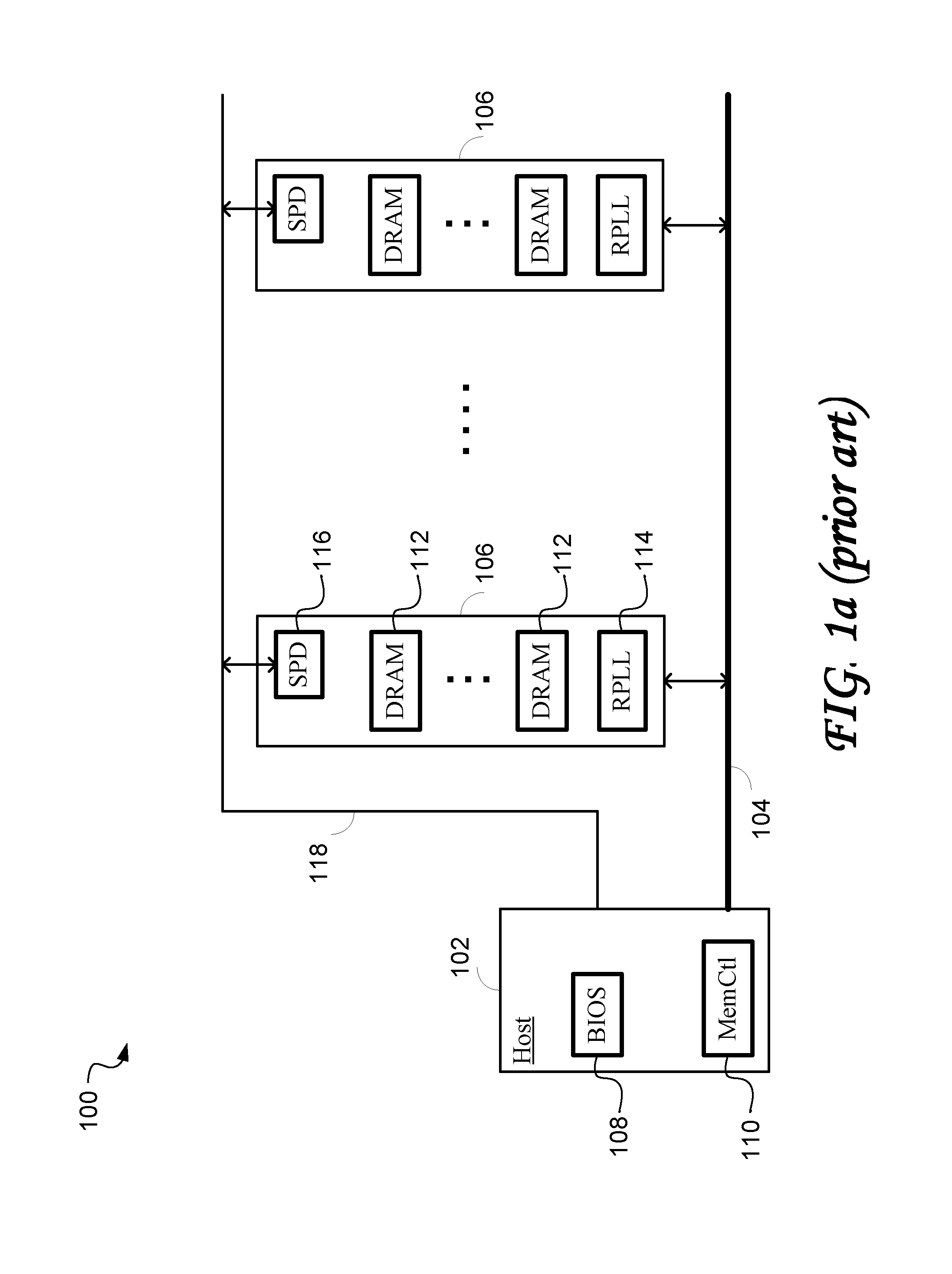

In computing, serial presence detect (SPD) is a standardized way to automatically access information about a memory module. Earlier 72-pin SIMMs included five pins that provided five bits of parallel presence detect (PPD) data, but the 168-pin DIMM standard changed to a serial presence detect to encode much more information.

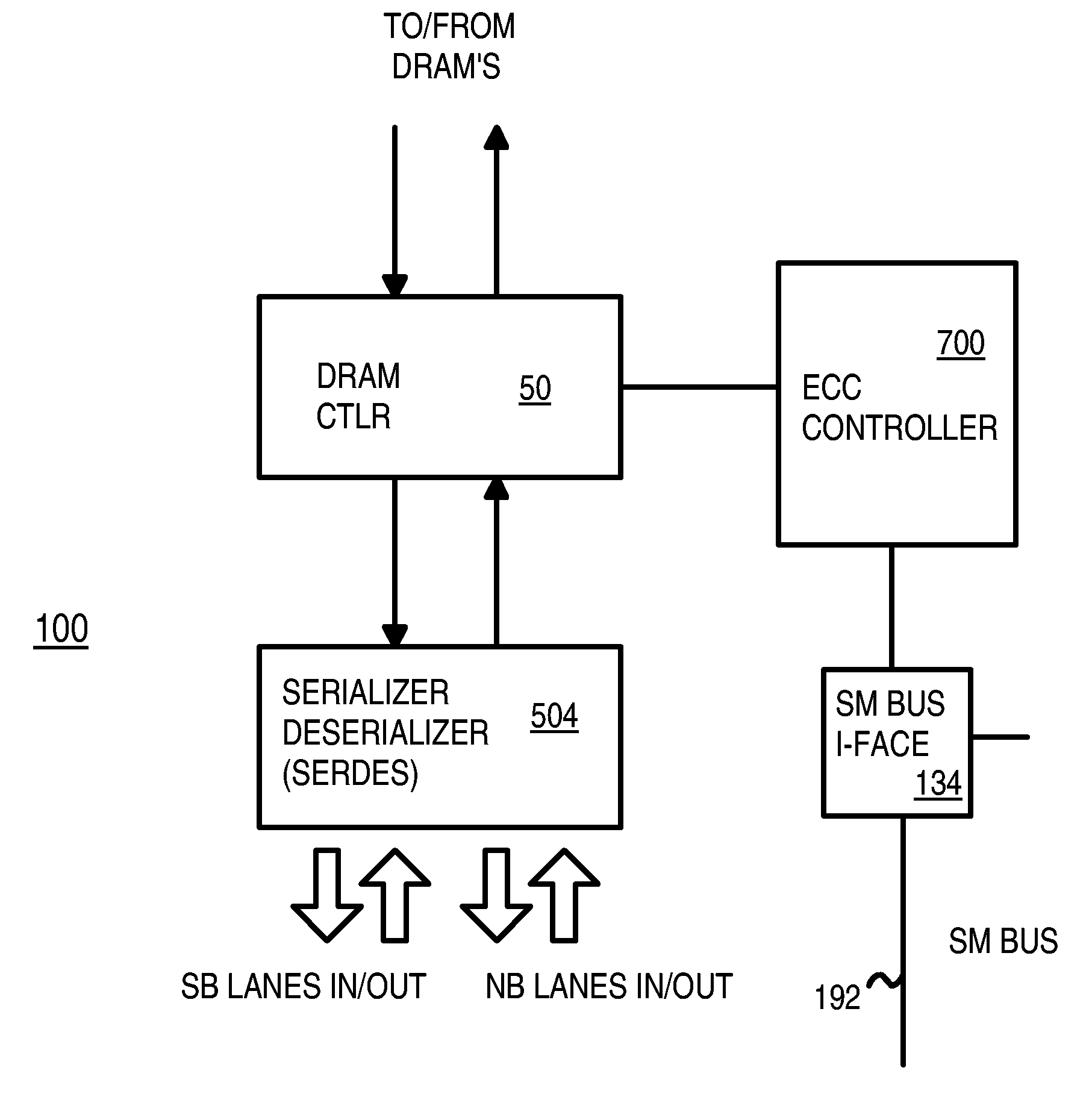

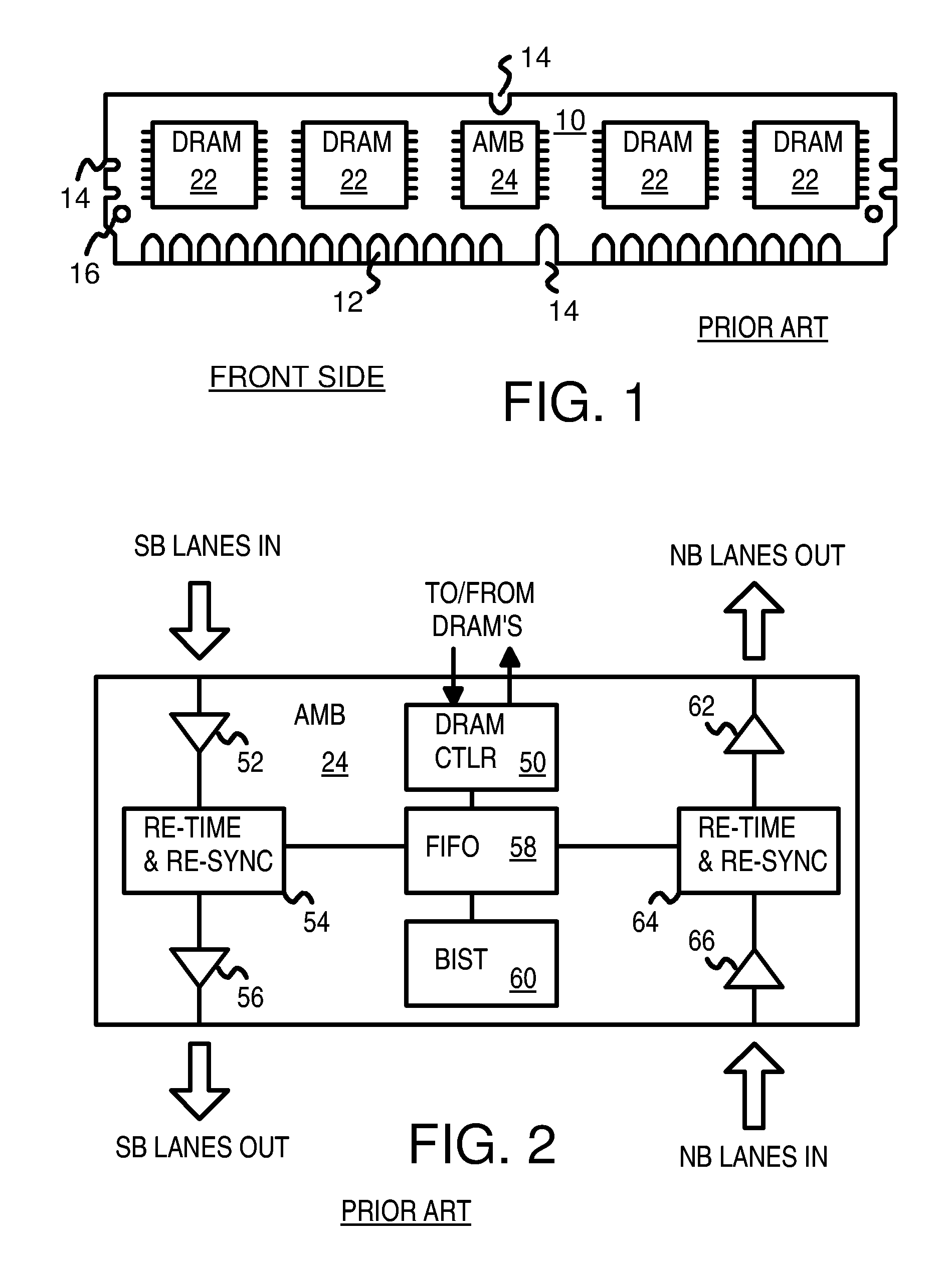

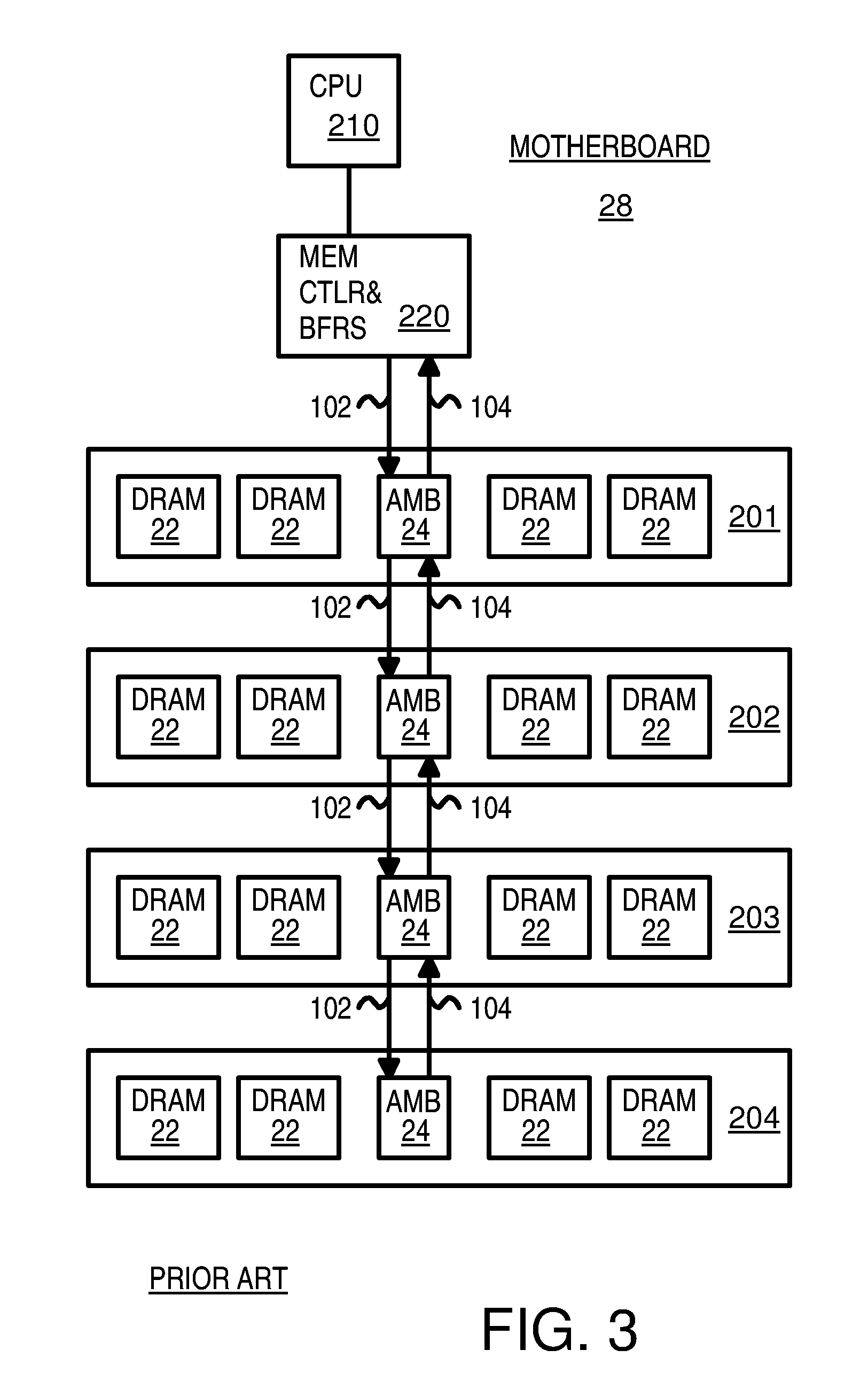

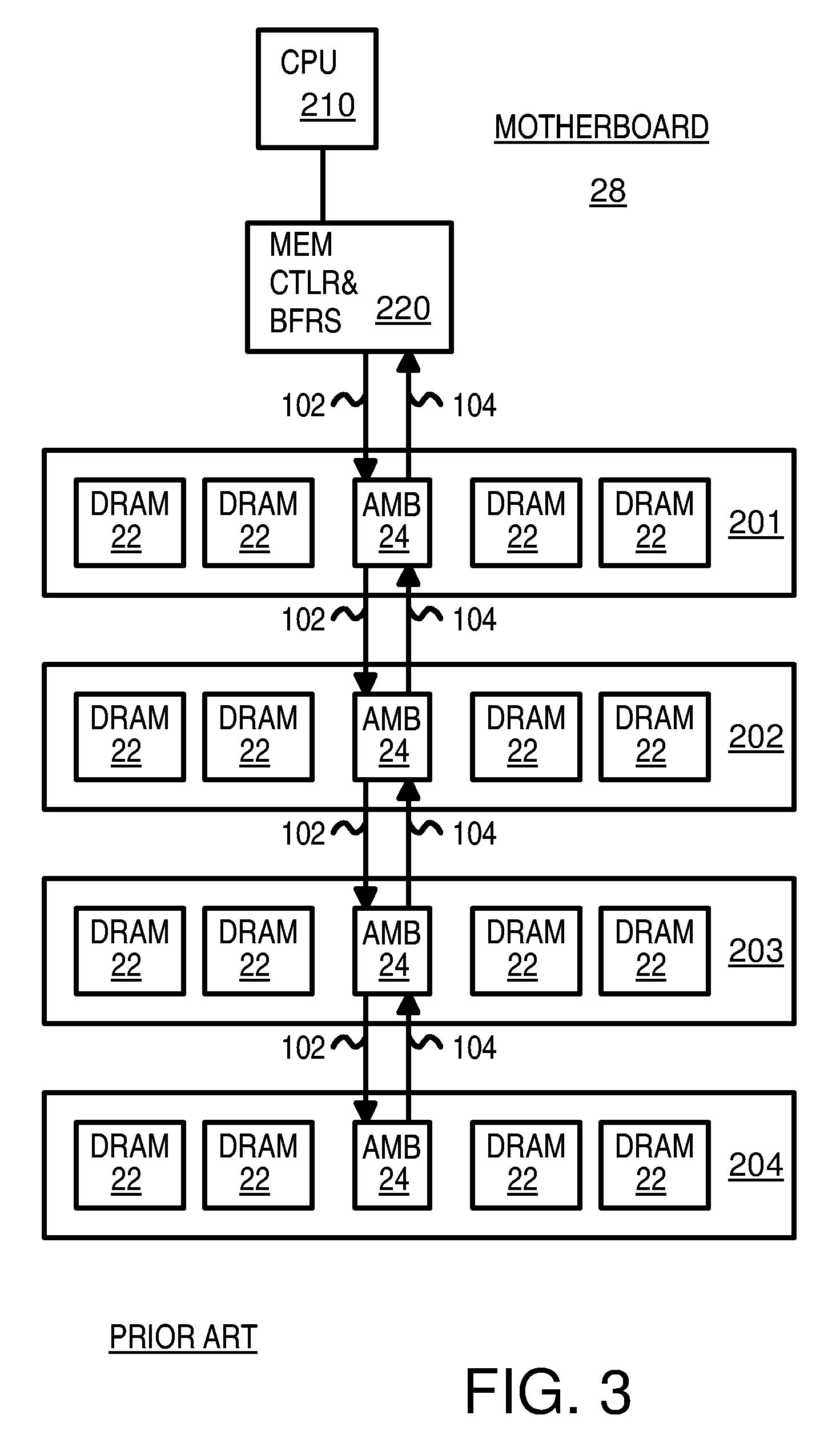

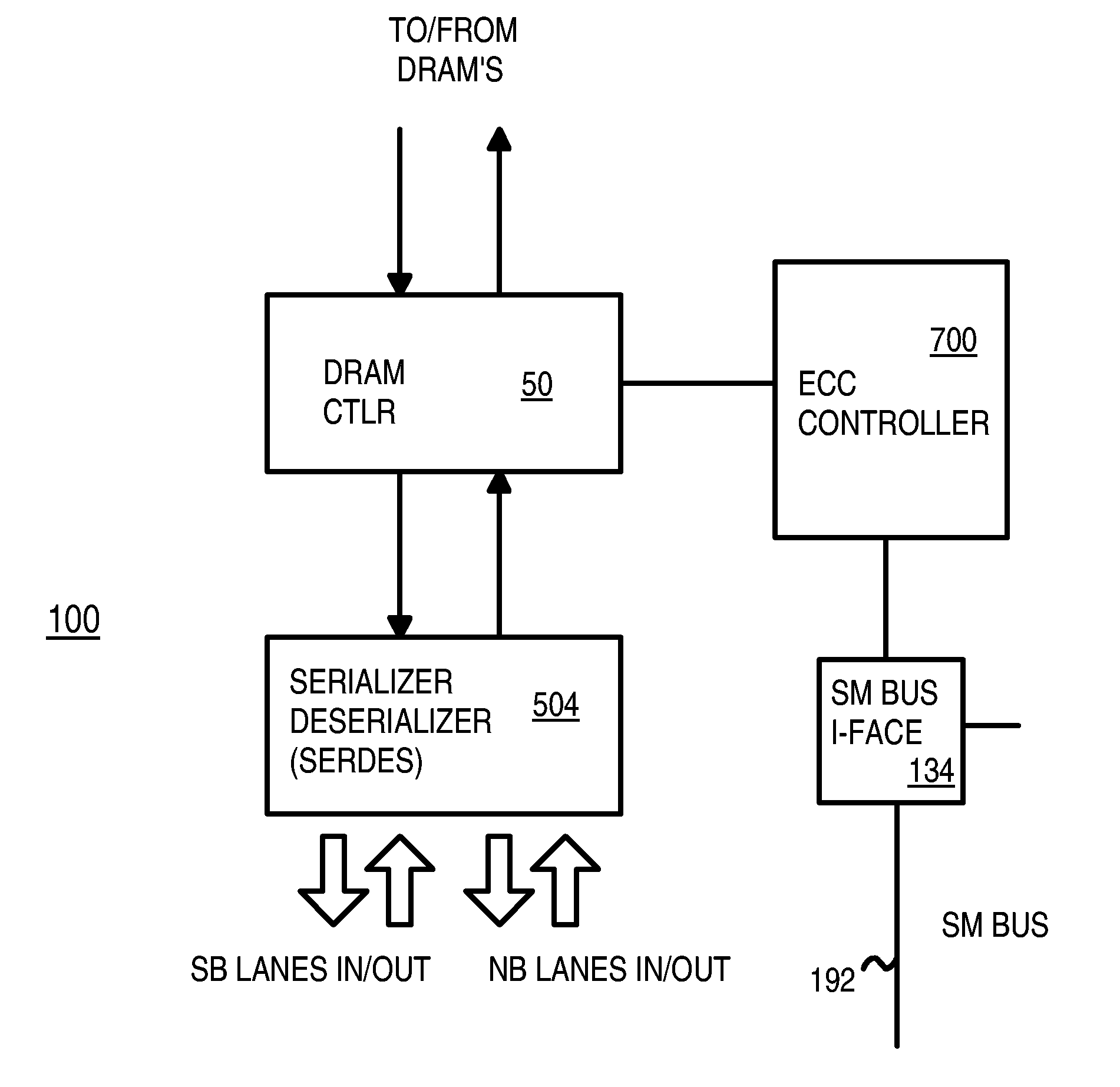

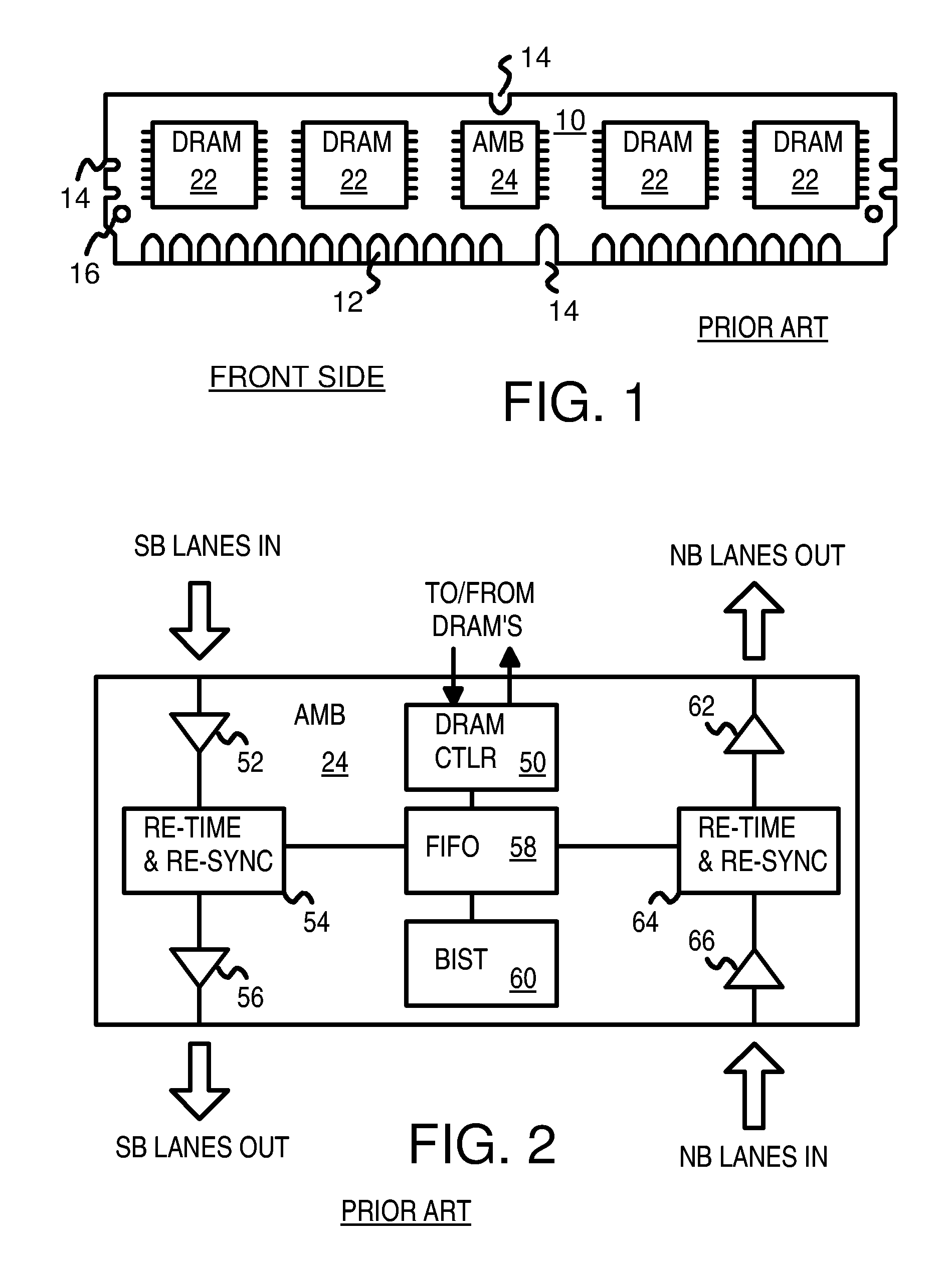

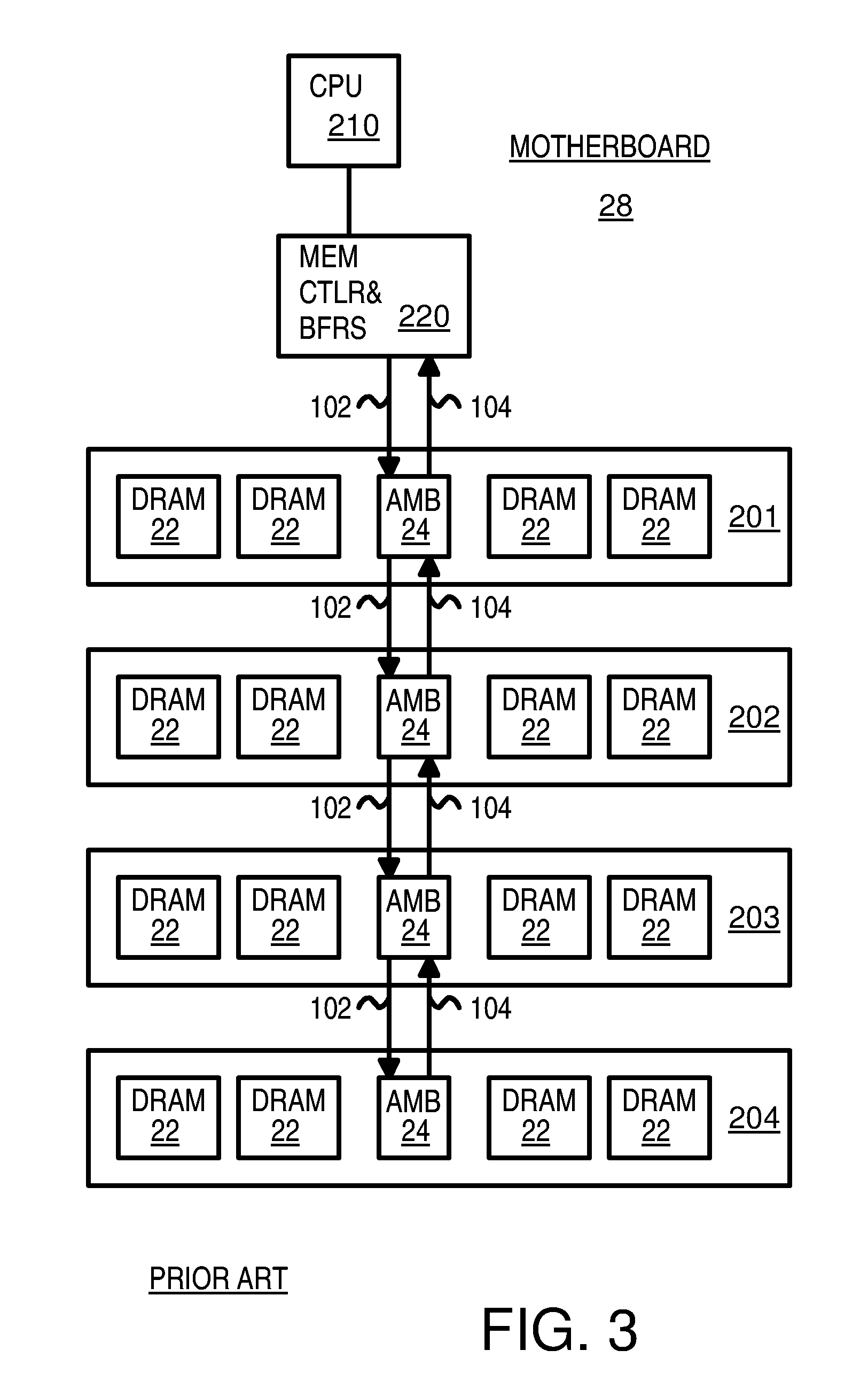

Fully-Buffered Memory-Module with Error-Correction Code (ECC) Controller in Serializing Advanced-Memory Buffer (AMB) that is transparent to Motherboard Memory Controller

ActiveUS20080022186A1Error detection/correctionStatic storageProgrammable read-only memoryError correcting

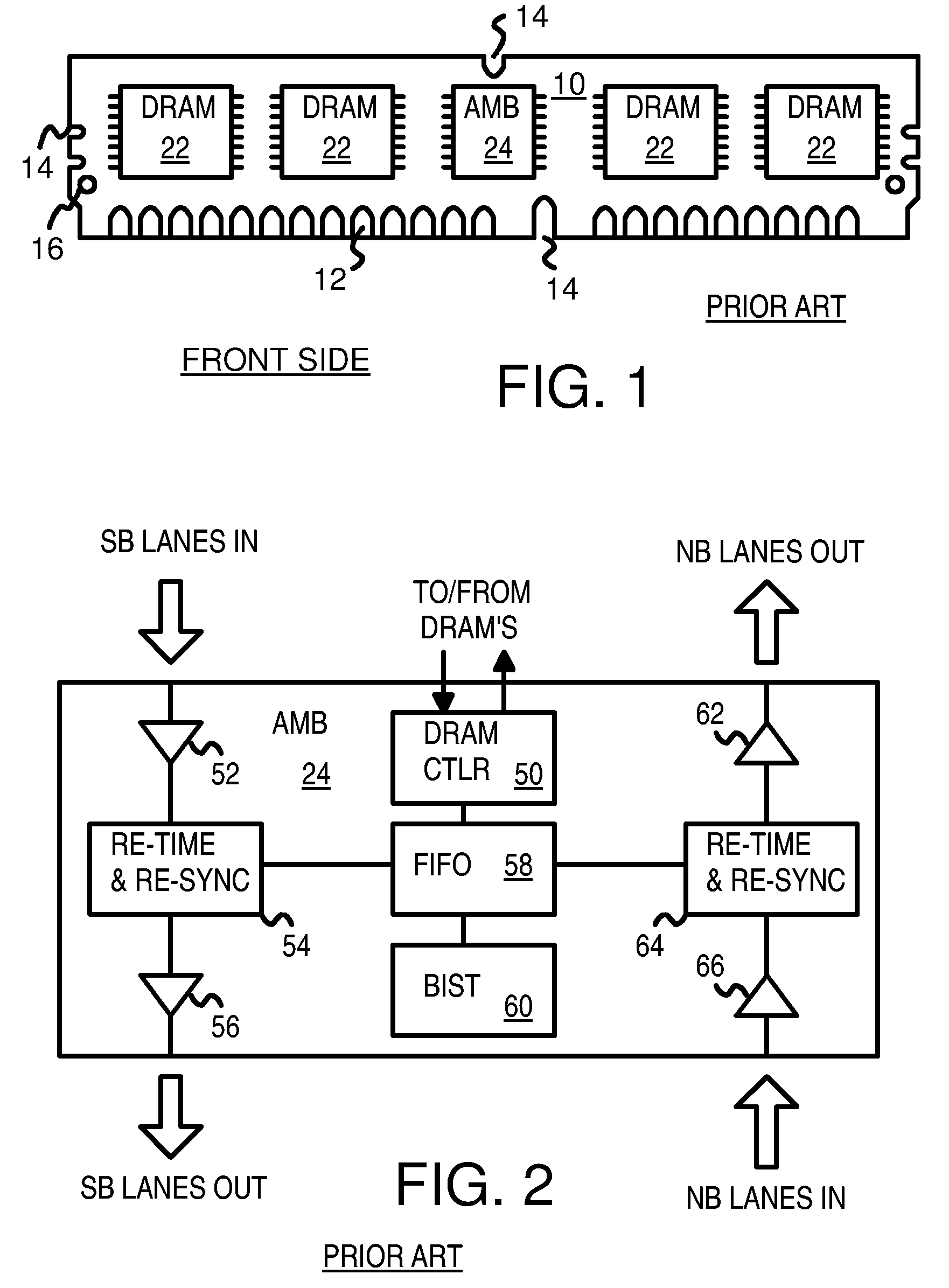

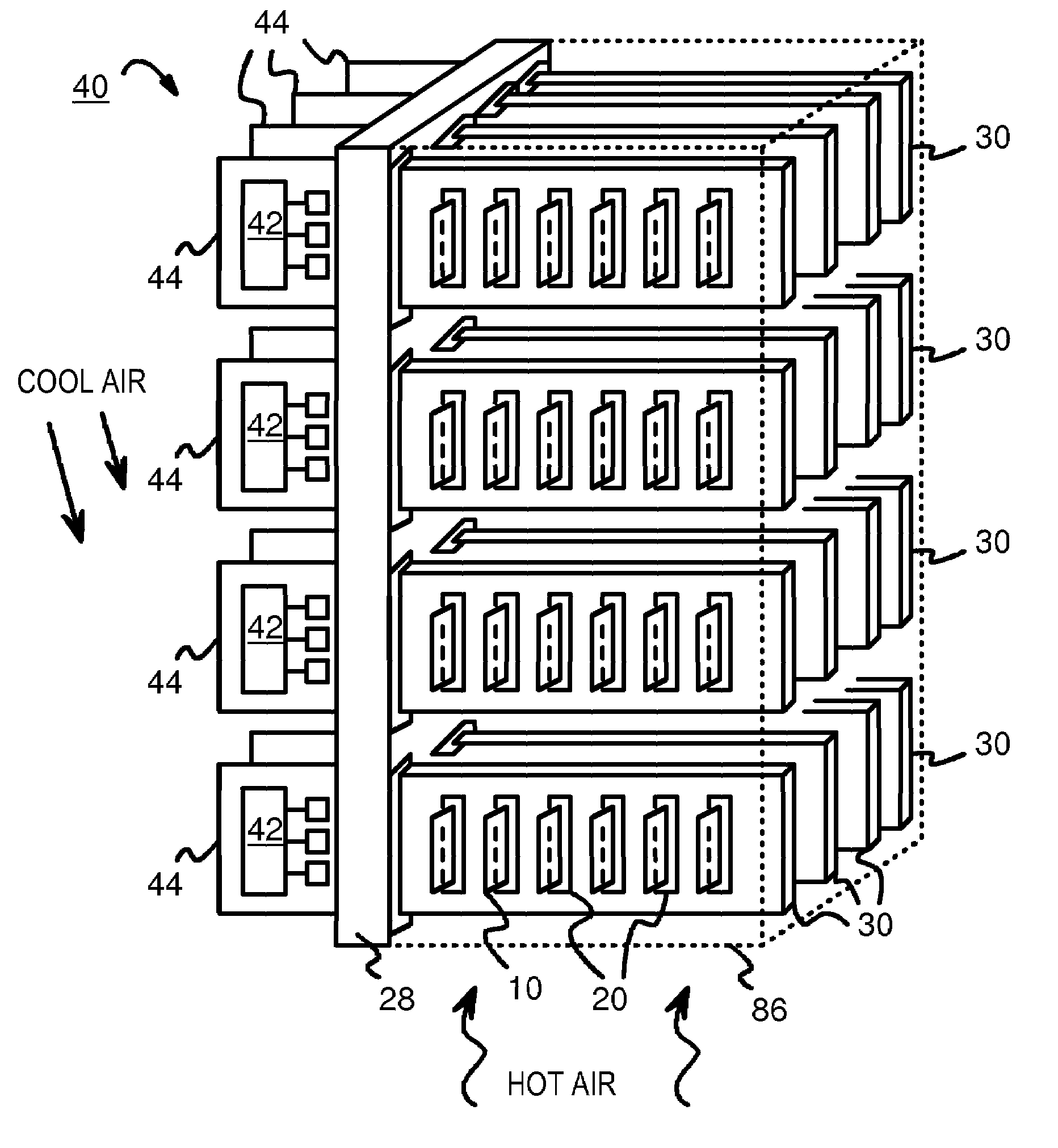

An error-correcting fully-buffered memory module can detect and correct some errors in data read from memory chips. An error correction code ECC controller is added to the Advanced Memory Buffer (AMB) on the memory module that fully buffers memory requests sent as serial packets. The error correction controller generates ECC bits for write data, and both the ECC bits and the write data are written to the memory chips by a DRAM controller in the AMB. During reads, an ECC checker generates a syndrome and can activate an error corrector to correct data or signal a non-correctable error. The corrected data is formed into serial packets sent back to the motherboard by the AMB. Configuration data for the ECC controller could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to error-correction configuration registers on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

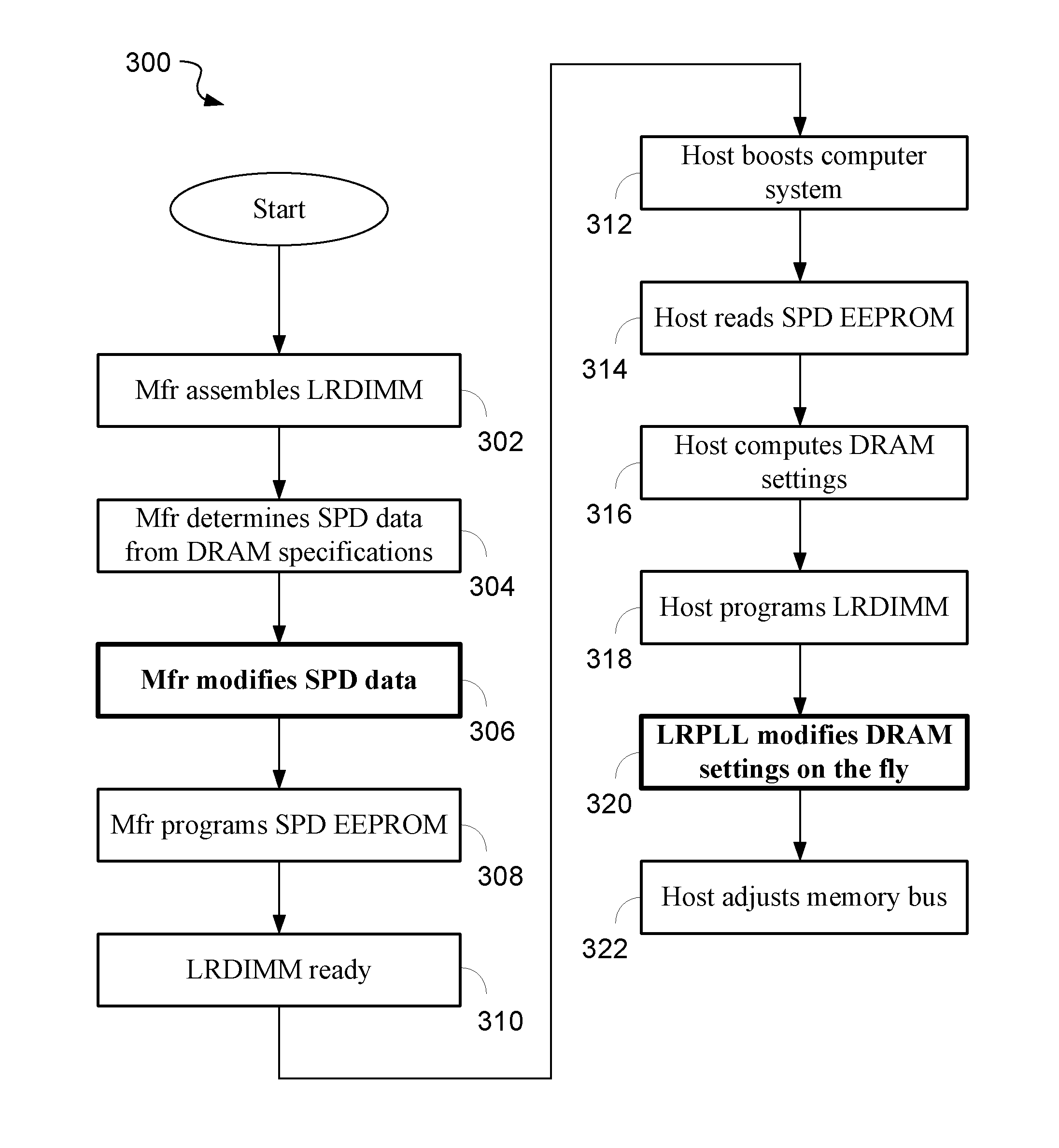

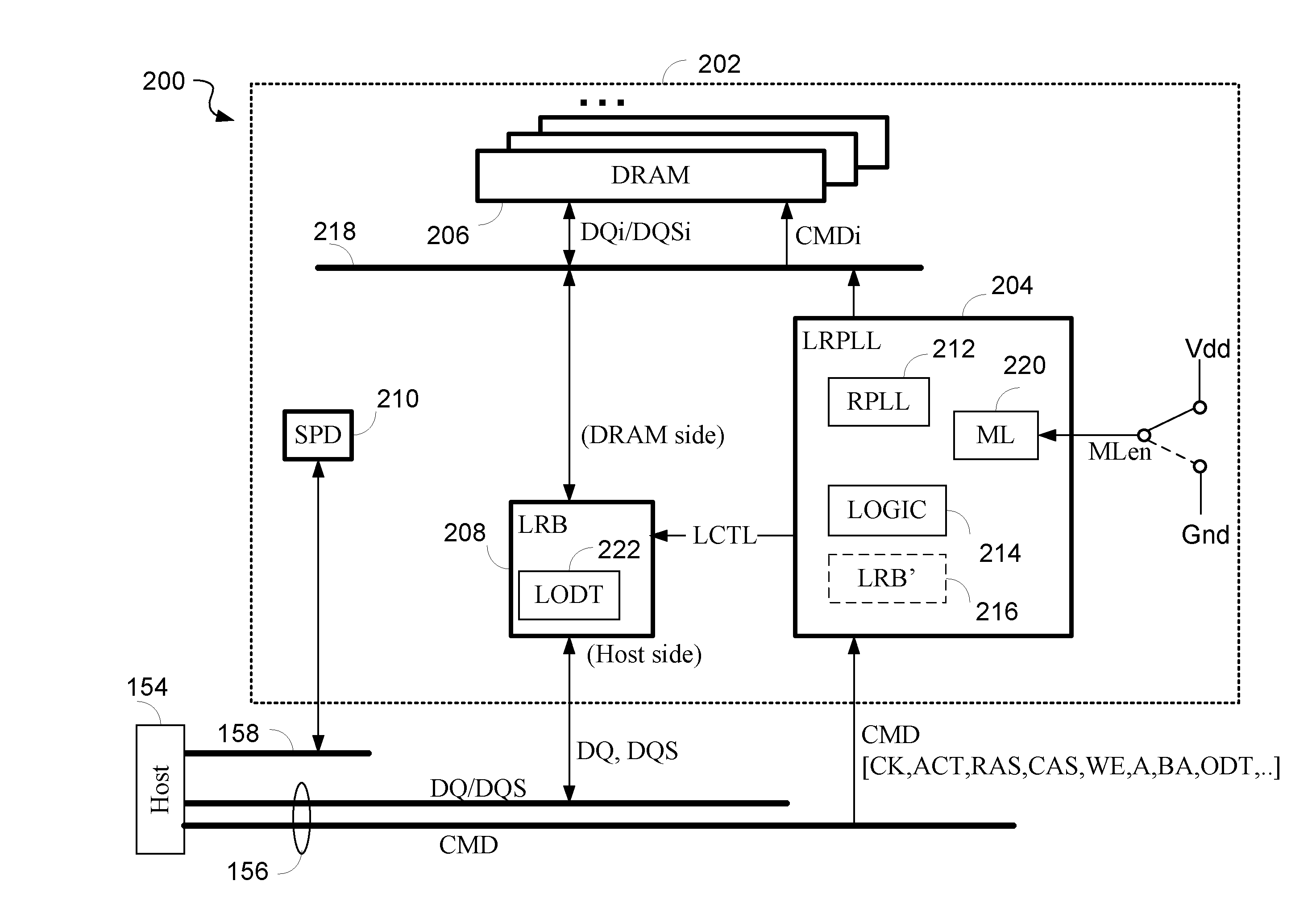

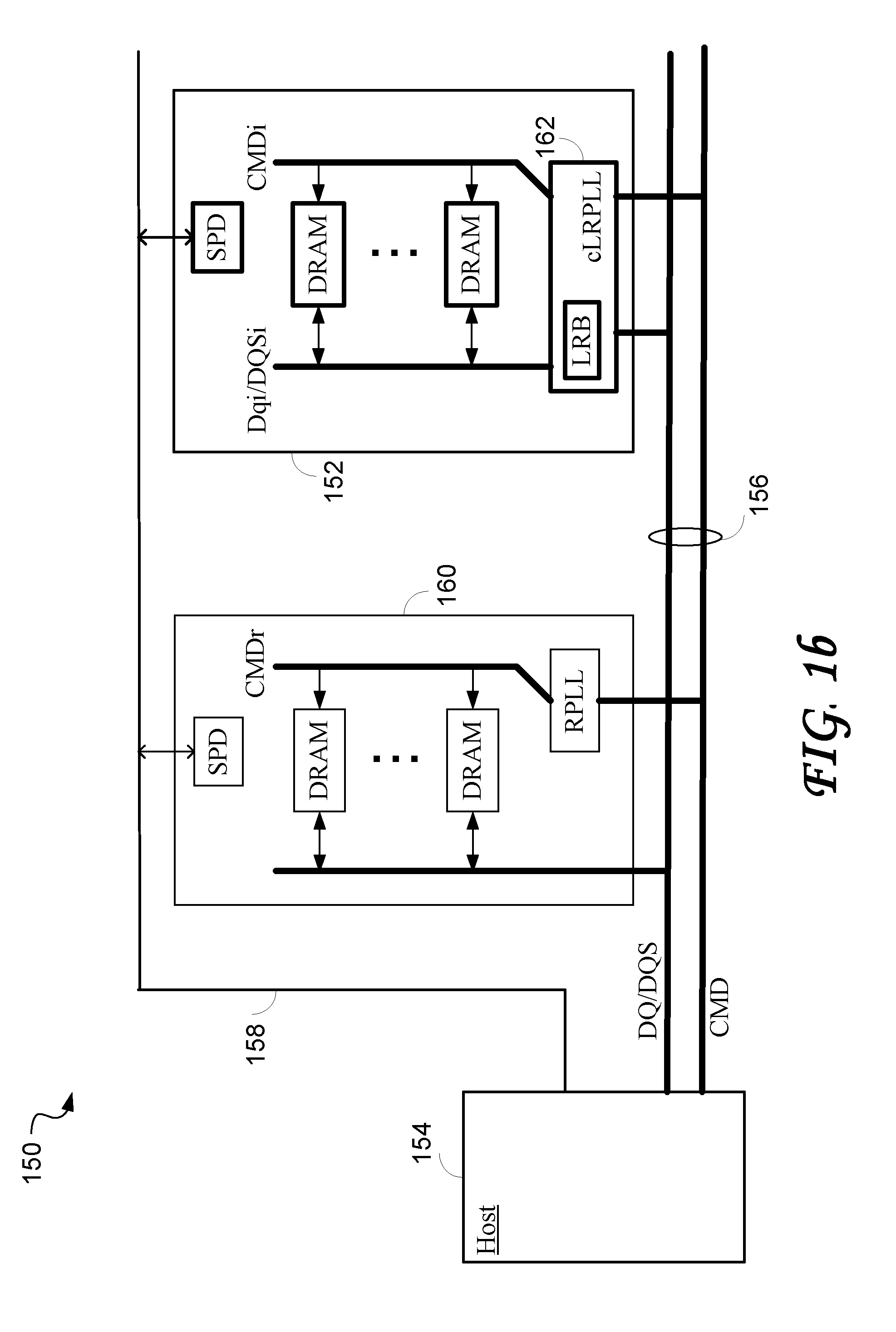

Load reduction dual in-line memory module (LRDIMM) and method for programming the same

ActiveUS8452917B2Minimize the numberIncrease power consumptionDigital computer detailsDigital storageProcessor registerControl signal

Owner:RAMBUS INC

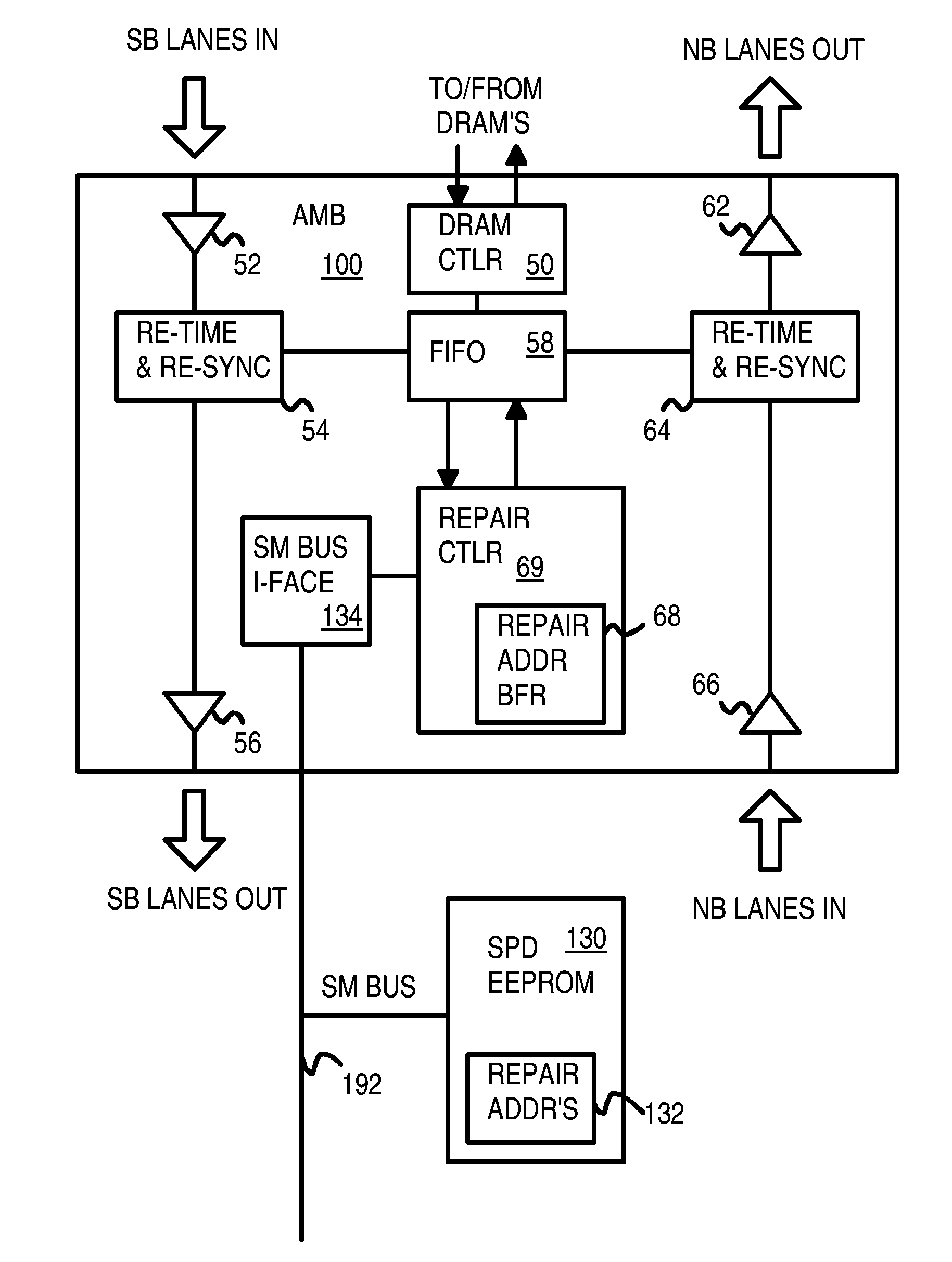

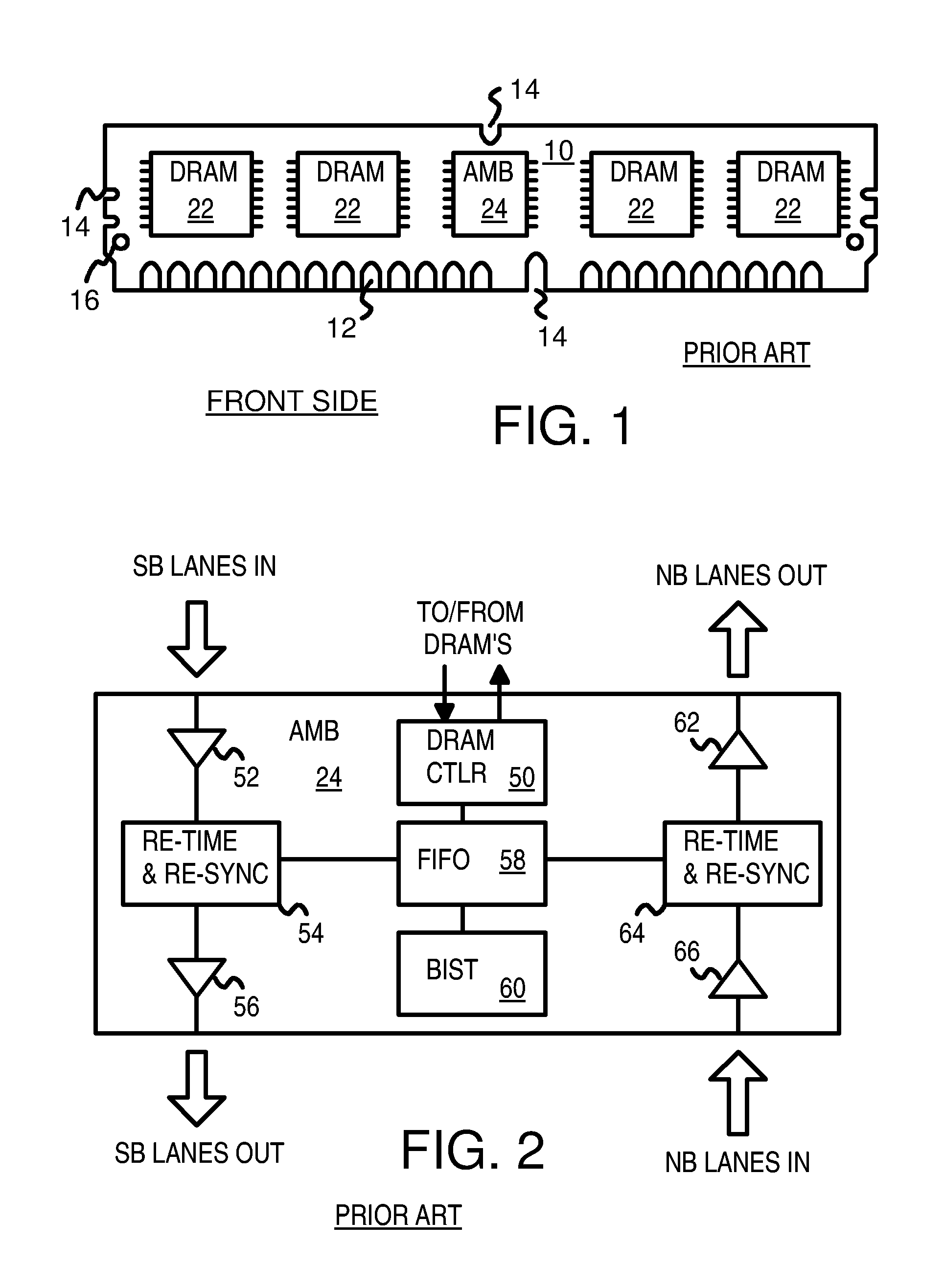

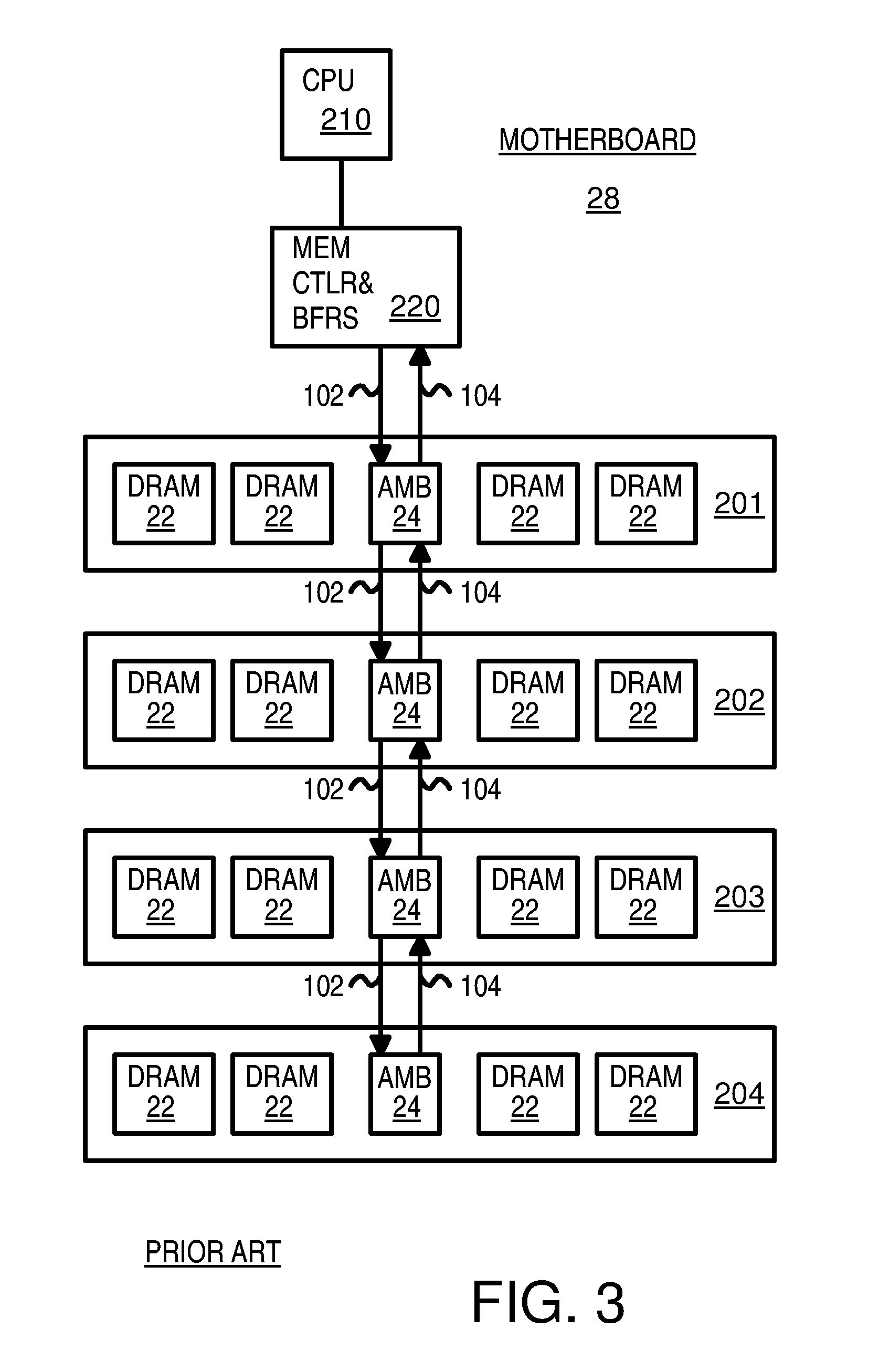

Fully-buffered memory-module with redundant memory buffer in serializing advanced-memory buffer (AMB) for repairing DRAM

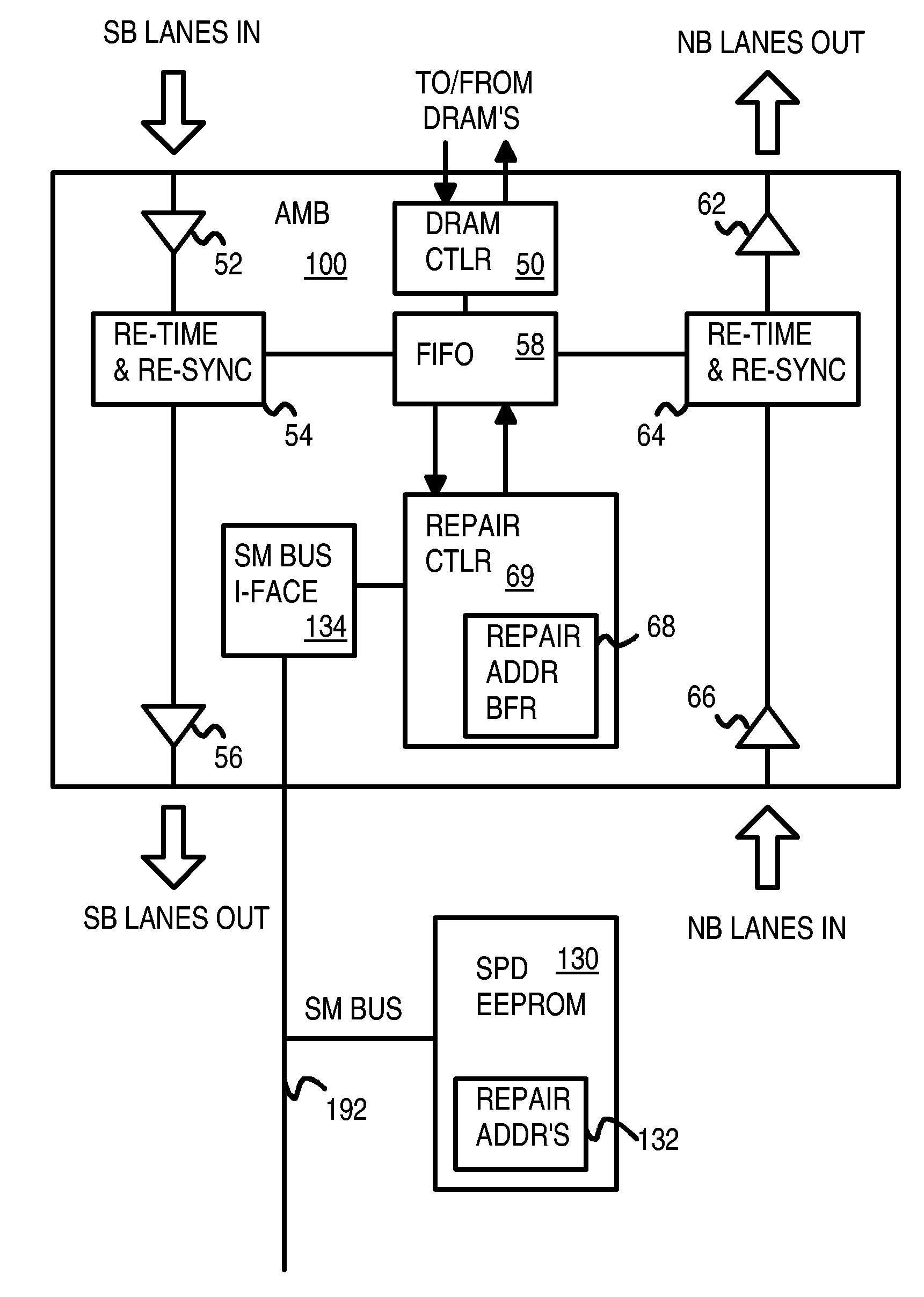

A repairing fully-buffered memory module can have memory chips with some defects such as single-bit errors. A repair controller is added to the Advanced Memory Buffer (AMB) on the memory module. The AMB fully buffers memory requests that are sent as serial packets over southbound lanes from a host. Memory-access addresses are extracted from the serial packets by the AMB. The repair controller compares the memory-access addresses to repair addresses and diverts access from defective memory chips to a spare memory for the repair addresses. The repair addresses can be located during testing of the memory module and programmed into a repair address buffer on the AMB. The repair addresses could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to the repair address buffer on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

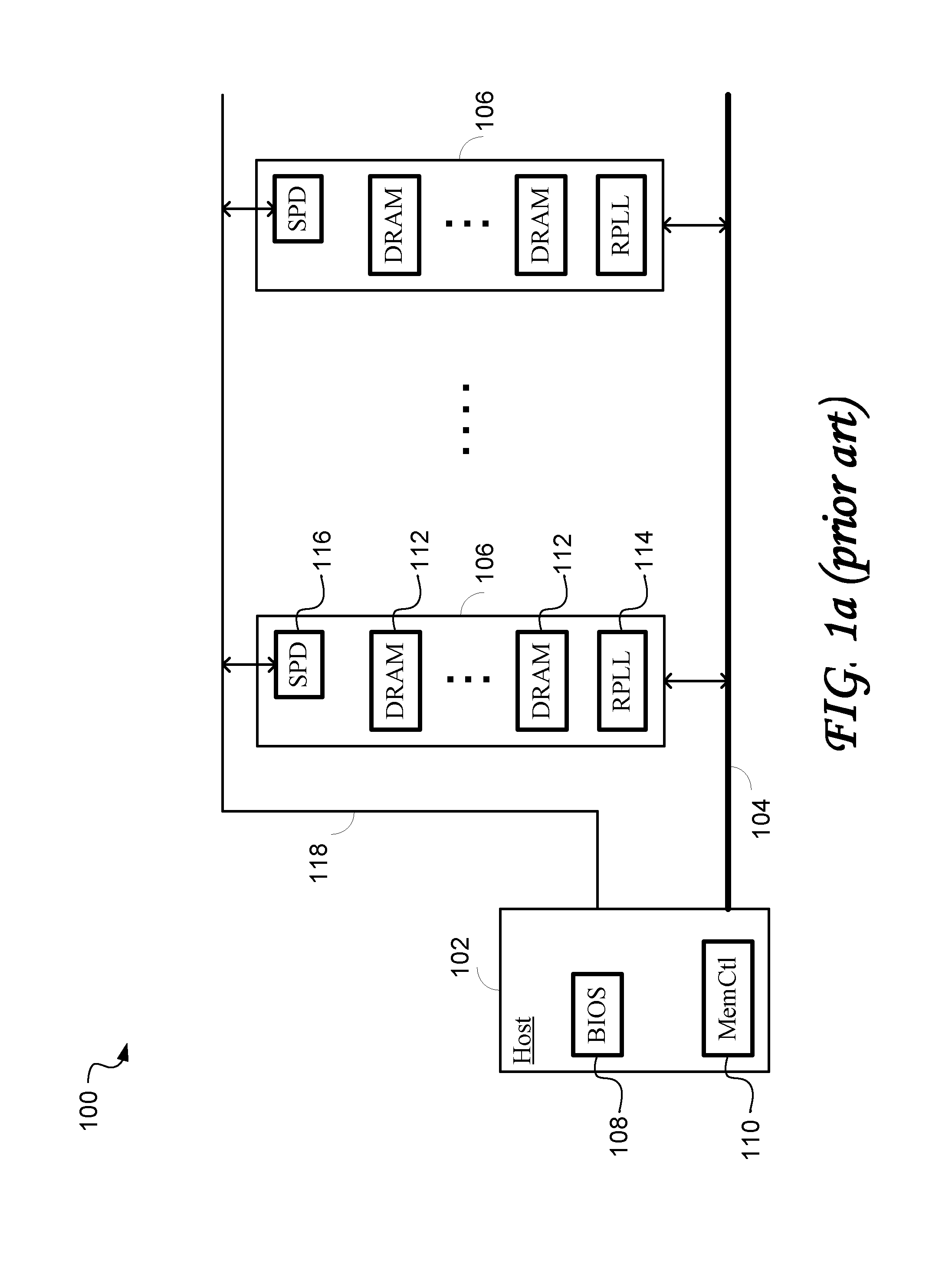

Load reduction dual in-line memory module (lrdimm) and method for programming the same

ActiveUS20100070690A1Minimize the numberIncrease power consumptionMemory adressing/allocation/relocationDigital computer detailsControl signalProcessor register

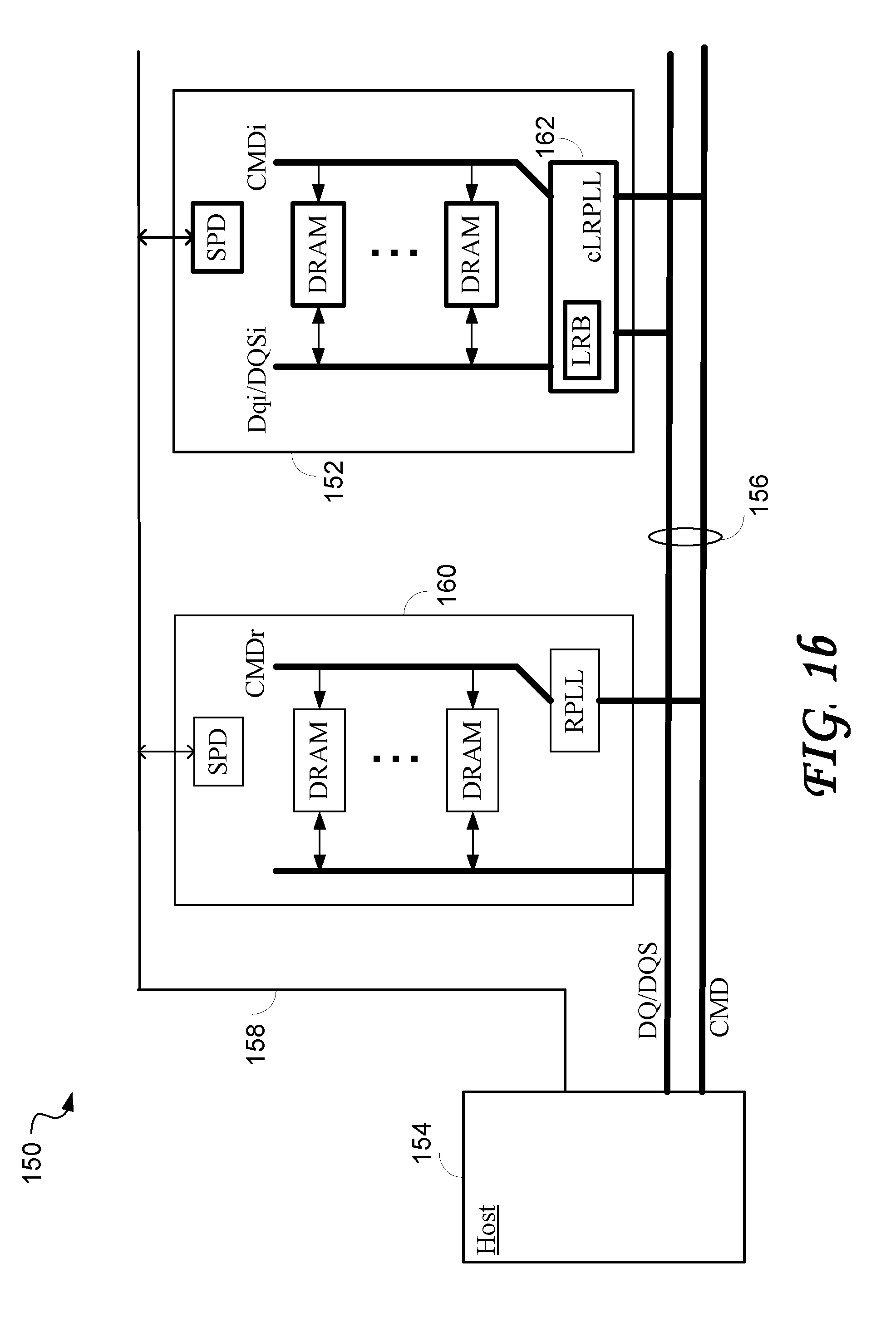

A load reduction dual in-line memory module (LRDIMM) is similar to a registered dual in-line memory module (RDIMM) in which control signals are synchronously buffered but the LRDIMM includes a load reduction buffer (LRB) in the data path as well. To make an LRDIMM which appears compatible with RDIMMs on a system memory bus, the serial presence detector (SPD) of the LRDIMM is programmed with modified latency support and minimum delay values. When the dynamic read only memory (DRAMs) devices of the LRDIMM are subsequently set up by the host at boot time based on the parameters provided by the SPD, selected latency values are modified on the fly in an enhanced register phase look loop (RPLL) device. This has the effect of compensating for the delay introduced by the LRB without violating DRAM constraints, and provides memory bus timing for a LRDIMM that is indistinguishable from that of a RDIMM.

Owner:RAMBUS INC

Fully-buffered memory-module with error-correction code (ECC) controller in serializing advanced-memory buffer (AMB) that is transparent to motherboard memory controller

ActiveUS7487428B2Error detection/correctionStatic storageProgrammable read-only memoryError correcting

An error-correcting fully-buffered memory module can detect and correct some errors in data read from memory chips. An error correction code ECC controller is added to the Advanced Memory Buffer (AMB) on the memory module that fully buffers memory requests sent as serial packets. The error correction controller generates ECC bits for write data, and both the ECC bits and the write data are written to the memory chips by a DRAM controller in the AMB. During reads, an ECC checker generates a syndrome and can activate an error corrector to correct data or signal a non-correctable error. The corrected data is formed into serial packets sent back to the motherboard by the AMB. Configuration data for the ECC controller could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to error-correction configuration registers on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

Manufacturing Method for Partially-Good Memory Modules with Defect Table in EEPROM

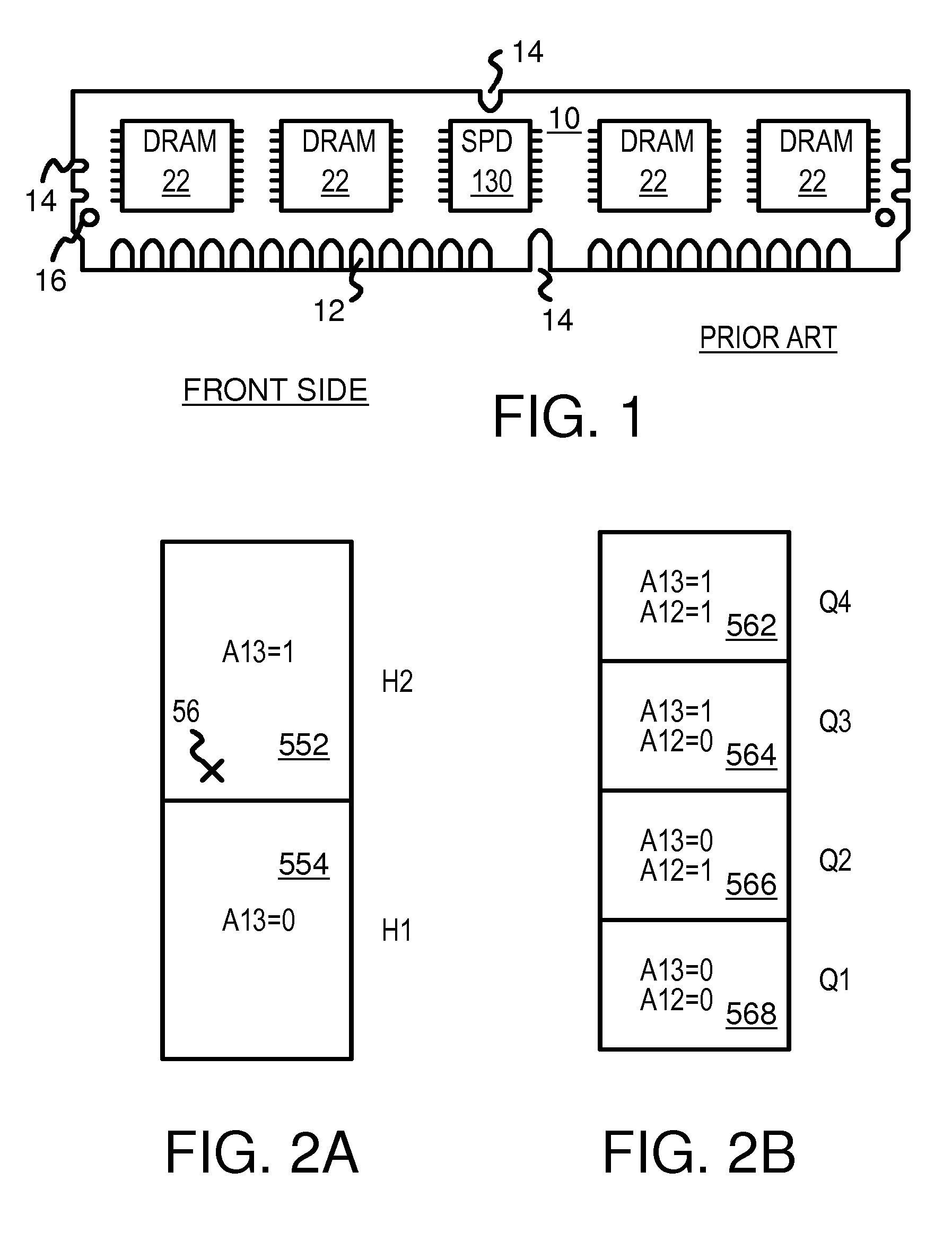

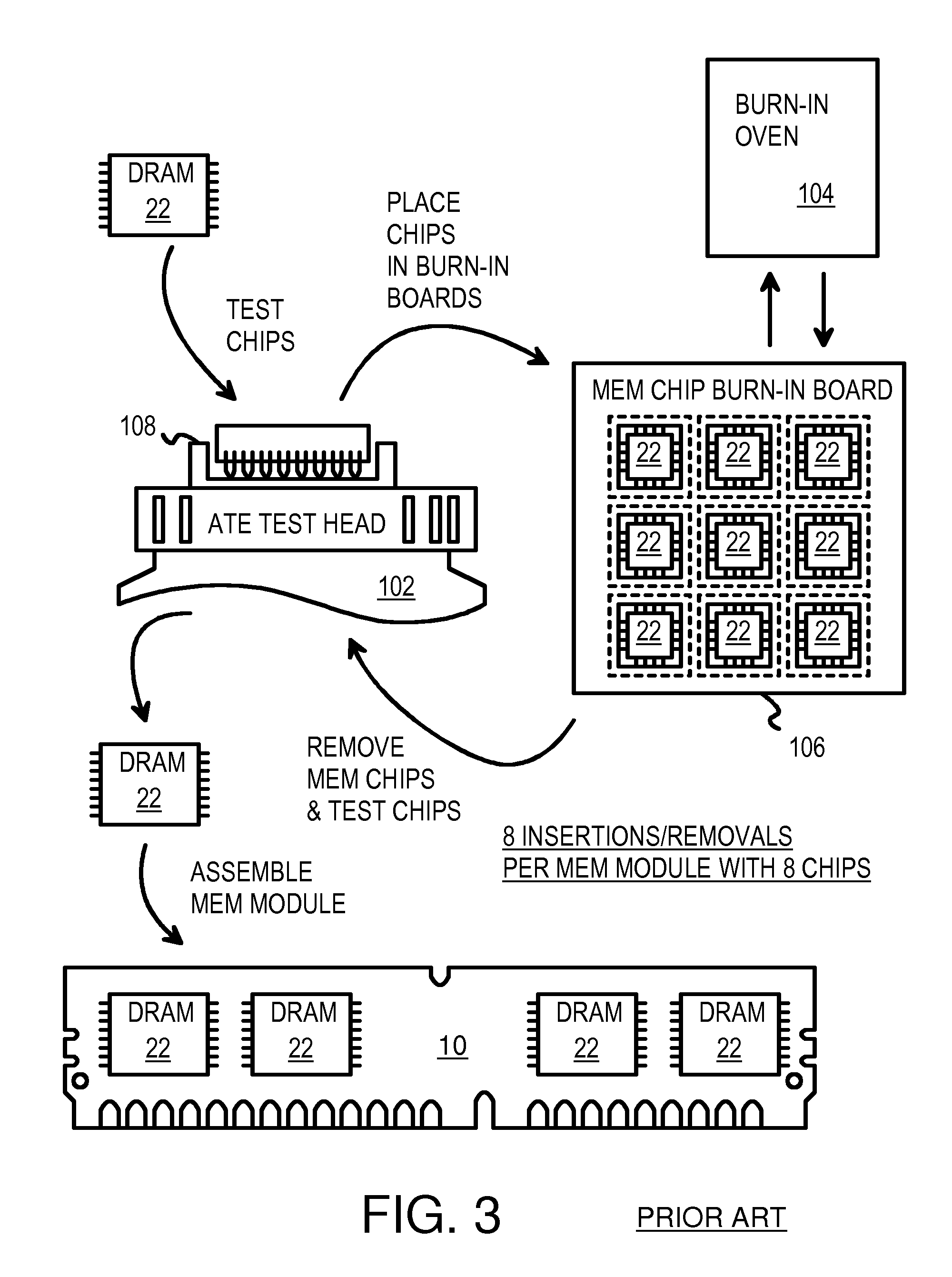

ActiveUS20090137070A1Semiconductor/solid-state device testing/measurementSolid-state devicesSerial presence detectDram chip

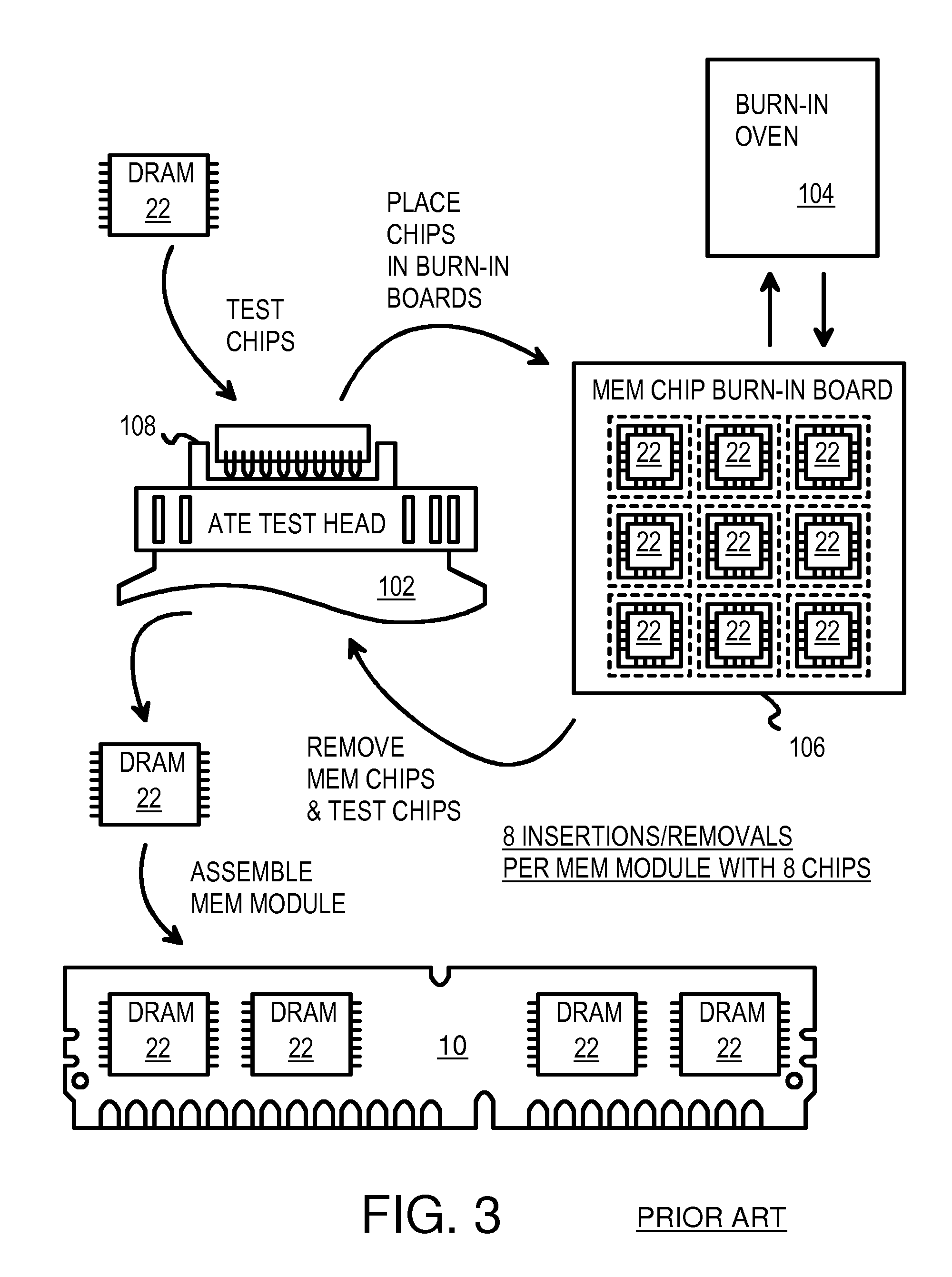

A manufacturing method makes memory modules from partially-good DRAM chips soldered to its substrate. The partially-good DRAM chips have a number of defective memory cells that is below a test threshold, such as 10%. Packaged DRAM chips are optionally pre-screened and considered to pass when the number of defects found is less than the test threshold. A defect table is created during testing and written to a serial-presence-detect electrically-erasable read-only memory (SPD-EEPROM) on the memory module. The memory module is finally tested on a target-system tester that reads the defect table during booting, and redirects memory access to defective memory locations identified by the defect table. The memory modules may be burned in or tested at various temperatures and voltages to increase reliability.

Owner:KINGSTON DIGITAL CO LTD

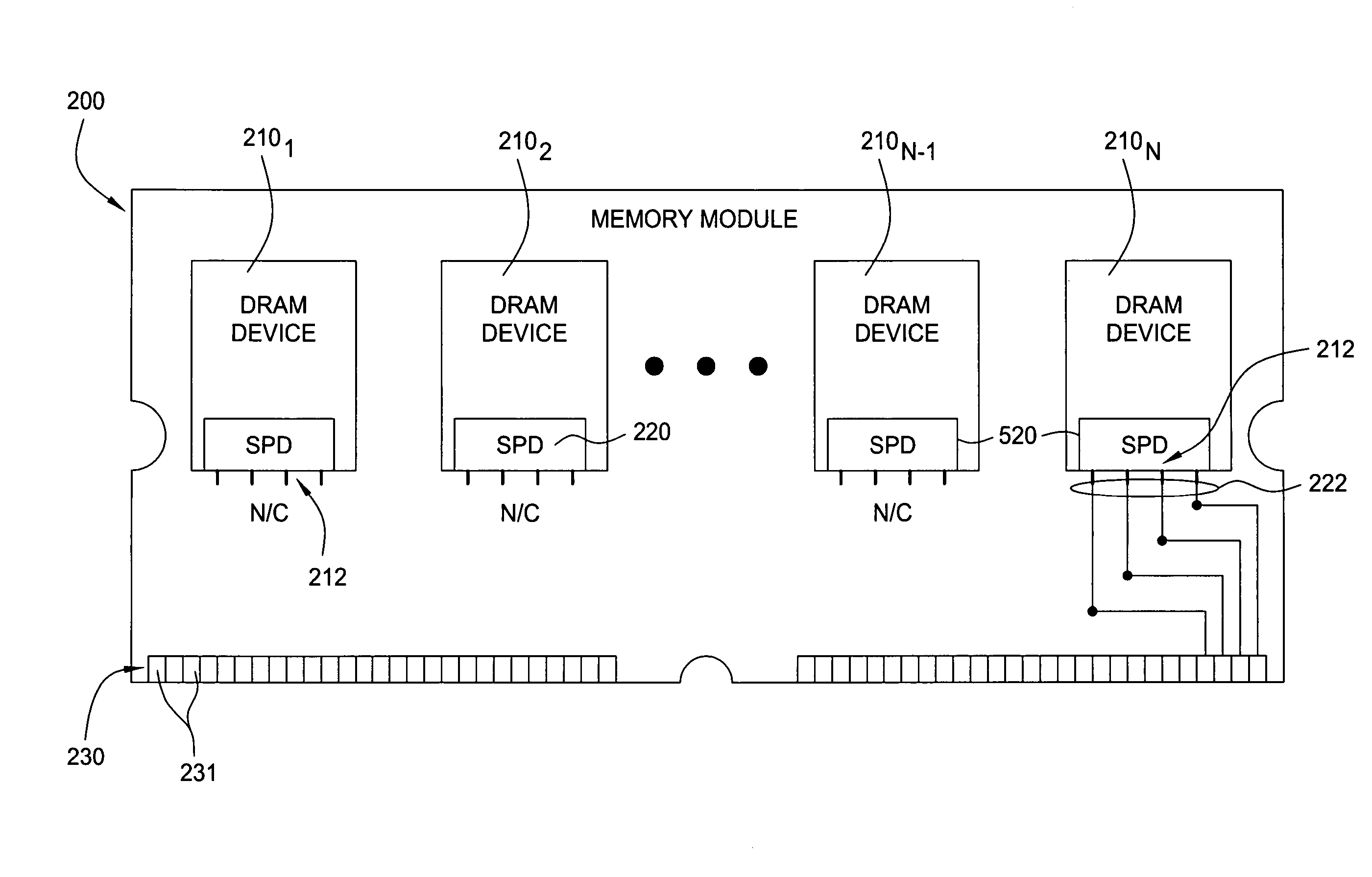

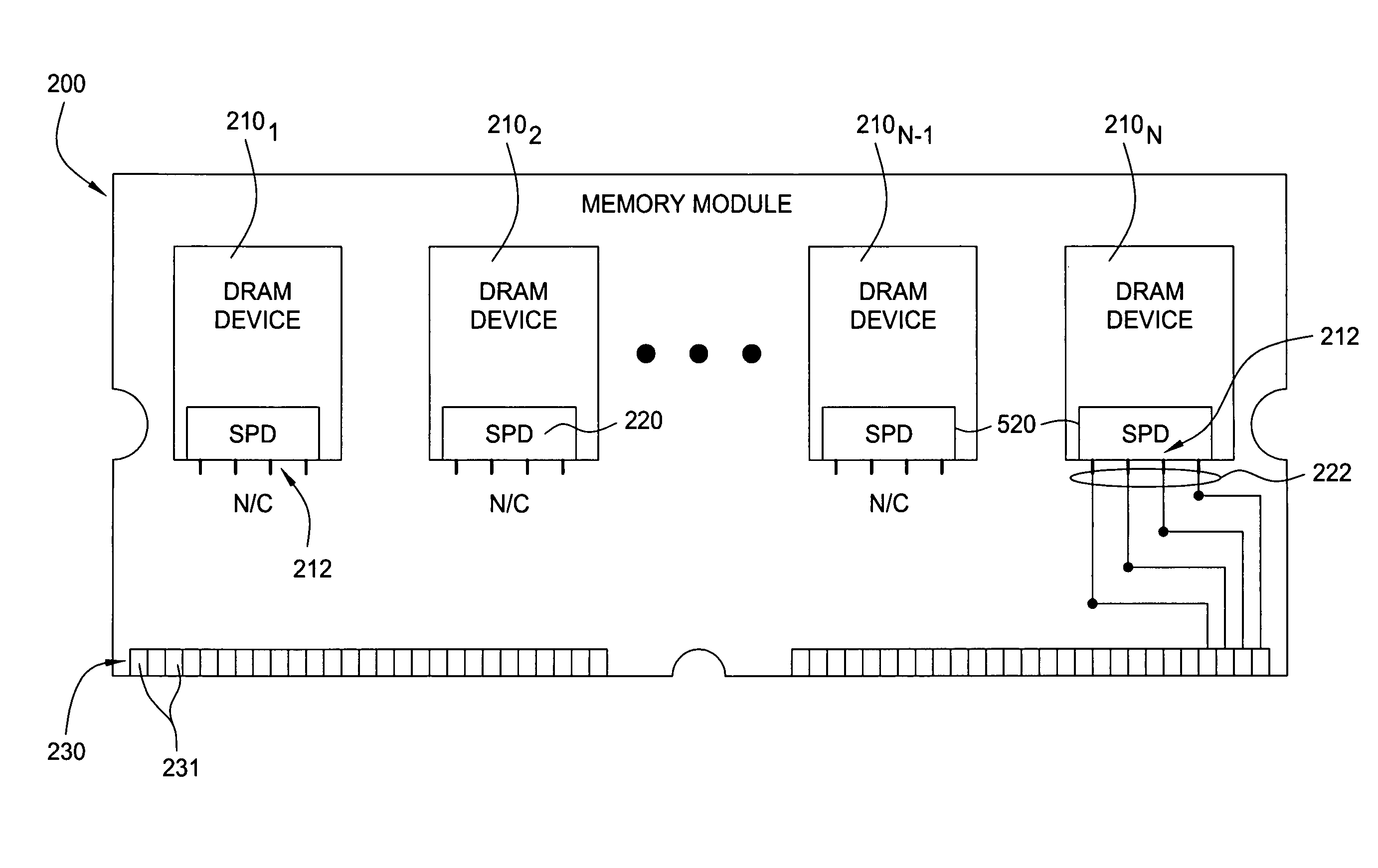

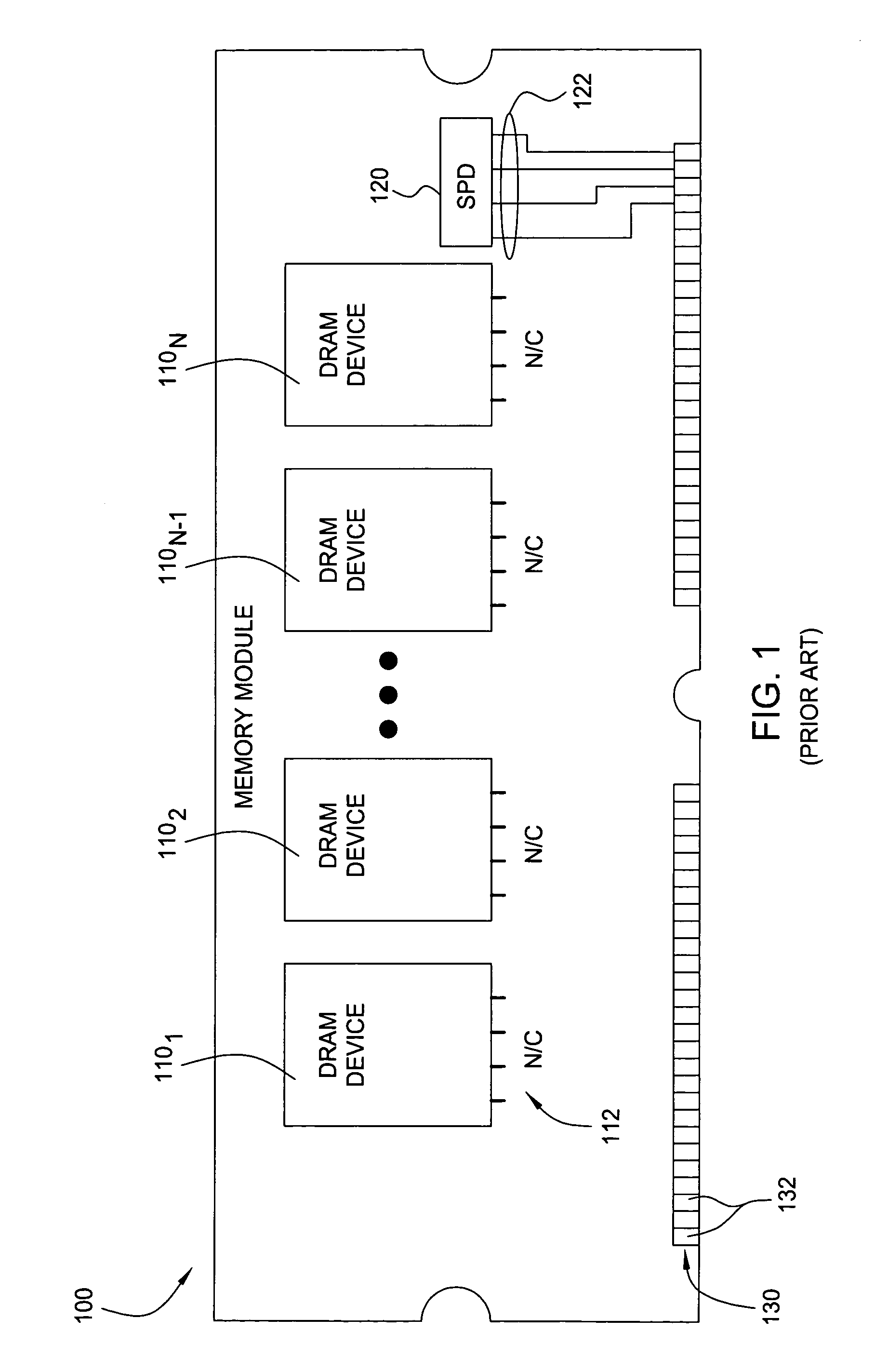

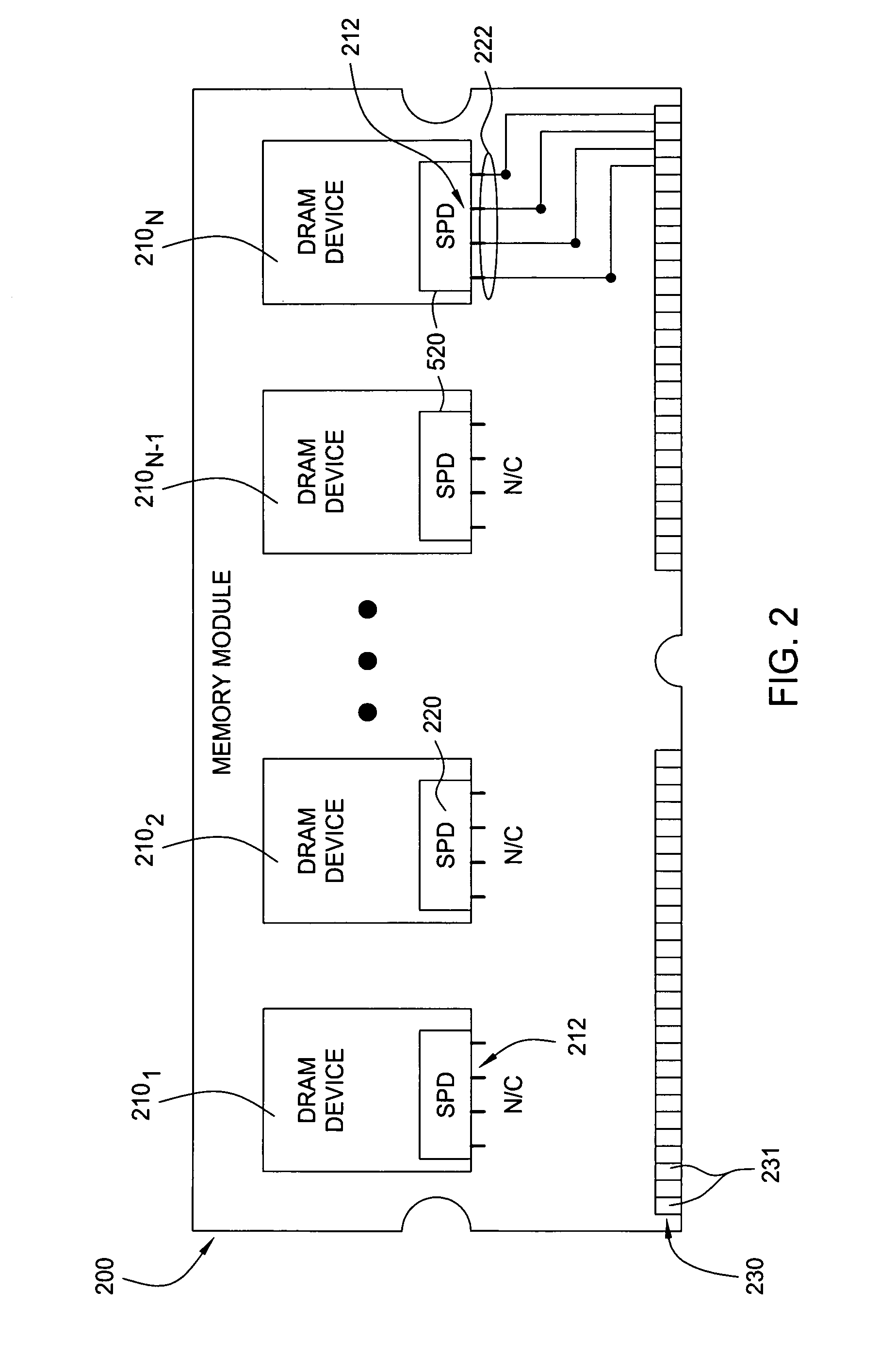

Serial presence detect functionality on memory component

InactiveUS20070058470A1Multiplex system selection arrangementsFinal product manufactureComputer hardwareSerial presence detect

Methods and apparatus for accessing serial presence detect data are provided. For some embodiments, serial presence detect logic is incorporated in memory devices, eliminating the need for a separate serial presence detect component.

Owner:POLARIS INNOVATIONS

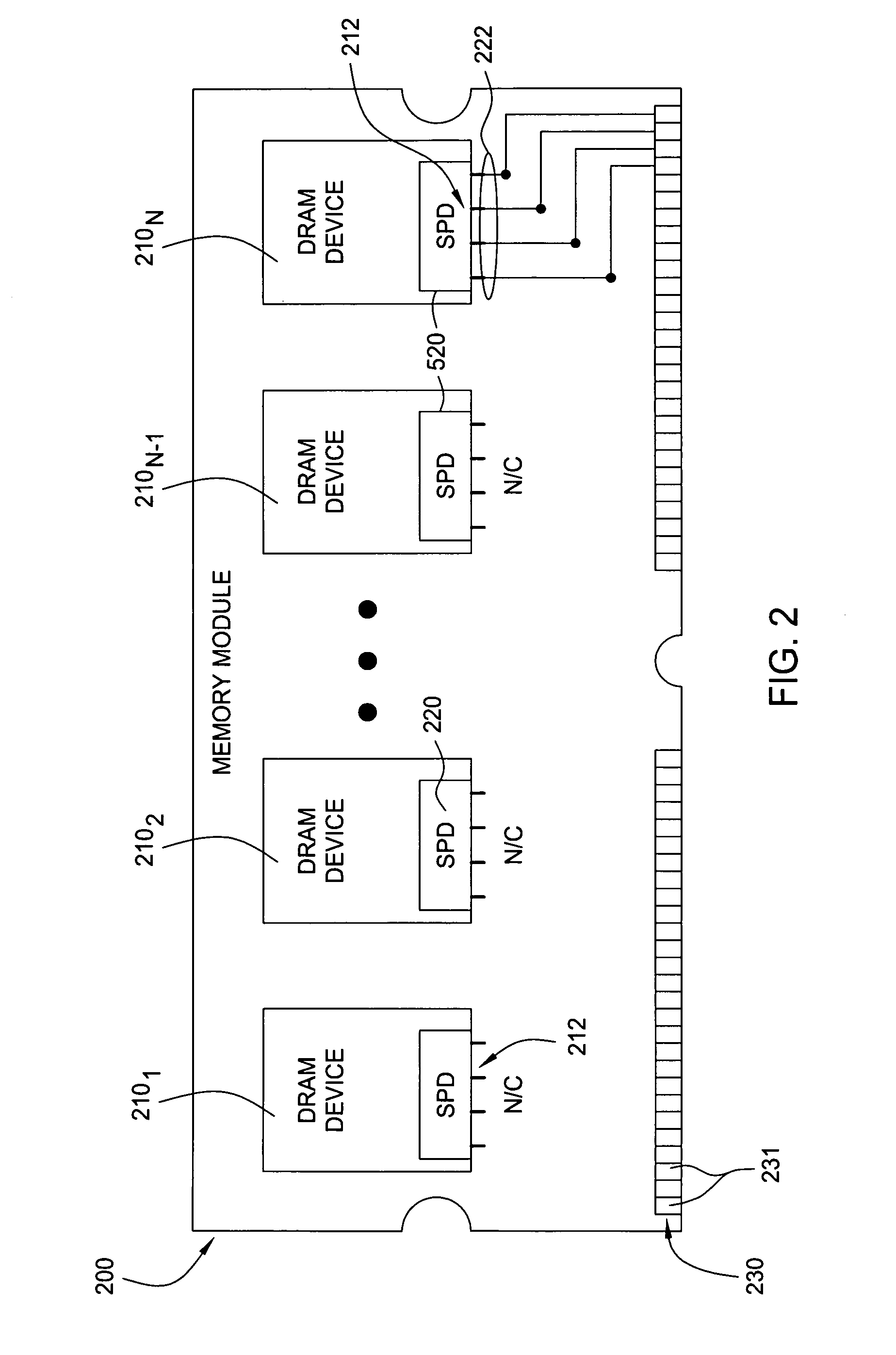

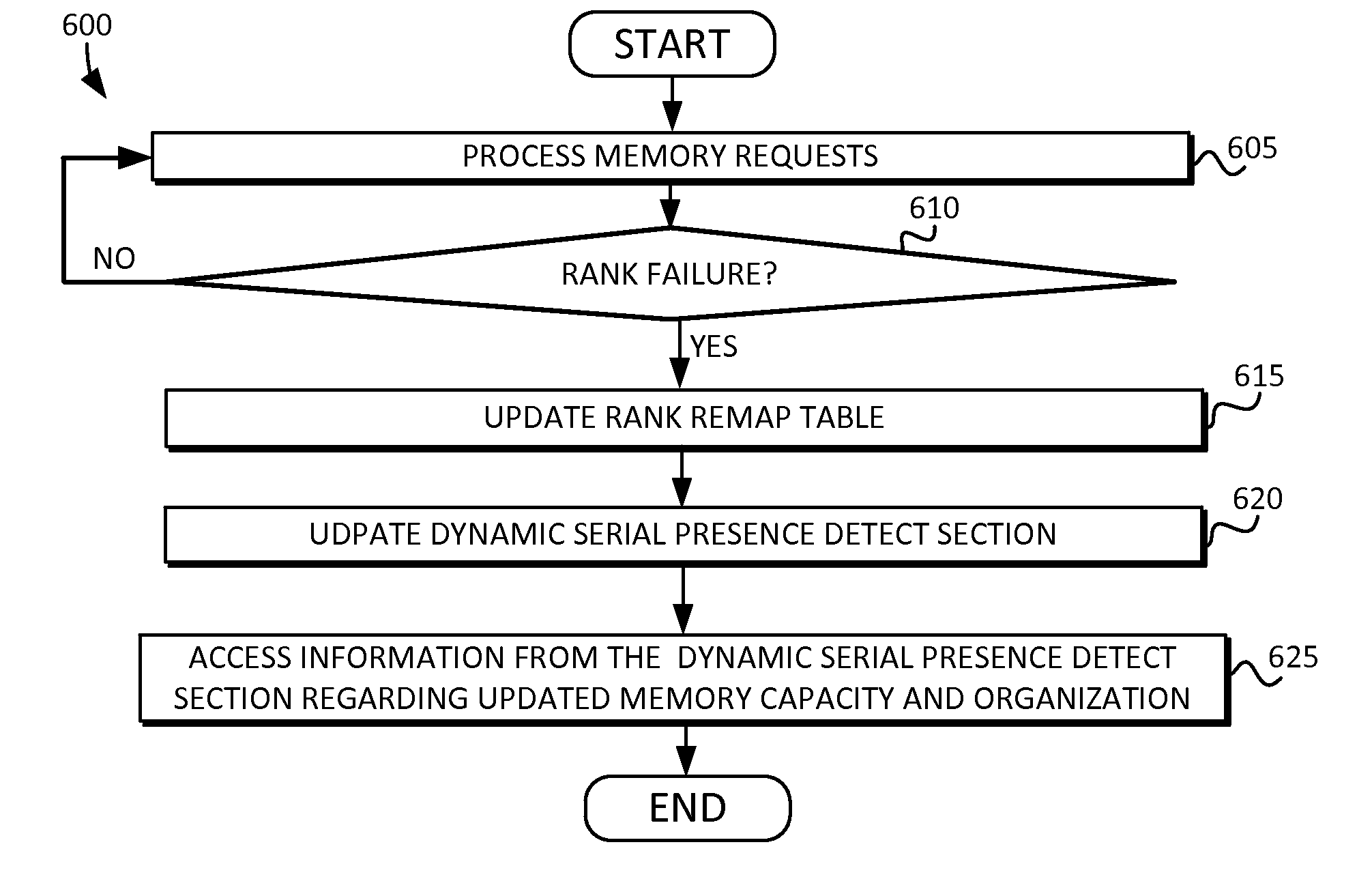

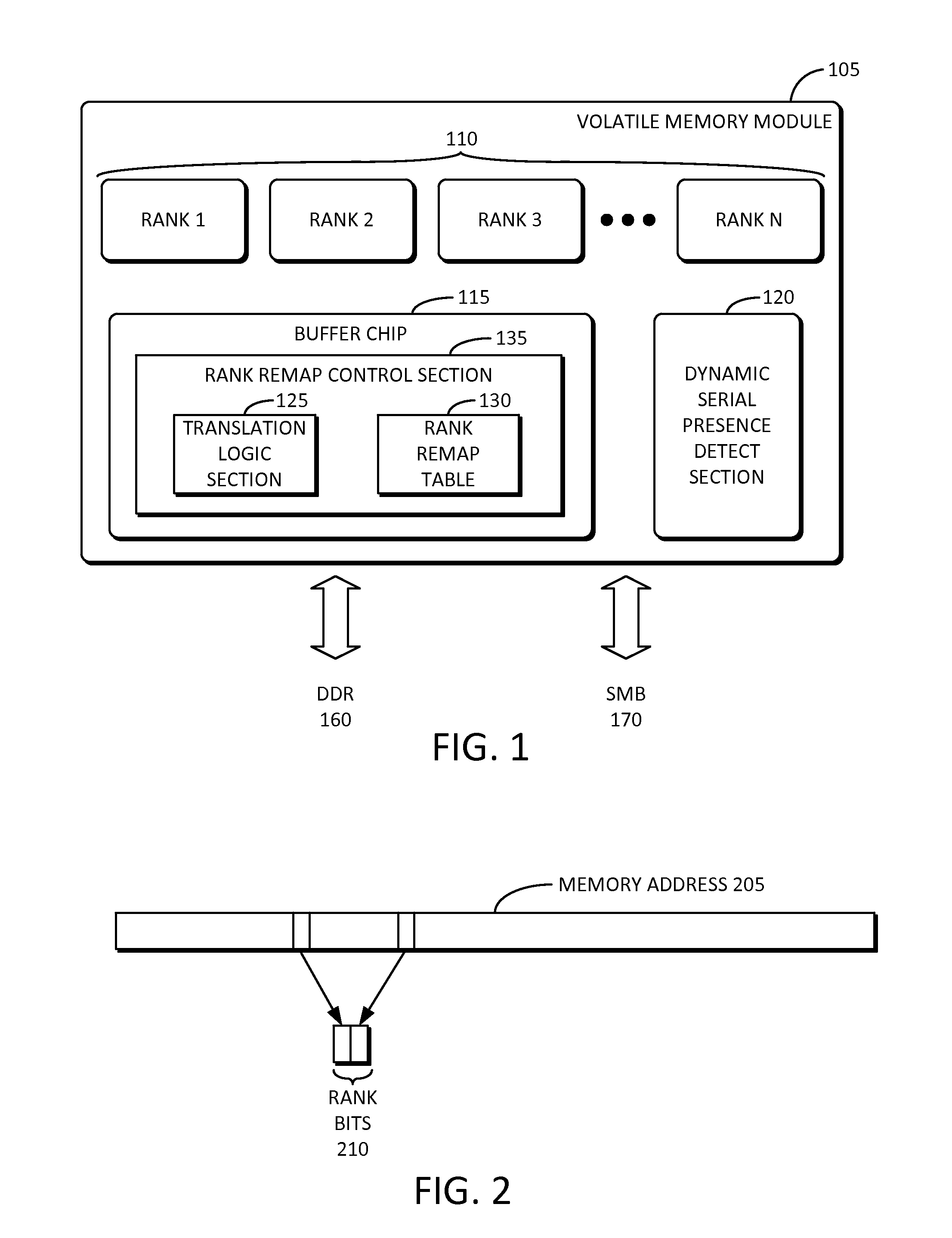

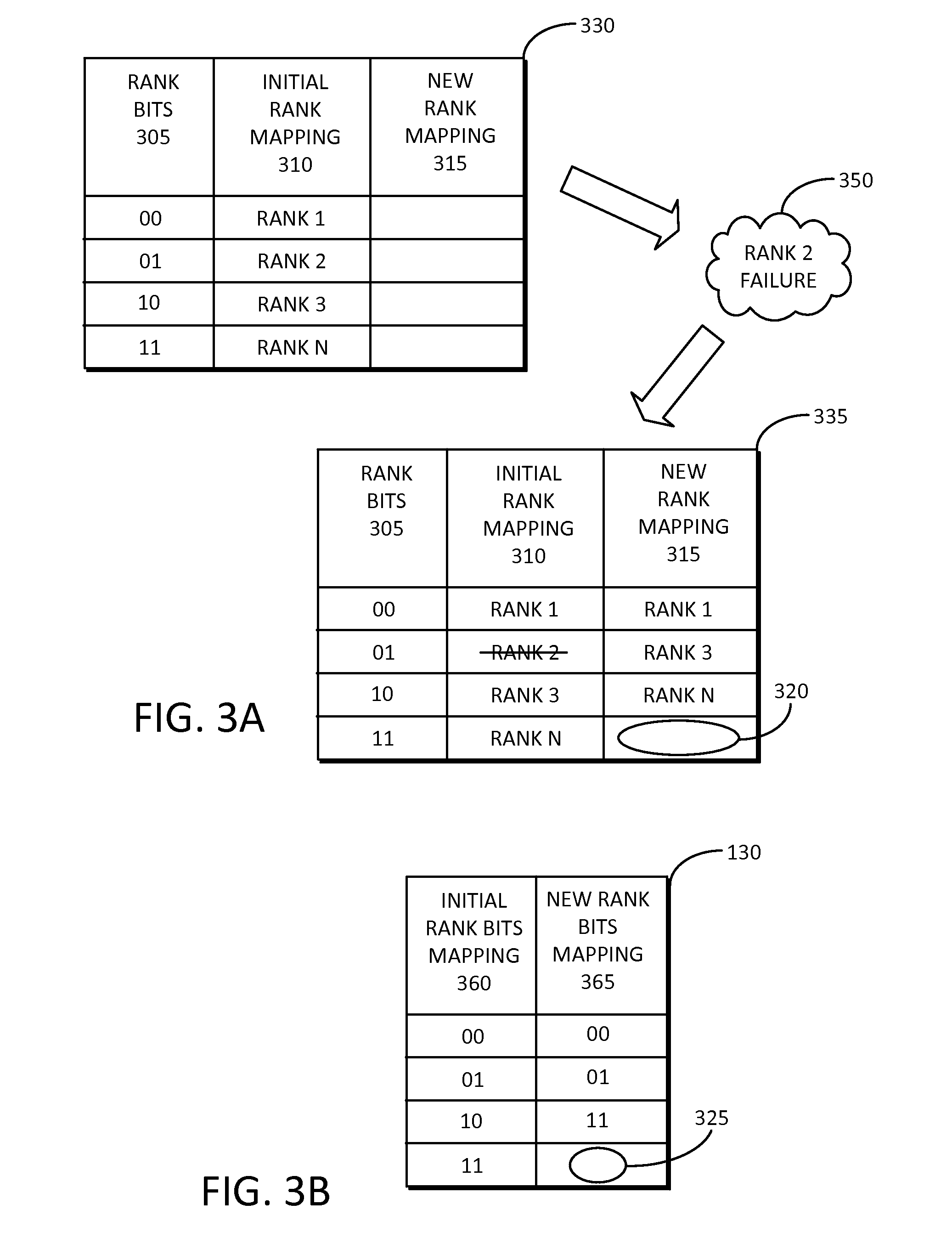

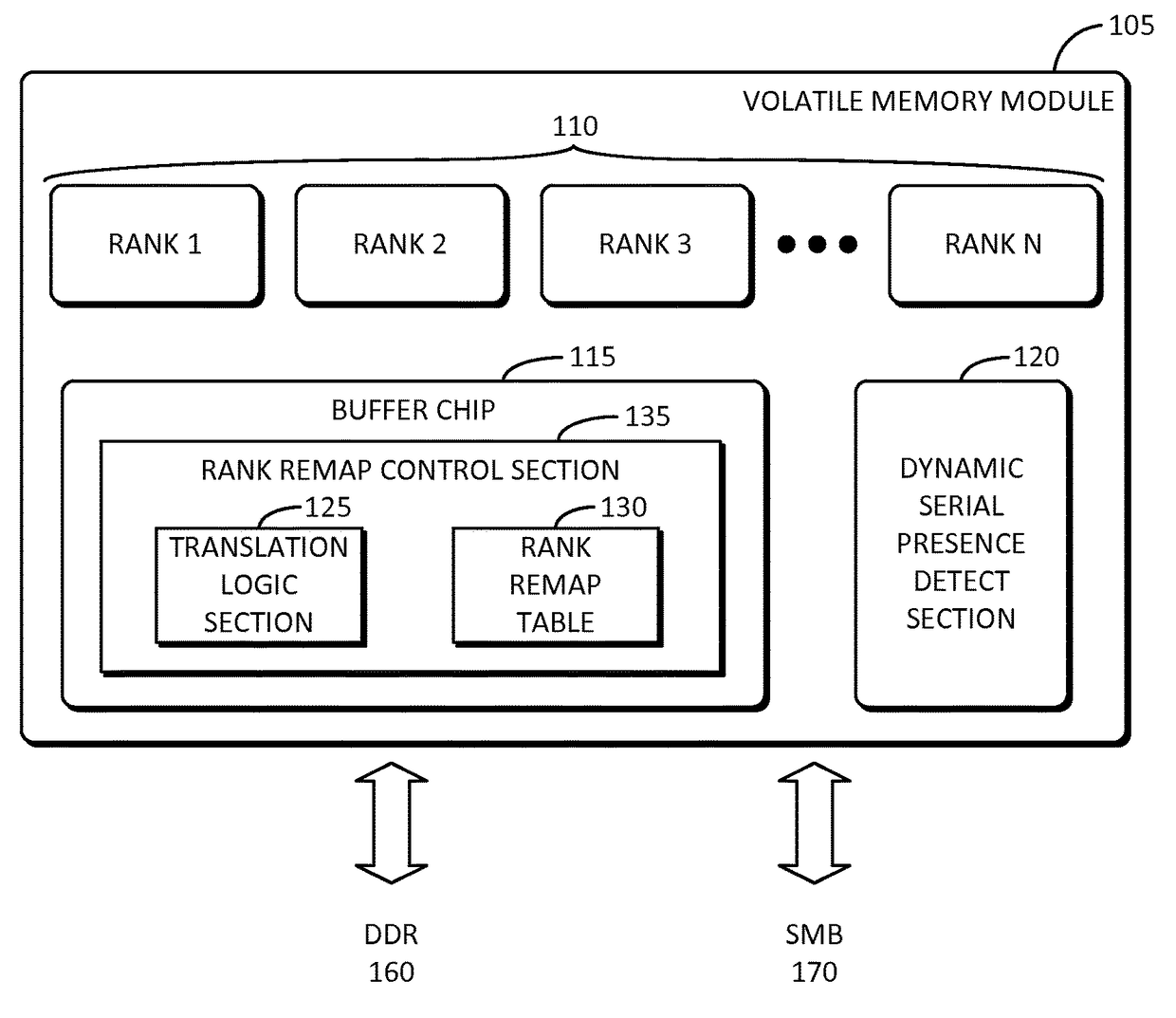

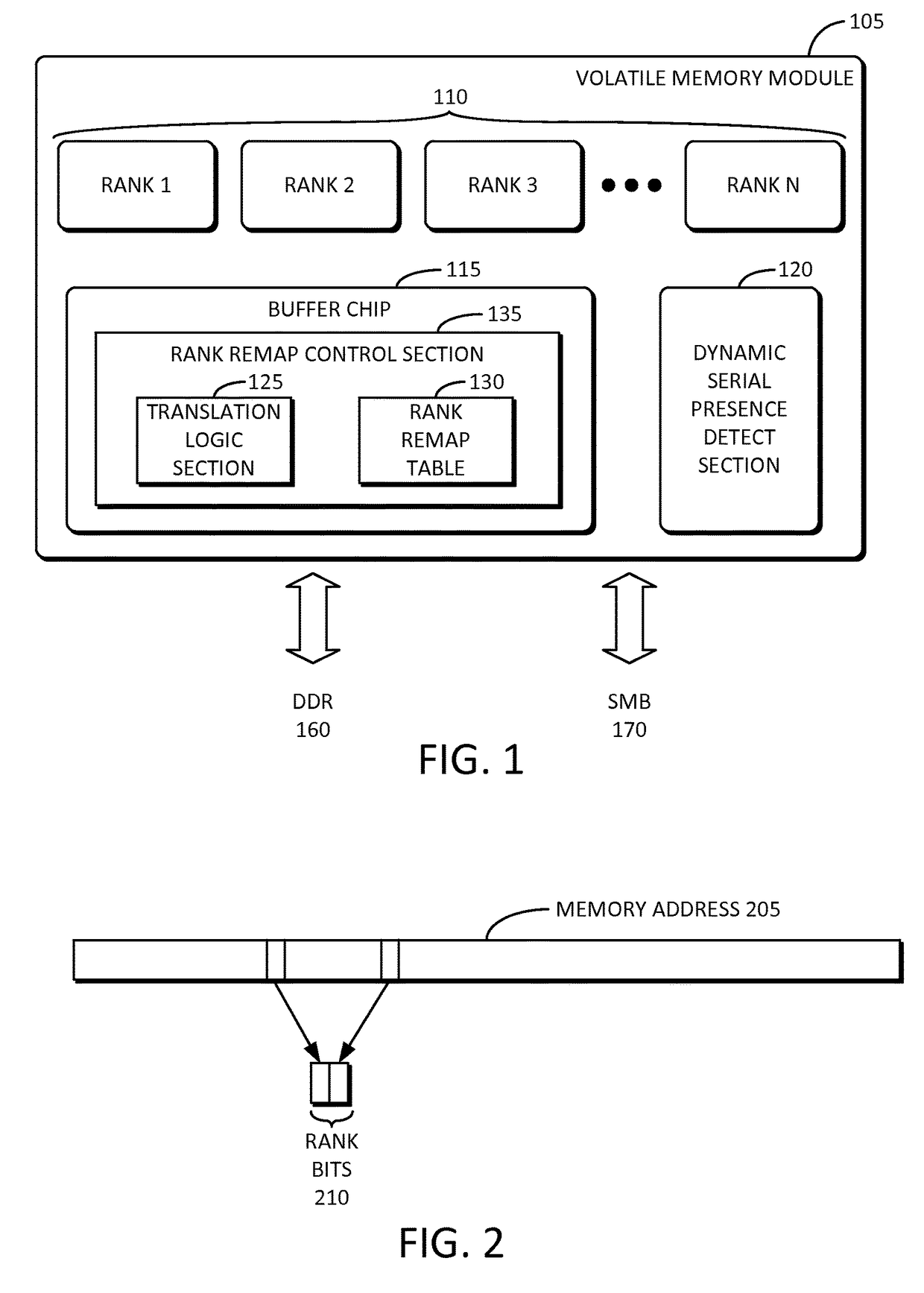

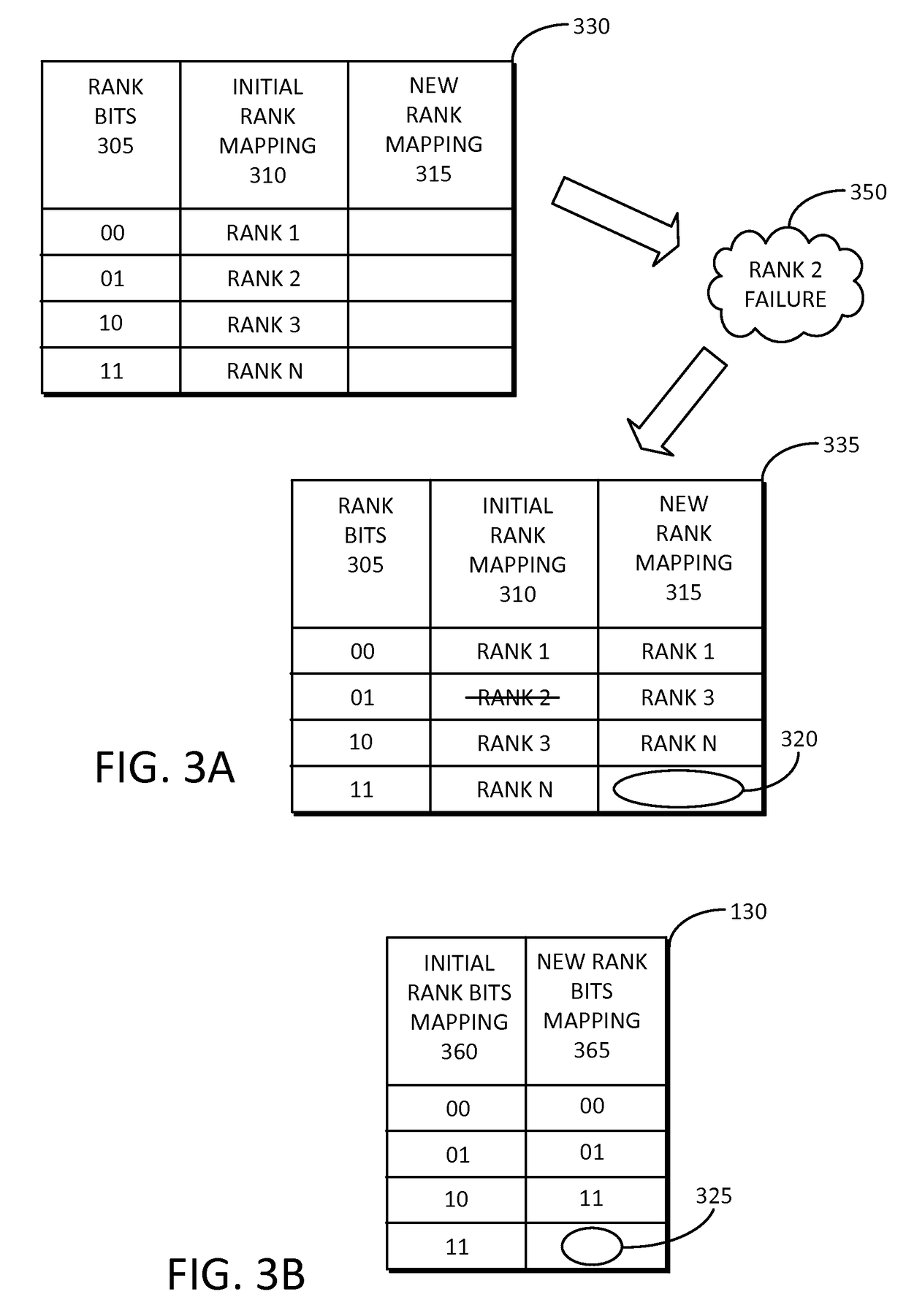

Rank and page remapping logic in a volatile memory

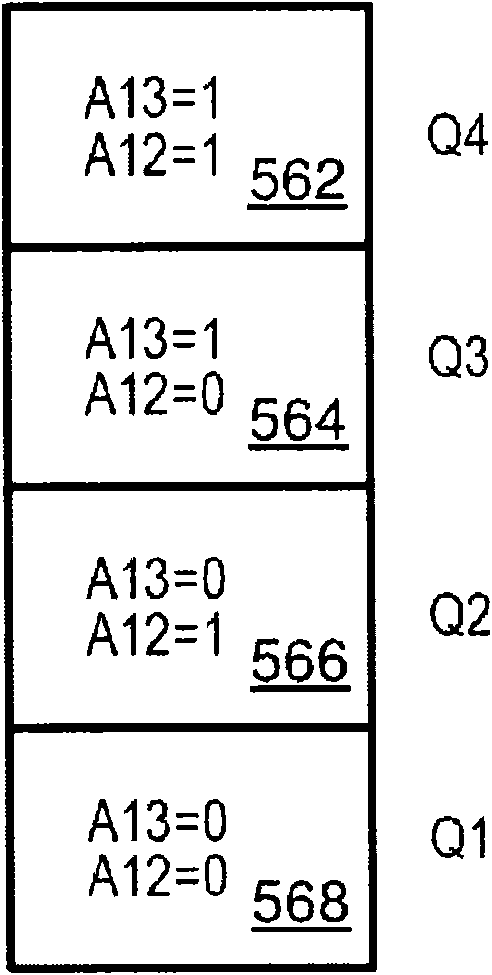

ActiveUS20160147623A1Memory architecture accessing/allocationMemory adressing/allocation/relocationSerial presence detectMemory rank

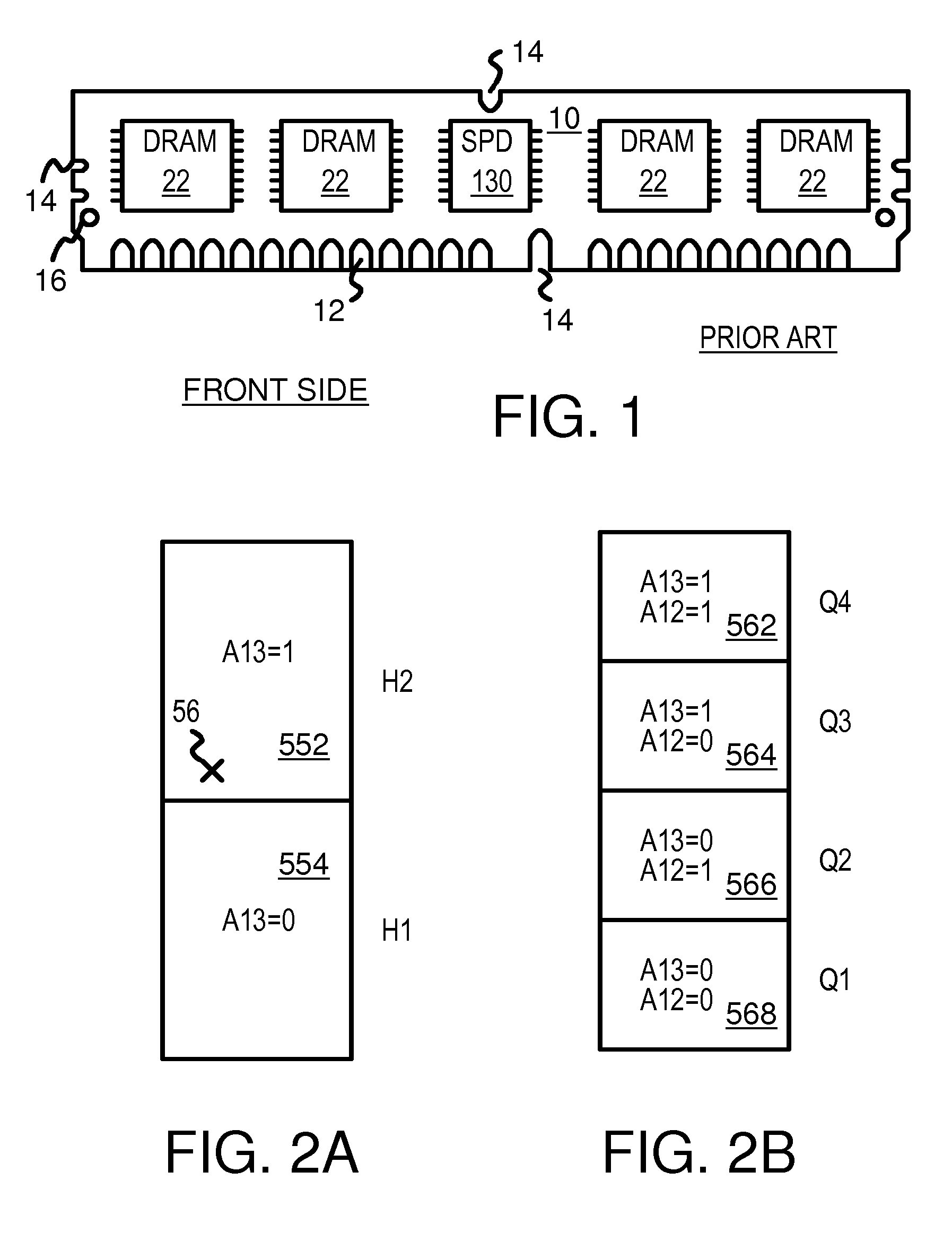

Embodiments of the inventive concept include a plurality of memory ranks, a buffer chip including a rank remap control section configured to remap a rank from among the plurality of memory ranks of the volatile memory module responsive to a failure of the rank, and a dynamic serial presence detect section configured to dynamically update a stated total capacity of the volatile memory module based at least on the remapped rank. In some embodiments, a memory module includes a plurality of memory ranks, an extra rank in addition to the plurality of memory ranks, the extra rank being a spare rank configured to store a new page corresponding to a failed page from among the plurality of ranks, and a buffer chip including a page remap control section configured to remap the failed page from among the plurality of ranks to the new page in the extra rank.

Owner:SAMSUNG ELECTRONICS CO LTD

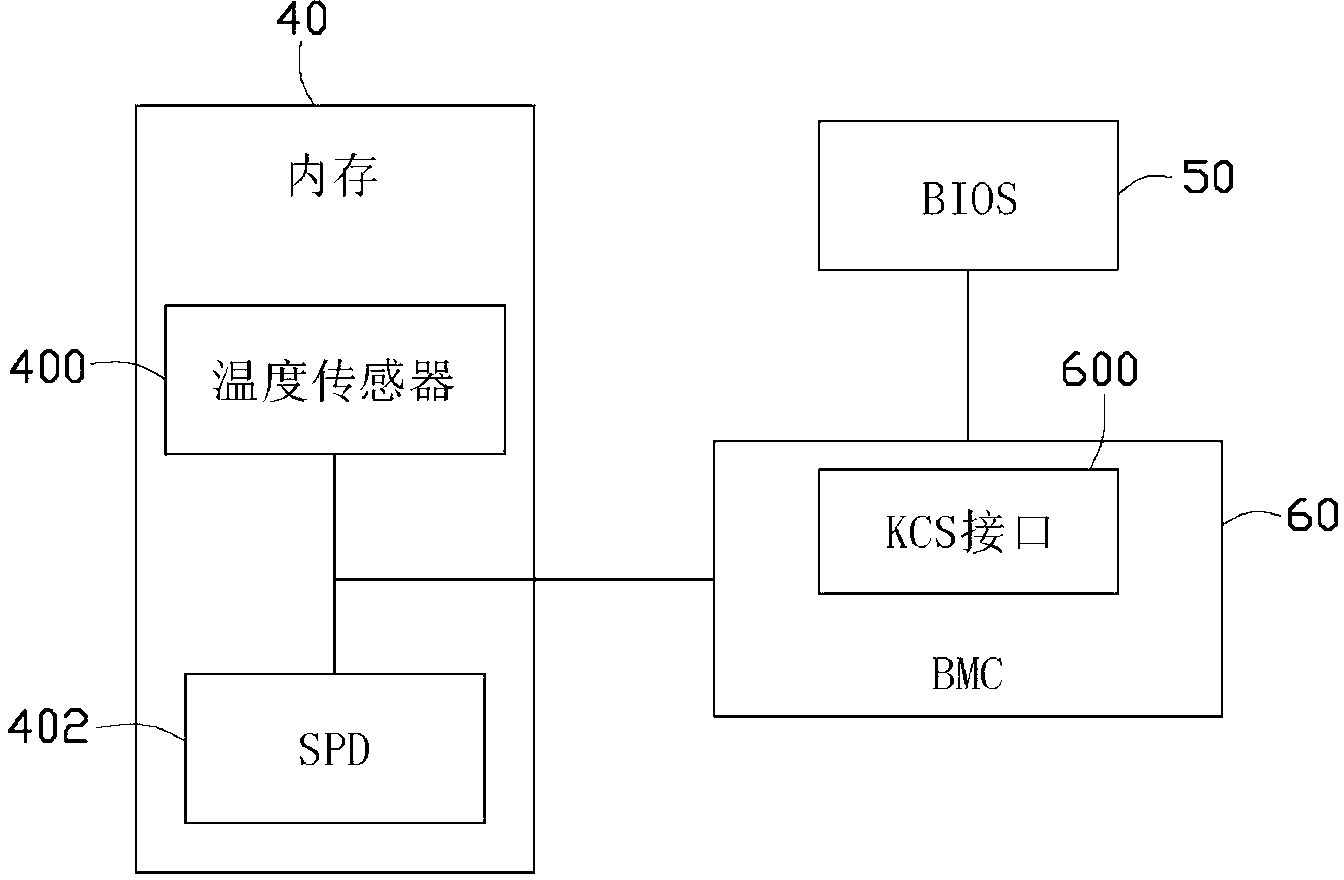

Computer starting detection system

InactiveCN103077102AImprove stabilityAvoid temperatureDetecting faulty computer hardwareBaseboardSerial presence detect

A computer starting detection system comprises a memory, a baseboard management controller and a basic input / output system, wherein the memory comprises a temperature sensor for detecting the memory temperature and a serial presence detect (SPD) for storing the memory allocation information, the basic input / output system is connected with the baseboard management controller through a low pin count (LPC) bus, and the baseboard management controller is connected with the SPD and the temperature sensor through an inter-integrated circuit (I2C) bus; the output of the basic input / output system encapsulates a command for supporting an LPC protocol and accessing a baseboard management controller protocol and transmitting the encapsulated command to the baseboard management controller through the LPC bus; and the baseboard management controller receives and encapsulates the command, so that the command can be transmitted to the SPD through the I2C bus to obtain the memory allocation information. By utilizing the computer starting detection system, the computer stability can be improved.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Fully-Buffered Memory-Module with Redundant Memory Buffer in Serializing Advanced-Memory Buffer (AMB) for Repairing DRAM

A repairing fully-buffered memory module can have memory chips with some defects such as single-bit errors. A repair controller is added to the Advanced Memory Buffer (AMB) on the memory module. The AMB fully buffers memory requests that are sent as serial packets over southbound lanes from a host. Memory-access addresses are extracted from the serial packets by the AMB. The repair controller compares the memory-access addresses to repair addresses and diverts access from defective memory chips to a spare memory for the repair addresses. The repair addresses can be located during testing of the memory module and programmed into a repair address buffer on the AMB. The repair addresses could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to the repair address buffer on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

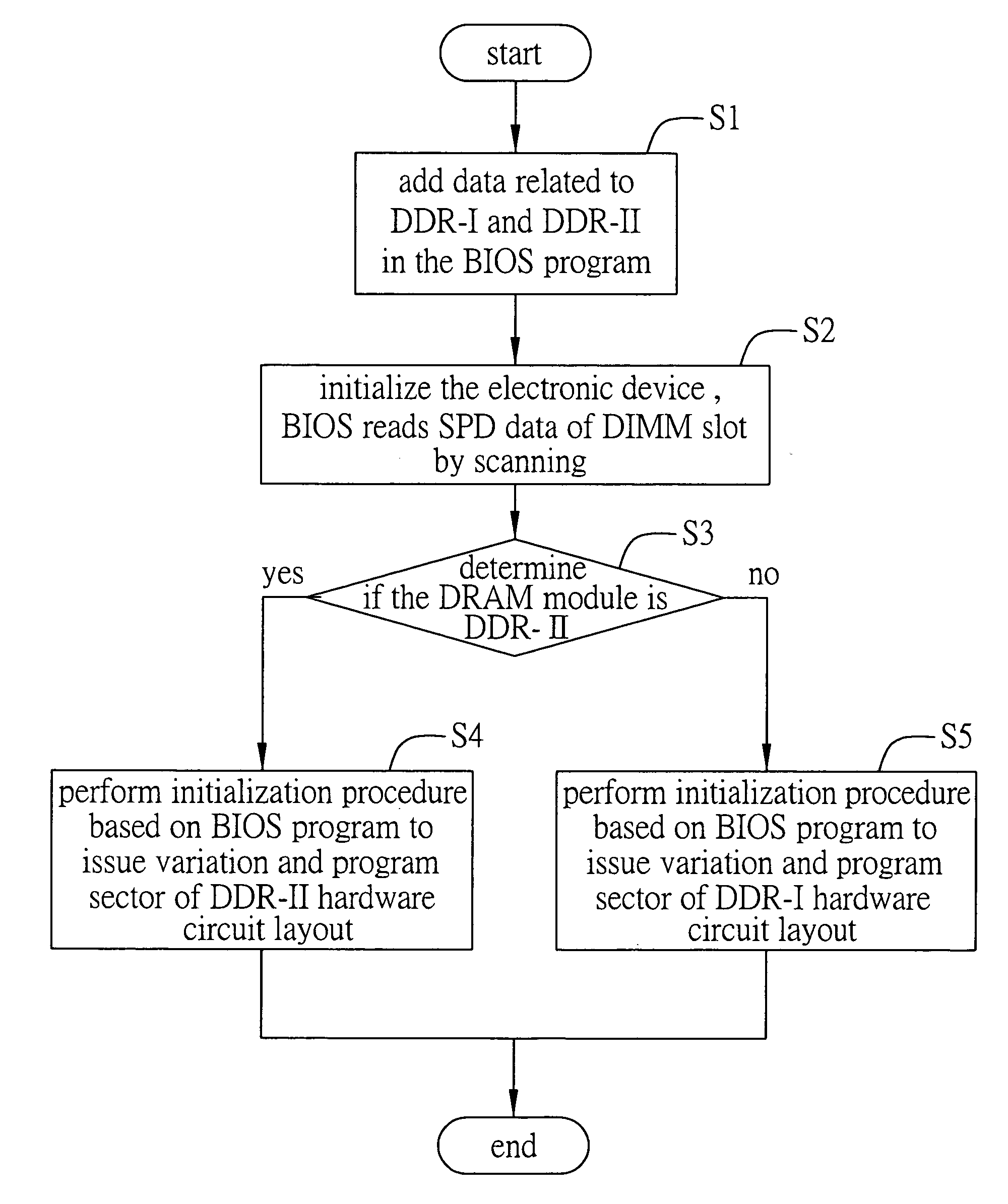

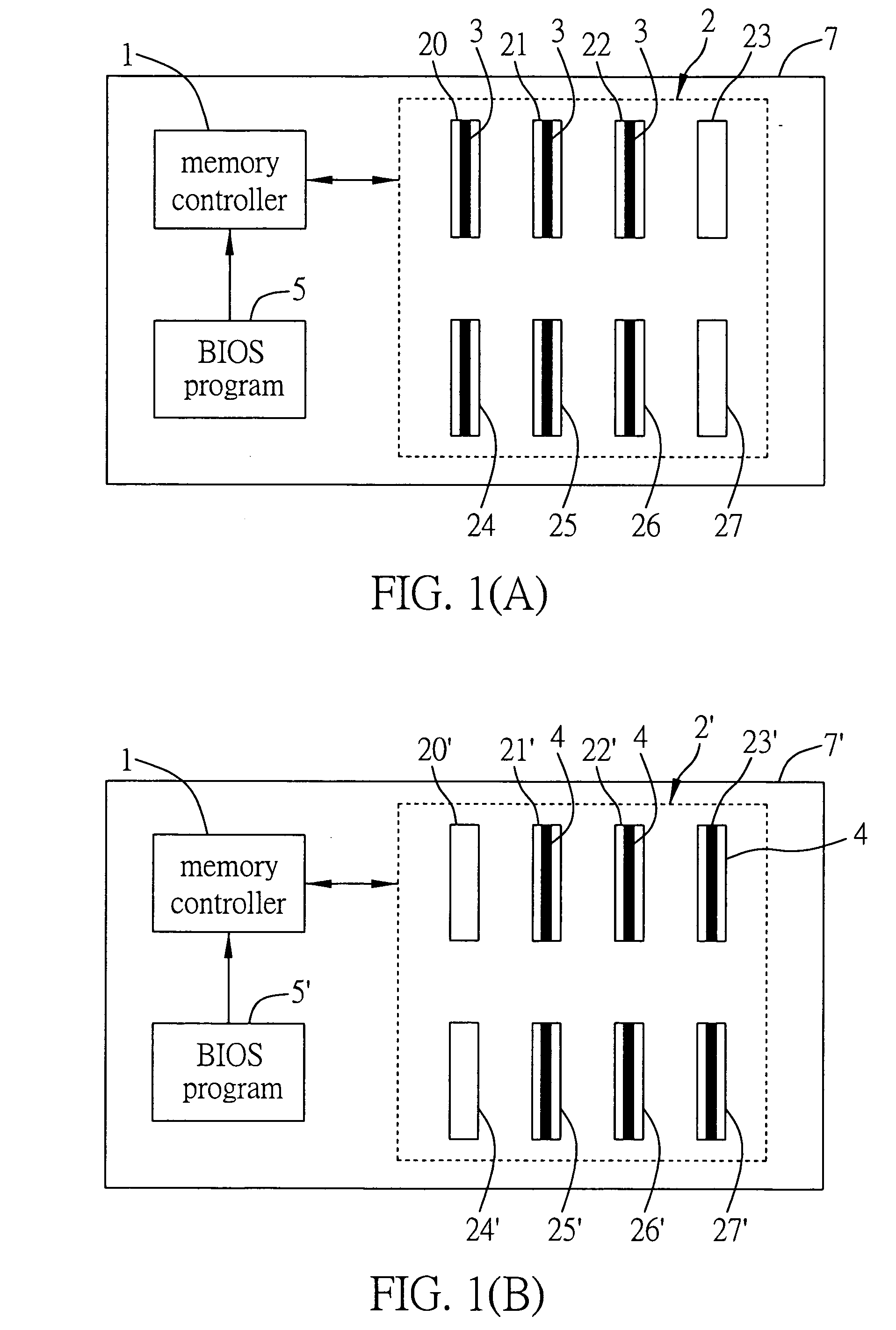

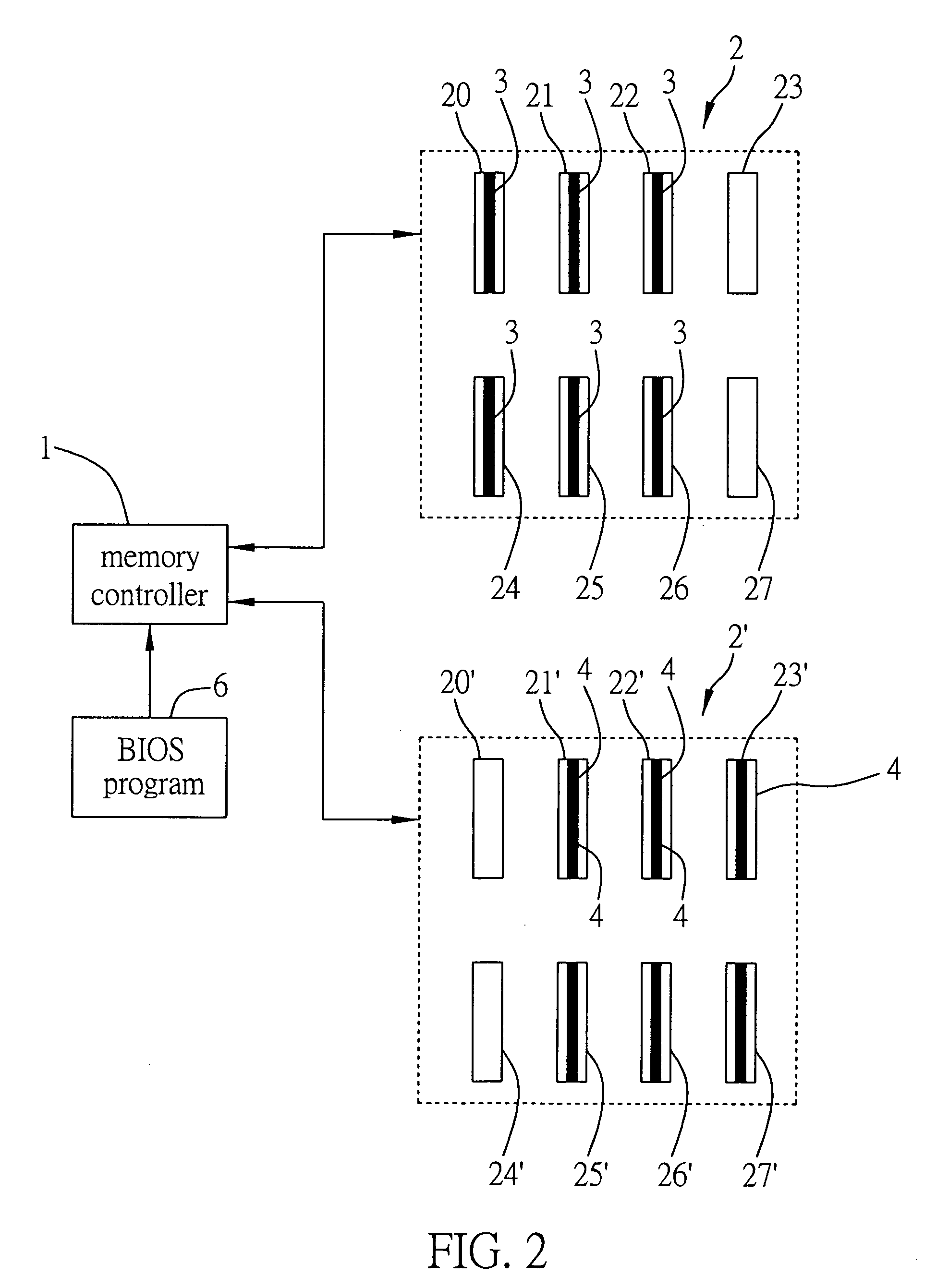

Method for controlling access of dynamic random access memory module

A method for controlling access for a DRAM module applicable to a substrate provided with at least a DRAM module slot of either a first or second specification, a memory controller and a BIOS program is proposed. Thus, access control for first and second DRAM modules installed in the DRAM module slots can be performed. The first and second DRAM module related data is pre-stored by the BIOS program. Then, a memory initialization process is performed by the substrate according to the BIOS program, such that the memory controller access the DRAM module provided on the substrate during the memory initialization process, and serial present detect (SPD) data of the DRAM module is read using an I2C protocol via a system management (SM) bus, so as to determine whether the DRAM module installed in the DRAM module slot is the first DRAM module or the second DRAM module according to a value in a memory type field of the SPD data. Finally, with the determined DRAM module, the DRAM module related data corresponding to the DRAM module is read from the BIOS program by the memory controller, so as to achieve access control for the DRAM module.

Owner:INVENTEC CORP

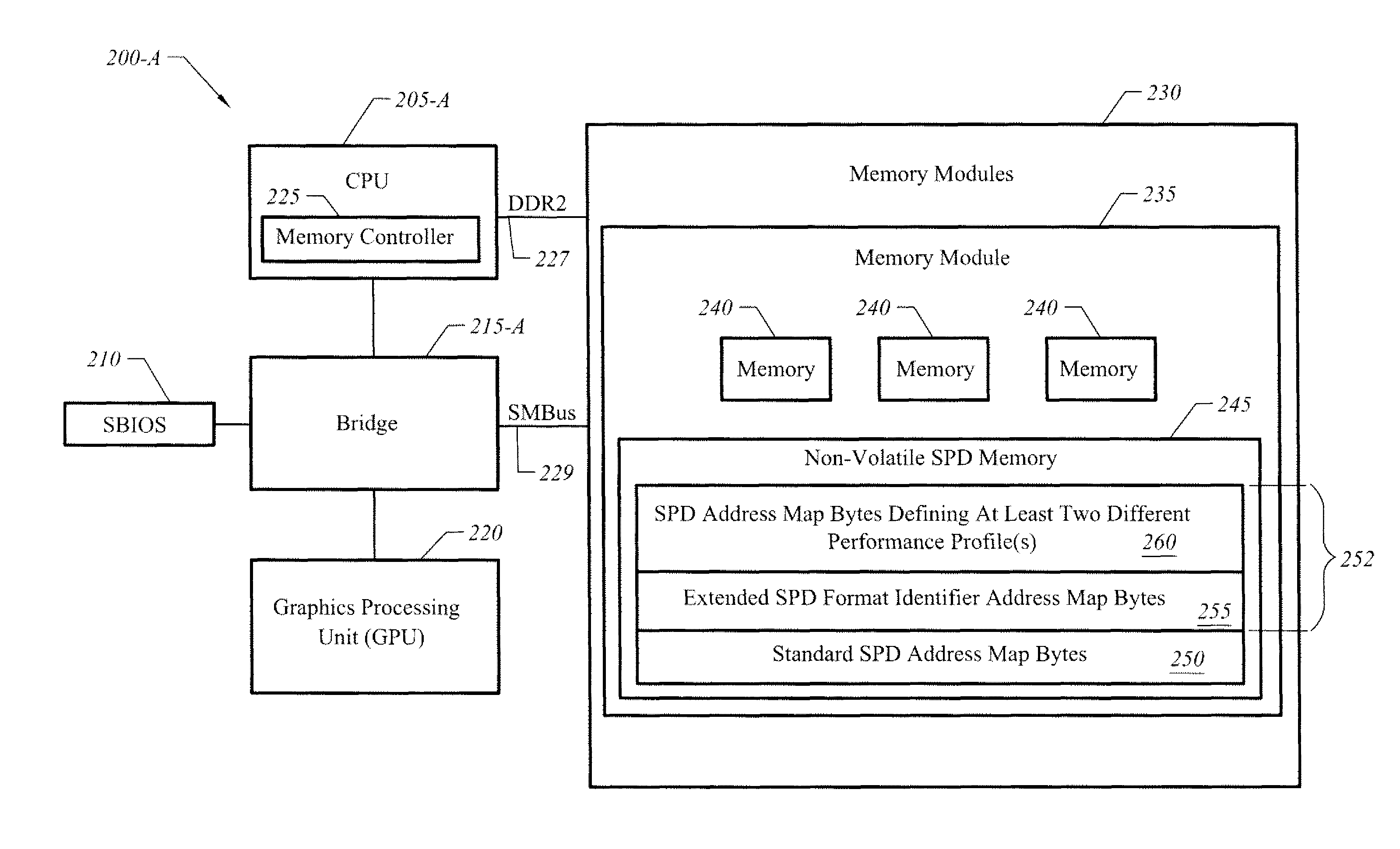

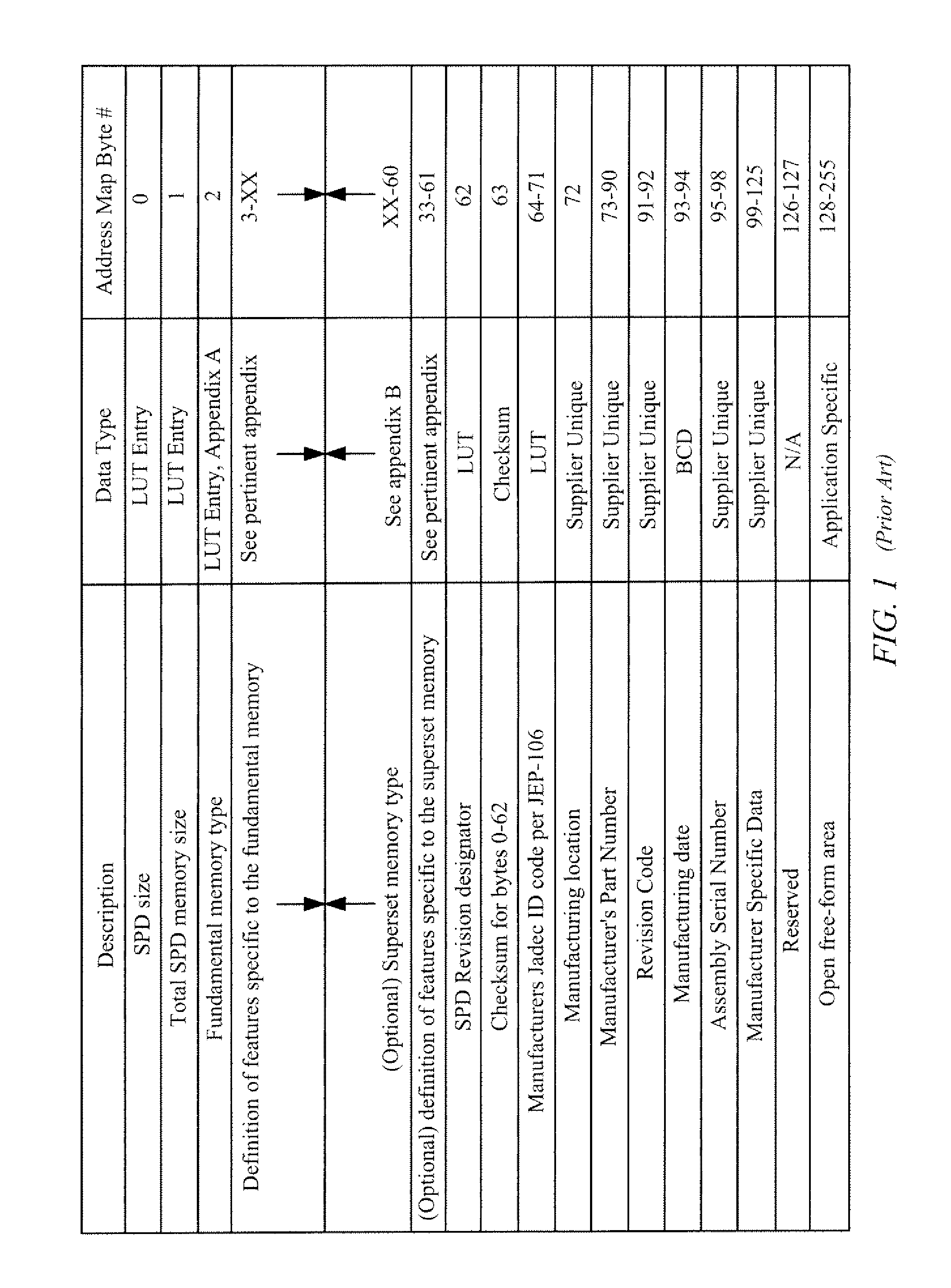

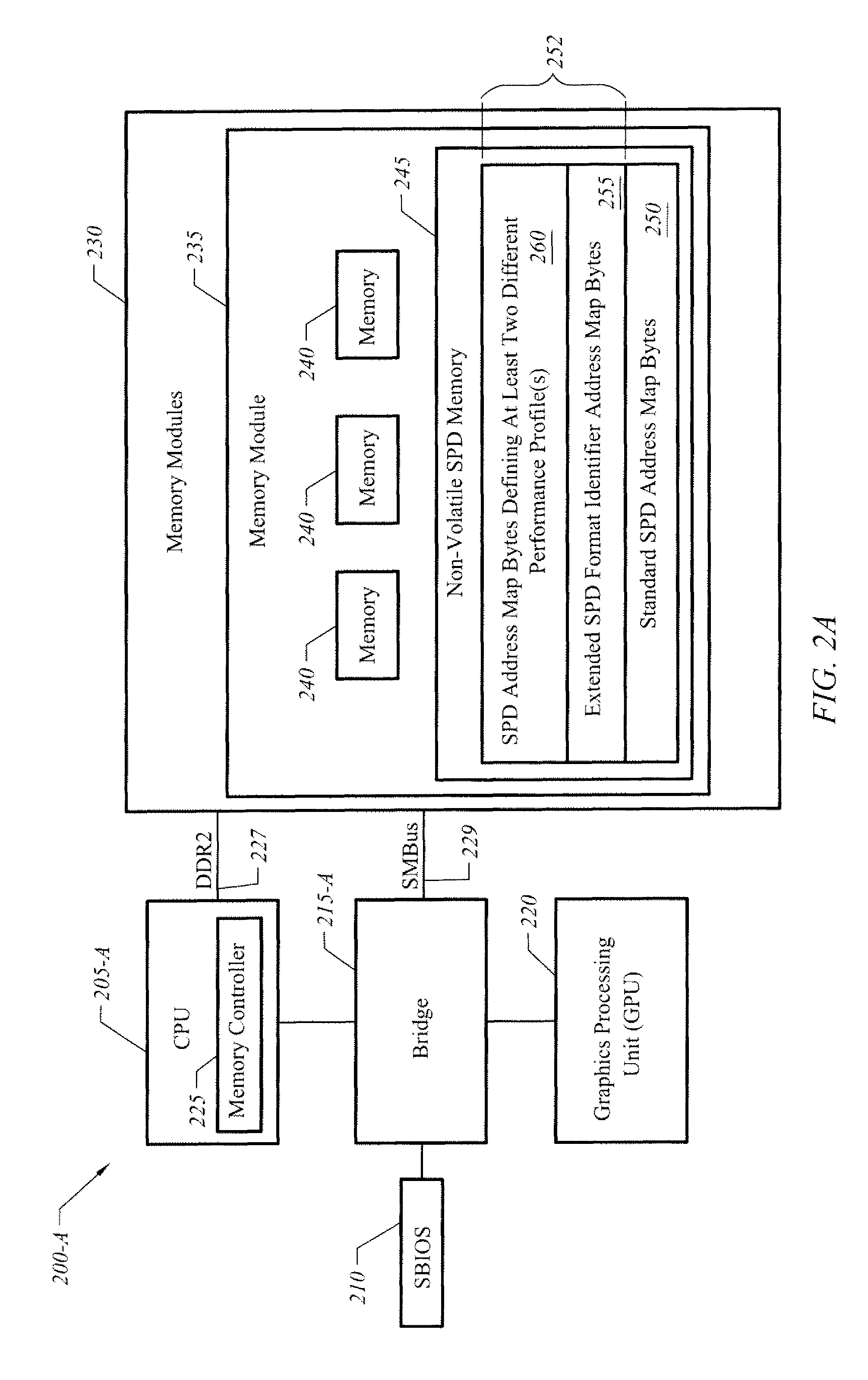

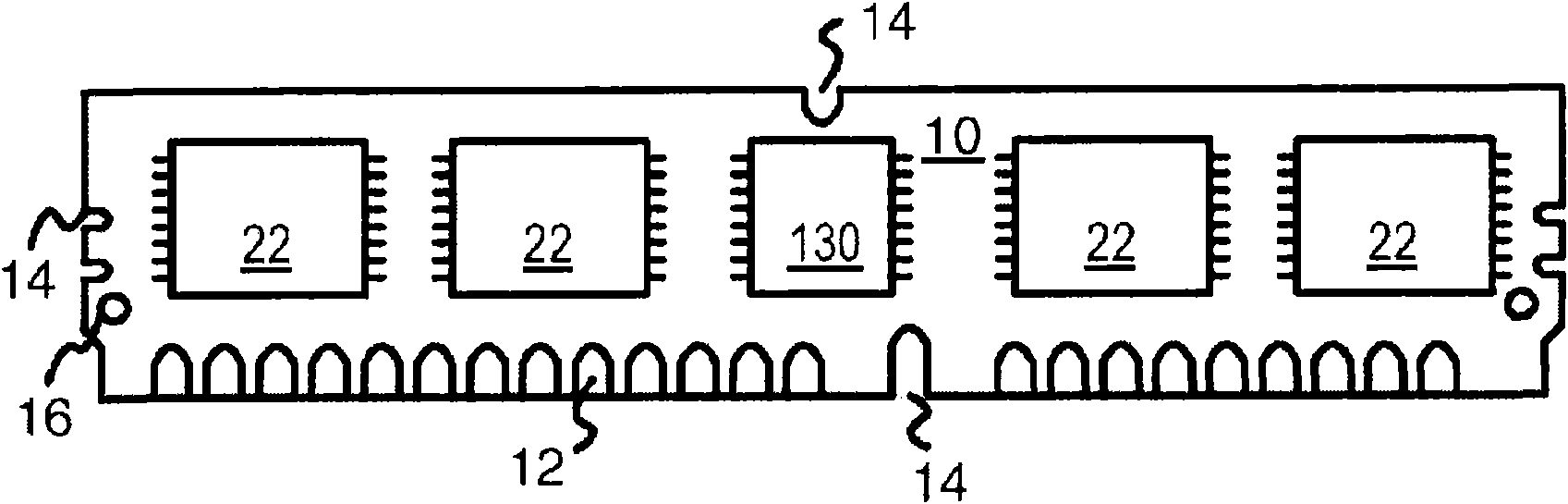

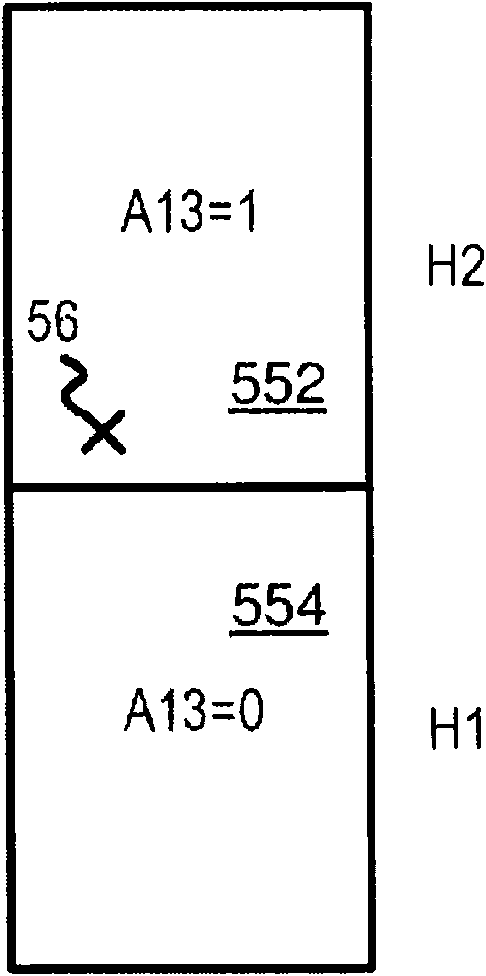

Apparatus, system, and method for extended serial presence detect for memory performance optimization

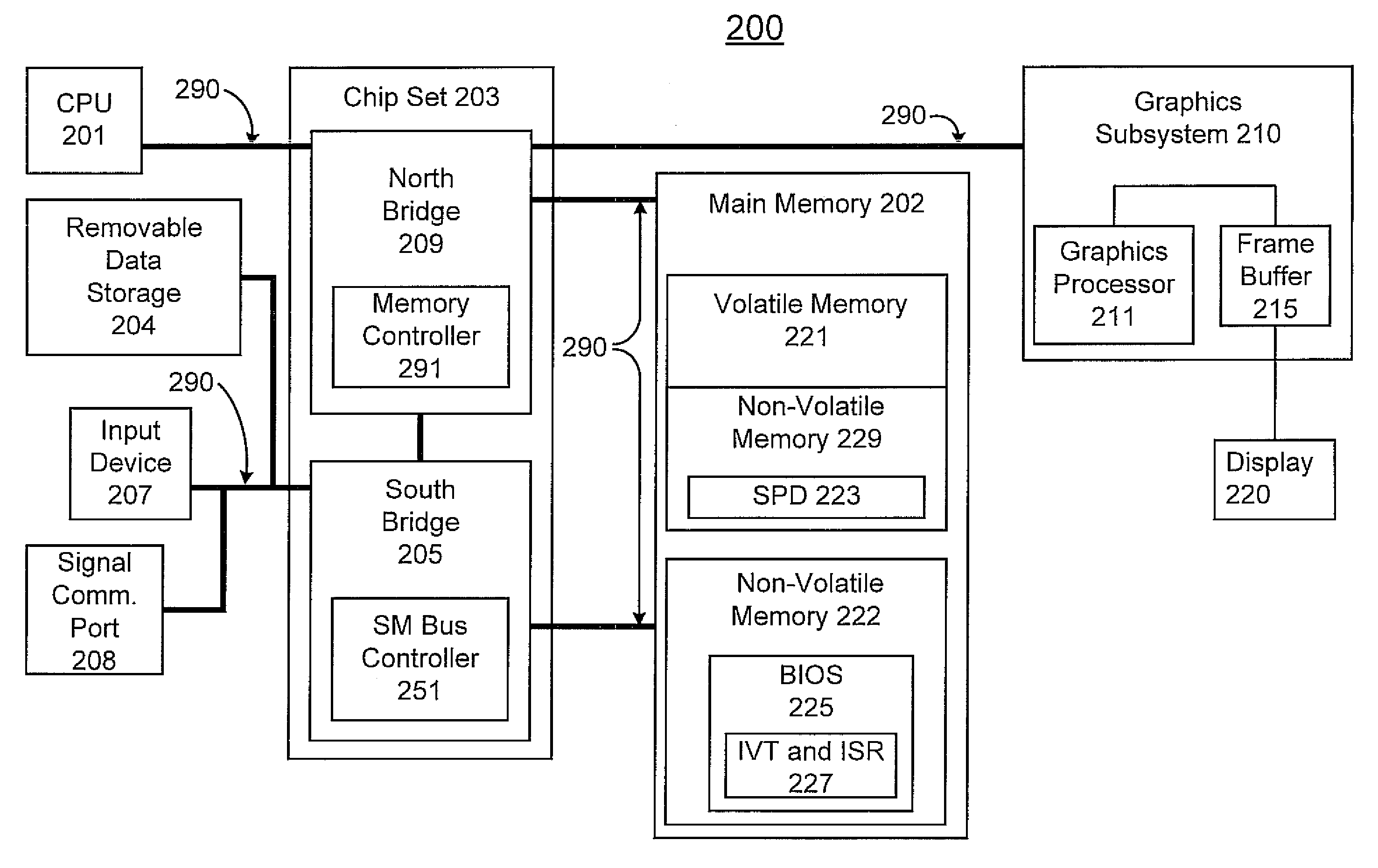

A computing system has a mode of operation in which at least two different memory parameter profiles are read by a BIOS to configure memory. In one implementation the memory parameter profiles are stored in a serial presence detect memory using an extended serial presence detect format.

Owner:NVIDIA CORP

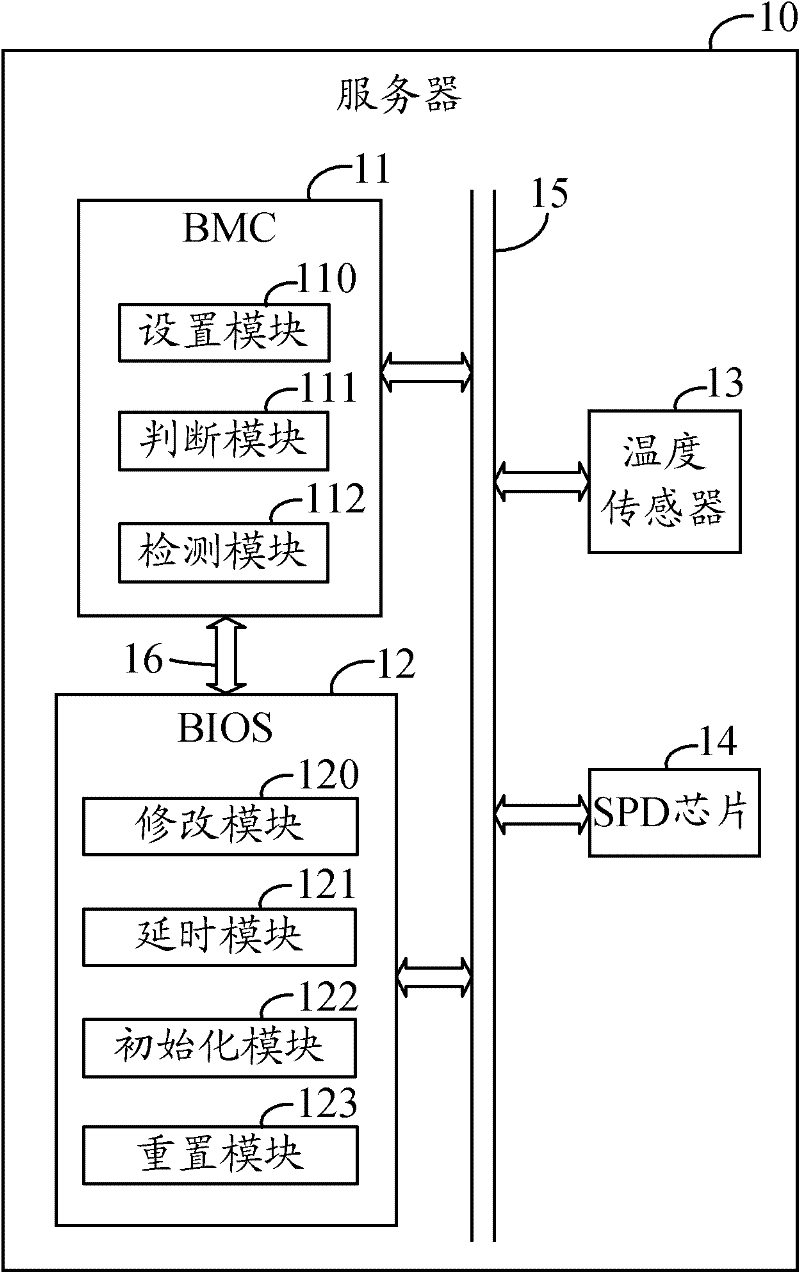

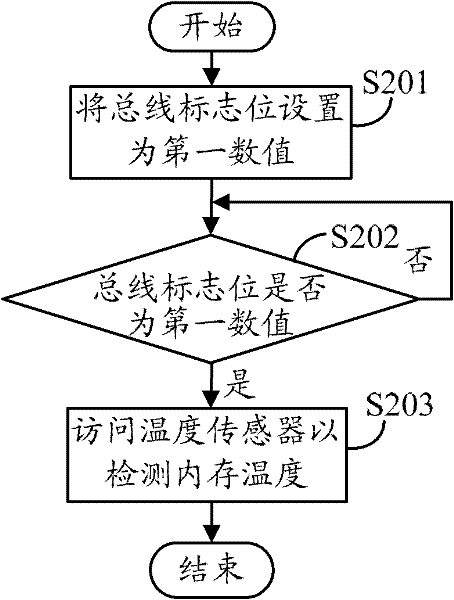

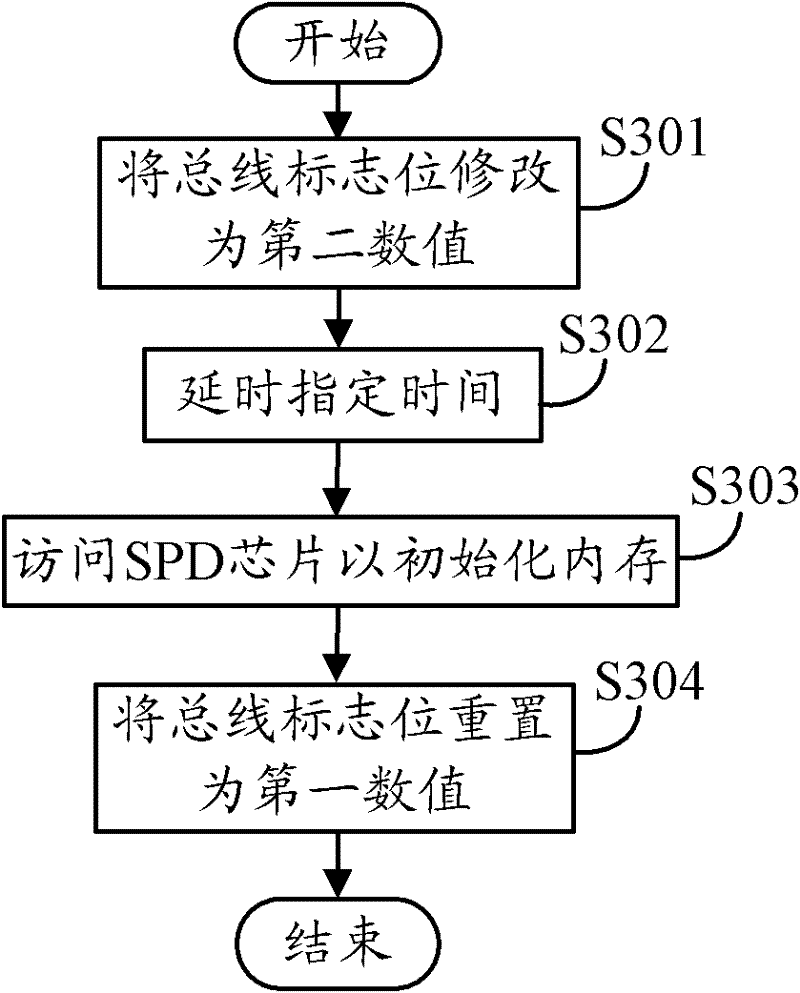

Server and method for avoiding bus collision

InactiveCN102446146AAvoid bus conflictsElectric digital data processingBaseboardSerial presence detect

A server comprises a BMC (Baseboard Management Controller), a BIOS (Basic Input Output System), a temperature sensor, and an SPD (Serial Presence Detect) chip. The BMC comprises a setting module, a judging module, and a detection module, wherein the setting module is used for setting a bus mark bit as a first numerical value when the server is started up; the judging module is used for judging whether the bus mark bit is the first numerical value or not when the temperature of an internal storage is required to be detected; and the detection module is used for visiting the temperature sensor by utilizing an I2C bus when the bus mark bit is the first numerical value. The BIOS comprises a modification module, a delay module, an initialization module and a reset module, wherein the modification module is used for setting the bus mark bit as a second numerical value when the inner storage is required to be initialized; the delay module is used for delaying schedule time; the initialization module is used for visiting the SPD chip by utilizing the I2C bus to acquire the configuration information on the internal storage to initialize the internal storage when the schedule time is over; and the reset module is used for resetting the bus mark bit as the first numerical value after the initialization of the internal storage is completed. The invention further provides a method for avoiding the bus collision by utilizing the server, which can avoid bus collision caused by that the I2C bus is simultaneously used by the BMC and the BIOS.

Owner:HUAINAN SHENGDAN NETWORK ENG TECH

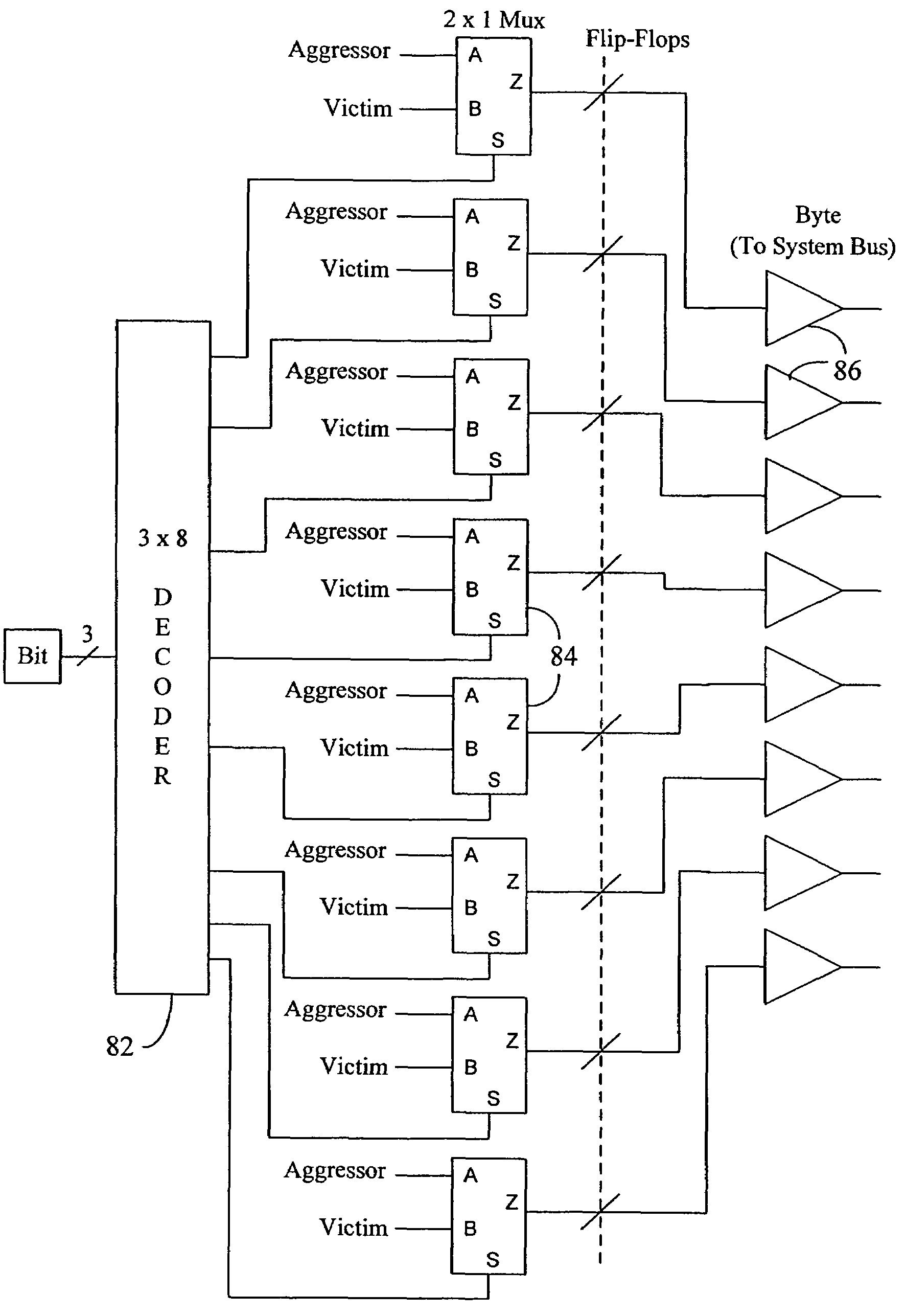

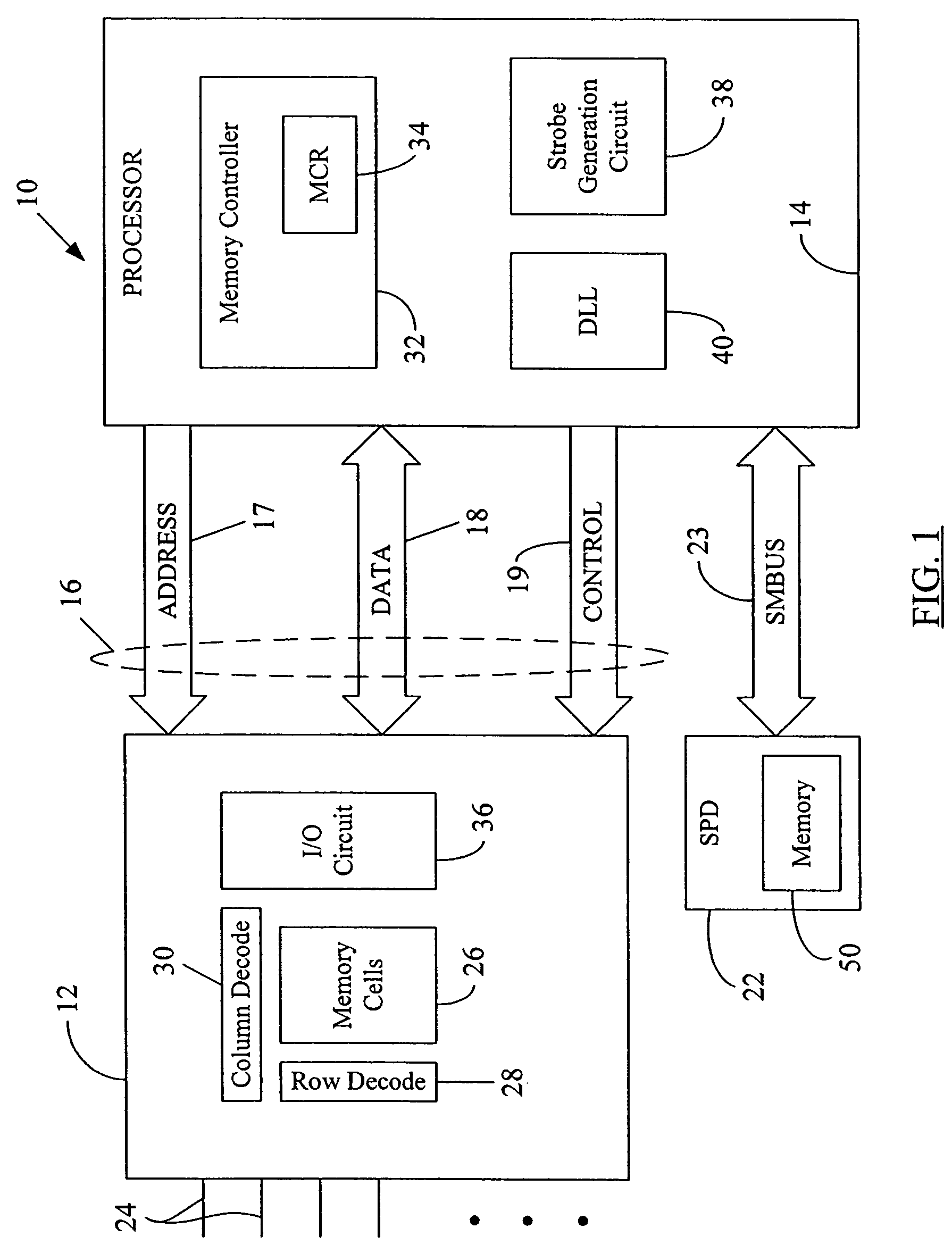

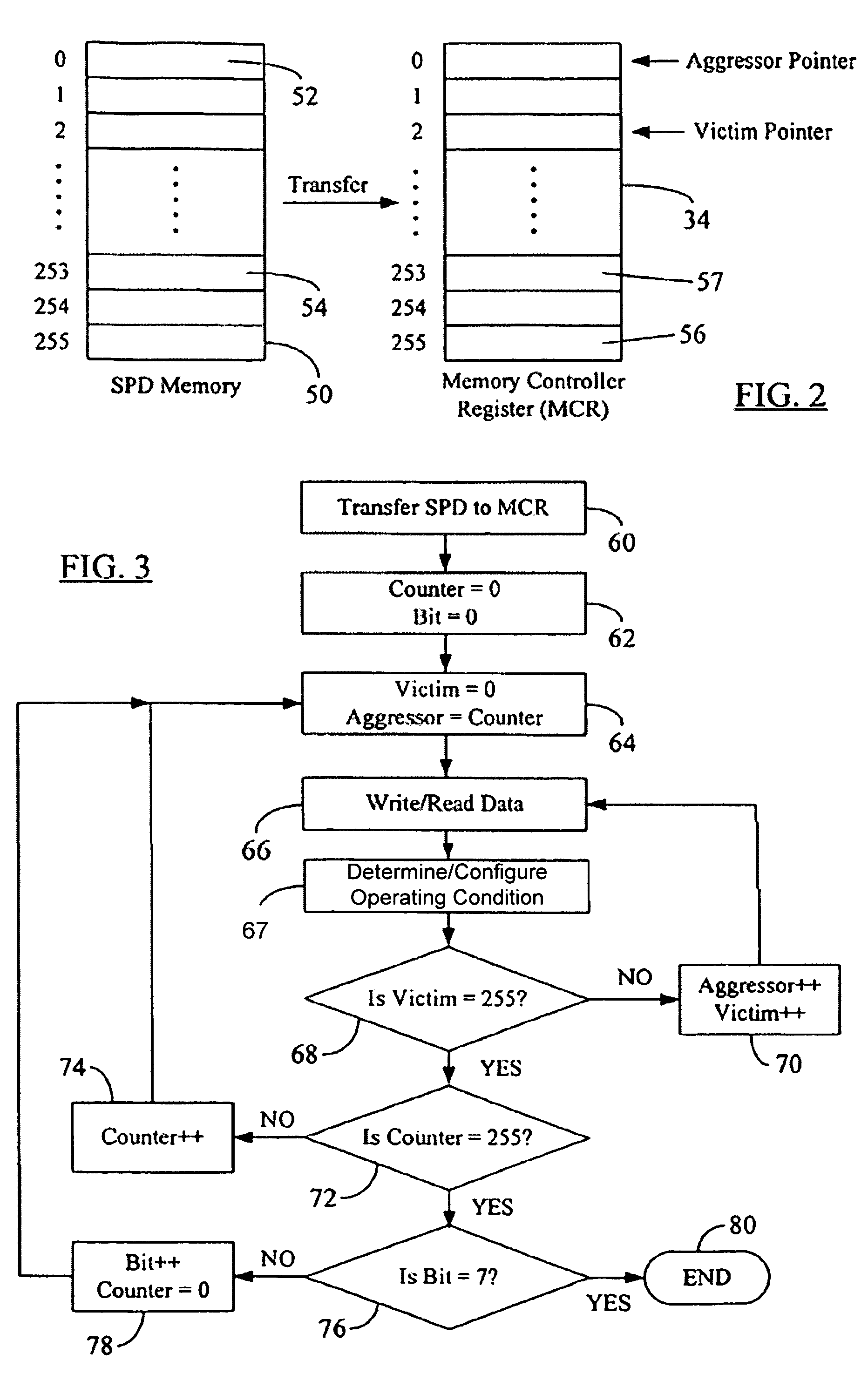

Providing memory test patterns for DLL calibration

InactiveUS7694202B2Easy to operateAccurate CalibrationElectronic circuit testingError detection/correctionMemory chipBit line

A system and method to provide memory test patterns for the calibration of a delay locked loop (DLL) using a pseudo random bit sequence (PRBS) stored in a serial presence detect (SPD) circuit memory. The test bits stored in the SPD memory are transferred to a memory controller register (MCR) and implemented on the system data bus as test patterns that closely simulate run-time switching conditions on the system bus, so as to allow more accurate calibration of the DLL. Test data write / read operations may be performed while signals for the test patterns are present on various bit lines in the data bus so as to allow for accurate determination or adjustment of the value for the delay to be provided by the DLL to the strobe signals during memory data reading operations at run time. Memory chips may also be tested over an operating range of values using the generated test patterns.

Owner:ROUND ROCK RES LLC

Manufacturing method for partially-good memory modules with defect table in EEPROM

ActiveUS7642105B2Semiconductor/solid-state device testing/measurementSolid-state devicesGoal systemRead-only memory

A manufacturing method makes memory modules from partially-good DRAM chips soldered to its substrate. The partially-good DRAM chips have a number of defective memory cells that is below a test threshold, such as 10%. Packaged DRAM chips are optionally pre-screened and considered to pass when the number of defects found is less than the test threshold. A defect table is created during testing and written to a serial-presence-detect electrically-erasable read-only memory (SPD-EEPROM) on the memory module. The memory module is finally tested on a target-system tester that reads the defect table during booting, and redirects memory access to defective memory locations identified by the defect table. The memory modules may be burned in or tested at various temperatures and voltages to increase reliability.

Owner:KINGSTON DIGITAL CO LTD

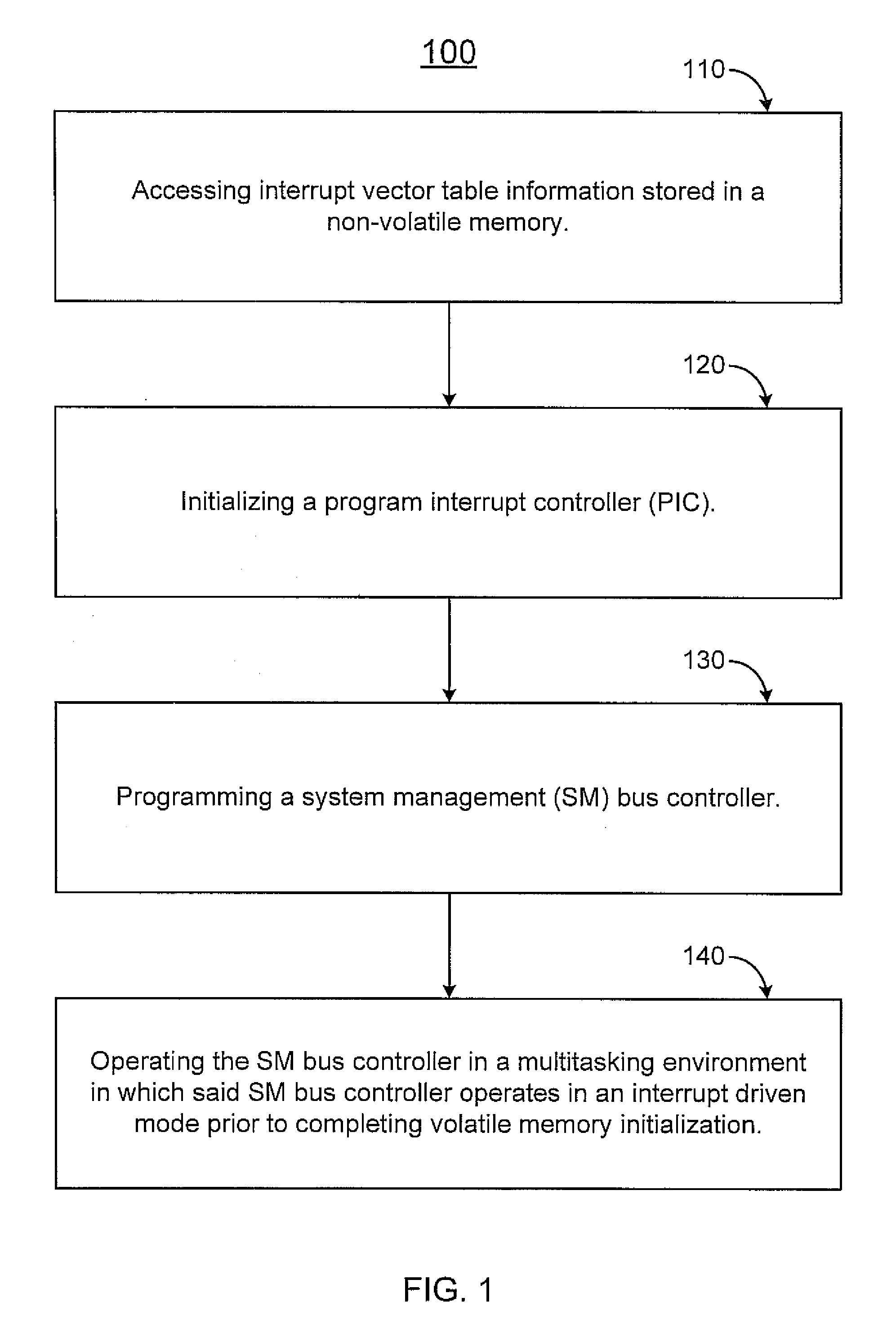

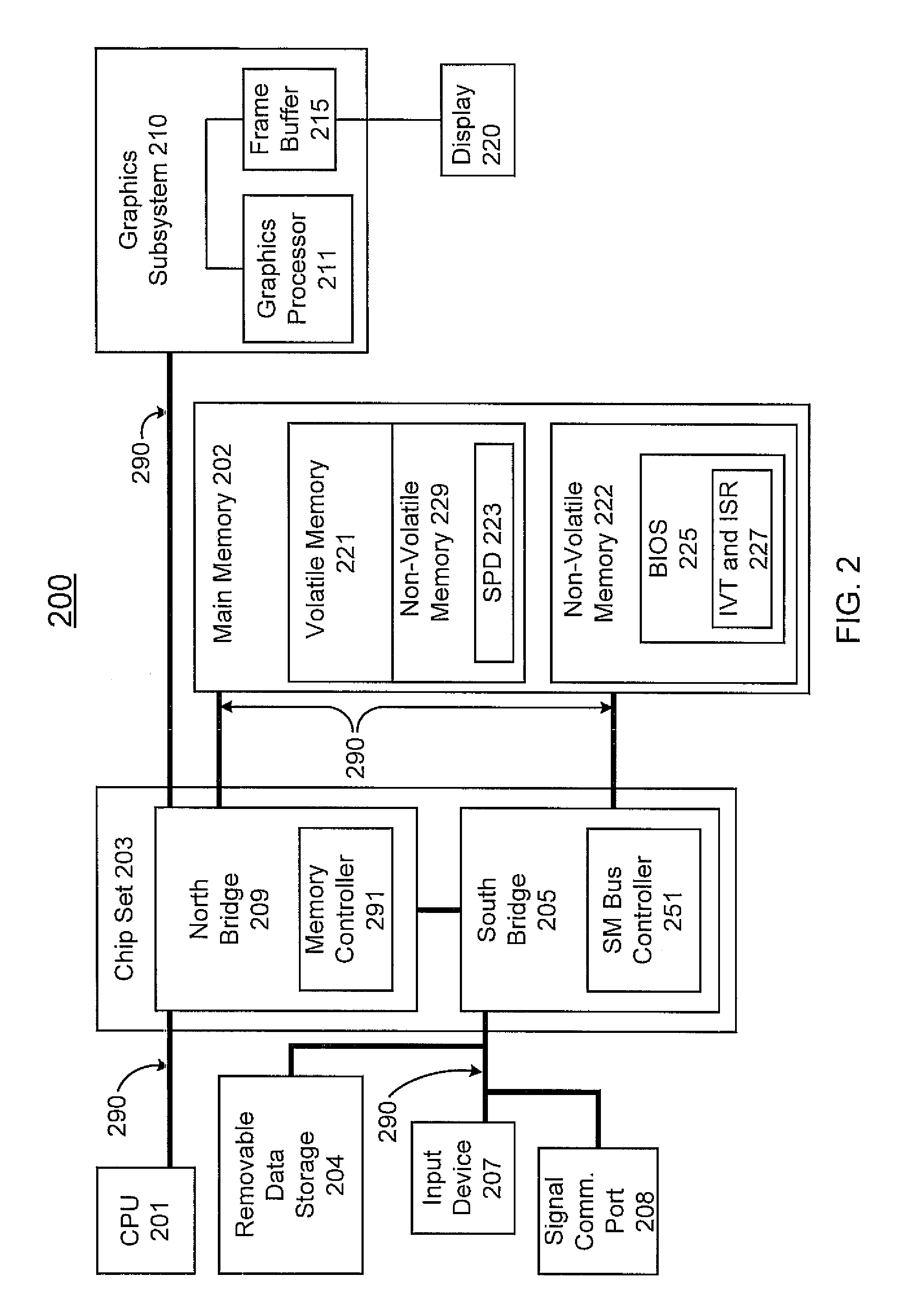

Multi-tasking bootstrap system and method

A multi-task boot strap system and method for expediting boot up initialization processes are presented. In one embodiment, a multi-task boot strap method includes accessing interrupt vector table information stored in a non-volatile memory. For example, an interrupt vector table and corresponding interrupt service routine information associated with a system management (SM) bus controller operation are accessed from a read only memory (ROM). A program interrupt controller (PIC) is initialized to interpret the interrupt information from the non-volatile memory. This permits the operation of the system management bus controller to be performed in a multi-tasking environment (e.g., operating the SM bus controller in an interrupt mode). A processor can be configured to retrieve the boot up information (e.g., serial presence detect data) and process interrupts with interrupt service routine information retrieved from non-volatile memory. The processor can performing other multi-task operations while waiting for an interrupt during boot up operations.

Owner:NVIDIA CORP

Method for manufacturing memory module by using defect list of electrically-erasable programmable read-only memory

The invention provides a method for manufacturing a memory module by using a defect list of an electrically-erasable programmable read-only memory. In the method, the memory module is manufactured by welding a partially-good dynamic random access memory chip on a memory module base plate; the partially-good dynamic random access memory chip is provided with defect memory units, of which the number is smaller than a detection threshold value(for example 10 percent); the packaged dynamic random access memory chips are randomly pre-screened, and when the number of defected ones is smaller than the detection threshold value, the detection is passed; during the detection period, a defect list is generated and written in a serial presence detection electrically-erasable programmable read-only memory of the memory module; and when a machine is started, a target system detector reads the defect list, the memory module performs the final detection on the target system detector and redirects the positions of the defect memories identified in the memory access defect list. The memory can complete the detection by burning or at different temperatures and voltages, so that the reliability of the memory is improved.

Owner:KINGSTON TECHNOLOGY (SHANGHAI) CO LTD

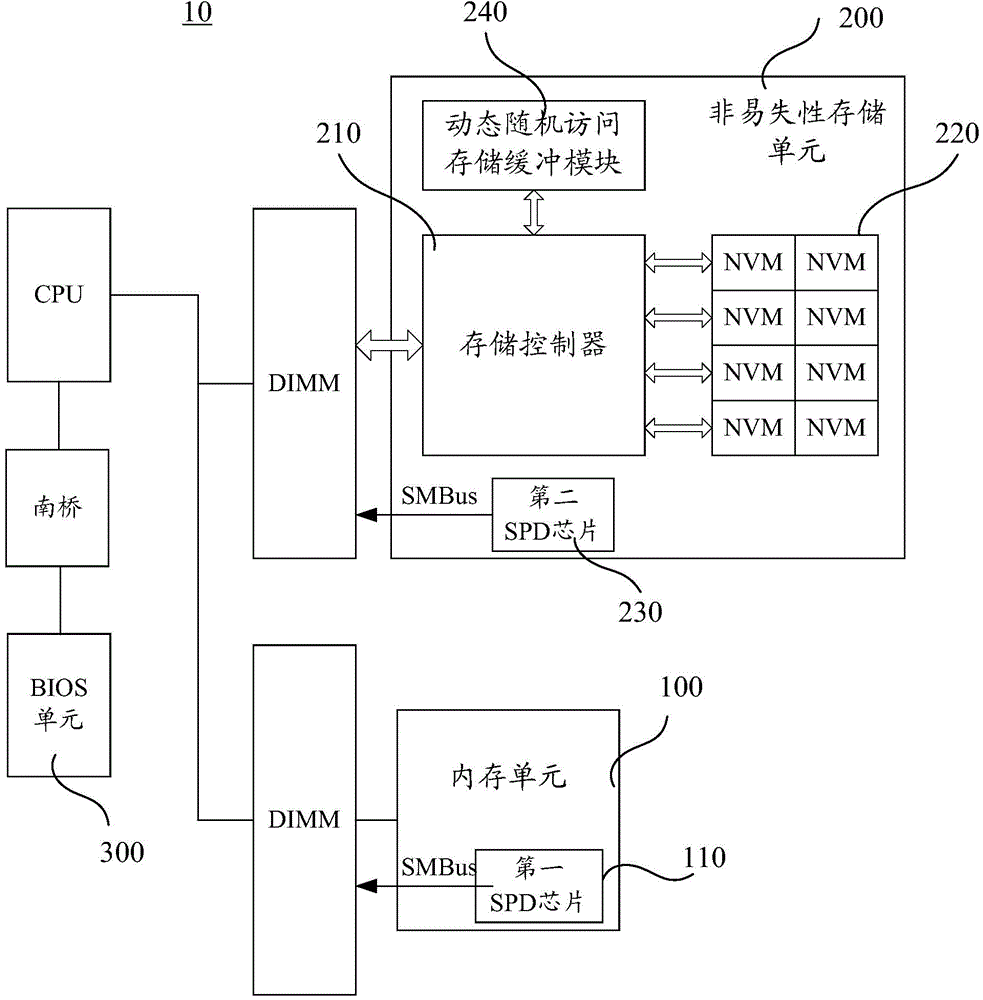

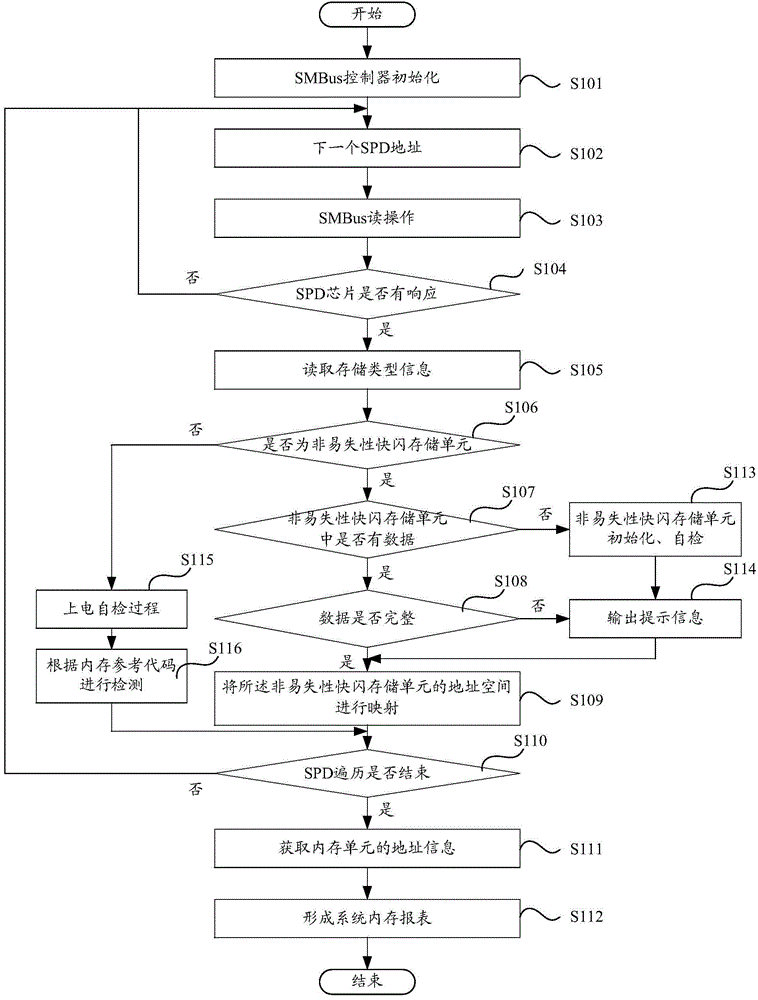

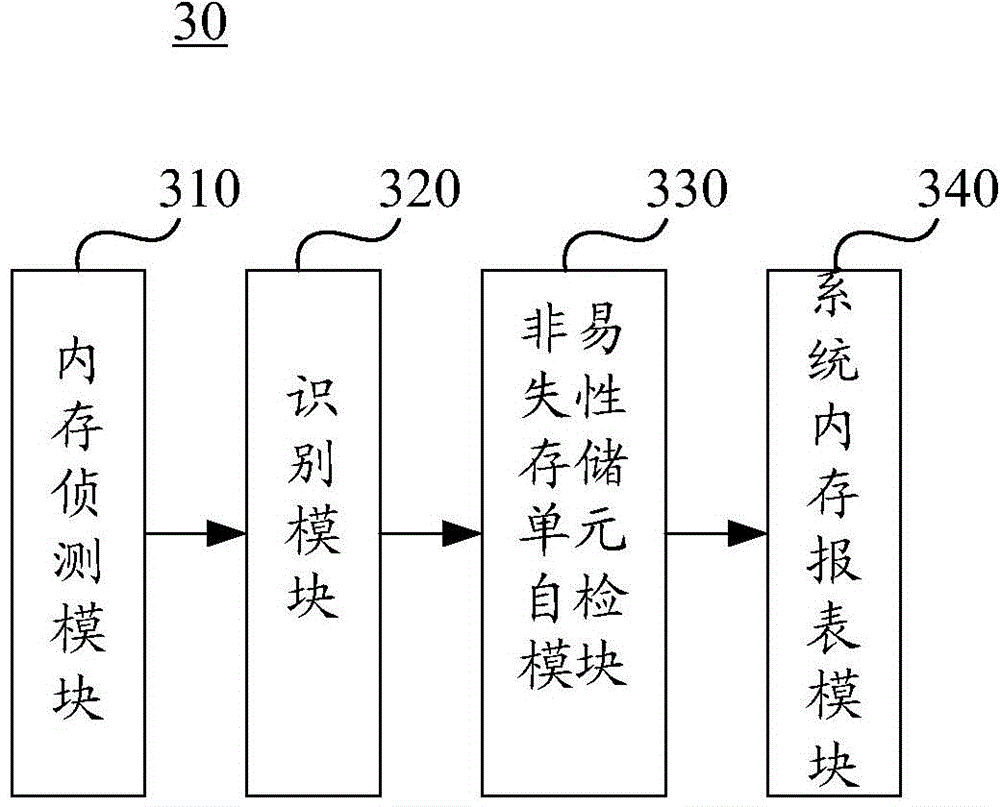

Computer system of heterogeneous hybrid memory architecture, control method of computer system and memory detection system

InactiveCN105786716ABalance costImprove read and write speedInput/output to record carriersMemory adressing/allocation/relocationDIMMMemory type

The invention relates to a computer system of heterogeneous hybrid memory architecture. The computer system comprises a memory unit, a non-volatile memory unit and a basic input and output system BIOS unit, wherein the memory unit comprises a first serial presence detect SPD chip and accesses the computer system through a dual inline memory module DIMM interface, and the first SPD chip comprises memory capacity information of the memory unit; the non-volatile memory unit comprises a second SPD chip and accesses the computer system through a DIMM interface, and the second SPD chip comprises memory capacity and memory type information of the non-volatile memory unit; the BIOS unit is used for acquiring capacity information of the second SPD chip at a power on self-test POST stage and then forming a system memory report by the capacity information of the second SPD chip and the memory capacity information of the memory unit. The invention further relates to a control method for the computer system and a memory detection system in the computer system. According to the computer system, the control method and the memory detection system, the whole computer system obtains a certain degree of balance on reading and writing speed and costs.

Owner:EVOC INTELLIGENT TECH

Serial presence detect functionality on memory component

InactiveUS7263019B2Multiplex system selection arrangementsFinal product manufactureComputer hardwareSerial presence detect

Methods and apparatus for accessing serial presence detect data are provided. For some embodiments, serial presence detect logic is incorporated in memory devices, eliminating the need for a separate serial presence detect component.

Owner:POLARIS INNOVATIONS LTD

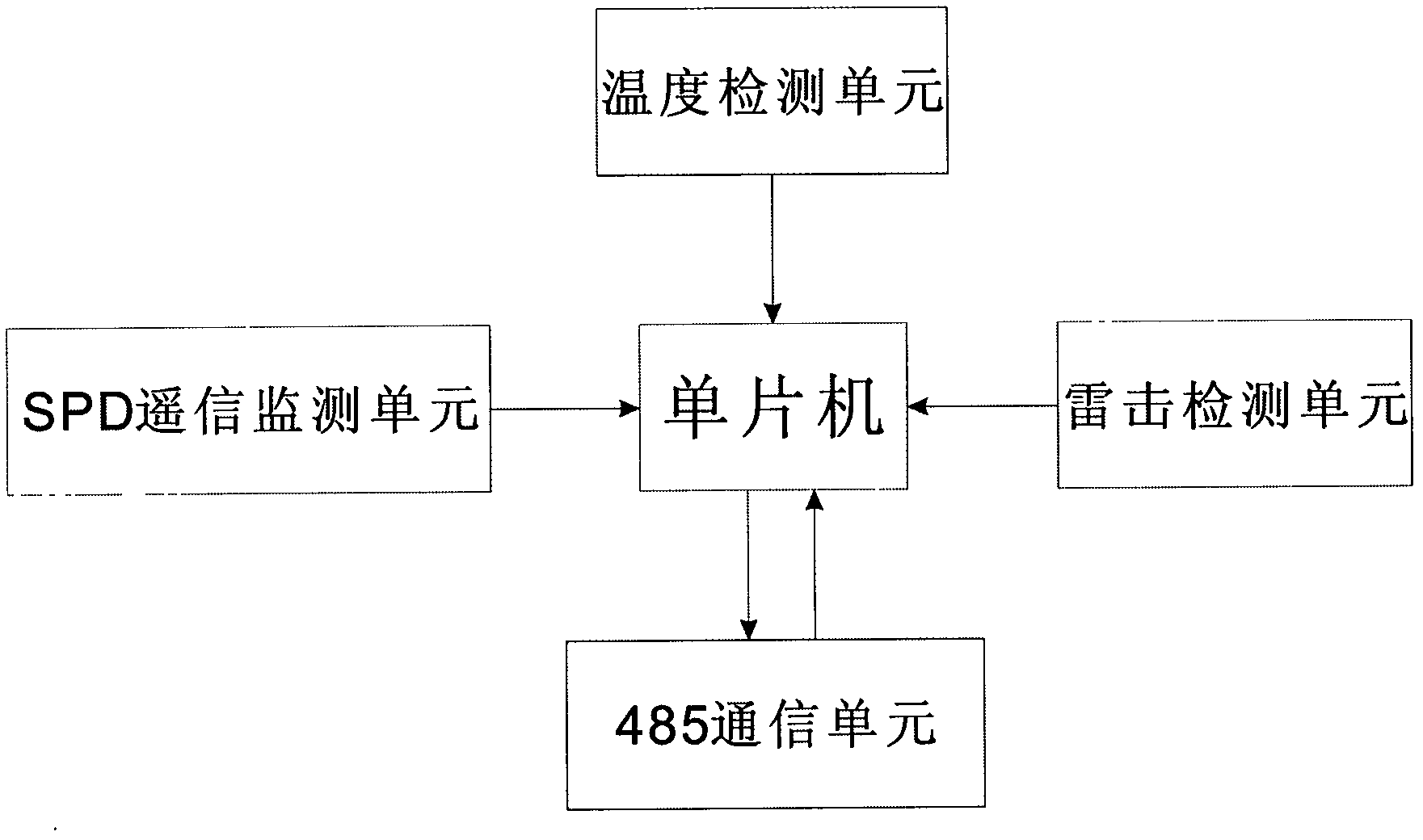

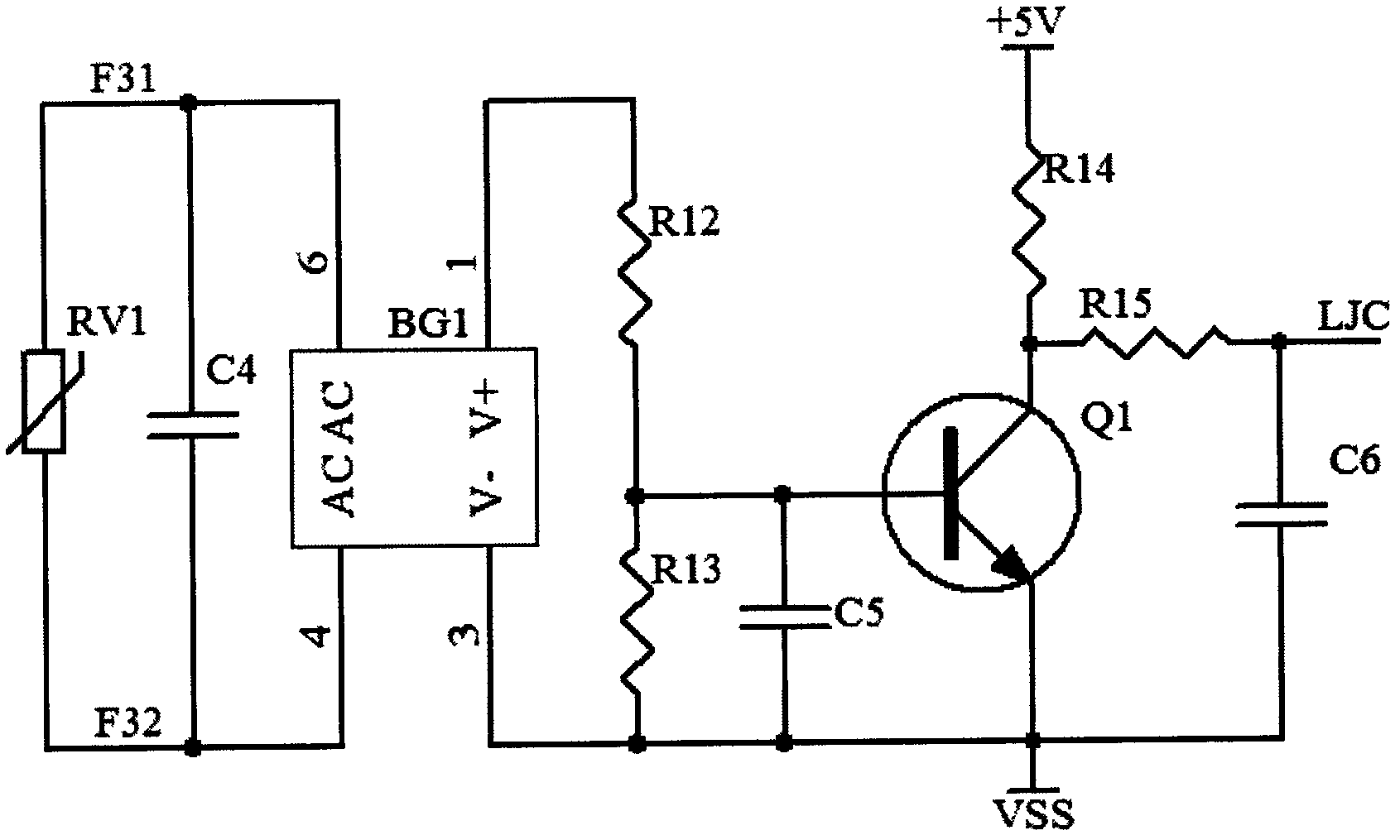

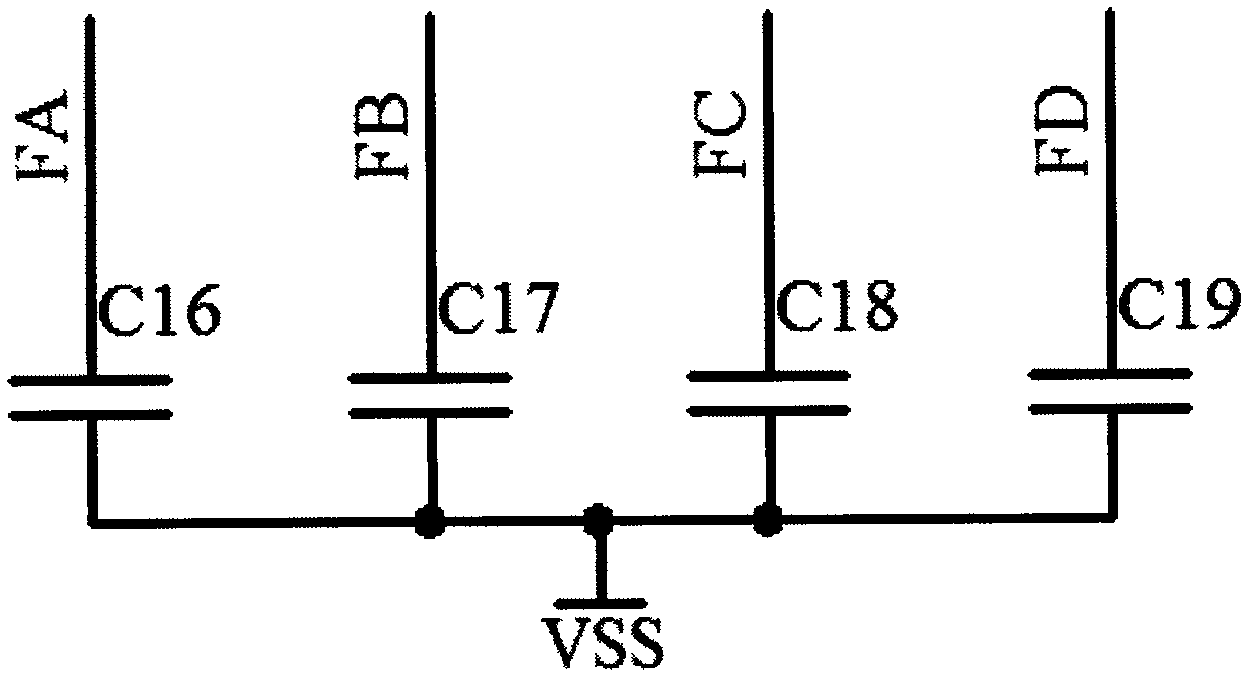

Intelligent lightning stroke monitoring device

InactiveCN102650653ARealize real-time monitoring functionReduce security impactCurrent/voltage measurementMicrocontrollerCommunication unit

The invention relates to an intelligent lightning stroke monitoring device comprising a singlechip microcomputer control unit module, an SPD (Serial Presence Detect) remote signaling monitoring unit module, a temperature detecting unit module, a lightning stroke detecting unit module and an RS485 communication unit module. According to the intelligent lightning stroke monitoring device, the singlechip microcomputer control unit module is used for controlling the SPD remote signaling monitoring unit module, the temperature detecting unit module, the lightning detecting unit module and the RS485 communication unit module; the temperature detecting unit module is initialized by the singlechip microcomputer control unit module and then can automatically work to detect the temperature of the surrounding environment, when the corresponding temperature property is detected, signals transmits data to the singlechip microcomputer control unit module in high-level digital signal codes and low-level digital signal codes, and the singlechip microcomputer control unit module judges the currently detected temperature according to the group of codes. The intelligent lightning stroke monitoring device disclosed by the invention realizes the real-time monitoring function.

Owner:上海金临电子科技有限公司

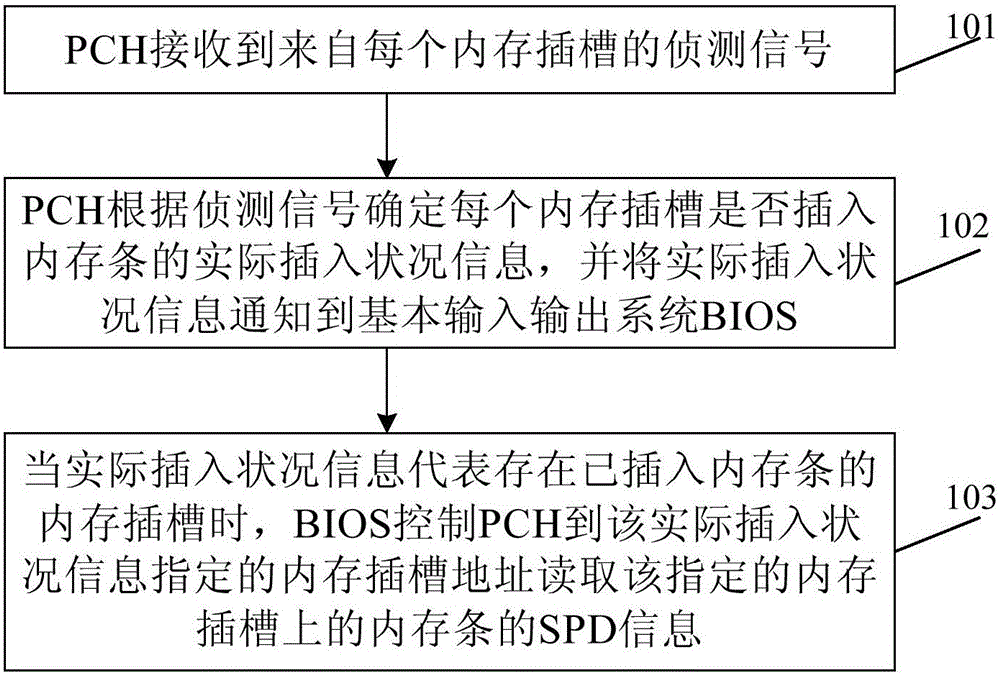

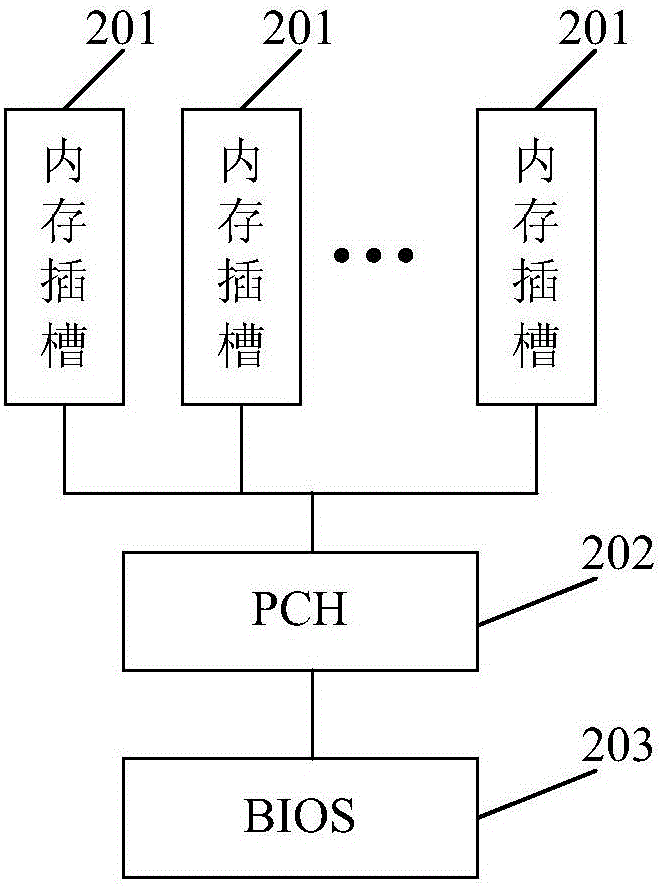

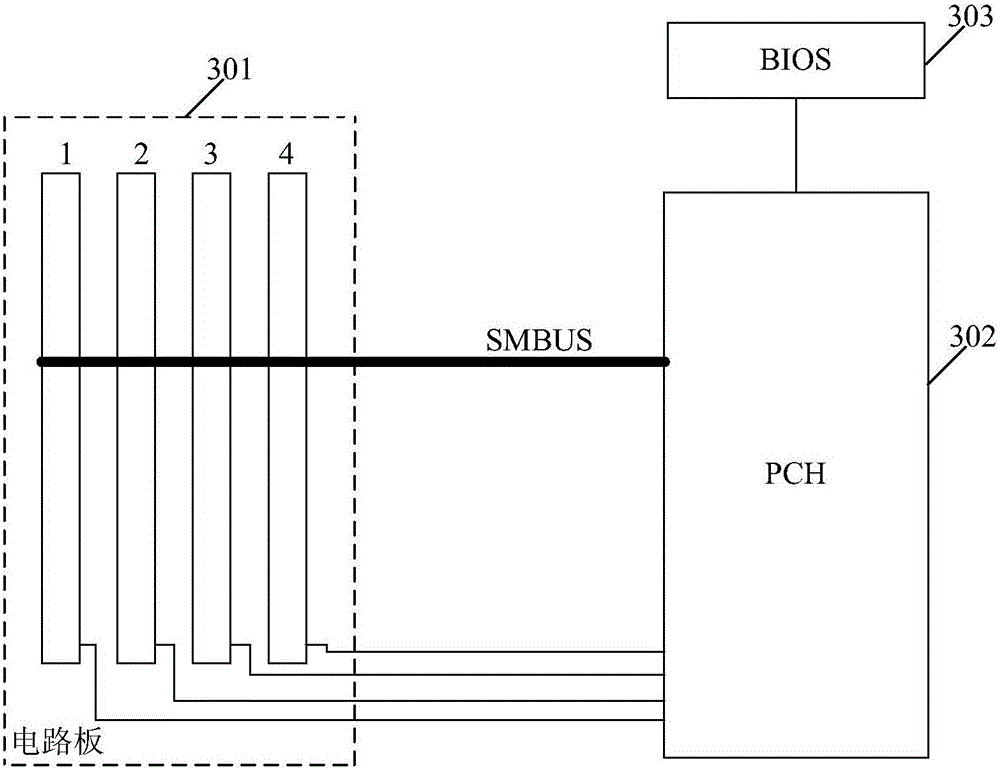

Method and system for detecting number of memory banks on circuit board

ActiveCN106547655AAcquisition speed is fastFast startupDetecting faulty computer hardwareElectricityMemory bank

The invention provides a method and a system for detecting the number of memory banks on a circuit board. A detection pin of each memory slot is electrically connected to a platform controller hub PCH, so as to output a detection signal for detecting whether a memory bank is inserted in the memory slot to the PCH. The method comprises the following steps: receiving the detection signal from each memory slot by the PCH; determining actual insert status information of whether the memory bank is inserted in each memory slot by the PCH according to the detection signal, and notifying a BIOS (Basic Input Output System) of the actual insert status information; and when the actual insert status information represents that the memory slot in which the memory bank has been inserted exists, then controlling the PCH to read SPD (Serial Presence Detect) information of a memory bank on the designated memory slot from a memory slot address designated by the actual insert status information by the BIOS. The method for detecting the number of the memory banks on the circuit board provided by the invention can effectively improve the acquisition speed of the SPD information, thereby effectively improving the starting speed of a computer system.

Owner:广东龙芯中科电子科技有限公司

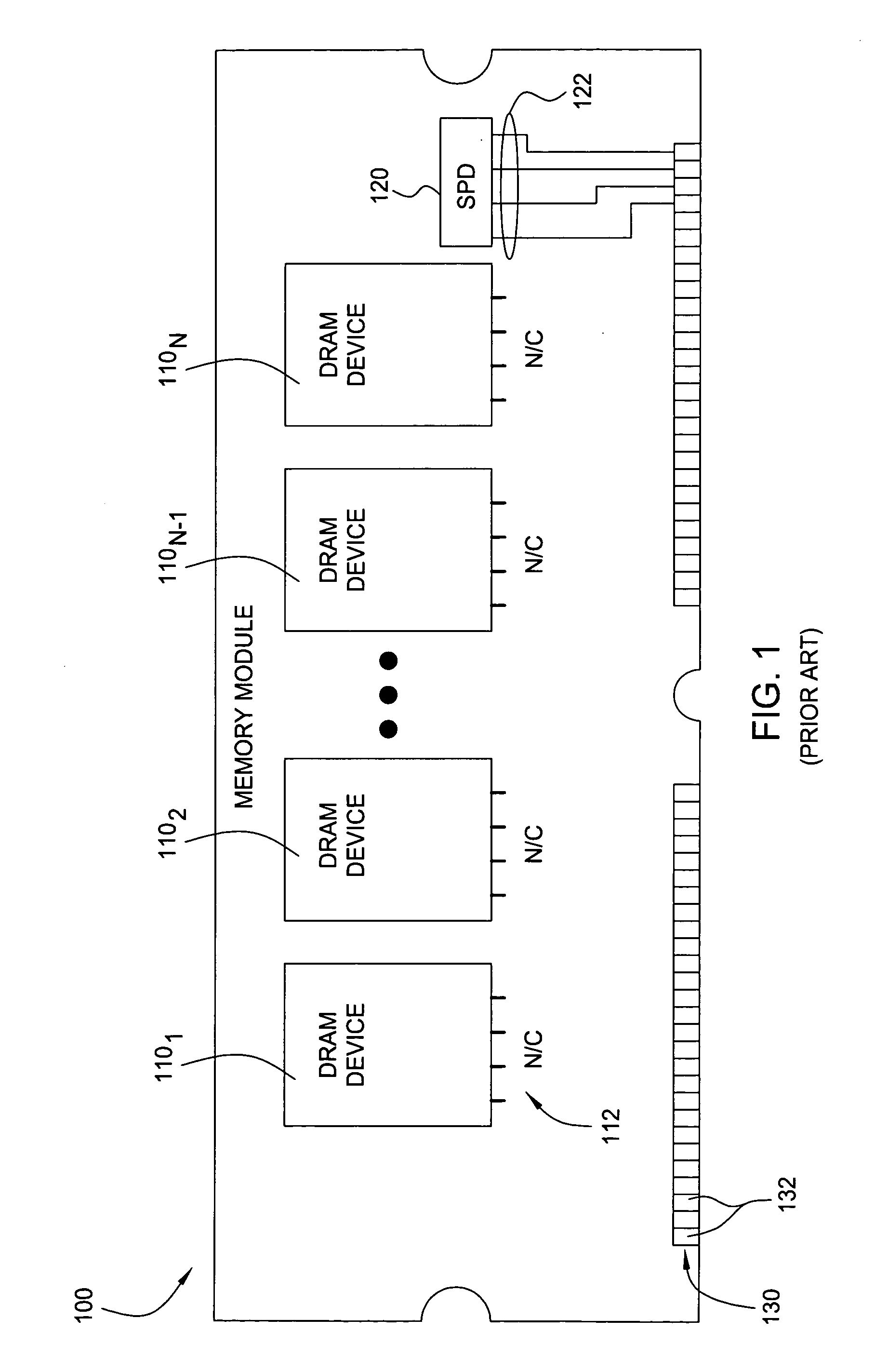

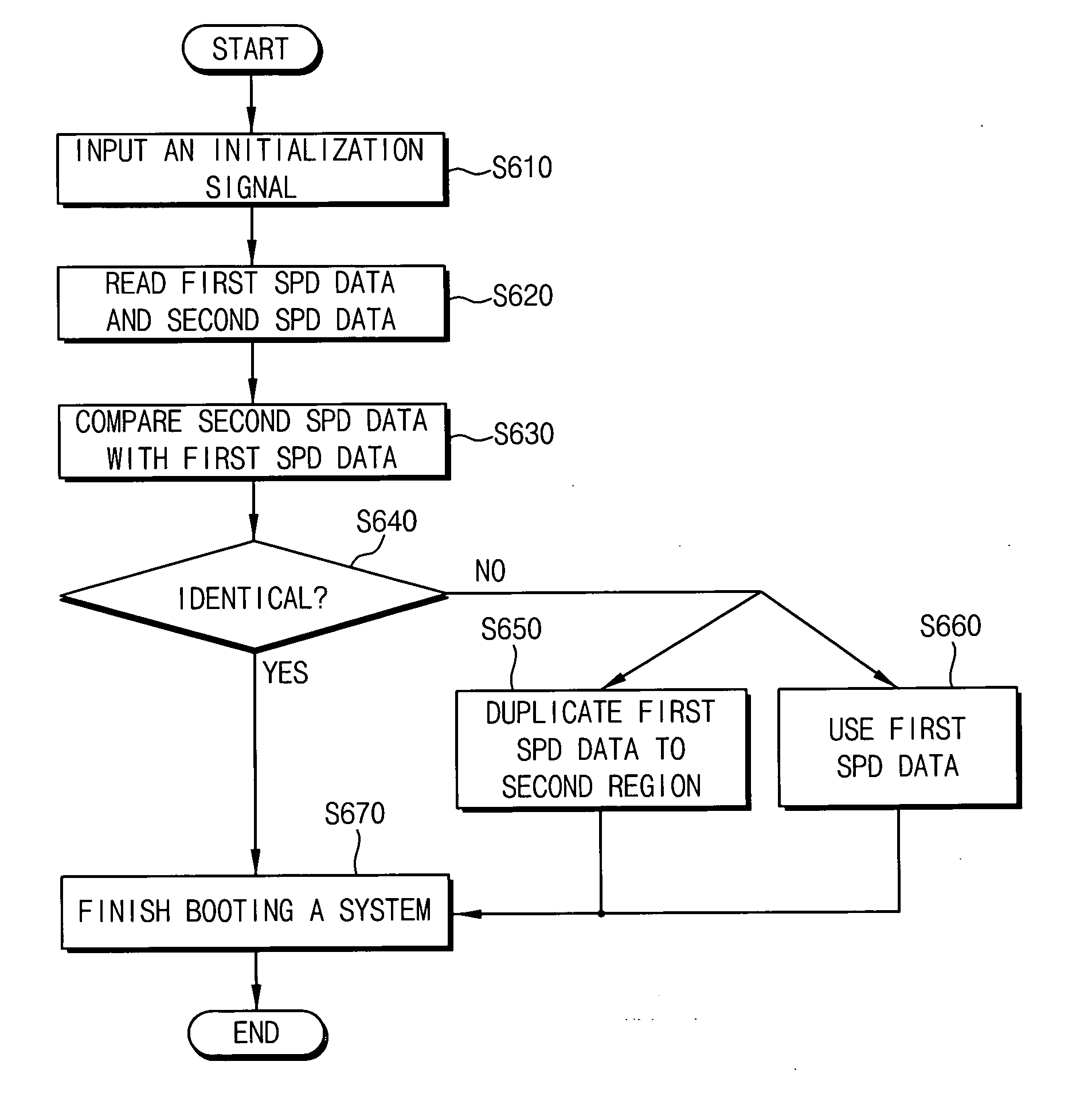

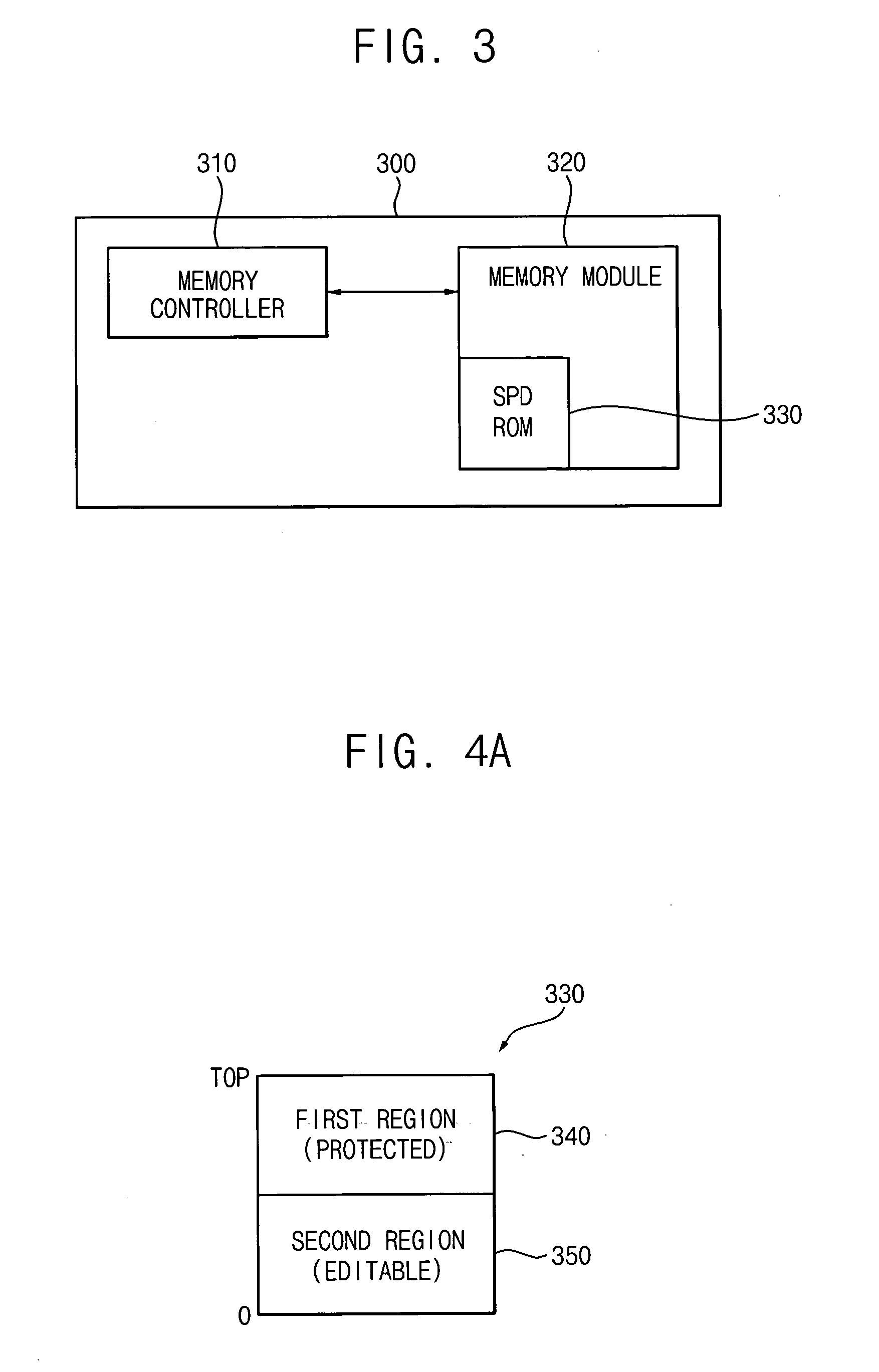

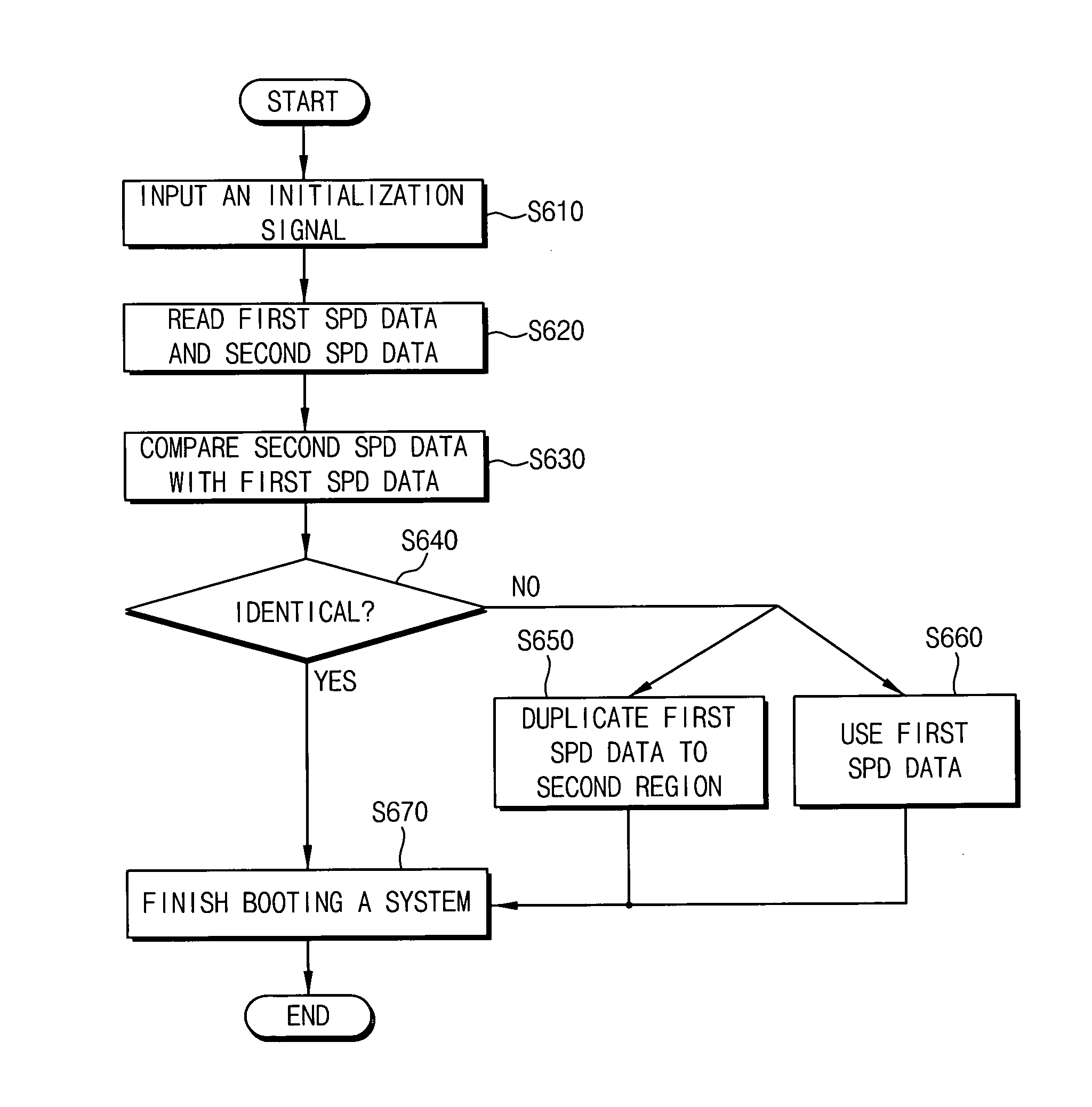

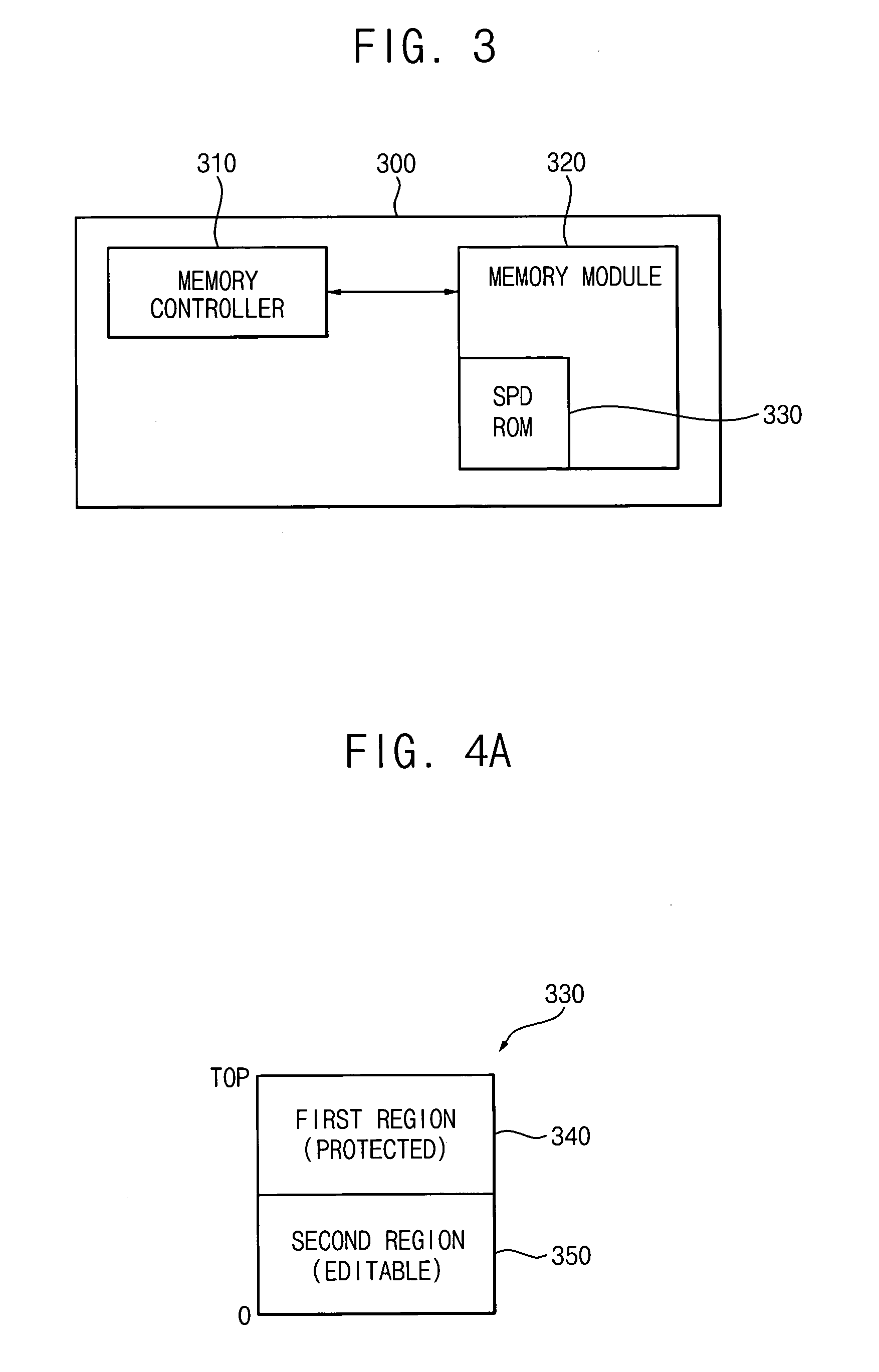

Memory module system using a partitioned serial presence detect memory

InactiveUS20080162867A1Problem be addressDigital computer detailsBootstrappingSerial presence detectMemory controller

A memory module system may include a serial presence detect (SPD) memory and a memory controller. The SPD memory may store first SPD data and second SPD data of a memory module. The SPD memory may be partitioned into at least two regions that may operate as multiple SPD ROMs. The memory controller may boot the memory module system based on a comparison between the first SPD data and the second SPD data when an initialization signal is input to the memory module system. The memory module system may be booted stably and may prevent system breakdowns.

Owner:SAMSUNG ELECTRONICS CO LTD

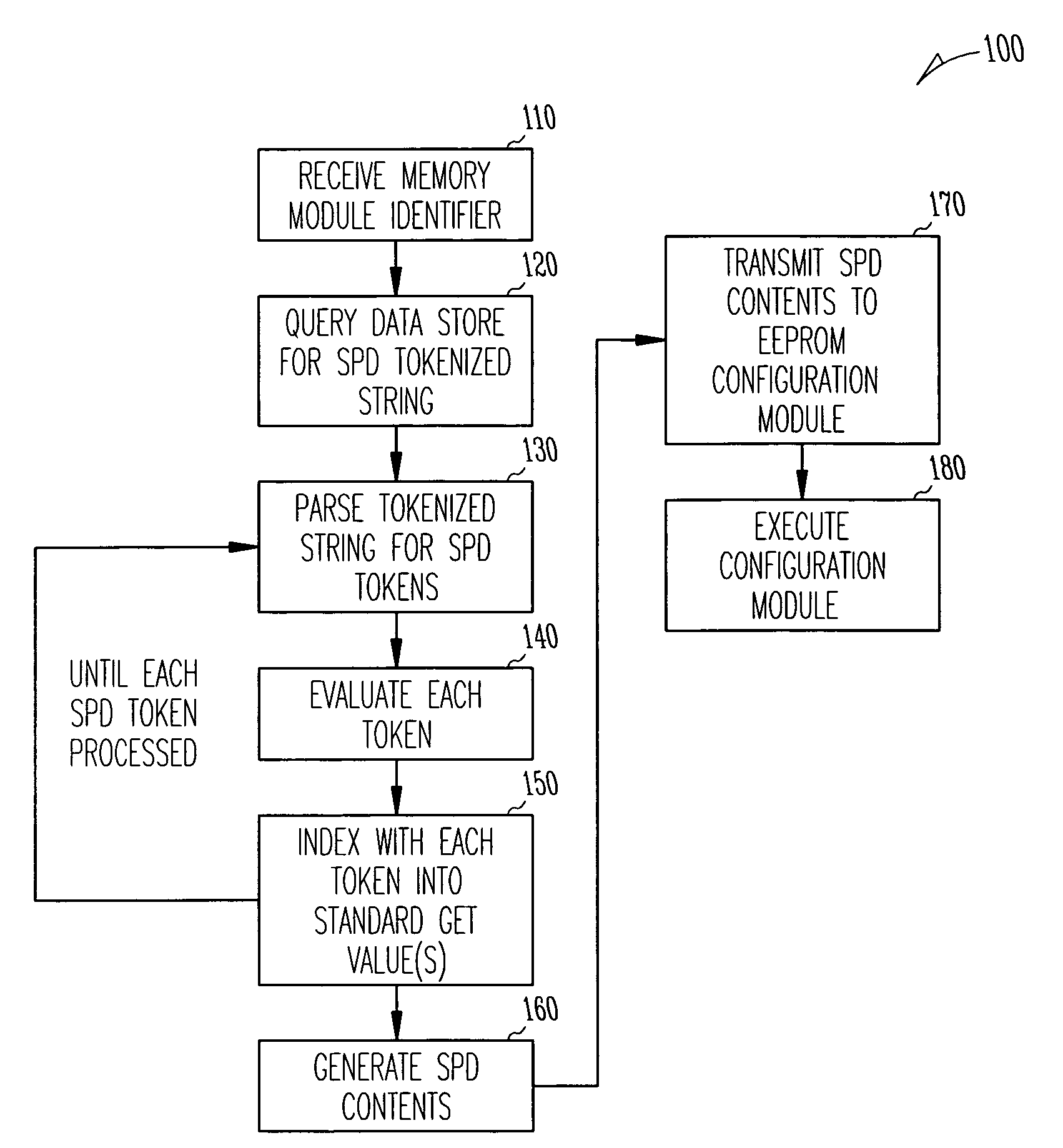

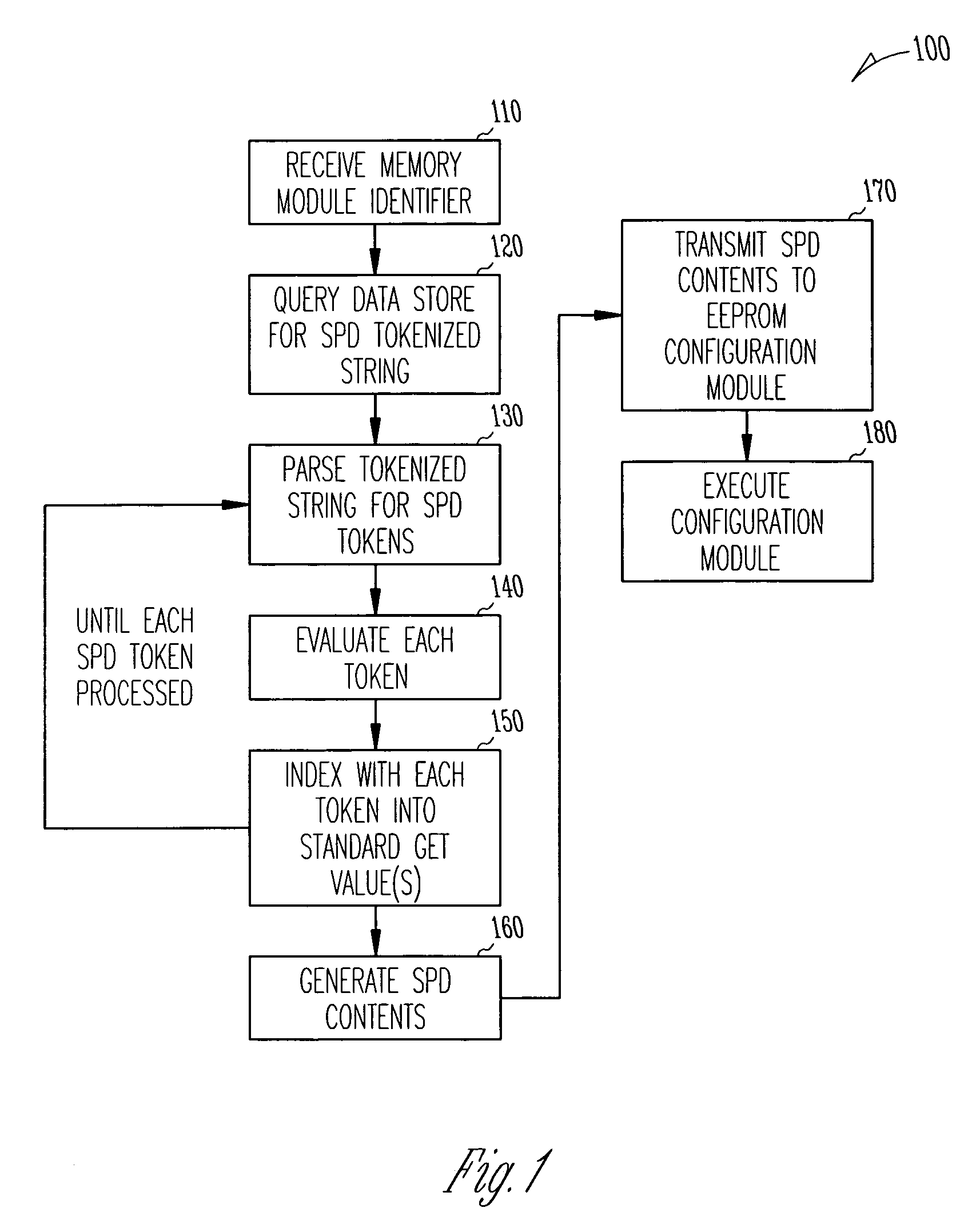

Techniques for generating serial presence detect contents

ActiveUS7152139B1Efficient processingRead-only memoriesDigital storageElectricityProgrammable read-only memory

Owner:MICRON TECH INC

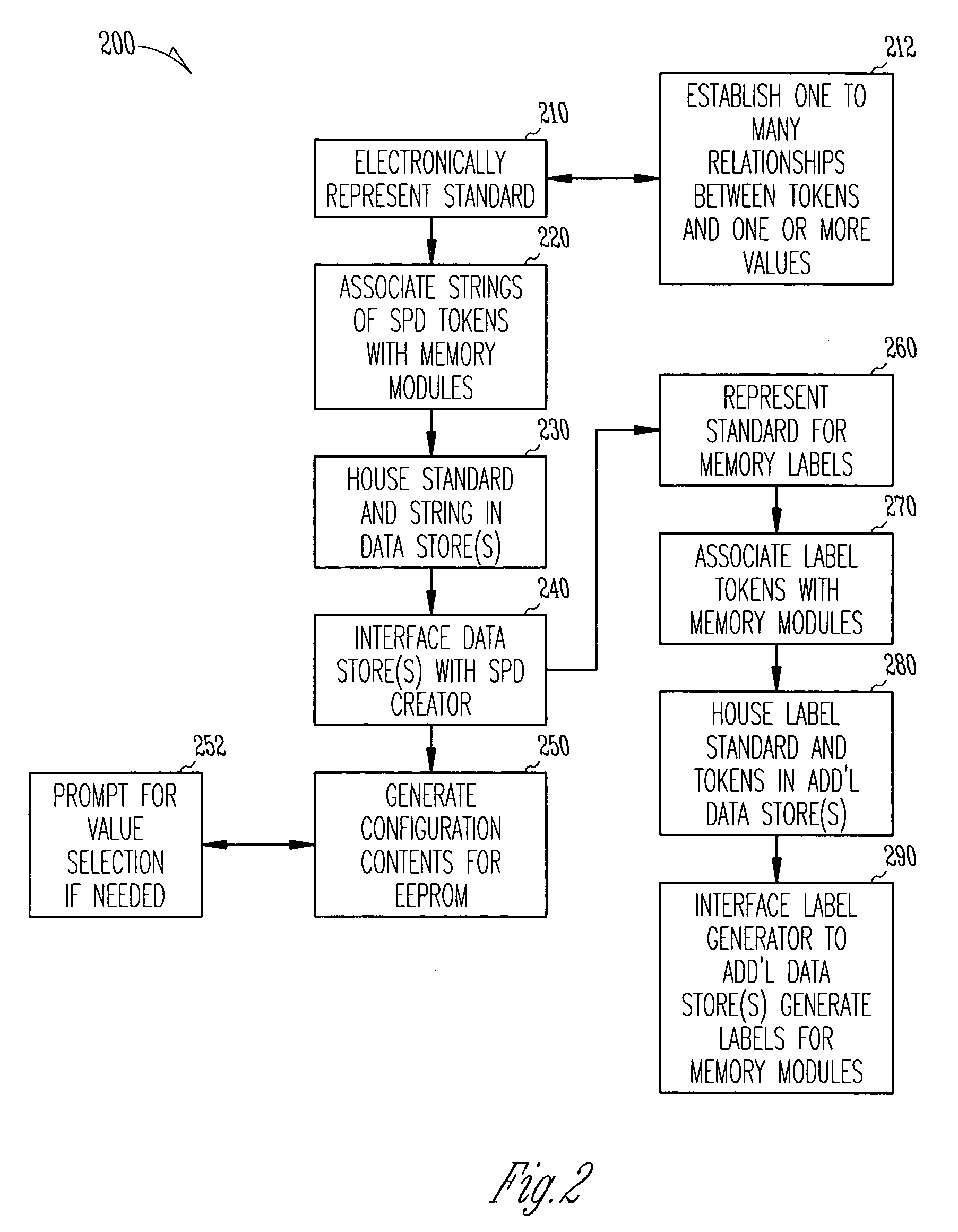

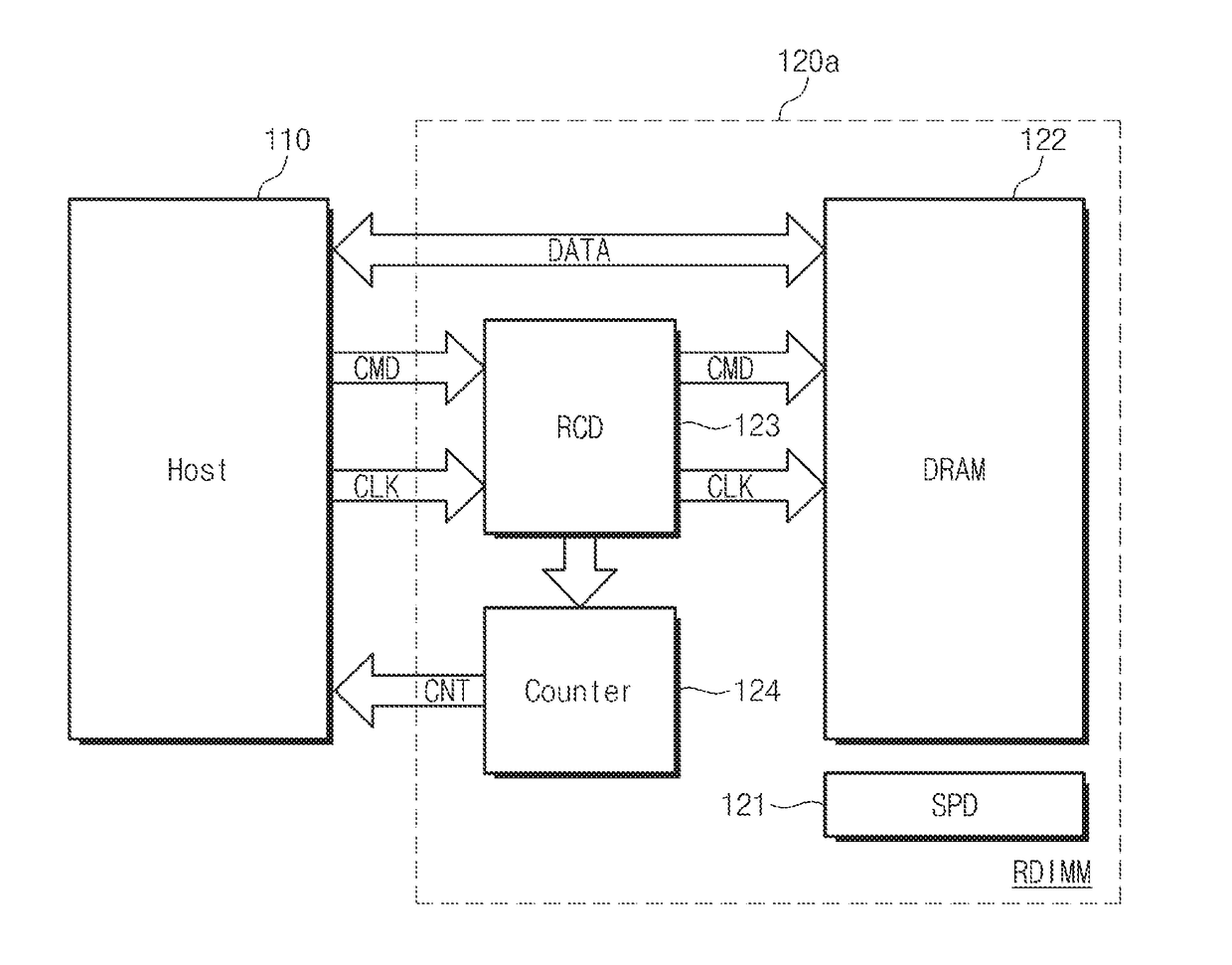

Memory module monitoring memory operation and power management method thereof

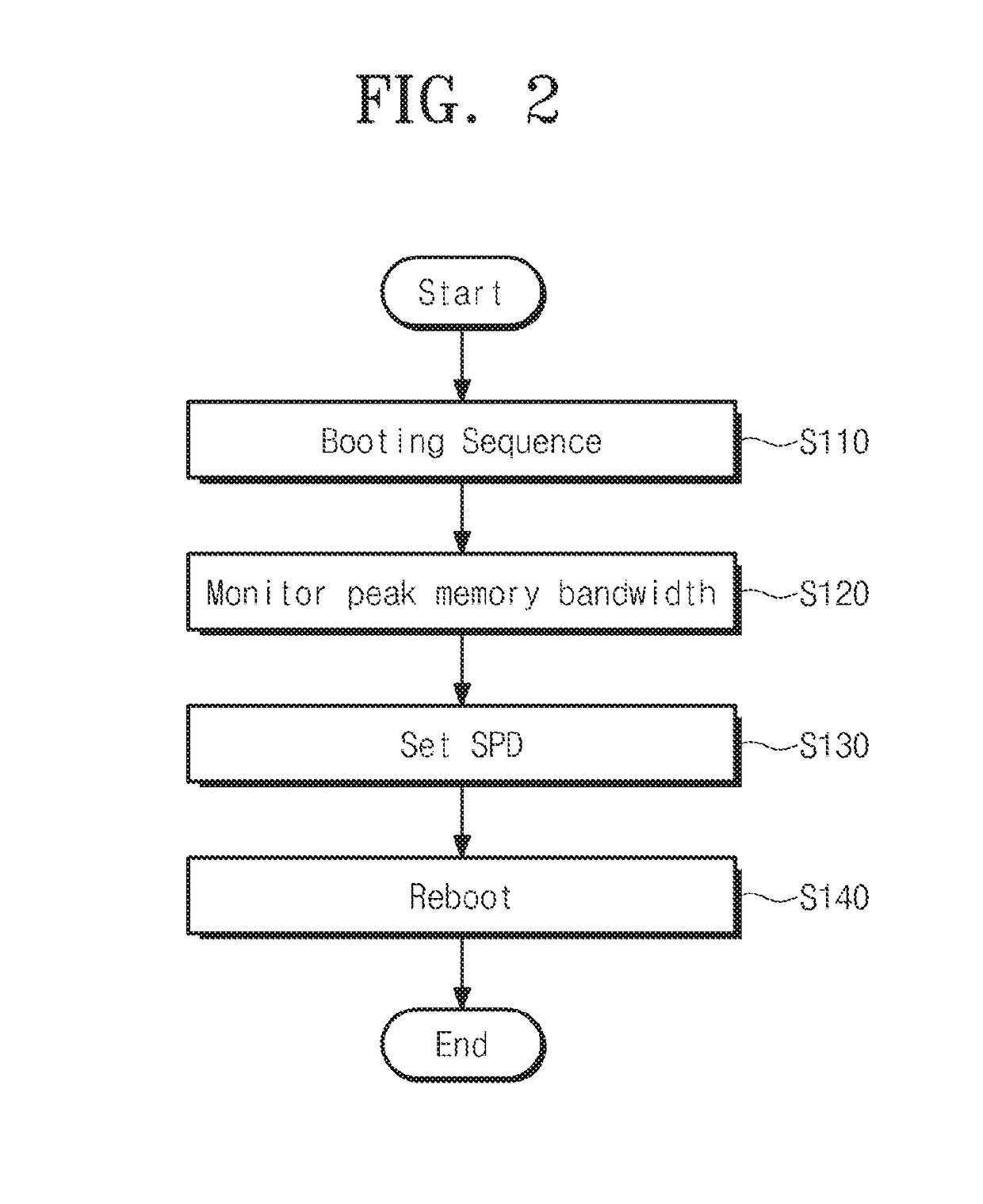

ActiveUS20170115915A1Improve power efficiencyInput/output to record carriersDigital storageComputer moduleSerial presence detect

A memory module includes a counter configured to count a number of commands received from a host to generate a counted number and provide the counted value to the host, a memory device configured to receive an operating frequency and an operating voltage from that host that are determined based on the counted number, and a serial presence detect (SPD) configured to store the operating frequency and operating voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

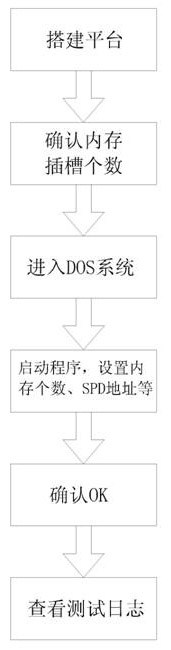

Method for testing stability of internal storage under DOS (Disk Operating System)

InactiveCN102193851AImprove work efficiencySave R&D and testing timeDetecting faulty computer hardwareSoftware engineeringSerial presence detect

The invention provides a method for testing the stability of an internal storage under a DOS (Disk Operating System). The testing process mainly comprises the following steps of: establishing a testing platform; entering a DOS interface to set testing time, the quantity of internal storage slots, each SPD (Serial Presence Detect) address and the name of an output log file; and checking a testing log after testing. Compared with the prior art, the method for testing the stability of the internal storage under the DOS has the characteristics of reasonable testing steps, safety, reliability, comprehensive check, rapidness for maintenance and the like; and the stability of the internal storages of different mainboards can be tested conveniently, the testing requirement is met, the research and development testing time is saved, the overall testing time is easy to arrange reasonably, and attended testing is not required, thus the working efficiency of developing personnel is increased.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Rank and page remapping logic in a volatile memory

ActiveUS9804920B2Memory architecture accessing/allocationDigital storageSerial presence detectMemory rank

Embodiments of the inventive concept include a plurality of memory ranks, a buffer chip including a rank remap control section configured to remap a rank from among the plurality of memory ranks of the volatile memory module responsive to a failure of the rank, and a dynamic serial presence detect section configured to dynamically update a stated total capacity of the volatile memory module based at least on the remapped rank. In some embodiments, a memory module includes a plurality of memory ranks, an extra rank in addition to the plurality of memory ranks, the extra rank being a spare rank configured to store a new page corresponding to a failed page from among the plurality of ranks, and a buffer chip including a page remap control section configured to remap the failed page from among the plurality of ranks to the new page in the extra rank.

Owner:SAMSUNG ELECTRONICS CO LTD

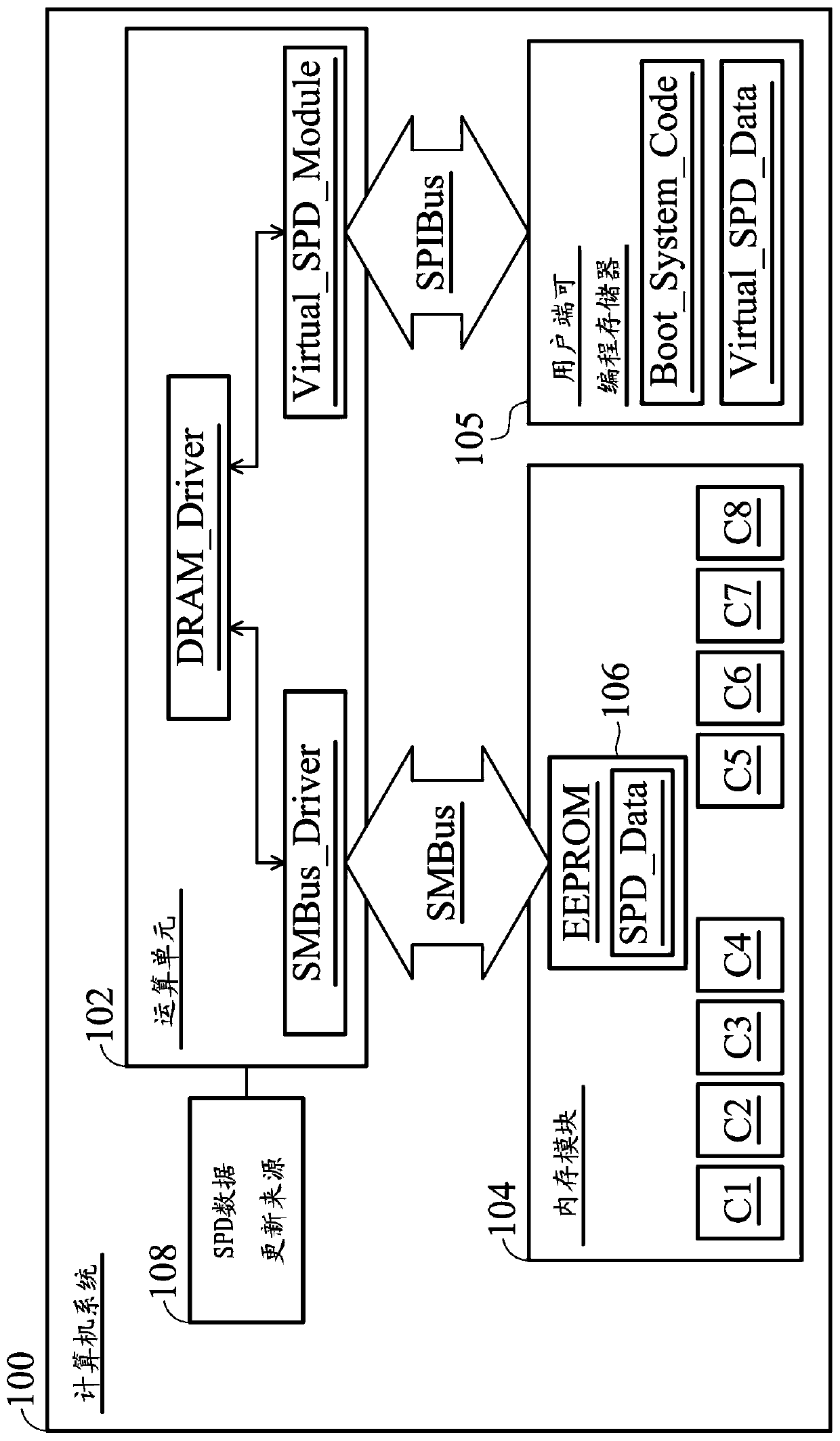

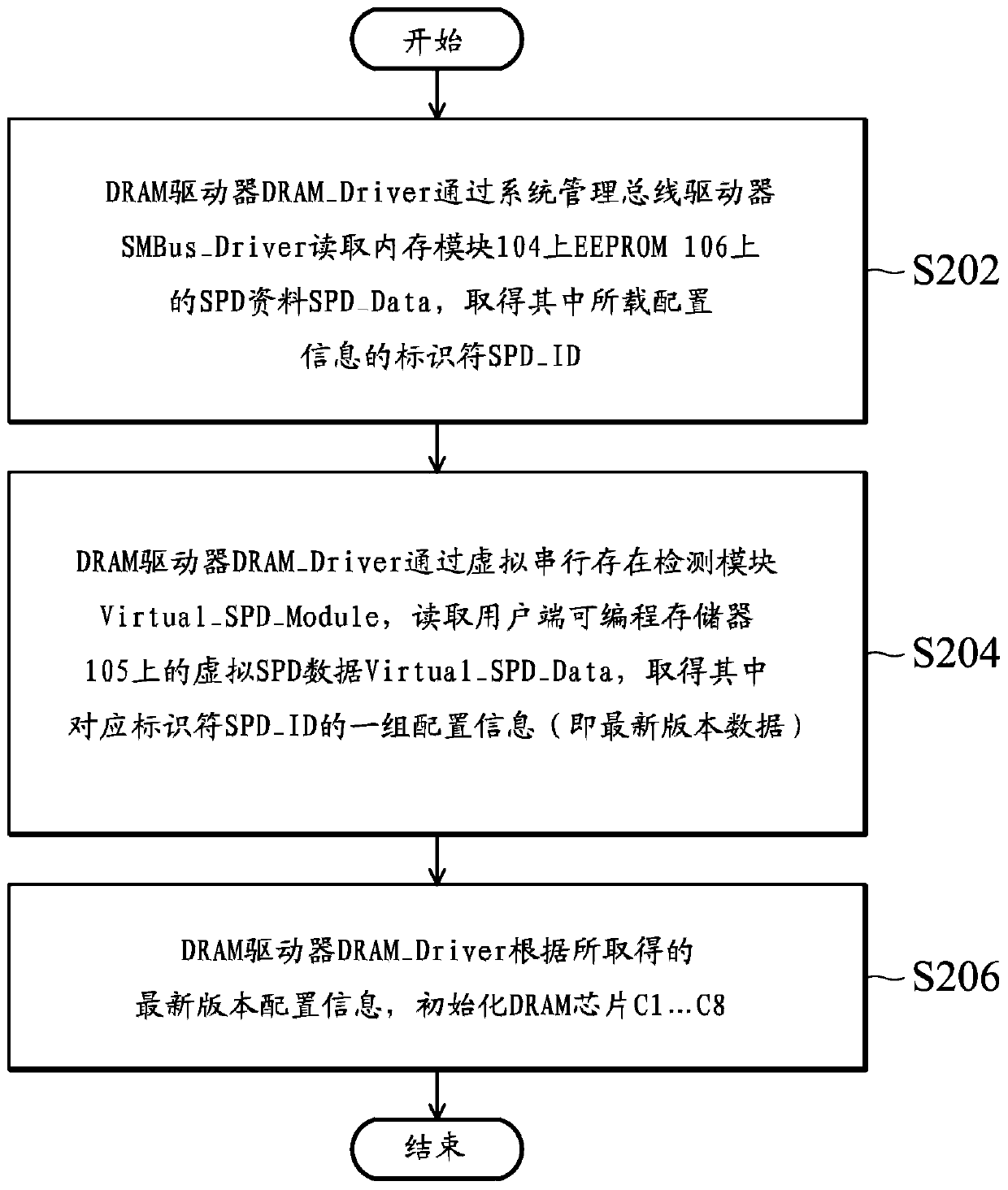

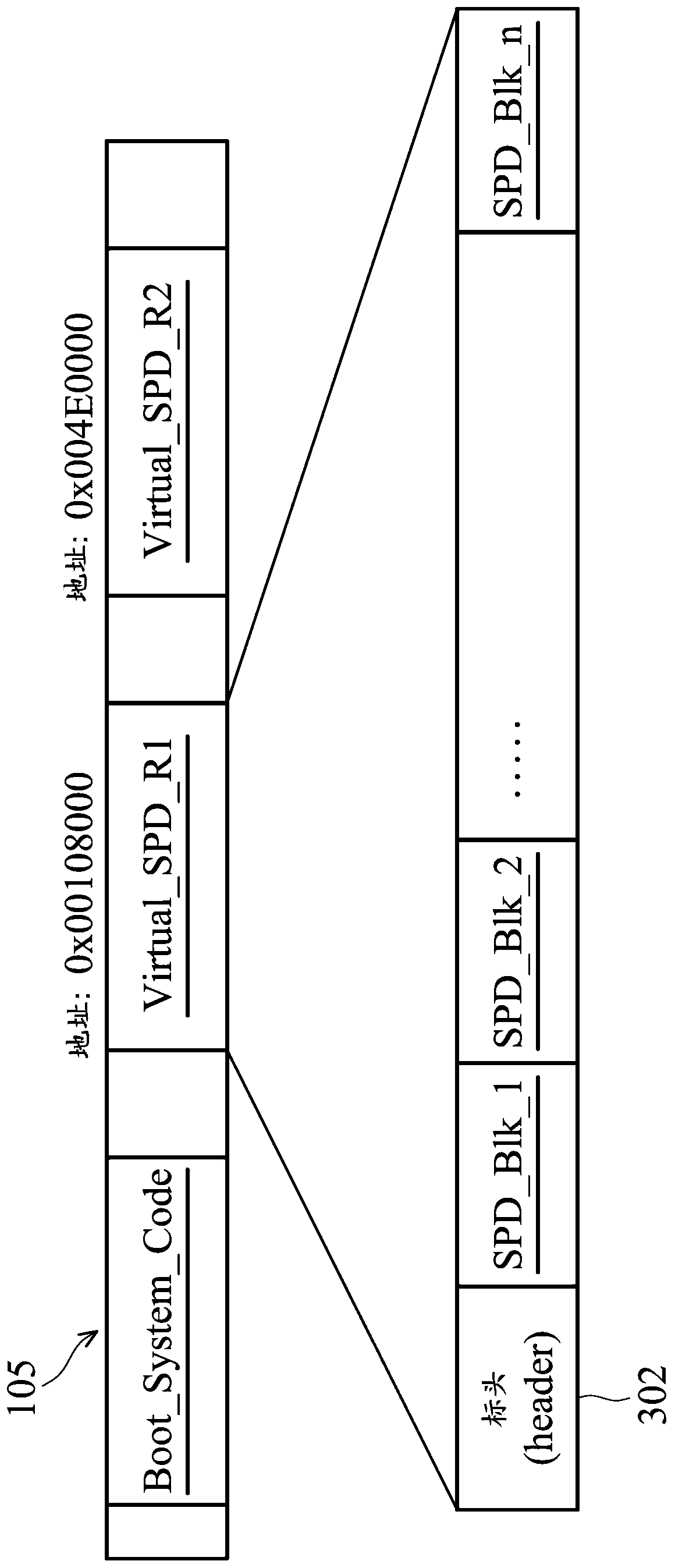

Computer system with serial presence detection data and memory module control method

A computer system with updatable serial presence detection data stores a virtual serial presence detection data with a client programmable memory. The virtual serial presence detection data comprisesconfiguration information of a memory module, and the storage of the virtual serial presence detection data is separated from a boot system code. An operation unit runs a memory driver for the memorymodule, and the memory driver reads the virtual serial existence detection data on the client programmable memory through a virtual serial existence detection module to obtain the configuration information of the memory module.

Owner:VIA ALLIANCE SEMICON CO LTD

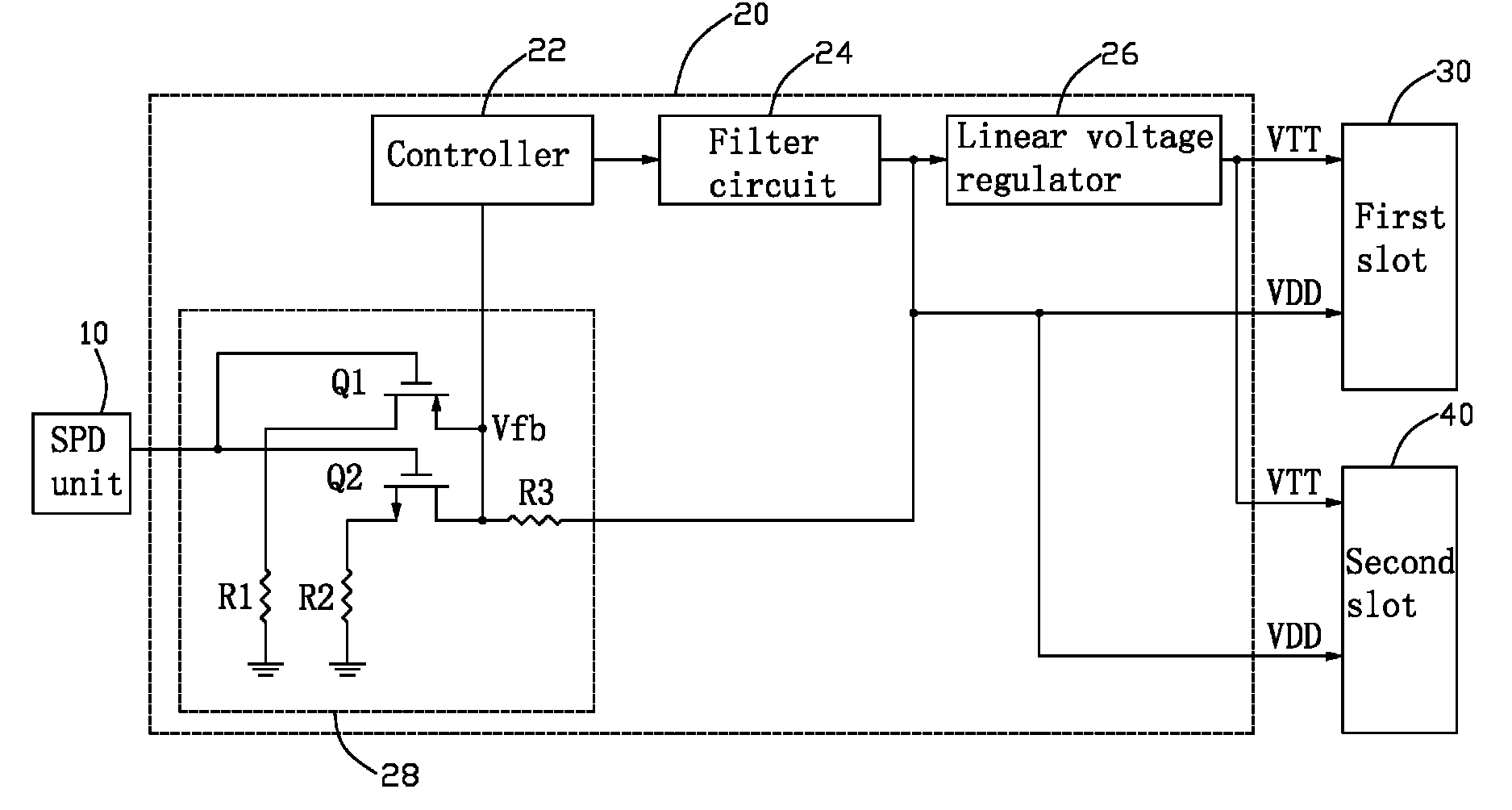

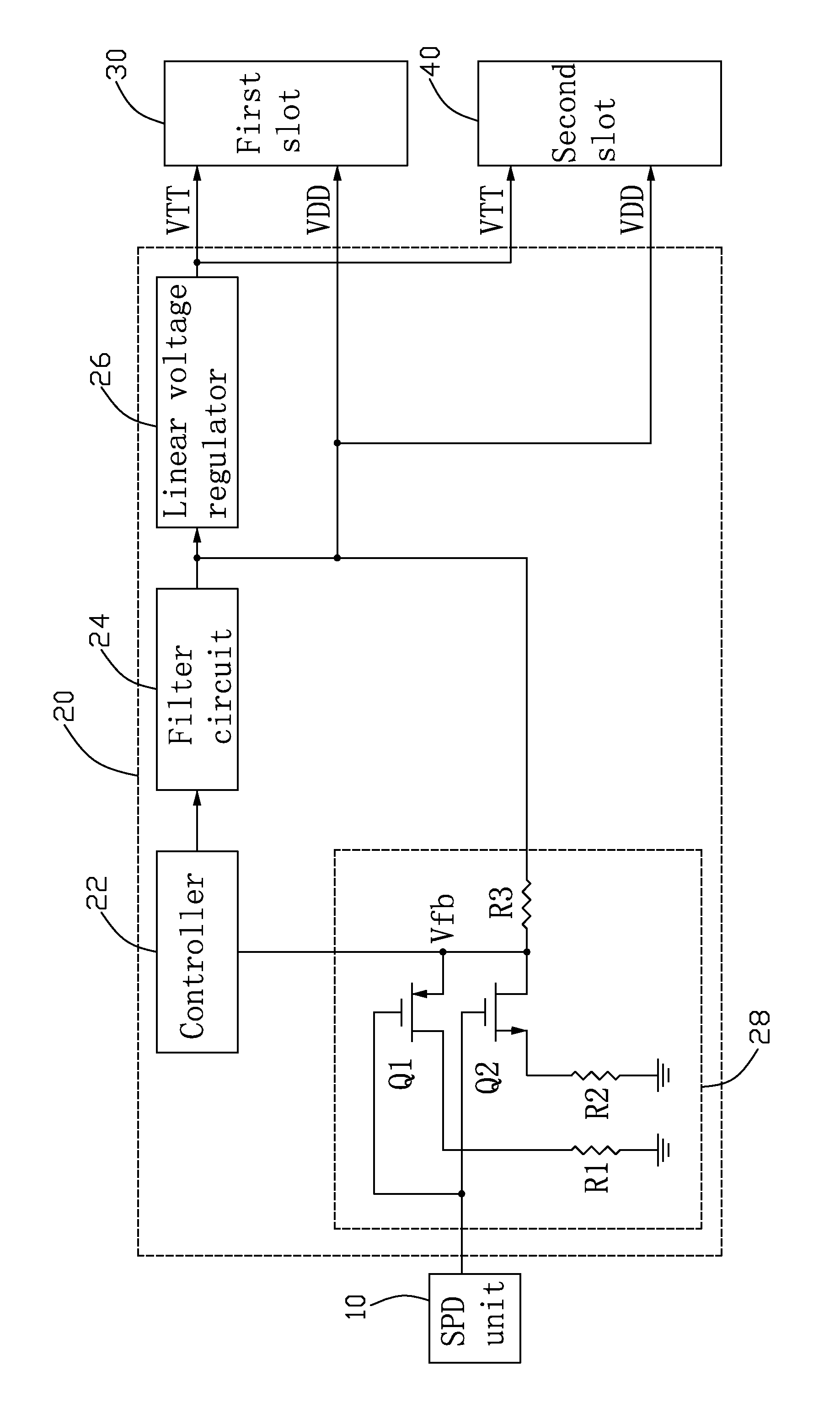

Motherboard with voltage regulator supporting DDR2 memory modules and DDR3 memory modules

An exemplary motherboard includes a first slot arranged for mounting a first type of memory, a second slot arranged for mounting a second type of memory, a voltage regulator electronically connected to the first slot and the second slot, and a serial presence detect (SPD) unit connected to the voltage regulator. The first memory and the second memory alternatively mounted on the motherboard, the SPD detects which type of memory is mounted on the motherboard, and the voltage regulator outputs voltages suitable for the type of the memory mounted on the motherboard according to a detection result of the SPD.

Owner:CLOUD NETWORK TECH SINGAPORE PTE LTD

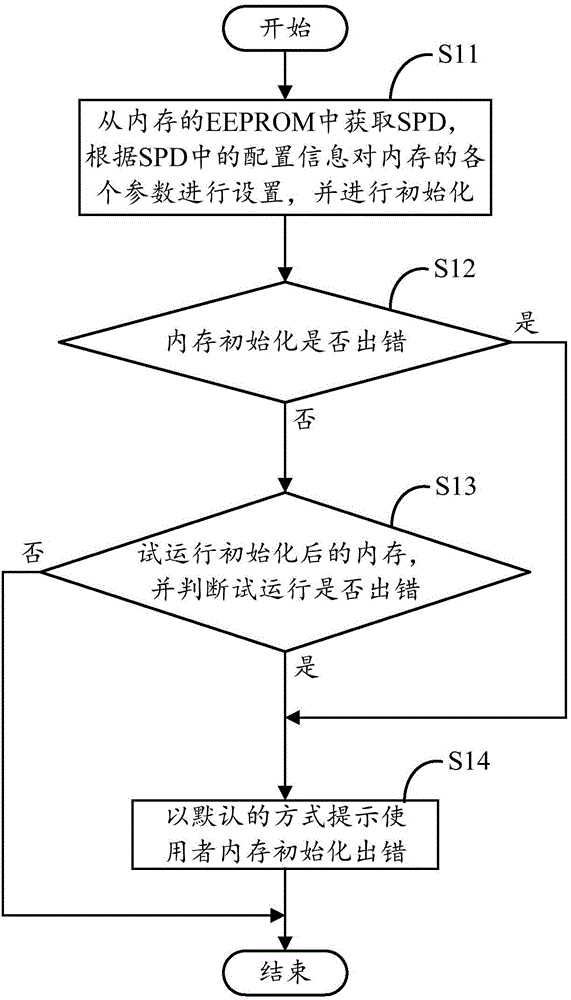

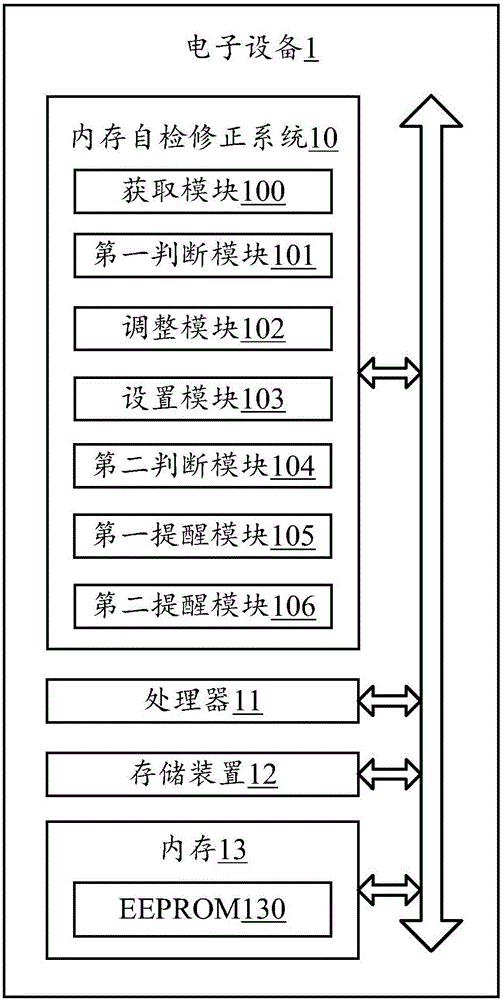

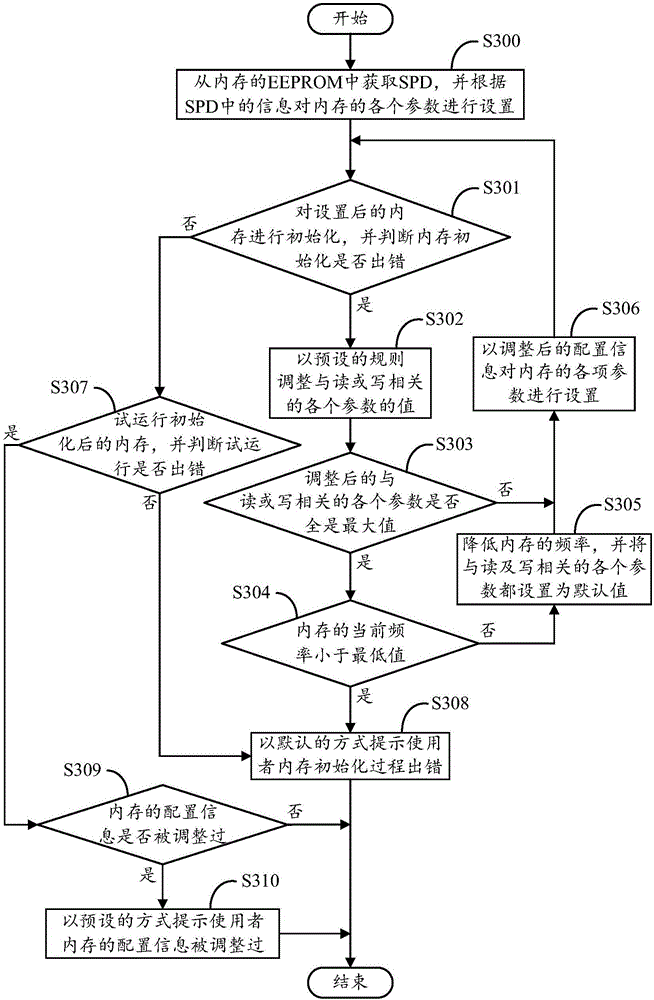

Memory self-inspection and correction system and method

ActiveCN106484550AAvoid manual correction of errors that ariseImprove experienceFault responseSerial presence detectComputer science

The present invention provides a memory self-inspection and correction method that is applied to the electronic device. The method comprises: an obtaining step of obtaining serial presence detect (SPD) from a memory, and setting each parameter of the memory; a first determining step of initializing the memory and determining whether memory initialization makes an error; an adjustment step of when the memory initialization makes an error, adjusting values of parameters associated with read or write by using a preset rule; and a setting step of when none of the adjusted values of parameters associated with read or write is the maximum value of each parameter, setting each parameter in the memory by using the adjusted configuration information, and re-initializing the memory; a second determination step of when the memory initialization makes no error, performing pilot run on the initialized memory, and determining whether the pilot run makes an error; and a first reminder step of when the pilot run makes an error, prompting the user that the memory initialization makes an error. The present invention provides a memory self-inspection and correction system.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Memory module system using a partitioned serial presence detect memory

A memory module system may include a serial presence detect (SPD) memory and a memory controller. The SPD memory may store first SPD data and second SPD data of a memory module. The SPD memory may be partitioned into at least two regions that may operate as multiple SPD ROMs. The memory controller may boot the memory module system based on a comparison between the first SPD data and the second SPD data when an initialization signal is input to the memory module system. The memory module system may be booted stably and may prevent system breakdowns.

Owner:SAMSUNG ELECTRONICS CO LTD