Interrupt processing method of multi-PCIE (Peripheral Component Interface Express) equipment system

A system interrupt and processing method technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problem of inability to handle multiple PCIE device interrupts, and achieve the effect of shortening the interrupt delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

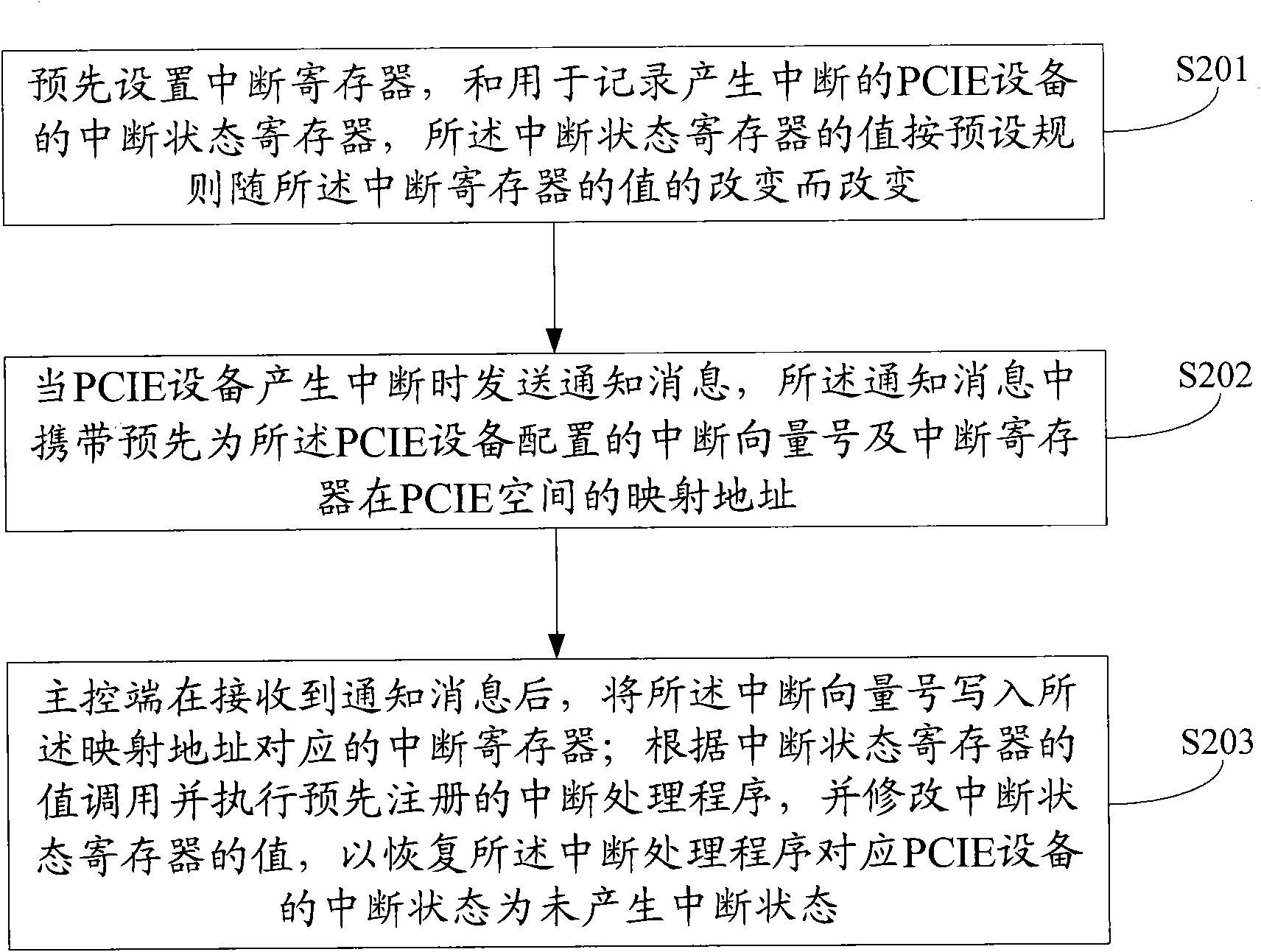

[0050] see figure 2 , the embodiment of the present invention provides a kind of multi-PCIE device system interruption processing method, comprises the following steps:

[0051] Step S201: Presetting an interrupt register and an interrupt status register for recording the interrupted PCIE device, the value of the interrupt status register changes with the value of the interrupt register according to preset rules.

[0052] Step S202: Send a notification message when the PCIE device generates an interrupt, the notification message carrying the interrupt vector number pre-configured for the PCIE device and the mapping address of the interrupt register in the PCIE space.

[0053] Step S203: After receiving the notification message, the master control terminal writes the interrupt vector number into the interrupt register corresponding to the mapping address; calls and executes the pre-registered interrupt handler according to the value of the interrupt status register, and modifi...

Embodiment 2

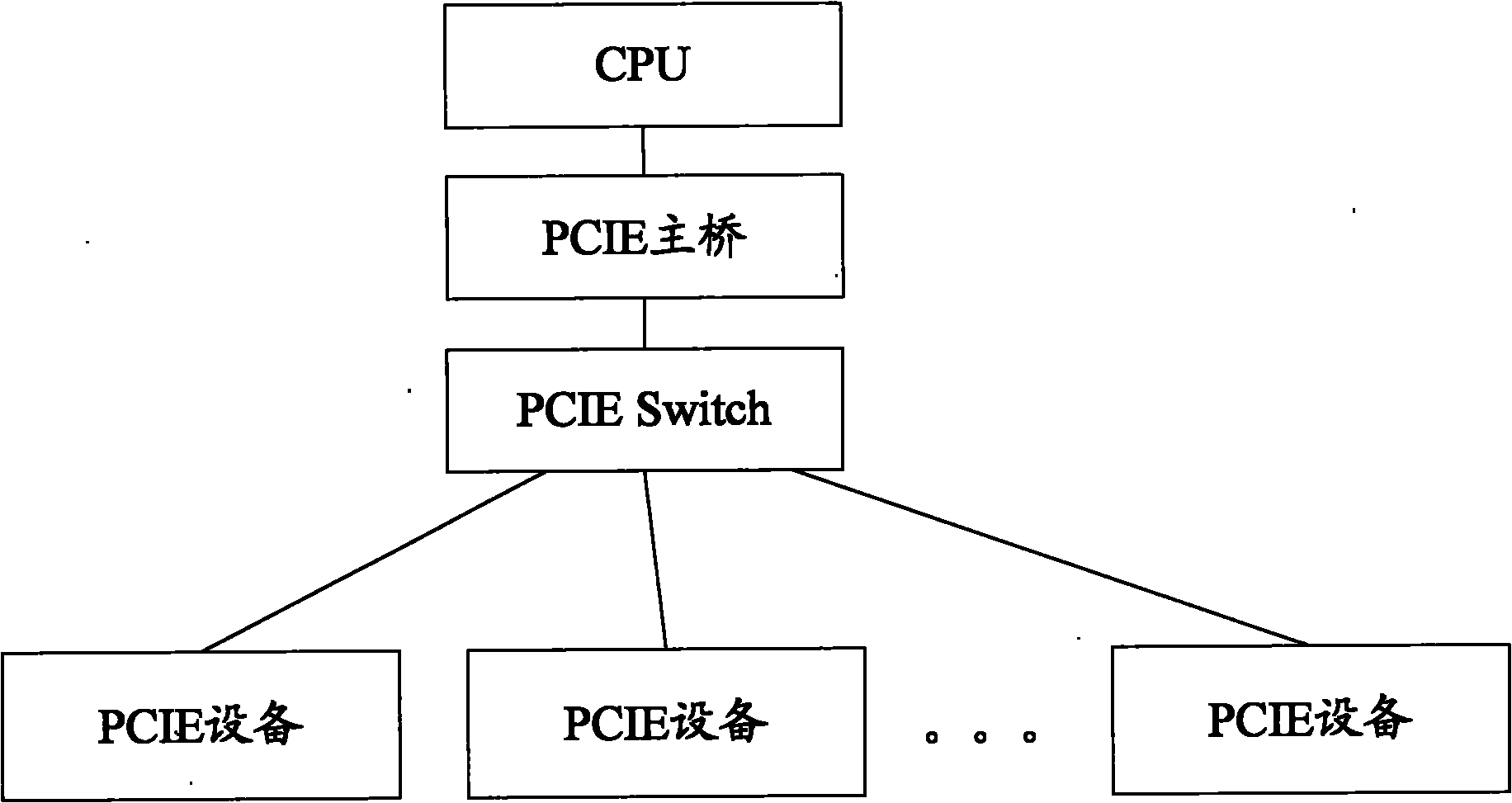

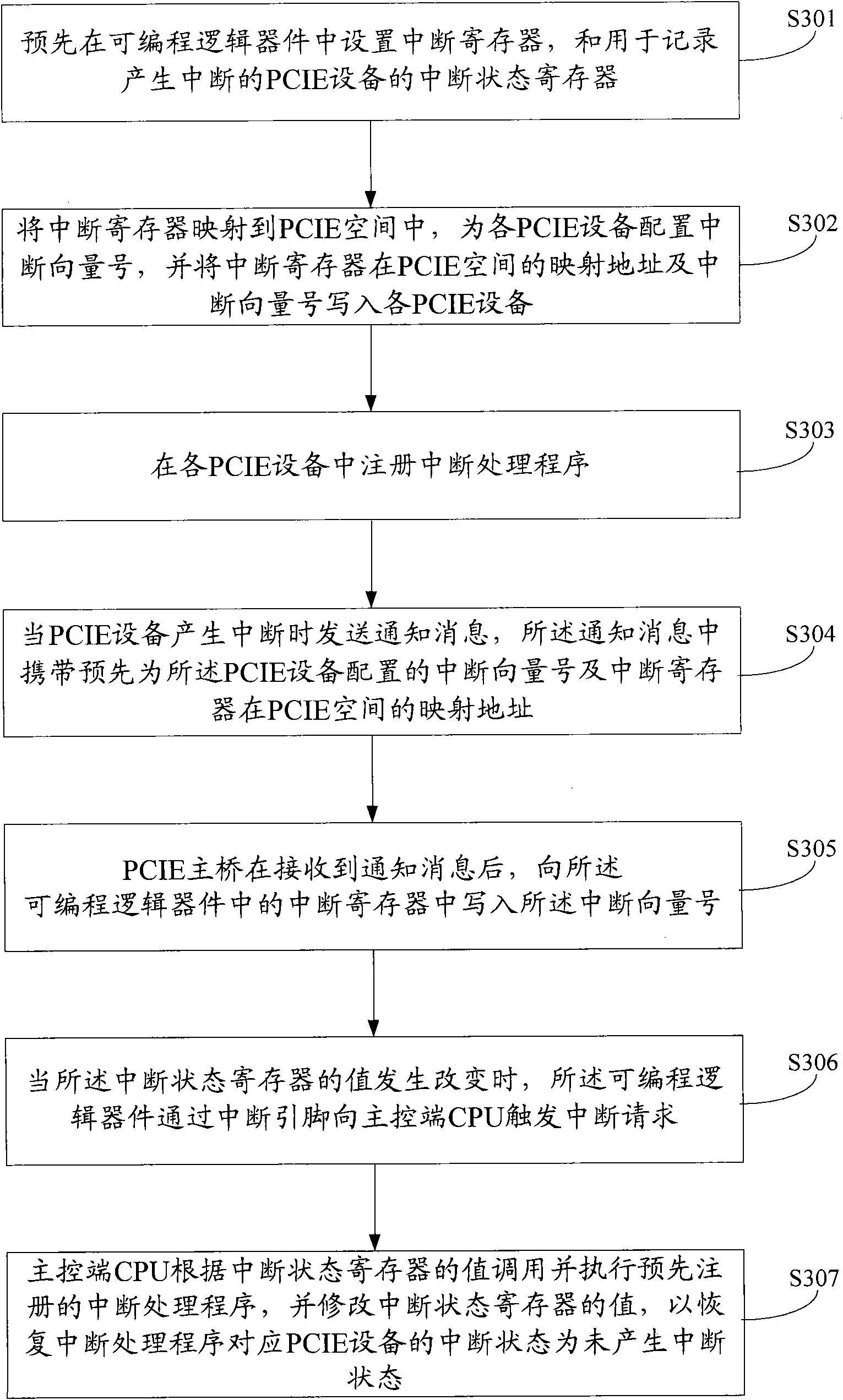

[0057] see image 3 , the embodiment of the present invention provides a preferred multi-PCIE device system interrupt processing method, combined with reference Figure 4 , preferably, the main control end comprises central processing unit CPU401, the PCIE main bridge 402 that links to each other with CPU401, is used for the data conversion between the CPU bus data format supported by CPU401 and the data format supported by each PCIE device, and the possible linking to each other with CPU401 Program logic device 403 . Of course, according to actual application scenarios, a PCIE Switch may also be included between the PCIE main bridge 402 and each PCIE device, for coordinating data exchange among multiple PCIE devices.

[0058] Preferably, the programmable logic device may be CPLD or FPGA or the like.

[0059] In practical applications, the PCIE main bridge 402 can be set on the motherboard, or integrated in the CPU 401 .

[0060] The method provided by the embodiment of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More