Mismatch calibration method for streamline ADC (Analog-to-Digital Converter) multi-bit sub DAC (Digital-to0Analog Converter) capacitor

A technology of capacitance mismatch and calibration method, applied in the direction of analog/digital conversion calibration/test, etc., can solve problems such as nonlinear error calibration, and achieve the effect of improving accuracy and high compensation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] Below in conjunction with example and accompanying drawing, the present invention is described in further detail.

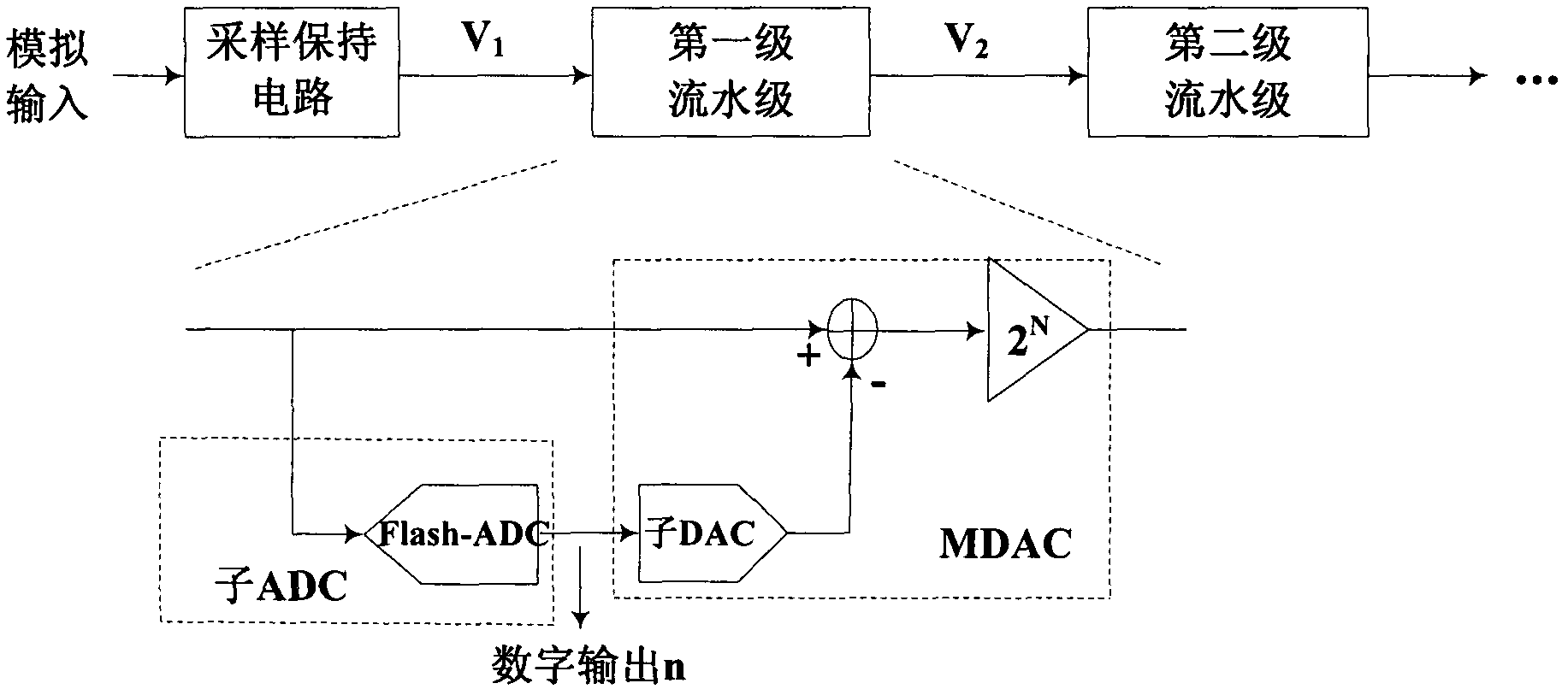

[0048] The pipeline ADC contains multiple pipeline stages, each pipeline stage contains sub-ADC, sub-DAC, amplifier and subtractor, and the analog input signal V in Input to the sub-ADC for quantization to generate a digital output, and at the same time send the digital output to the sub-DAC for digital-to-analog conversion, output analog, and convert the analog input signal V in and the output analog quantity are subtracted in the subtractor, and then the output voltage V is obtained after being amplified by the amplifier out , which is the output of MDAC; in the pipeline stage, sub-DAC, subtractor and amplifier together form MDAC;

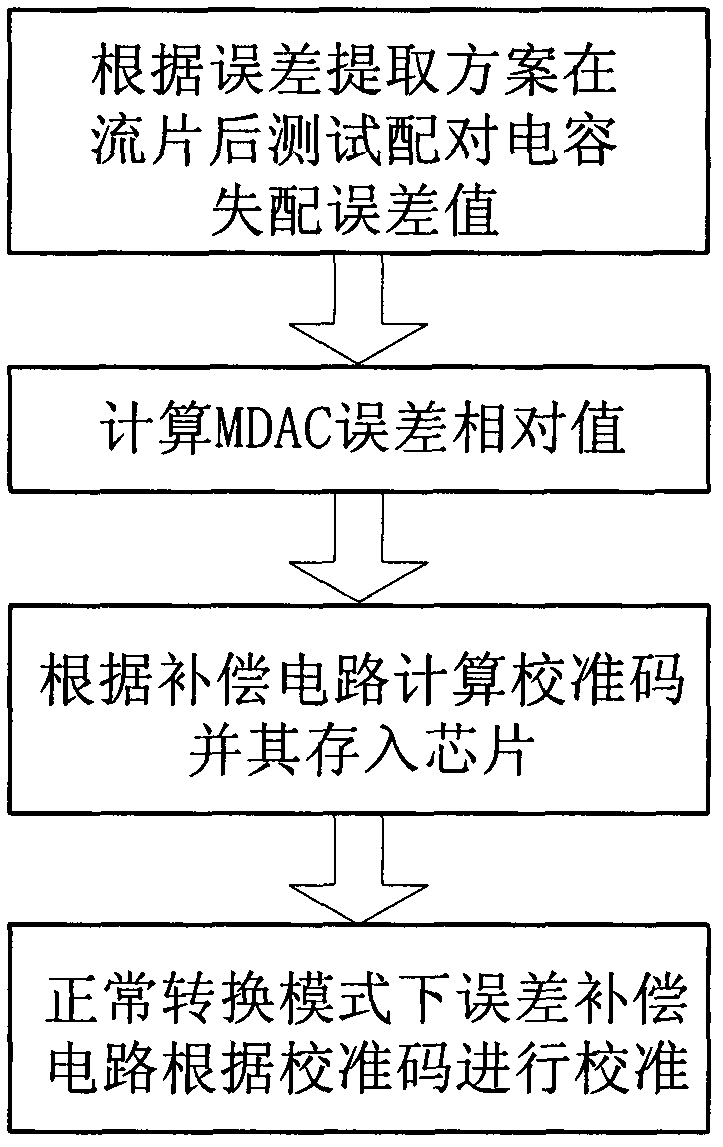

[0049] Such as image 3 As shown, the present invention provides a pipelined ADC multi-bit sub-DAC capacitor mismatch calibration method, the basic calibration process is: first, after the chip tape-out, the paired capacito...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More