Very long instruction word variable long instruction realization method and processor for realizing same

A technology of ultra-long instruction words and variable-length instructions, which is applied in the direction of concurrent instruction execution and machine execution devices, can solve the problems of difficult calculation operations and single instruction implementation, and achieve the goals of improving performance, shortening the number of cycles, and enhancing parallel computing capabilities Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

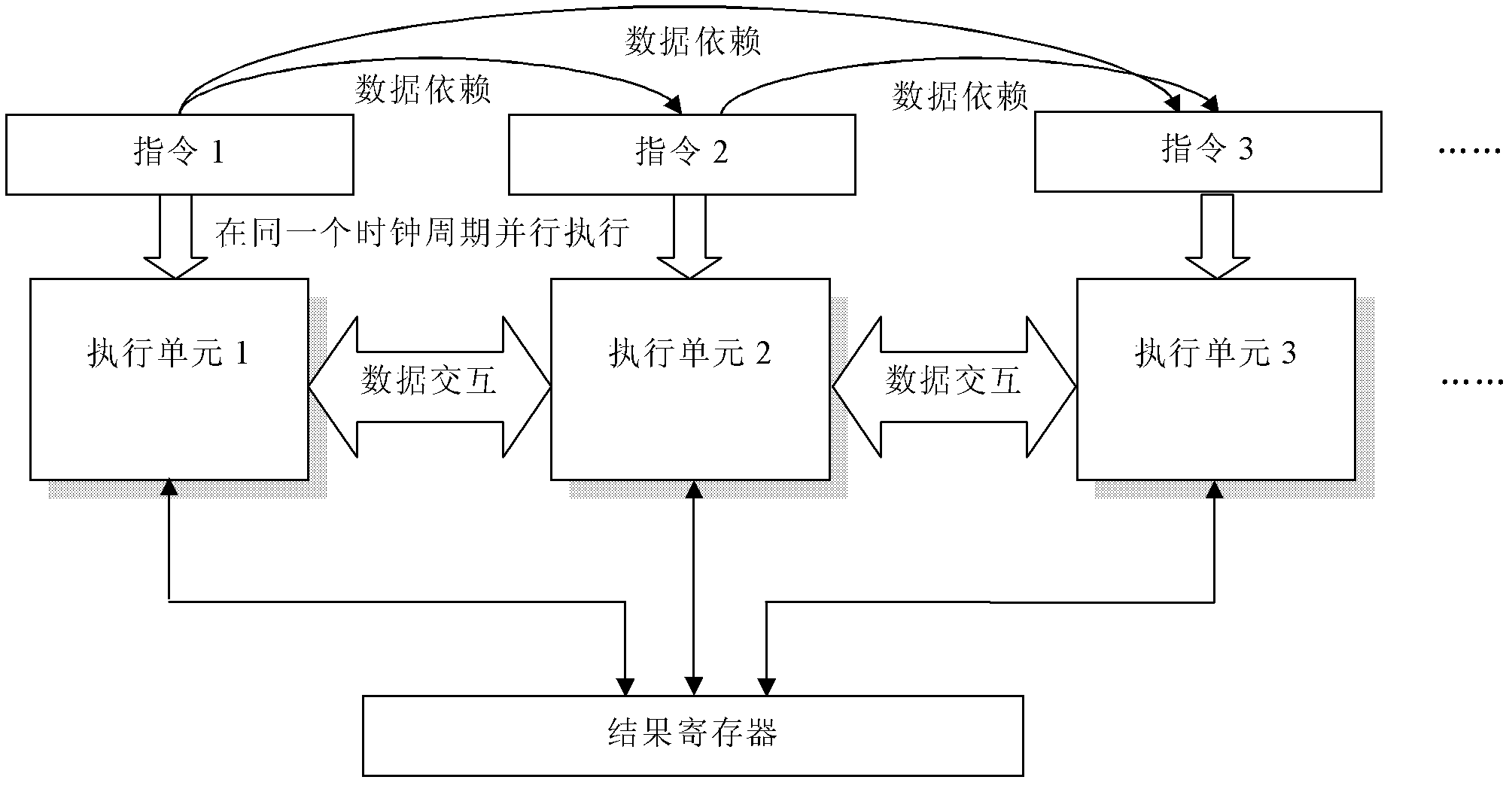

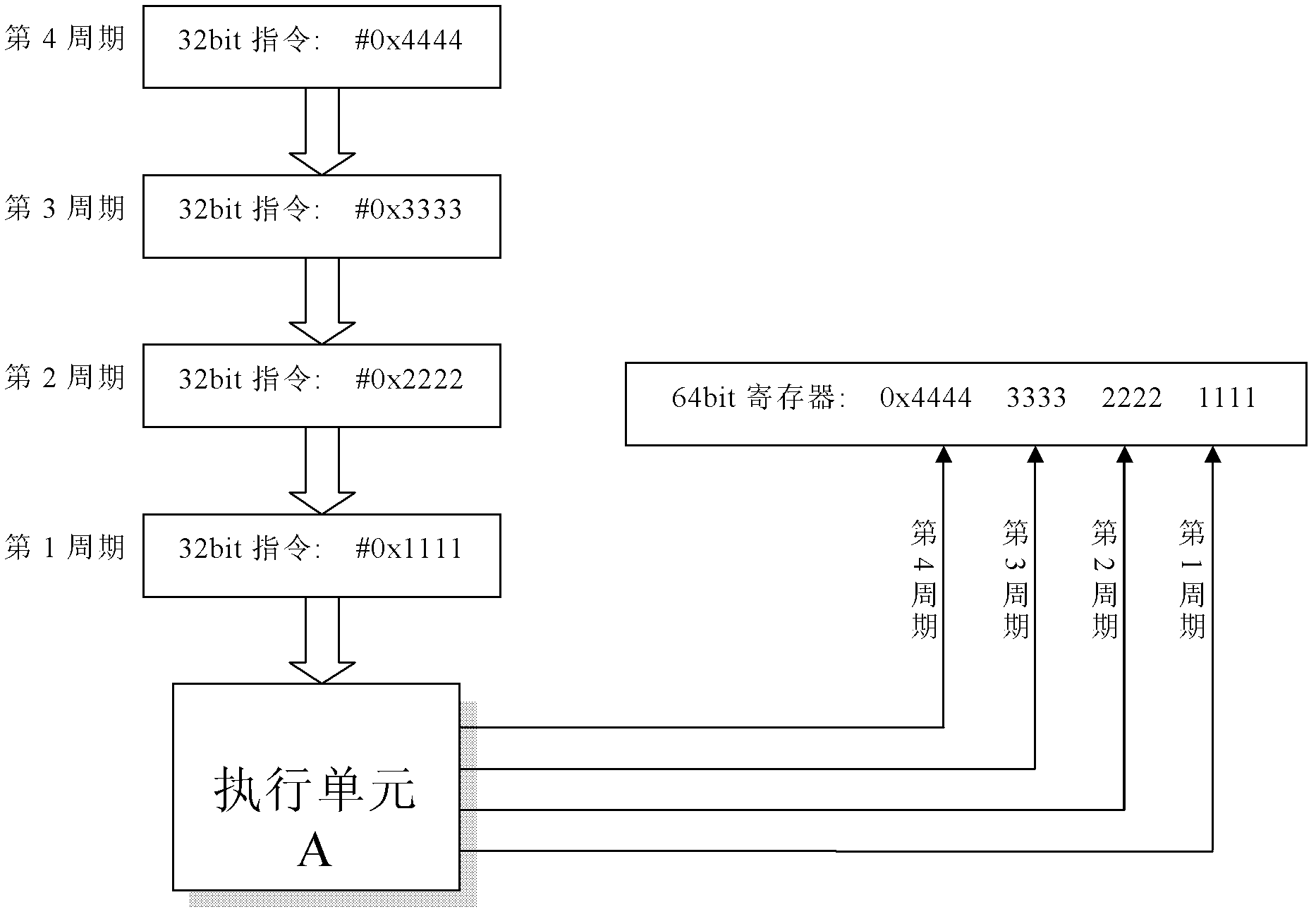

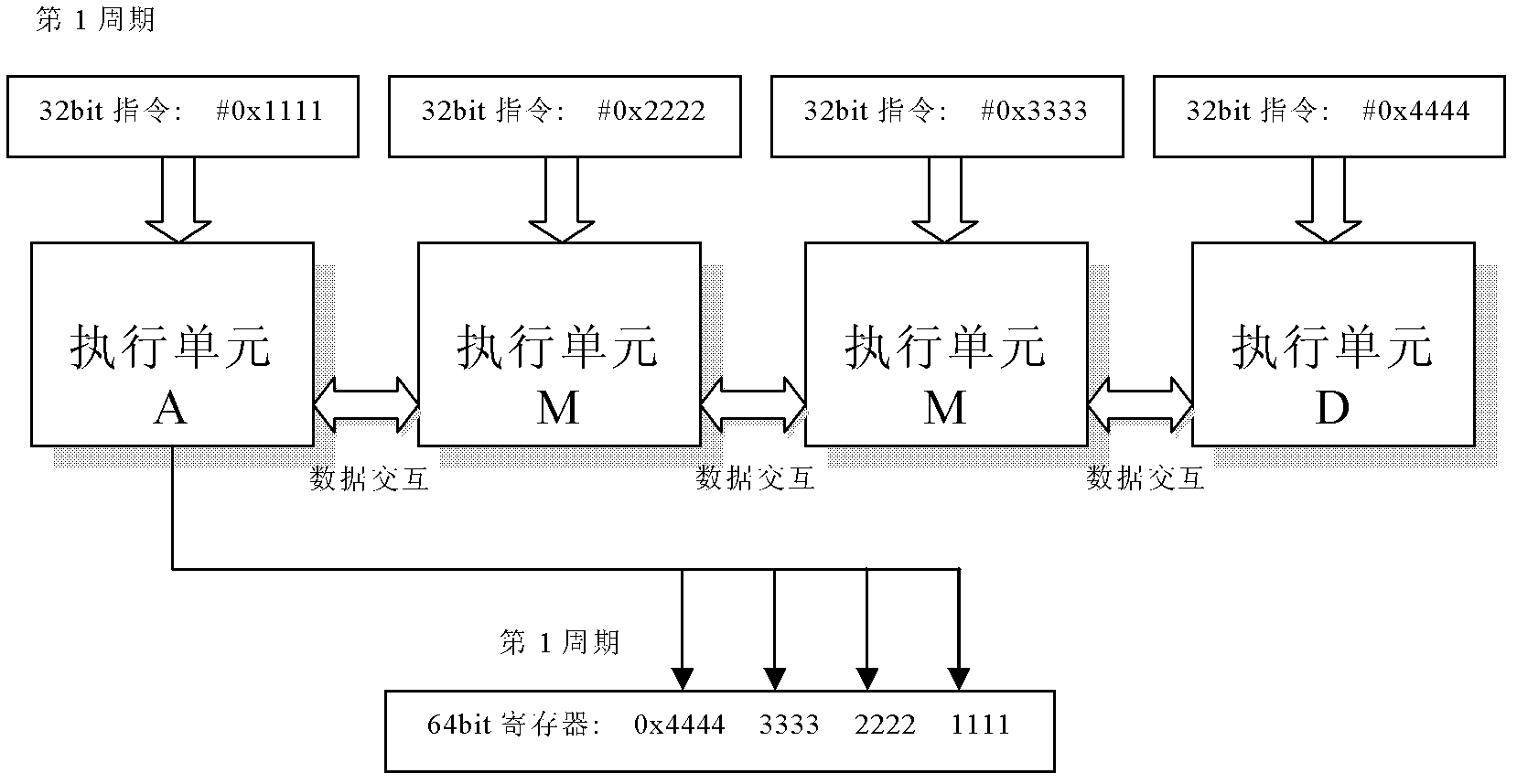

[0022] Take Magnolia, a third-generation digital signal processor independently developed by the DSP Laboratory of the Institute of Microelectronics, Tsinghua University, as an example. It is a processor with a VLIW architecture. There are 8 execution units in the Magnolia processor, and 32-bit fixed-length instruction encoding is adopted, such as figure 1 shown. For processors with VLIW architecture, the data dependencies of each instruction are determined by the compiler. The compiler can arrange instructions without data dependencies to the same clock under the condition of satisfying various hardware resource constraints. Cycles are executed in parallel. In the actual execution process, the processor's judgment on the parallelism of instructions is determined by the unique "functional unit ascending order" method of the processor.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More