Patents

Literature

72 results about "Reduced instruction set computing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A reduced instruction set computer, or RISC (/rɪsk/), is one whose instruction set architecture (ISA) allows it to have fewer cycles per instruction (CPI) than a complex instruction set computer (CISC). Various suggestions have been made regarding a precise definition of RISC, but the general concept is that such a computer has a small set of simple and general instructions, rather than a large set of complex and specialized instructions. Another common RISC trait is their load/store architecture, in which memory is accessed through specific instructions rather than as a part of most instructions.

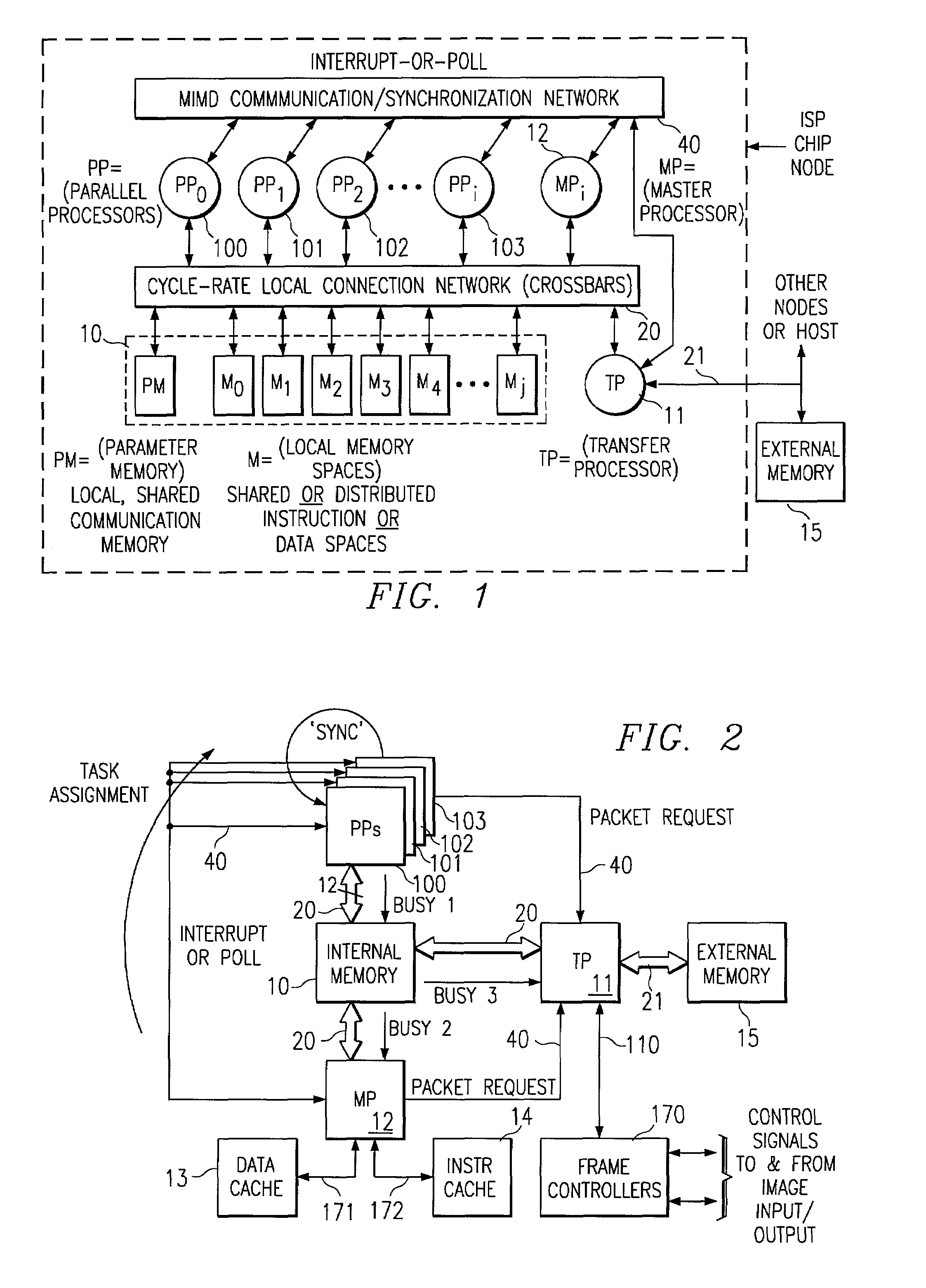

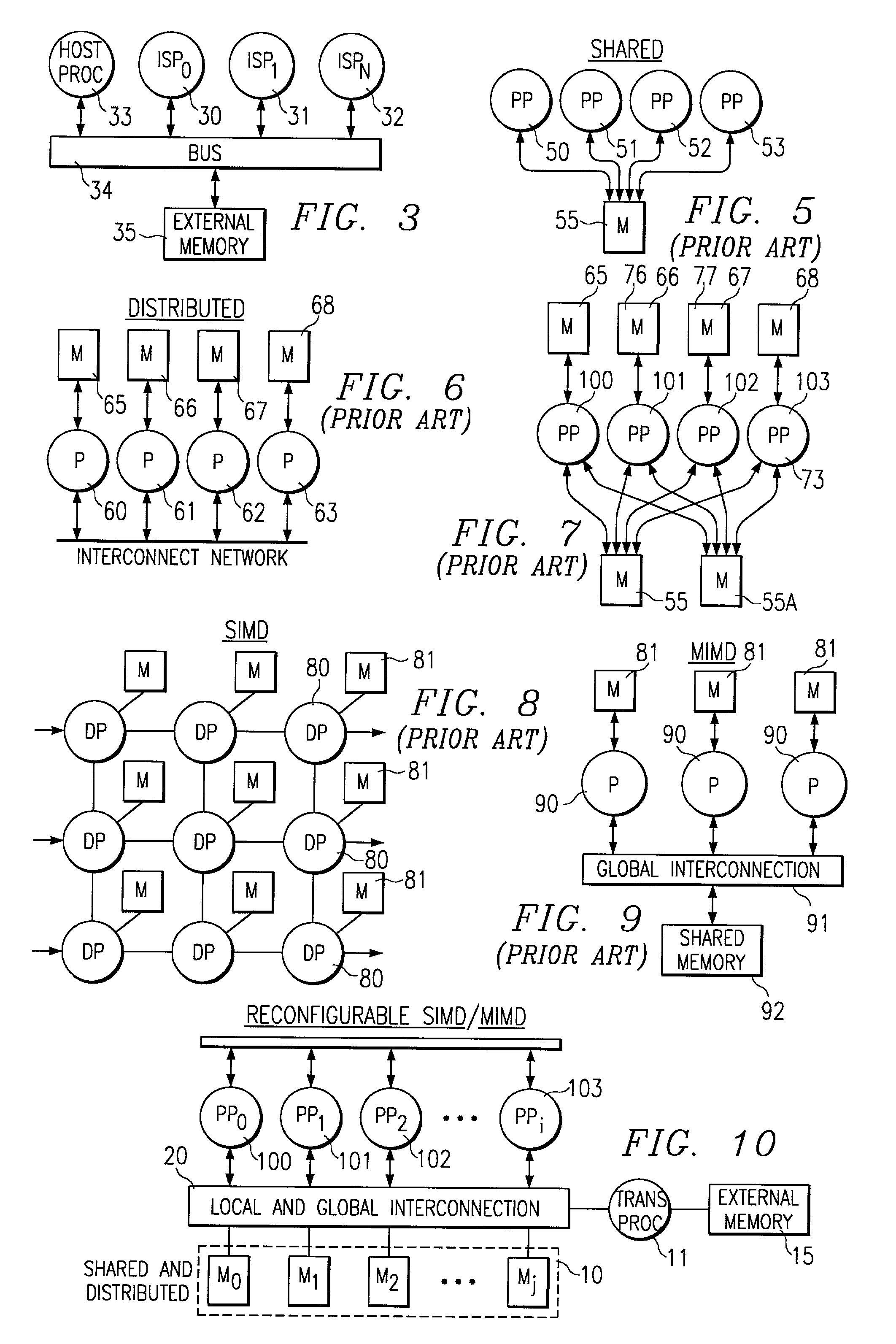

Single integrated circuit embodying a risc processor and a digital signal processor

InactiveUS6260088B1Save spaceImprove versatilityGeneral purpose stored program computerMultiple digital computer combinationsDigital signal processingComputer image

A single integrated circuit includes first and second data processors operating on different instruction sets independently operating on disjoint programs and data. The single integrated circuit preferably includes an external interface, a shared data transfer controller and shared memory divided into plural independently accessible memory banks. The two data processors are preferably a digital signal processor (DSP) and a reduced instruction set computer (RISC) processor. The DSP and RISC processors are suitably programmed to perform differing aspects of computer image processing.

Owner:TEXAS INSTR INC

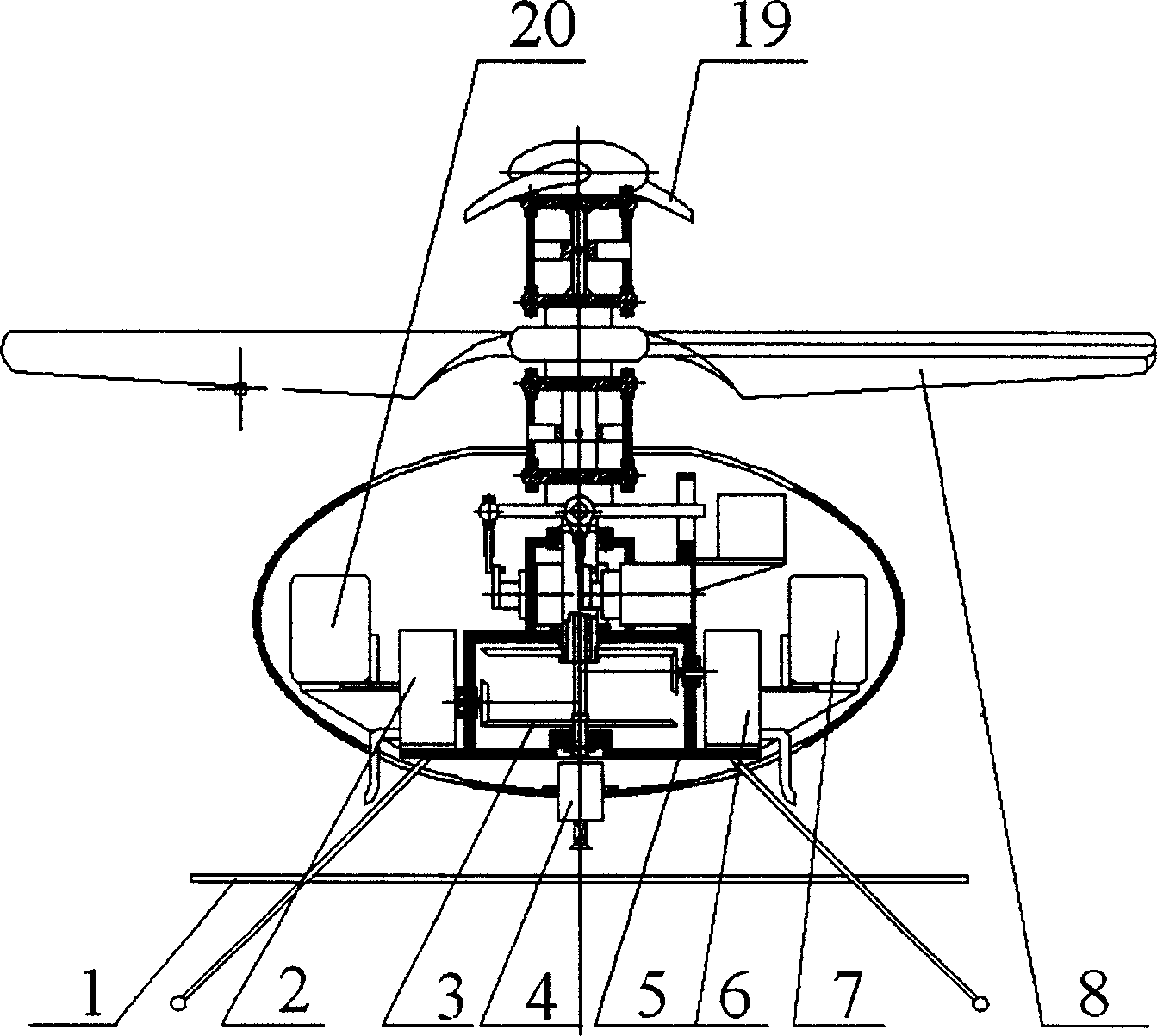

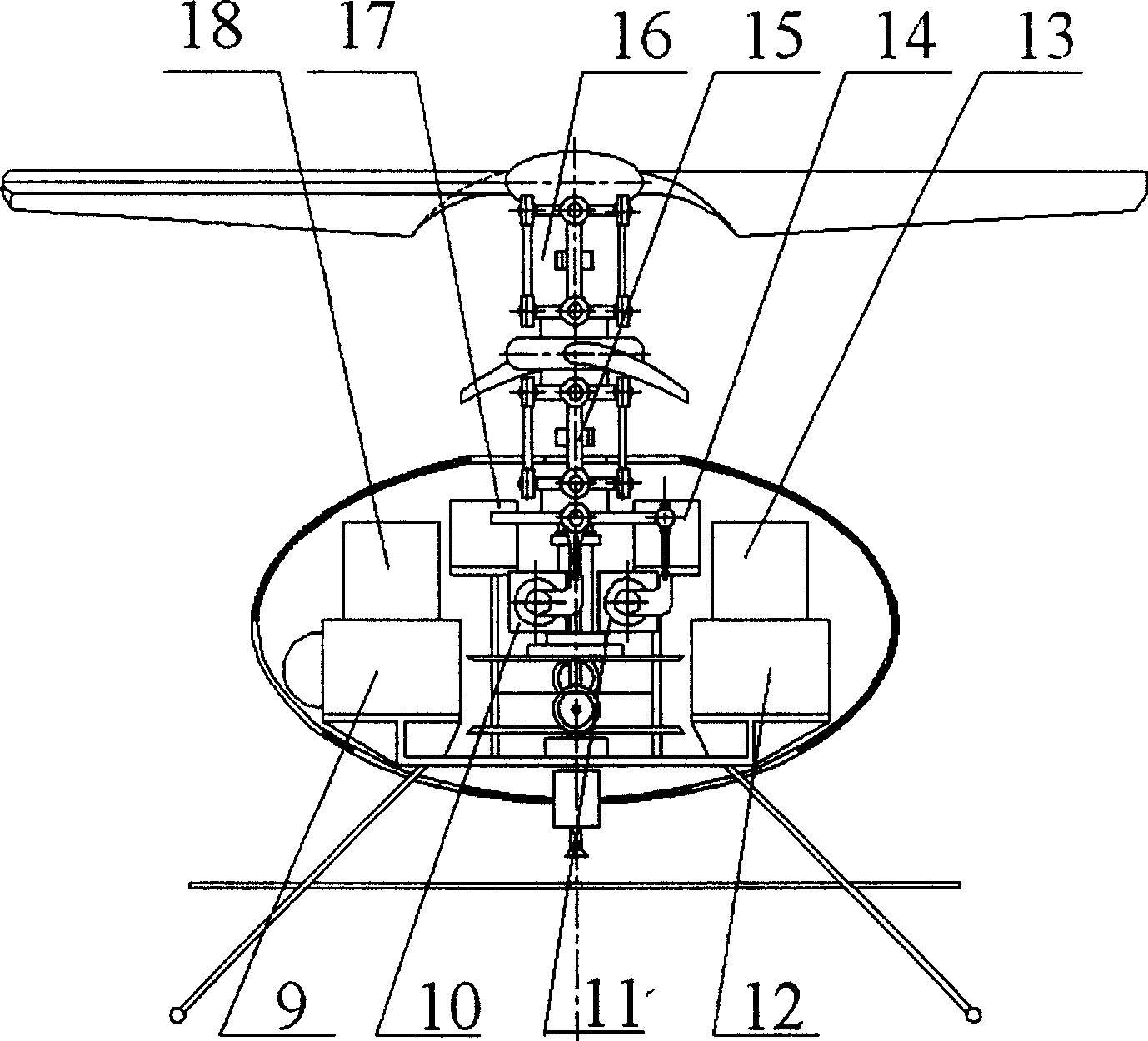

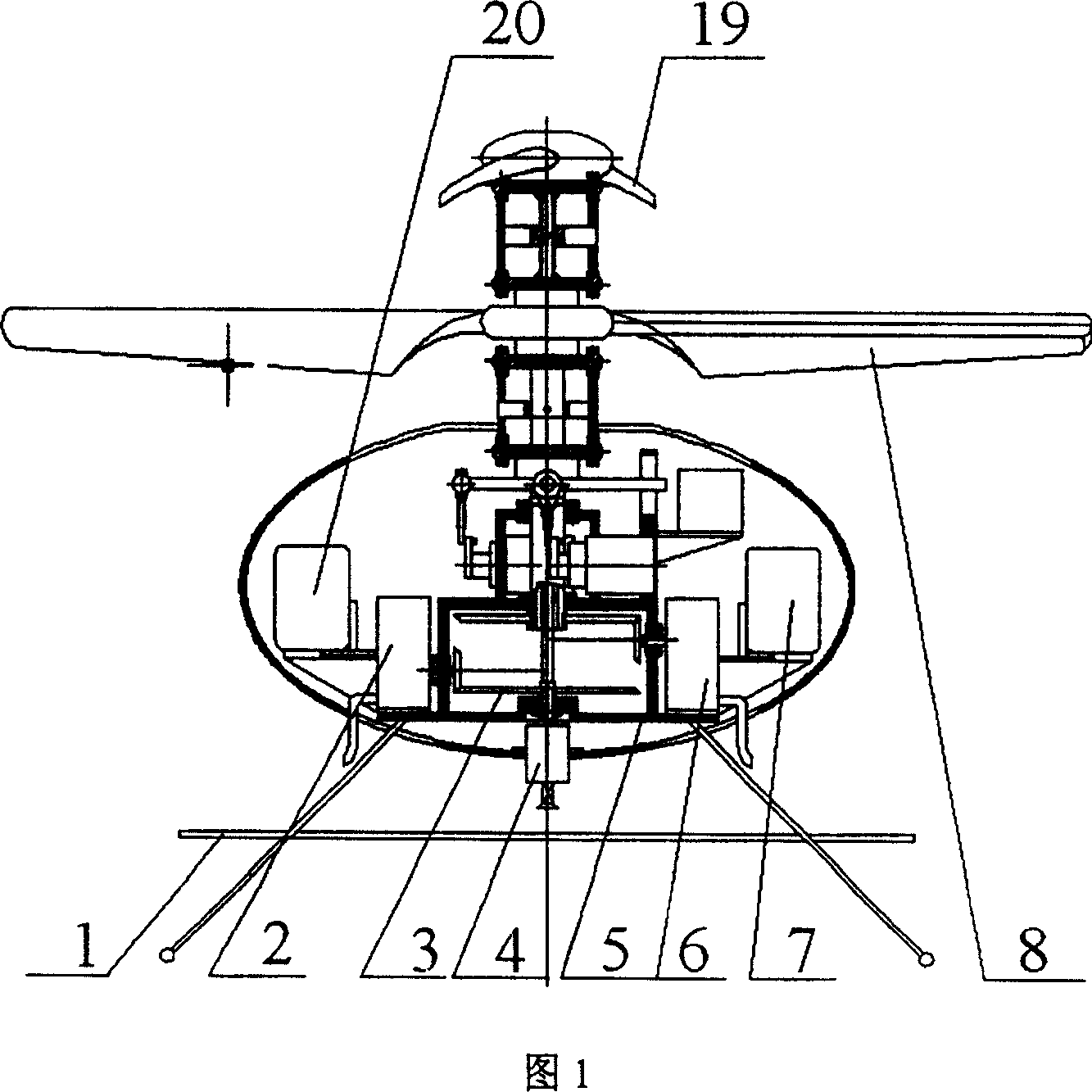

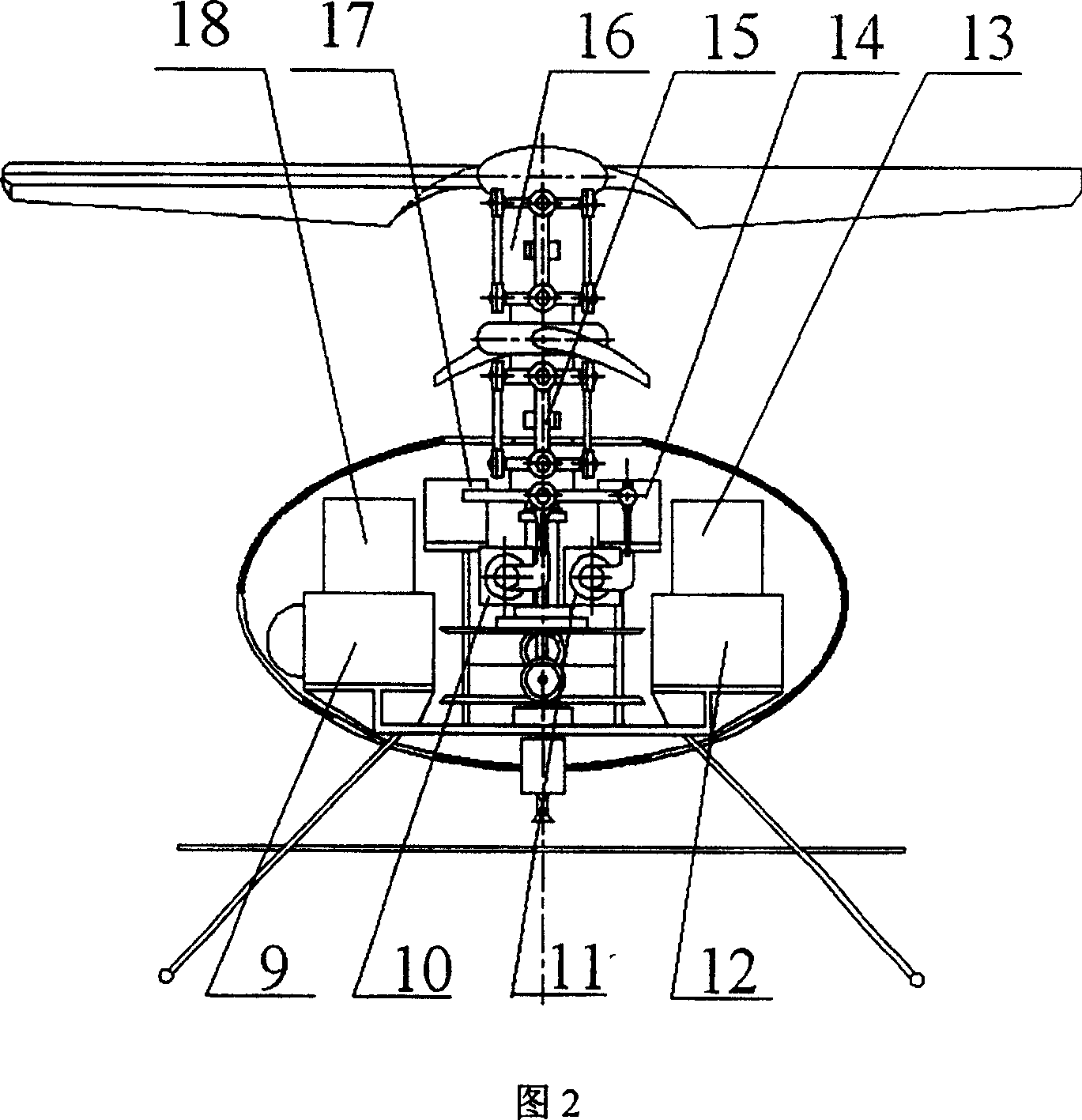

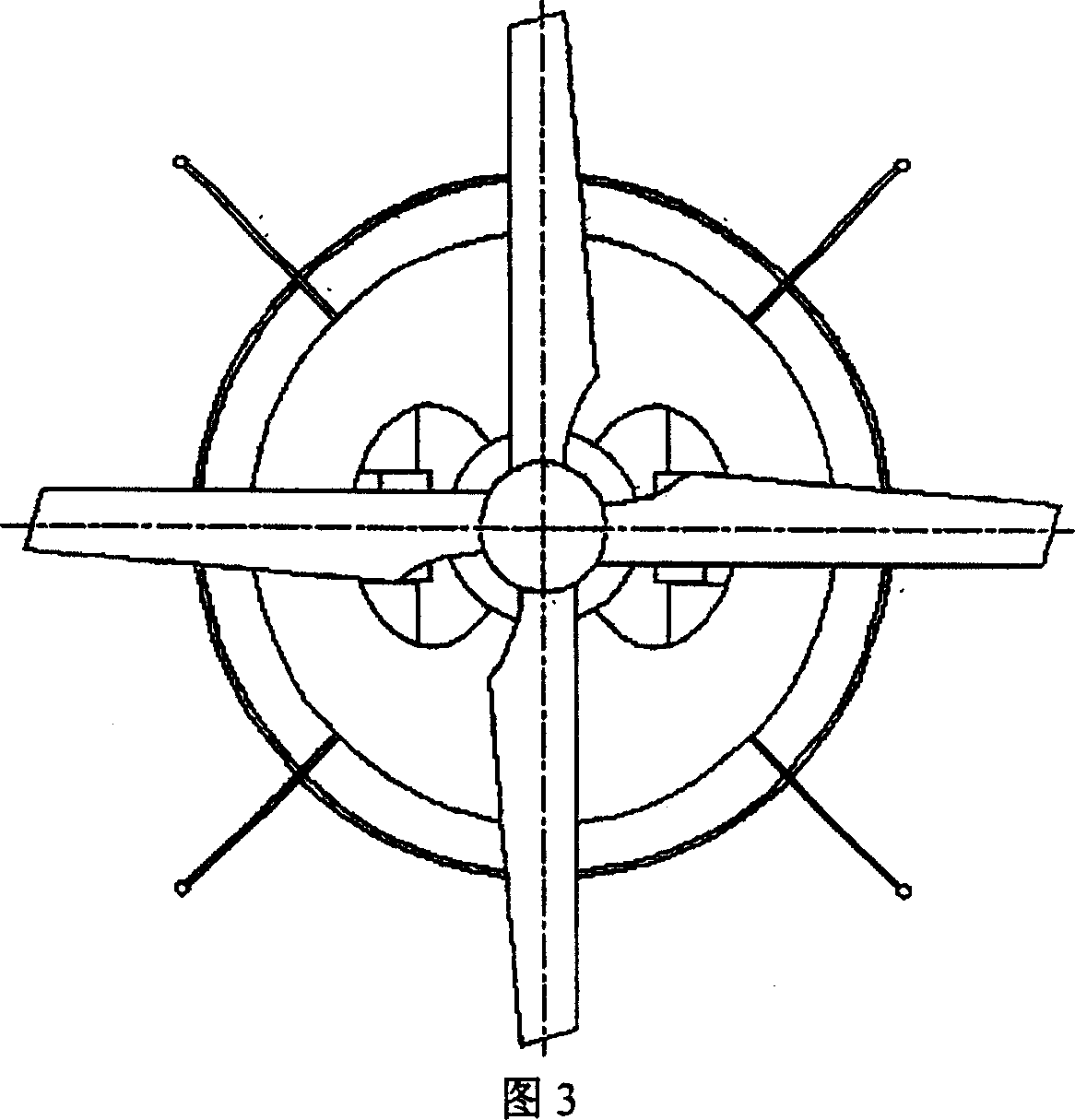

Power circuit scanning test robot airplane and controlling system

InactiveCN1645284ANo casualtiesAvoid lostToy aircraftsCable installation apparatusNavigation systemElectric power

A robot airplane for tour inspection of power line in counterwise driving structure of coxial double propeller uses two engines to control flight stability, GPS and GIS to confirm flight path, computer processor to adjust flight attitute and battery to provide power for motor, transducer and data link system. Its control system consists of navigation system, autonomous planning system, data link system and on line detection system.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

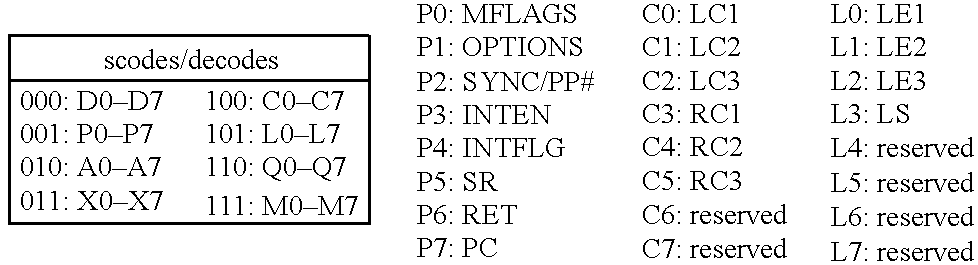

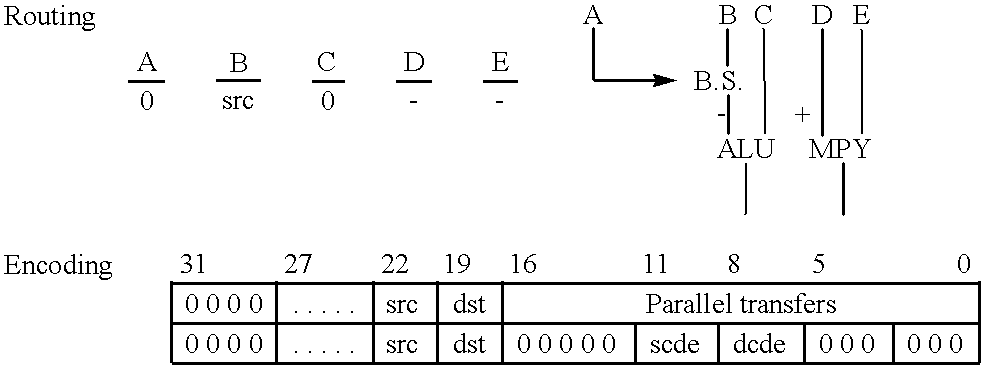

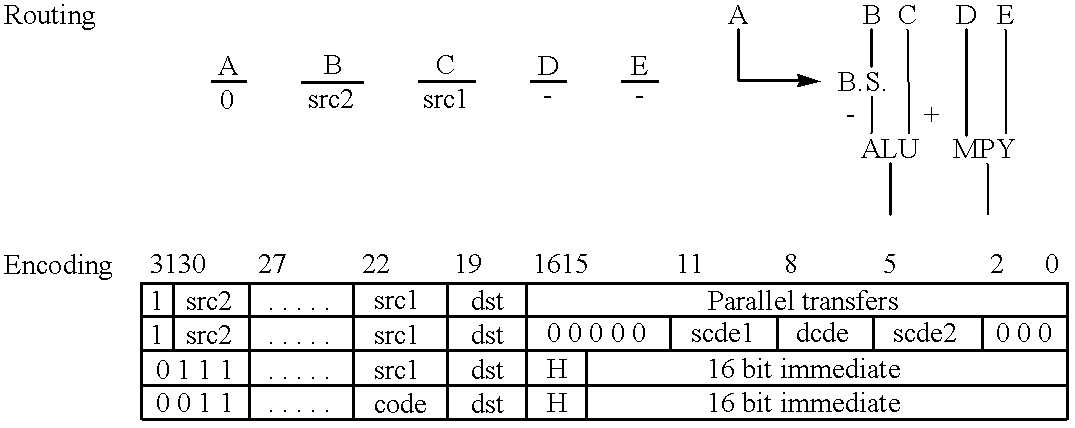

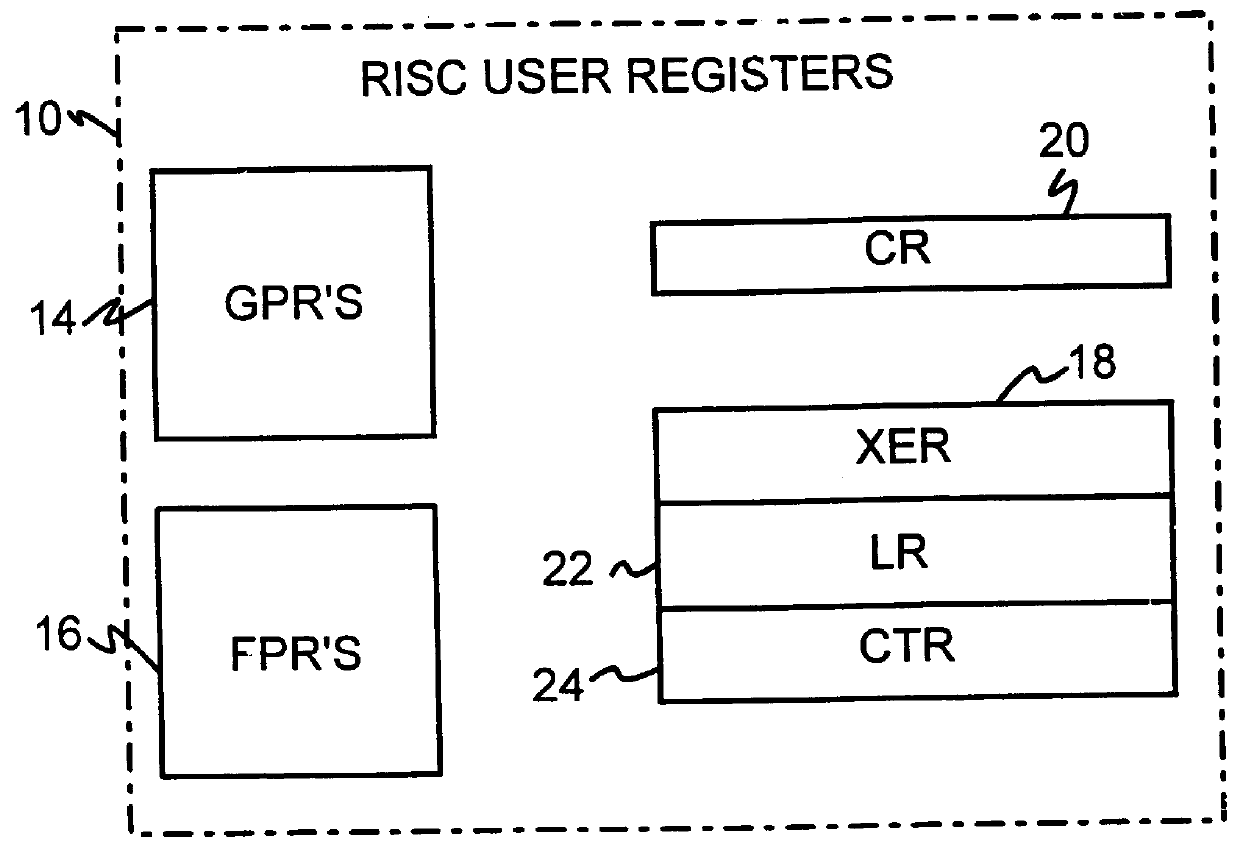

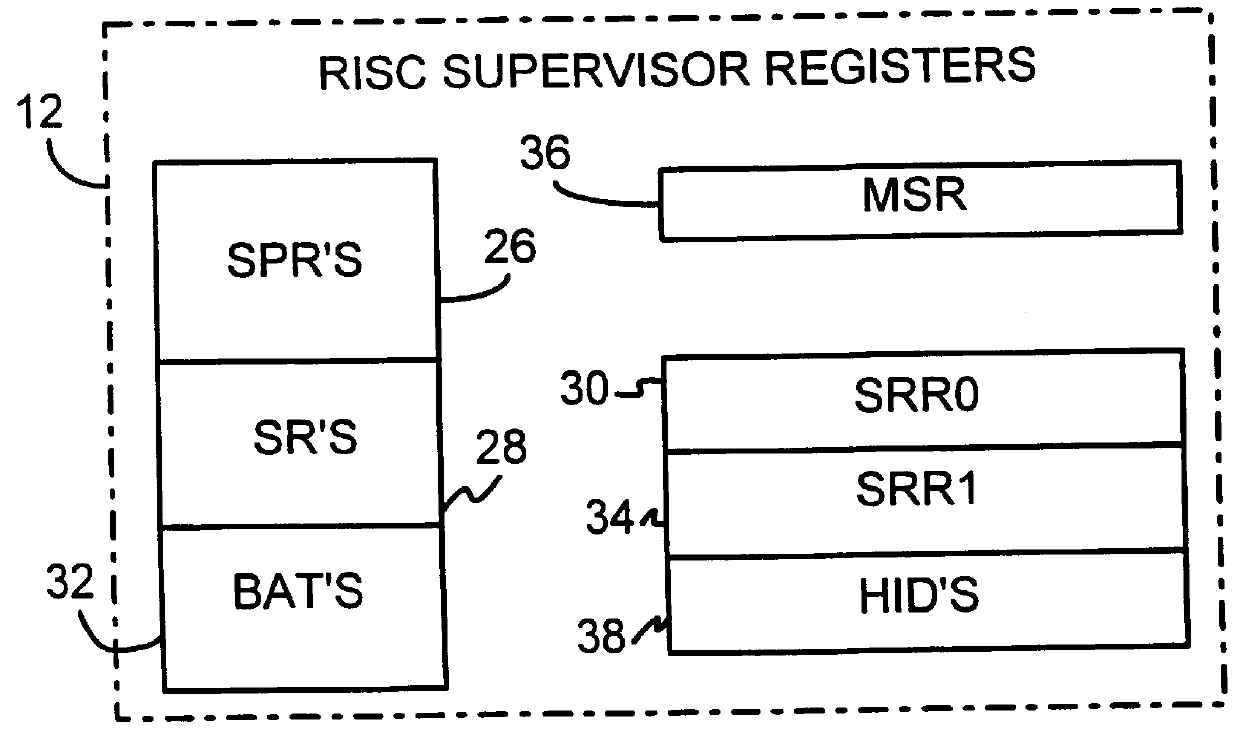

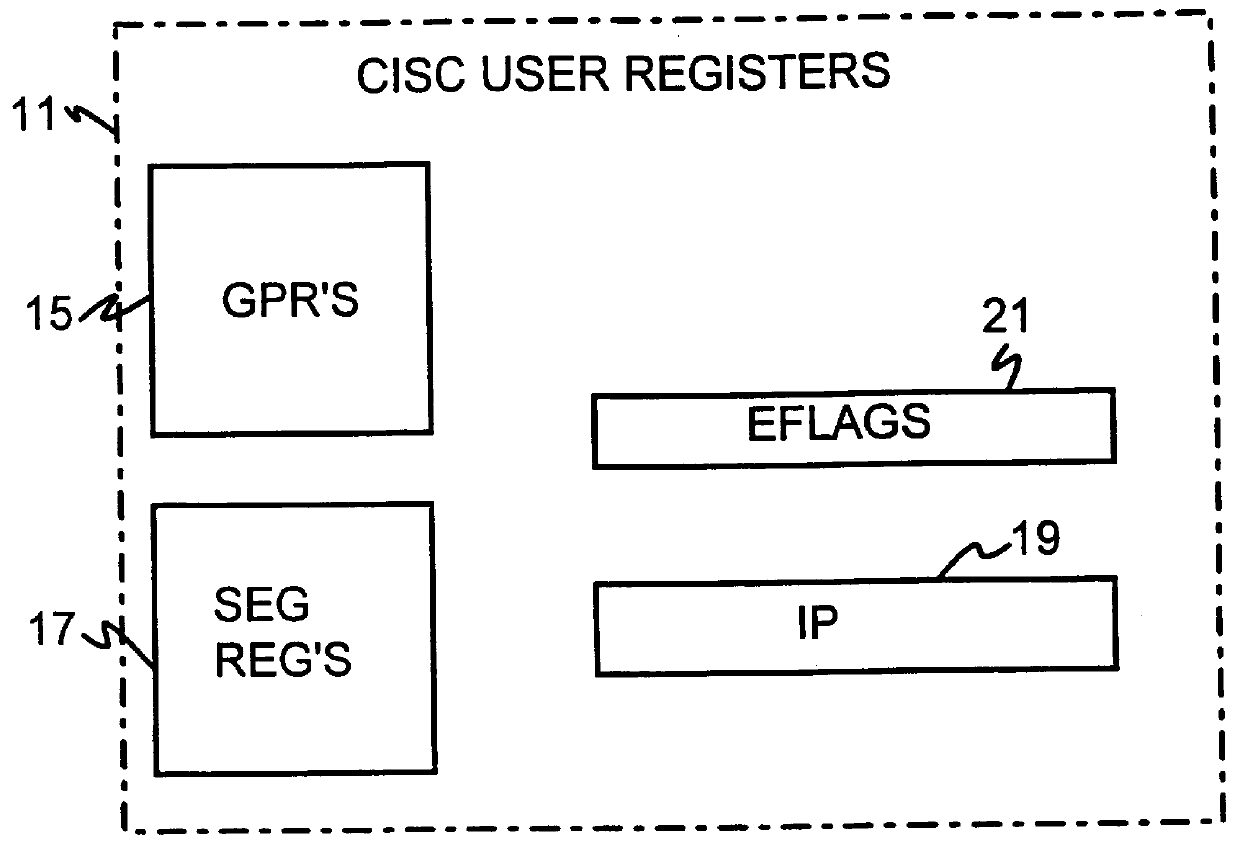

Shared register architecture for a dual-instruction-set CPU to facilitate data exchange between the instruction sets

A dual-instruction set central processing unit (CPU) is capable of executing instructions from a reduced instruction set computer (RISC) instruction set and from a complex instruction set computer (CISC) instruction set. Data and address information may be to transferred from a CISC program to a RISC program running on the CPU by using shared registers. The architecturally-defined registers in the CISC instruction set are merged or folded into some of the architecturally-defined registers in the RISC architecture so that these merged registers are shared by the two instructions sets. In particular, the flags or condition code registers defined by each architecture are merged together so that CISC instructions and RISC instructions will implicitly update the same merged flags register when performing computational instructions. The RISC and CISC registers are folded together so that the CISC flags are at one end of the register while the frequently used RISC flags are at the other end, but the RISC instructions can read or write any bit in the merged register. The CISC code segment base address is stored in the RISC branch count register, while the CISC floating point instruction address is stored in the RISC branch link register. The general-purpose registers (GPR's) are also merged together, allowing a CISC program to pass data to a RISC program merely by writing one of its GPR's, switching control to the RISC program, and the RISC program reading one of its GPR's that is merged with and corresponds to the CISC GPR that was written to by the CISC program.

Owner:SAMSUNG ELECTRONICS CO LTD

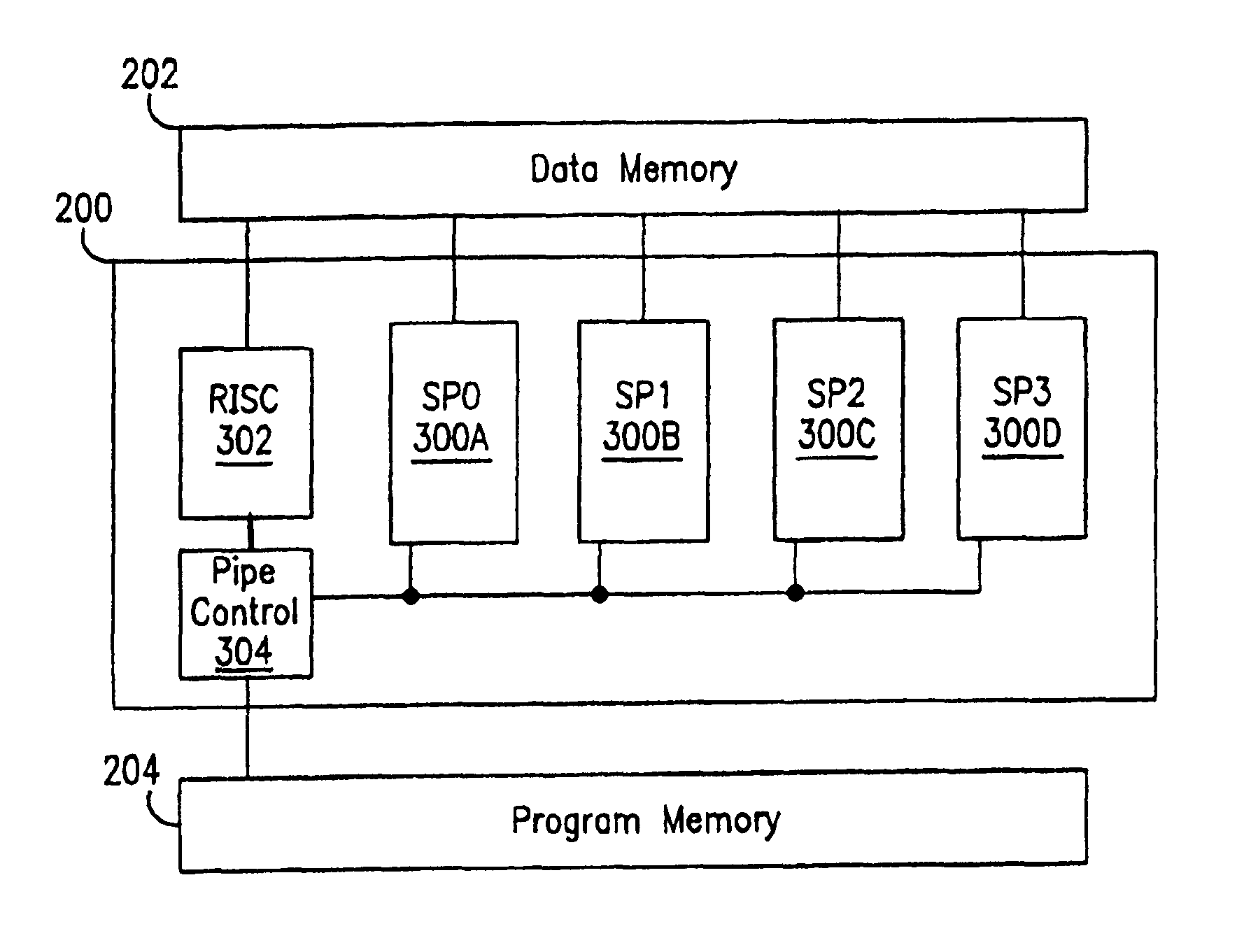

Single integrated circuit embodying a dual heterogenous processors with separate instruction handling hardware

InactiveUS6948050B1Save board spaceSave spaceGeneral purpose stored program computerConcurrent instruction executionDigital signal processingMemory bank

A single integrated circuit includes first and second data processors operating on different instruction sets independently operating on disjoint programs and data. The single integrated circuit preferably includes an external interface, a shared data transfer controller and shared memory divided into plural independently accessible memory banks. The two data processors are preferably a digital signal processor (DSP) and a reduced instruction set computer (RISC) processor. The DSP and RISC processors are suitably programmed to perform differing aspects of computer image processing.

Owner:TEXAS INSTR INC

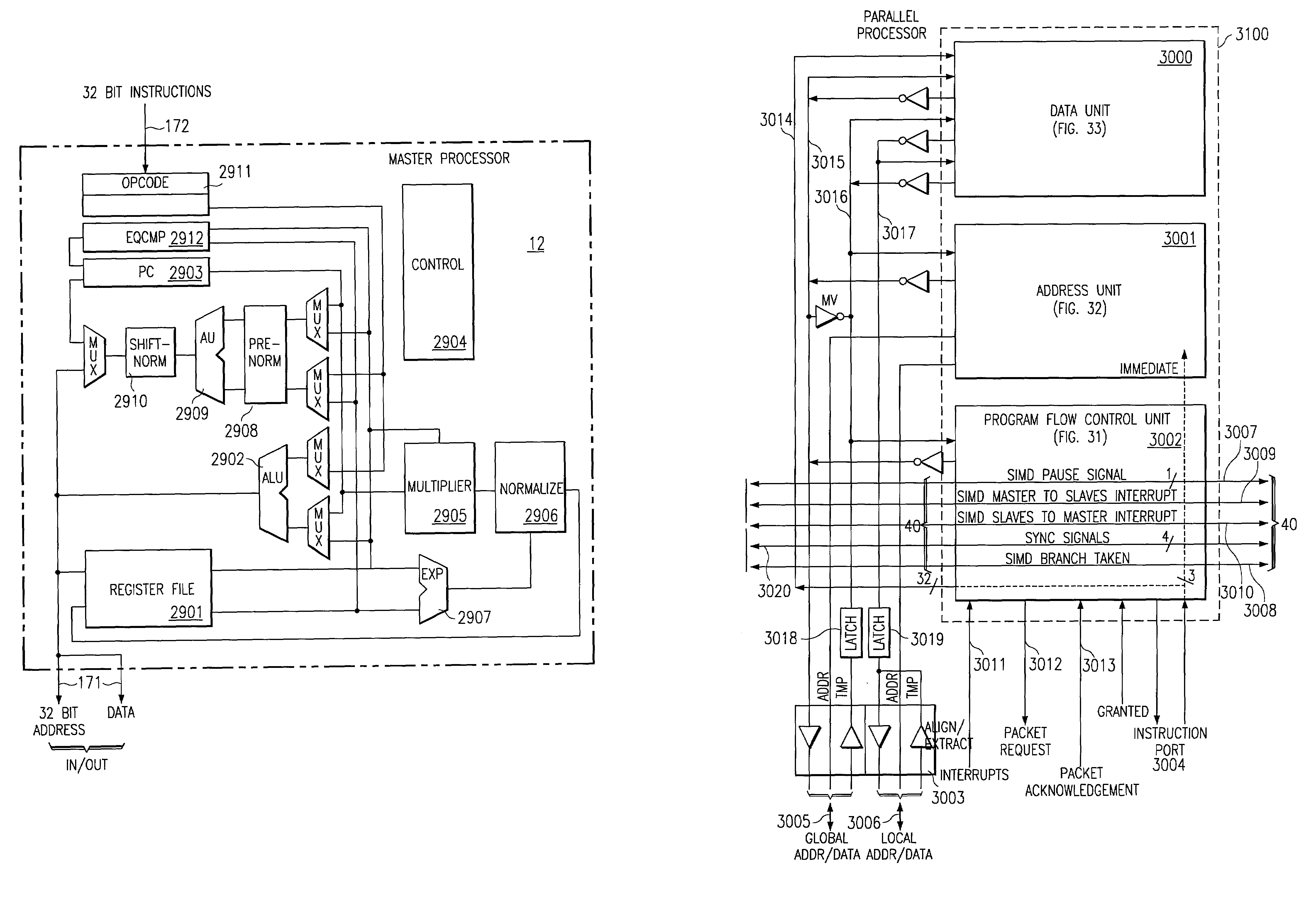

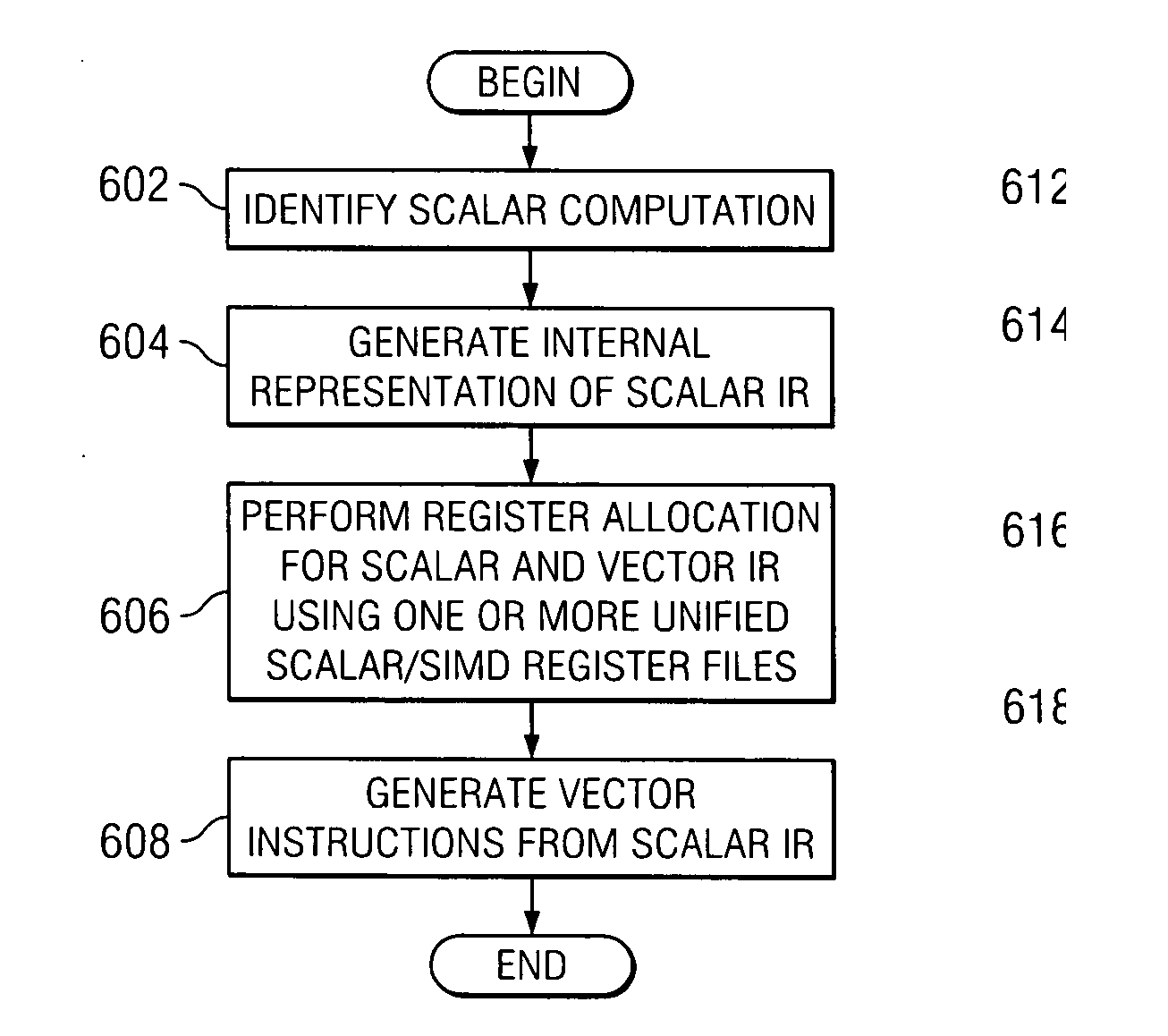

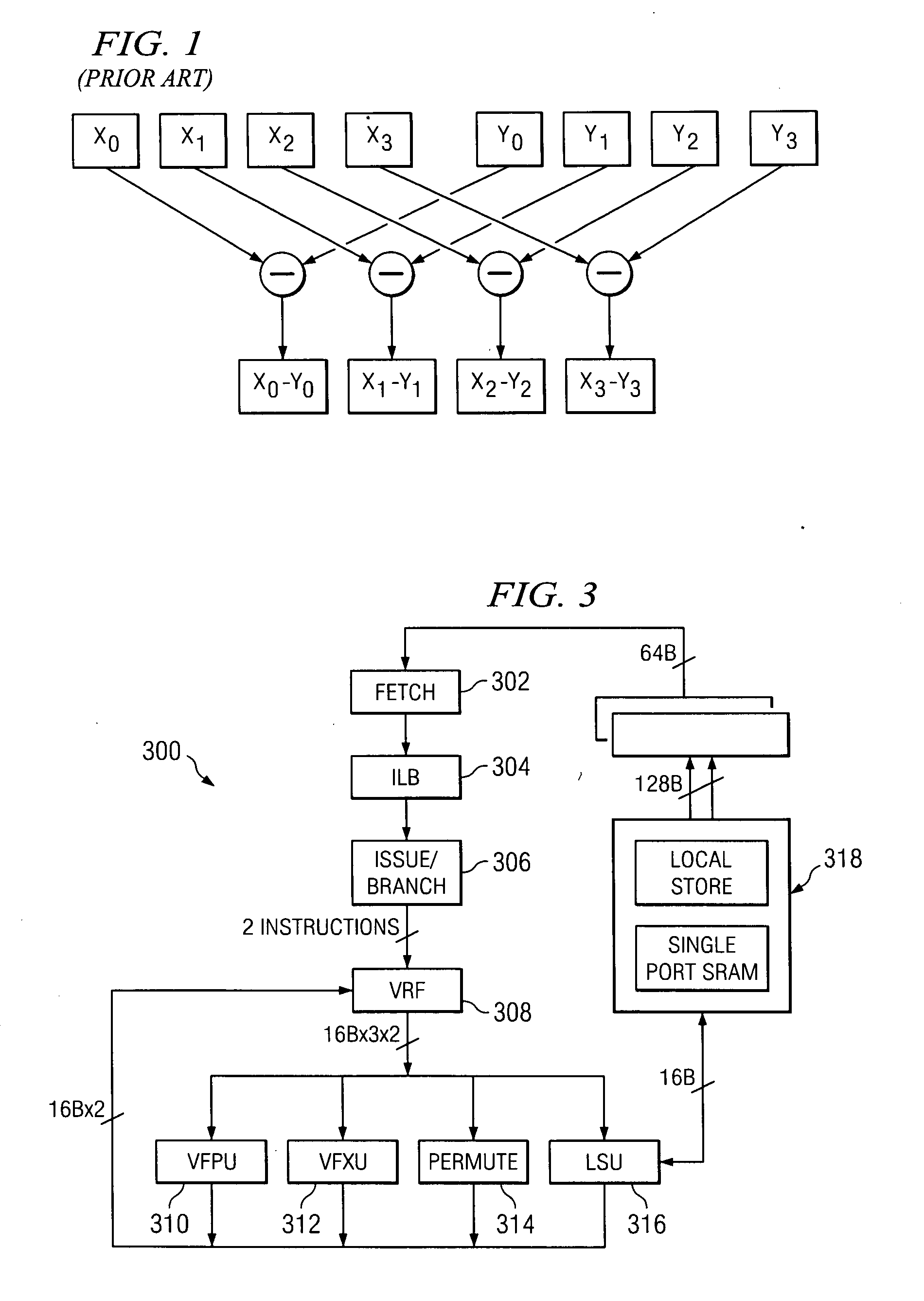

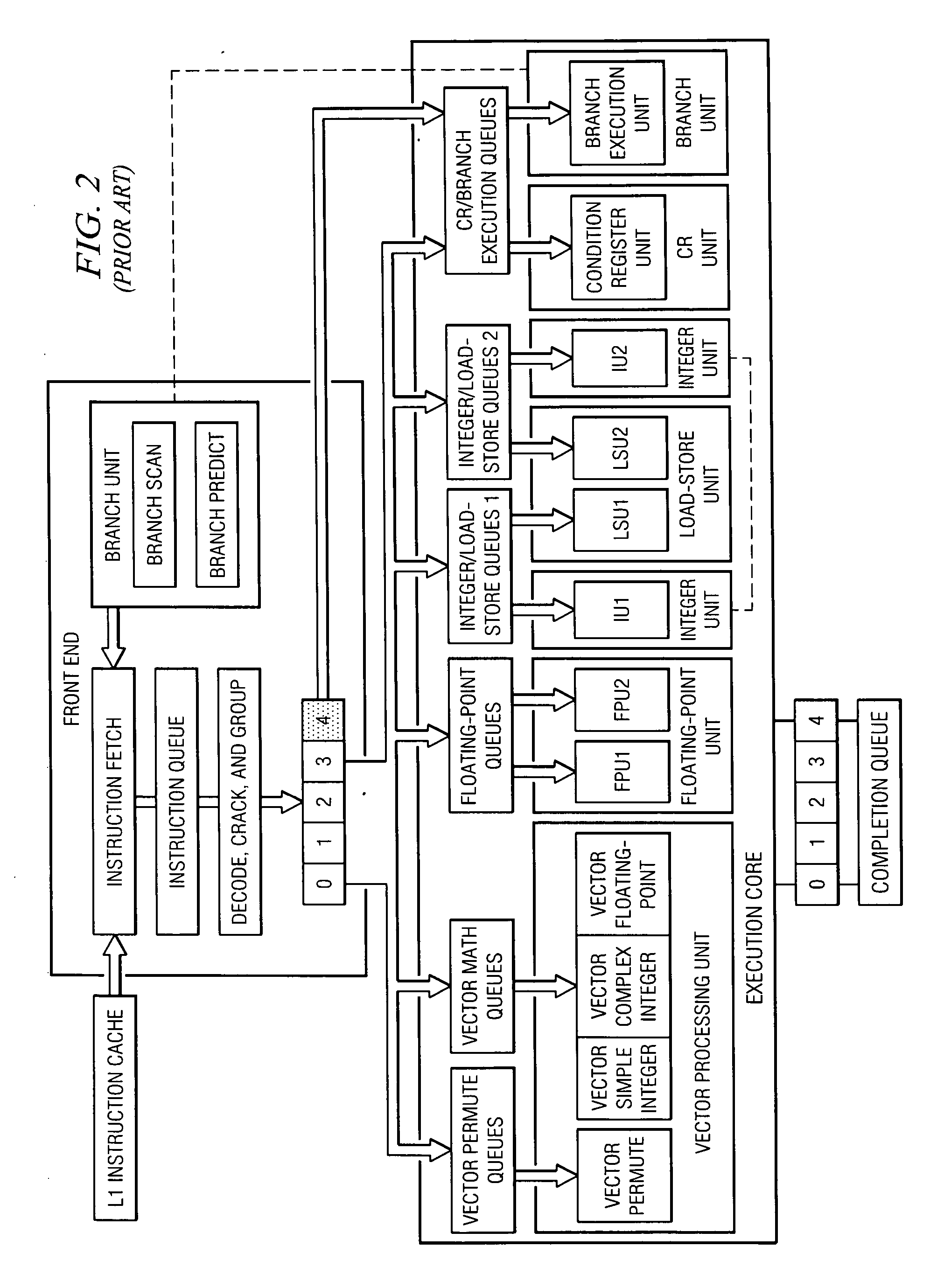

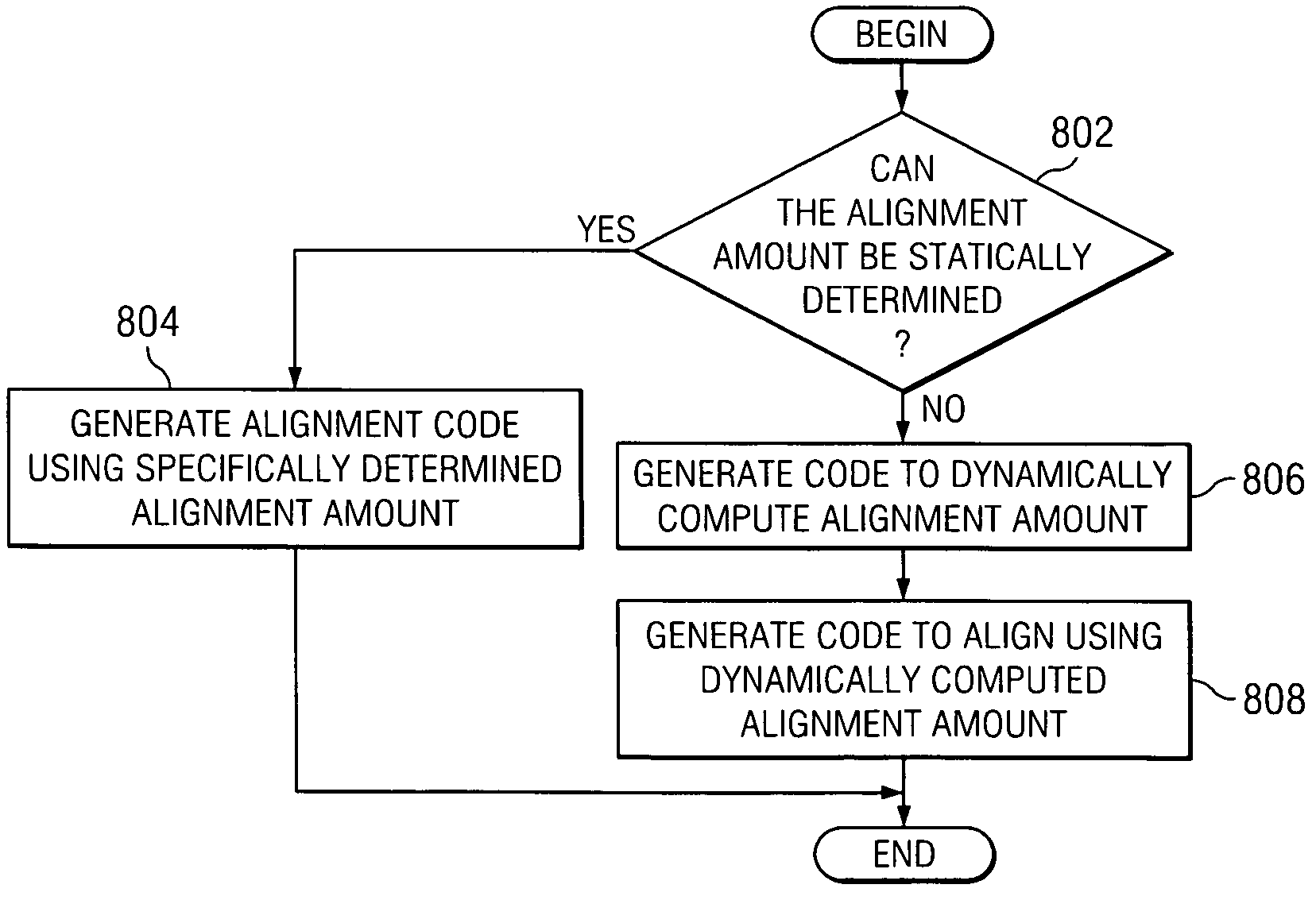

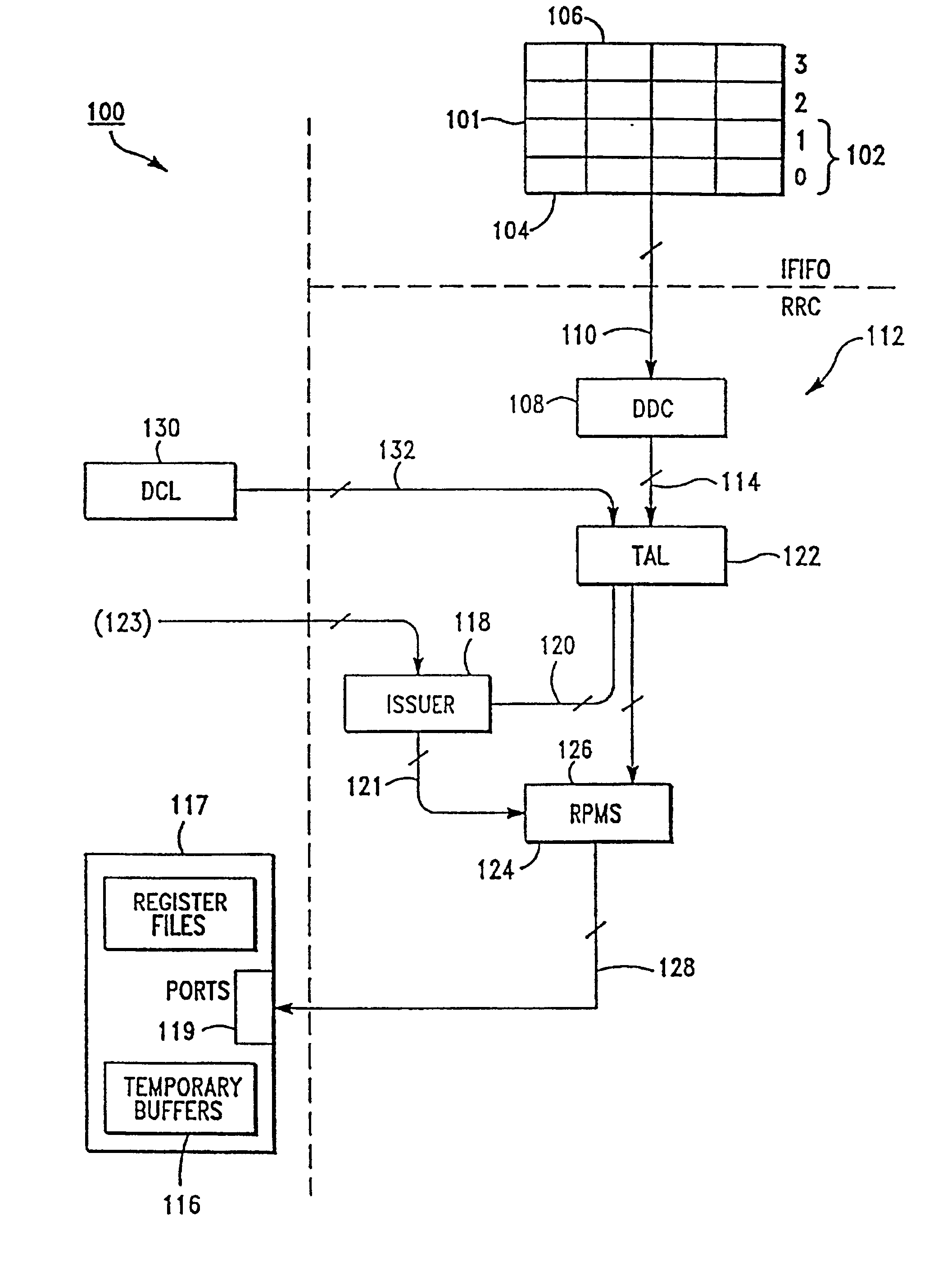

Compilation for a SIMD RISC processor

InactiveUS20070124722A1Software engineeringGeneral purpose stored program computerData processing systemScalar Value

A computer implemented method, data processing system, and computer usable code are provided for generating code to perform scalar computations on a Single-Instruction Multiple-Data (SIMD) Reduced Instruction Set Computer (RISC) architecture. The illustrative embodiments generate code directed at loading at least one scalar value and generate code using at least one vector operation to generate a scalar result, wherein all scalar computation for integer and floating point data is performed in a SIMD vector execution unit.

Owner:IBM CORP

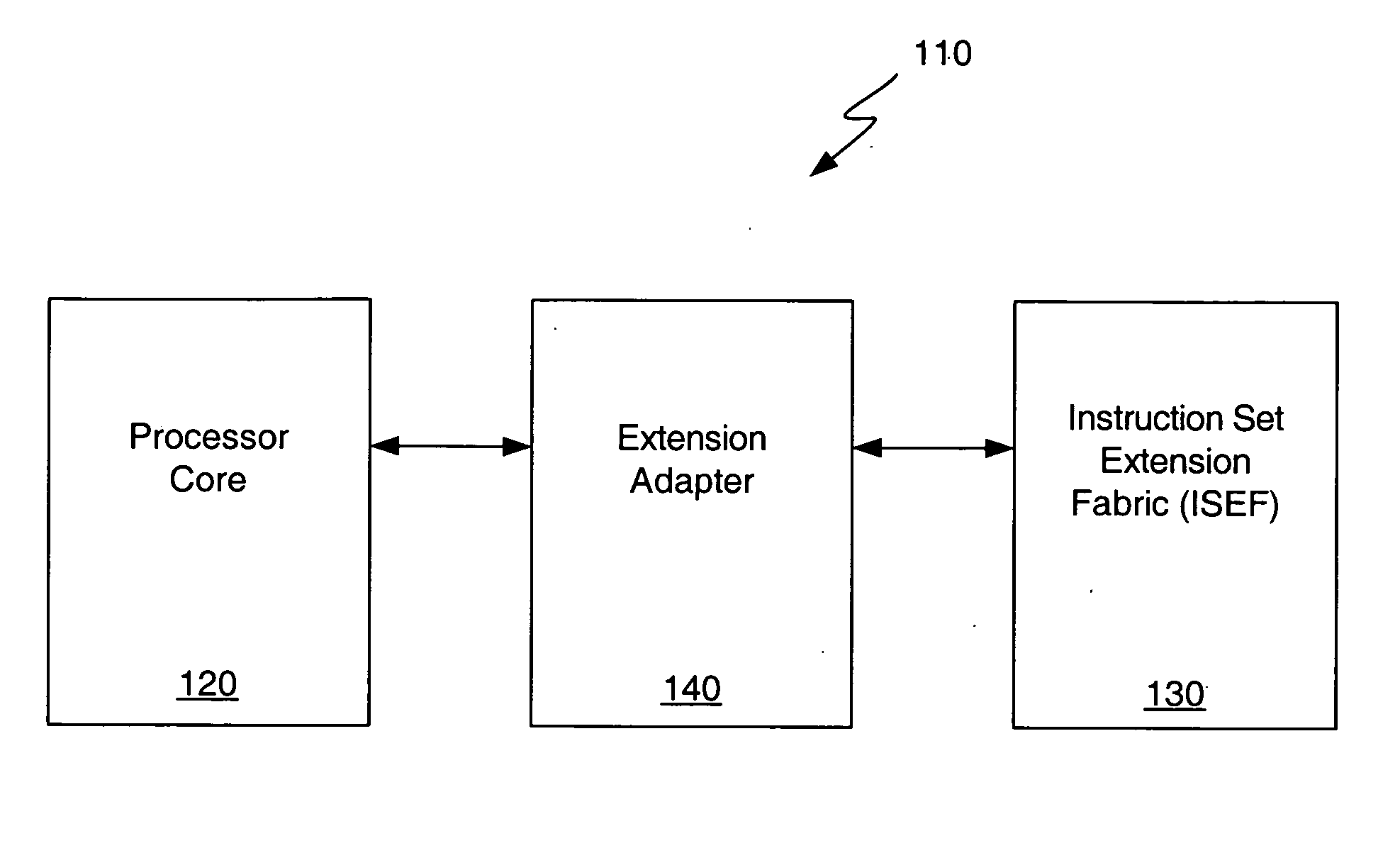

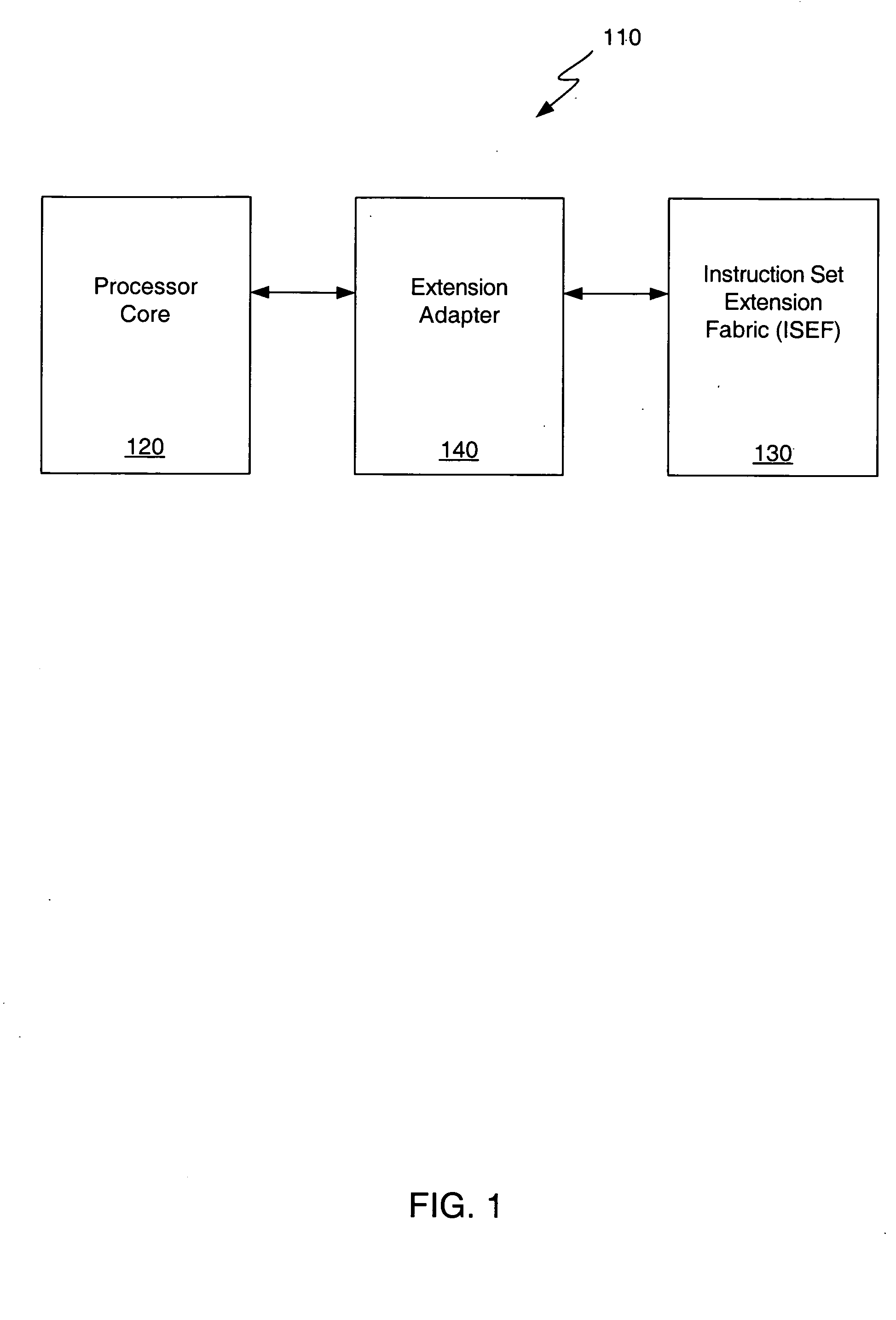

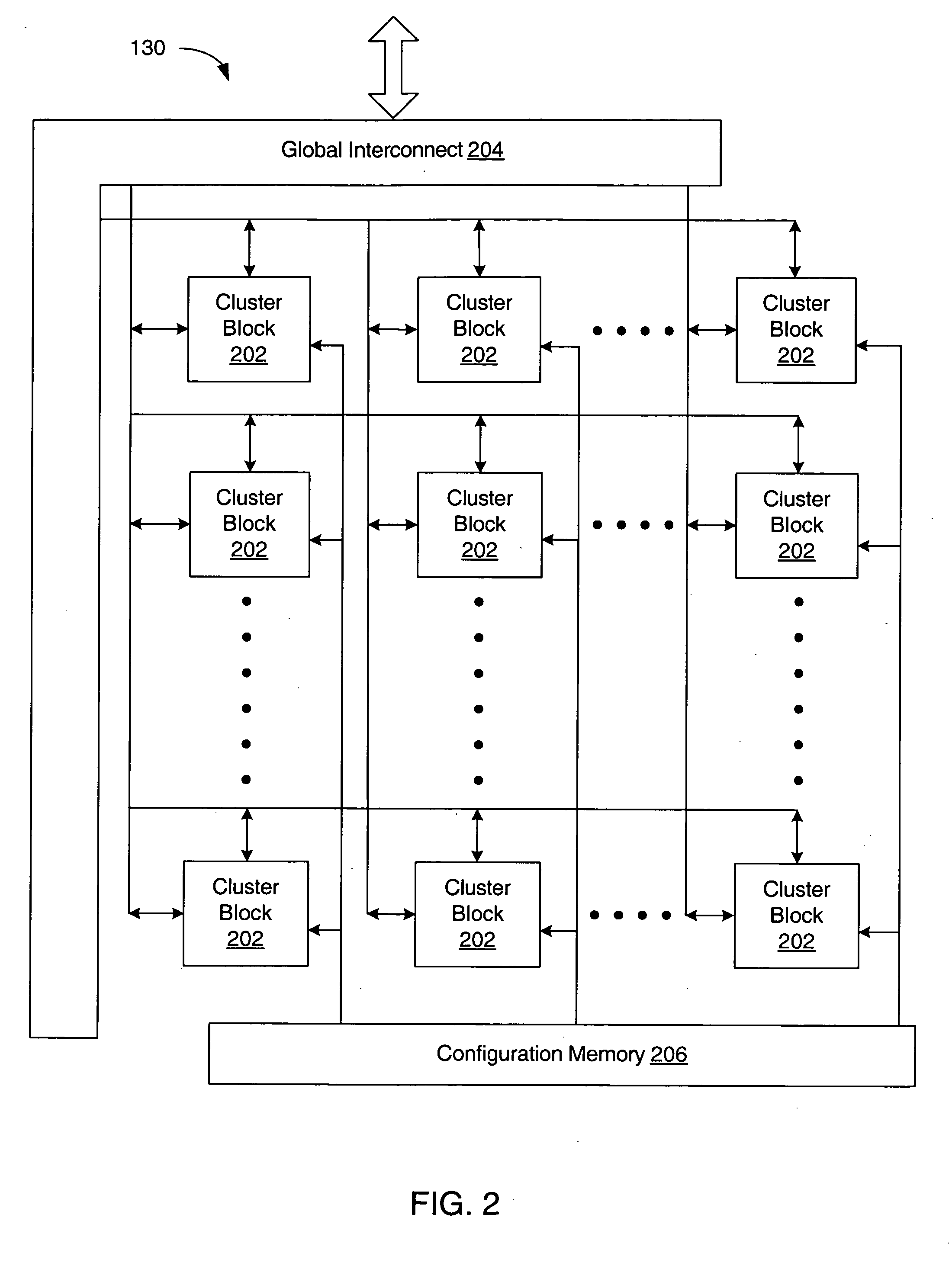

Reconfigurable instruction set computing

InactiveUS20050027970A1General purpose stored program computerConcurrent instruction executionInstruction memoryProgrammable logic device

A system and method for adding reconfigurable computational instructions to a reduced instruction set computer. A computer program contains instruction extensions not native to the instruction set of the processor core and is loaded into an instruction memory accessible by the processor core of the computer. The computer program is then detected for containing the instruction extension. The programmable logic device is then configured to execute the instruction extension. The programmable logic device then executes the instruction extension for use by the processor core in processing the computer program.

Owner:XILINX INC

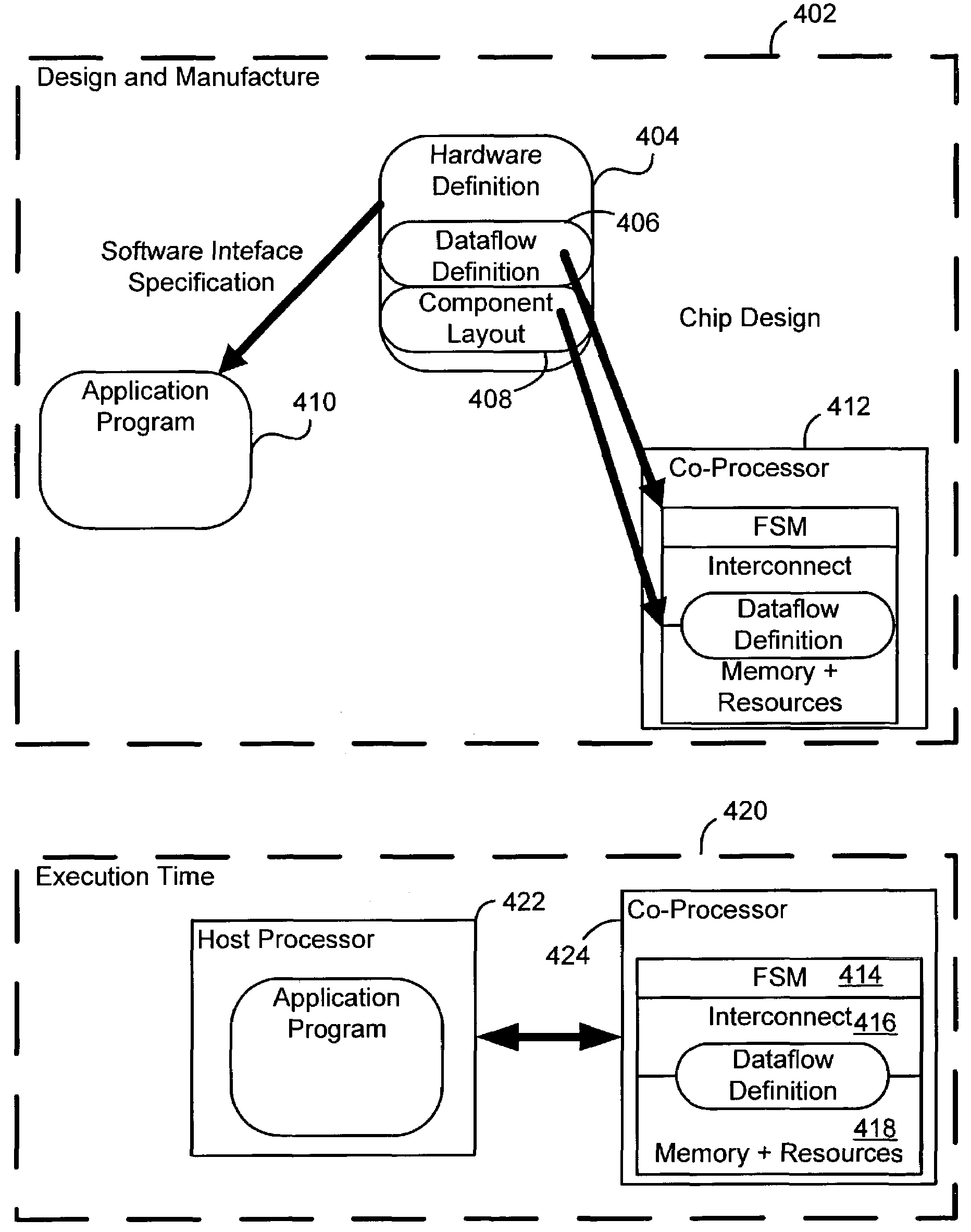

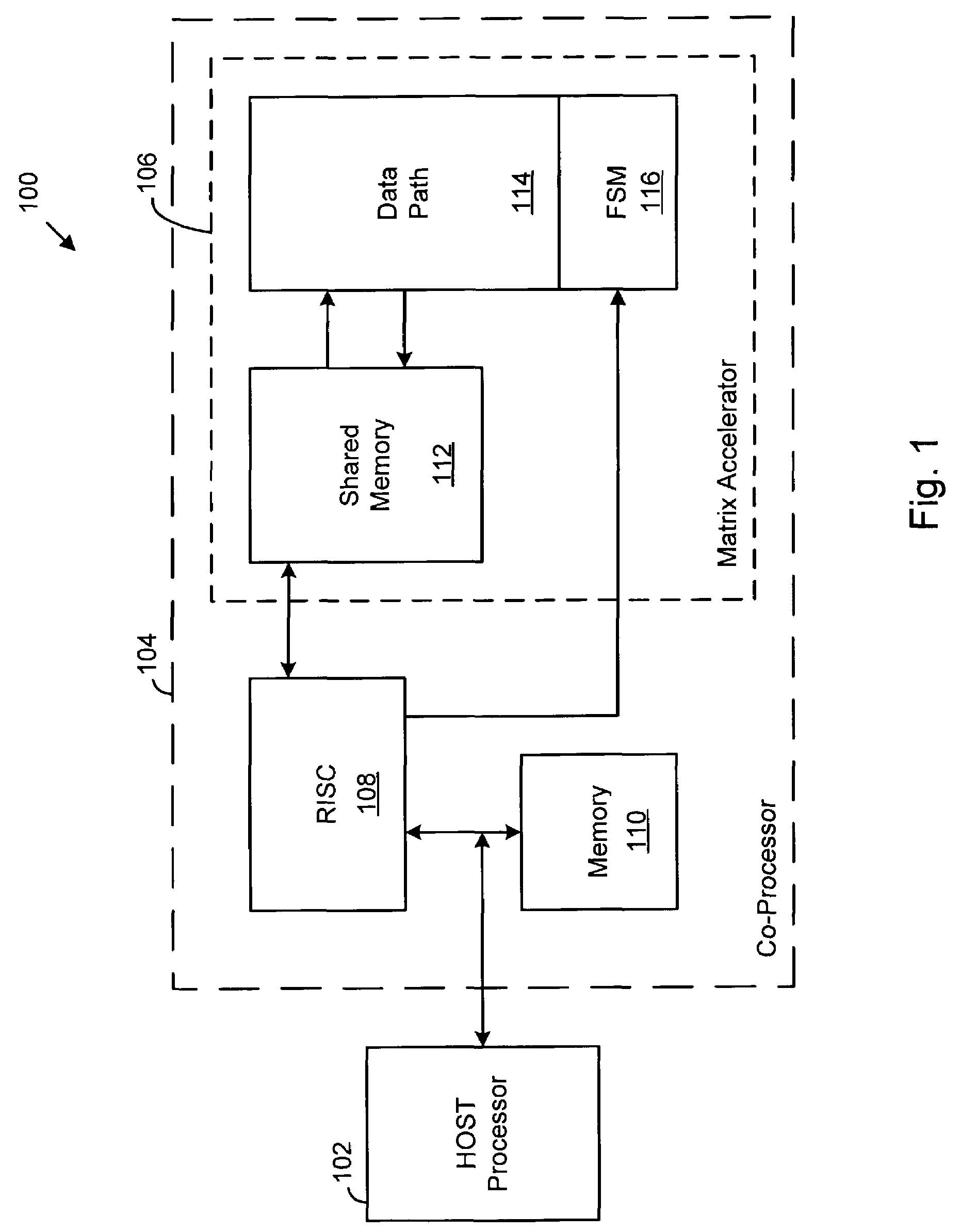

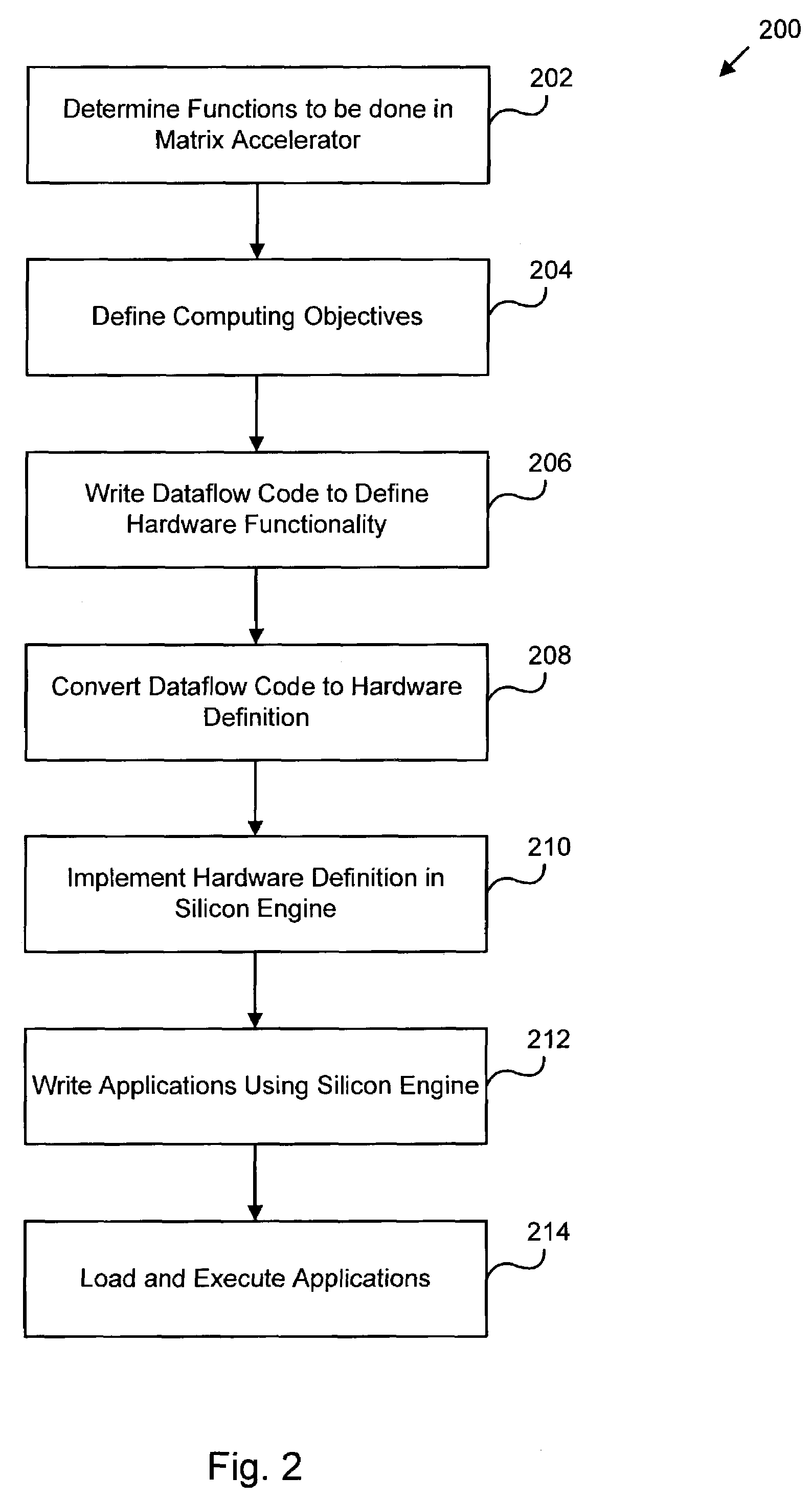

Digital processing architecture using compiled dataflow definition

A system whereby a data flow language written in relatively high-level description is compiled to a hardware definition. The hardware definition is then used to configure data flow in a target processing system at execution time, or run time. In a preferred embodiment, the target processing system includes a Reduced-Instruction Set Computer (RISC) processor in communication with a finite state machine (FSM), shared memory, on-board memory, and other resources. The FSM is primarily used for accelerating matrix operations and is considered the target machine to be configured according to the dataflow definition. The RISC processor serves as a co-processor to an external central processing unit (CPU) that is a host processor for executing application code. Other embodiments can use aspects of the invention in any other processing architecture. A dataflow language is used to define interconnections among hardware elements in the matrix datapath and controlled by FSM at run time and, thus, to determine hardware functionality at run time. The interconnectivity between the matrix datapath components, elements or resources, is capable of changing every clock cycle to optimize preferred calculations. The dataflow language is used to describe the optimized functions to an application programmer. The dataflow language is also compiled to a hardware definition that is used to create aspects of the desired functionality in silicon.

Owner:NVIDIA CORP

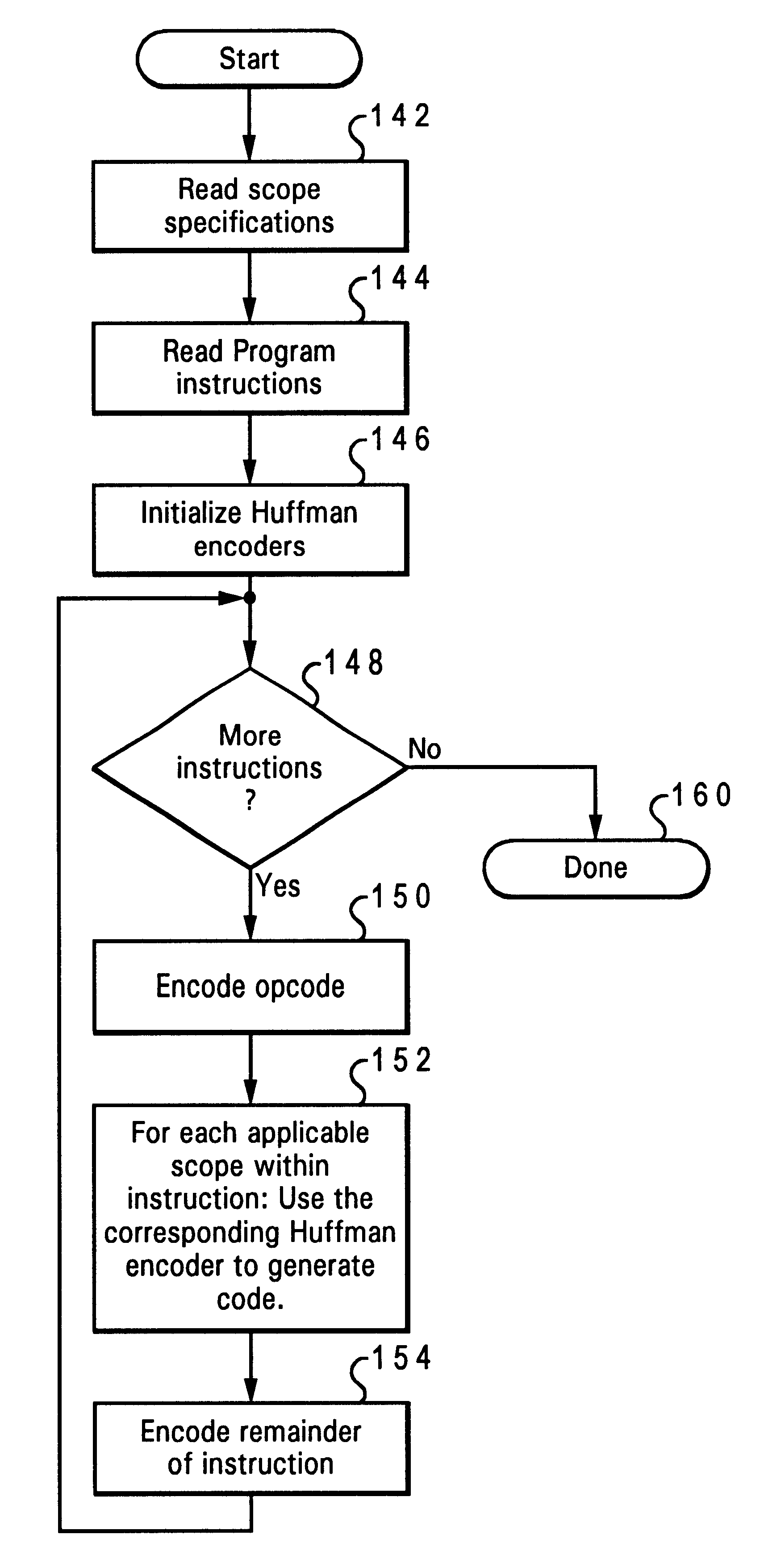

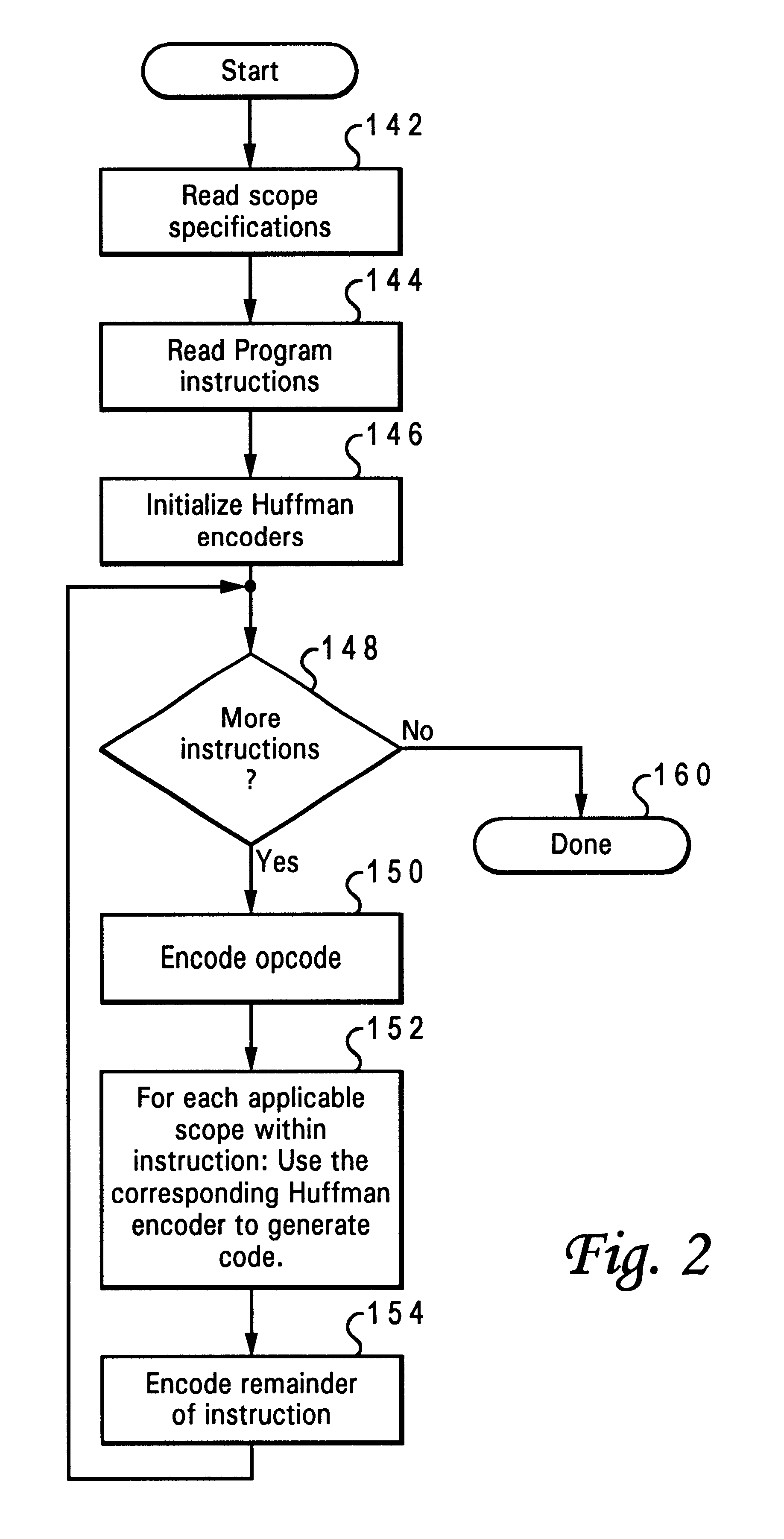

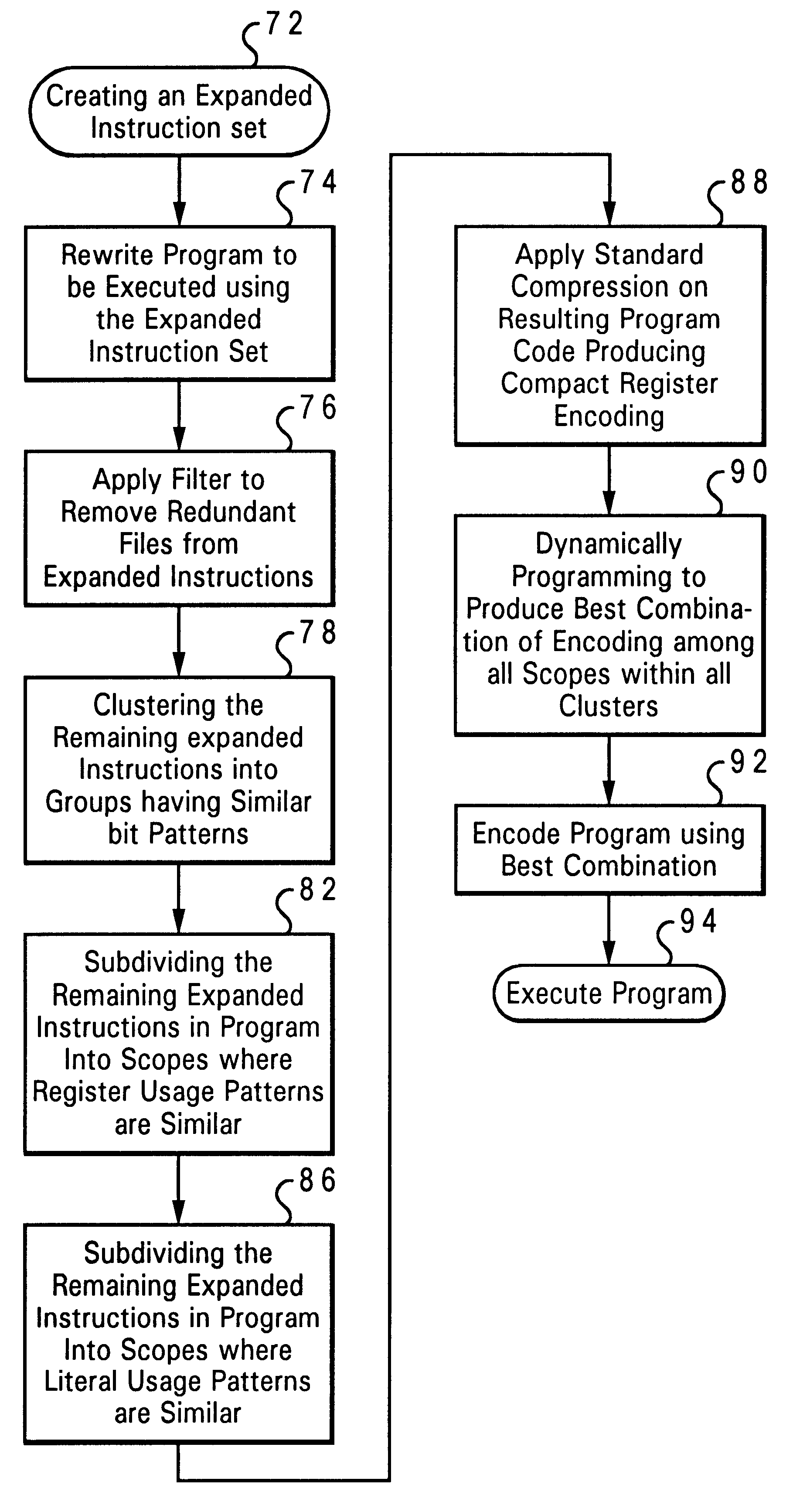

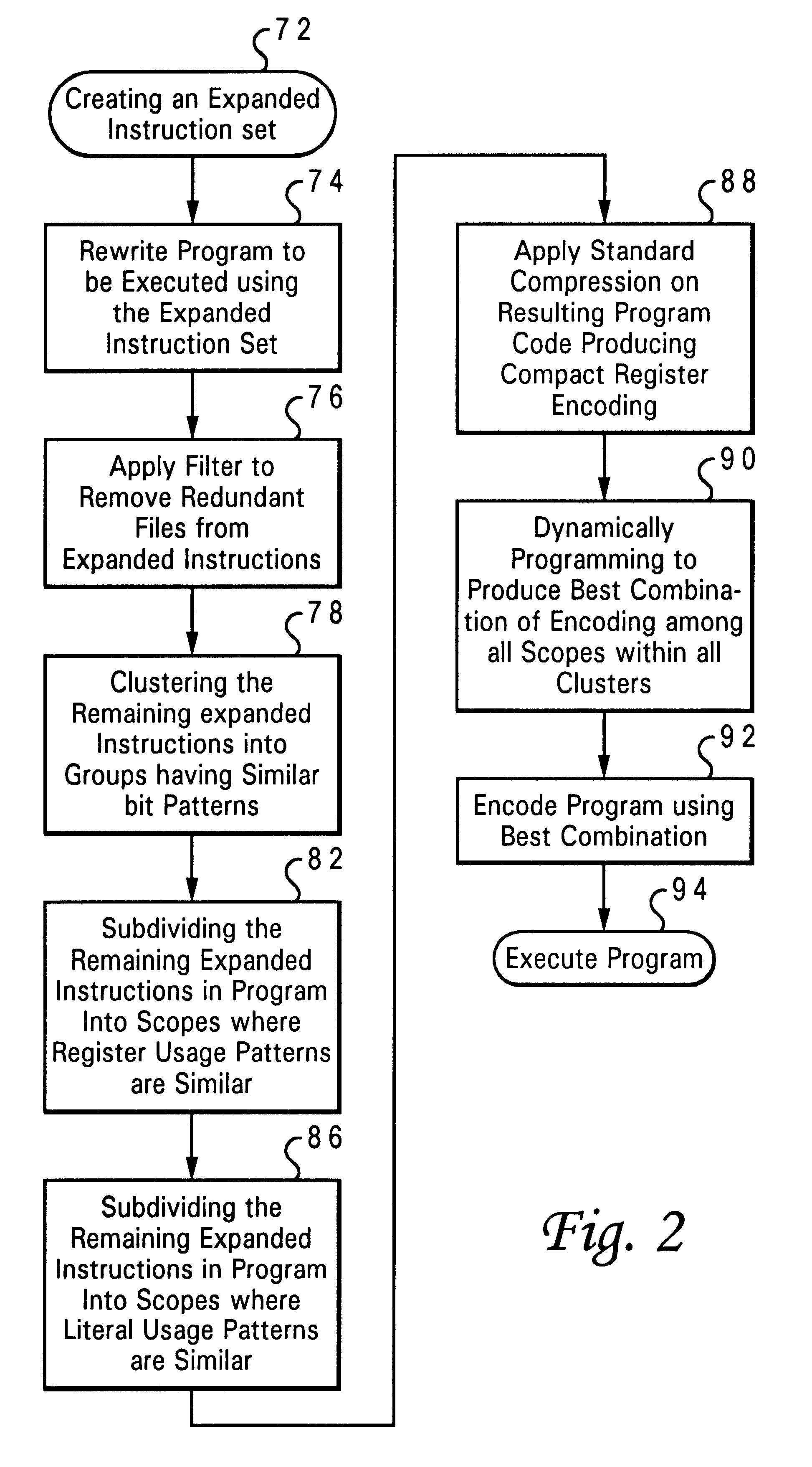

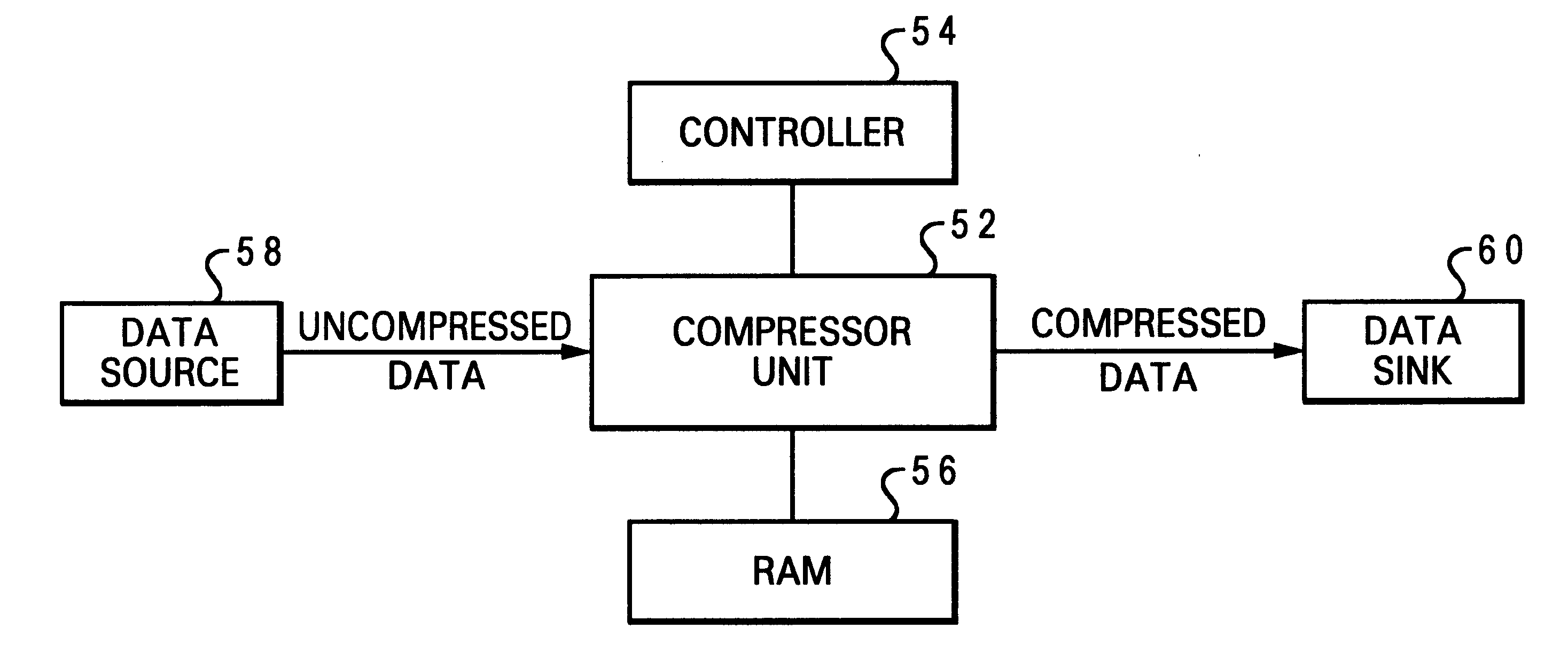

Method and system for scope-based compression of register and literal encoding in a reduced instruction set computer (RISC)

InactiveUS6233674B1Easy to compressEasily discerns the high pattern of usingSoftware engineeringRuntime instruction translationPowerPCProcessor register

A compression scheme for program executables that run in a reduced instruction set computer (RISC) architecture such as the PowerPC is disclosed. The method and system utilize scope-based compression for increasing the effectiveness of conventional compression with respect to register and literal encoding. First, discernible patterns are determined by exploiting instruction semantics and conventions that compilers adopt in register and literal usage. Additional conventions may also be set for register usage to facilitate compression. Using this information, separate scopes are created such that in each scope there is a more prevalent usage of a limited set of registers or literal value ranges, or there is an easily discernible pattern of register or literal usage. Each scope then is compressed separately by a conventional compressor. The resulting code is more compact because the small number of registers and literals in each scope makes the encoding sparser than when the compressor operates on the global scope that includes all instructions in a program. Additionally, scope-based compression reveals more frequent patterns within each scope than when considering the entire instruction stream as an opaque stream of bits.

Owner:IBM CORP

Thread suspension system and method

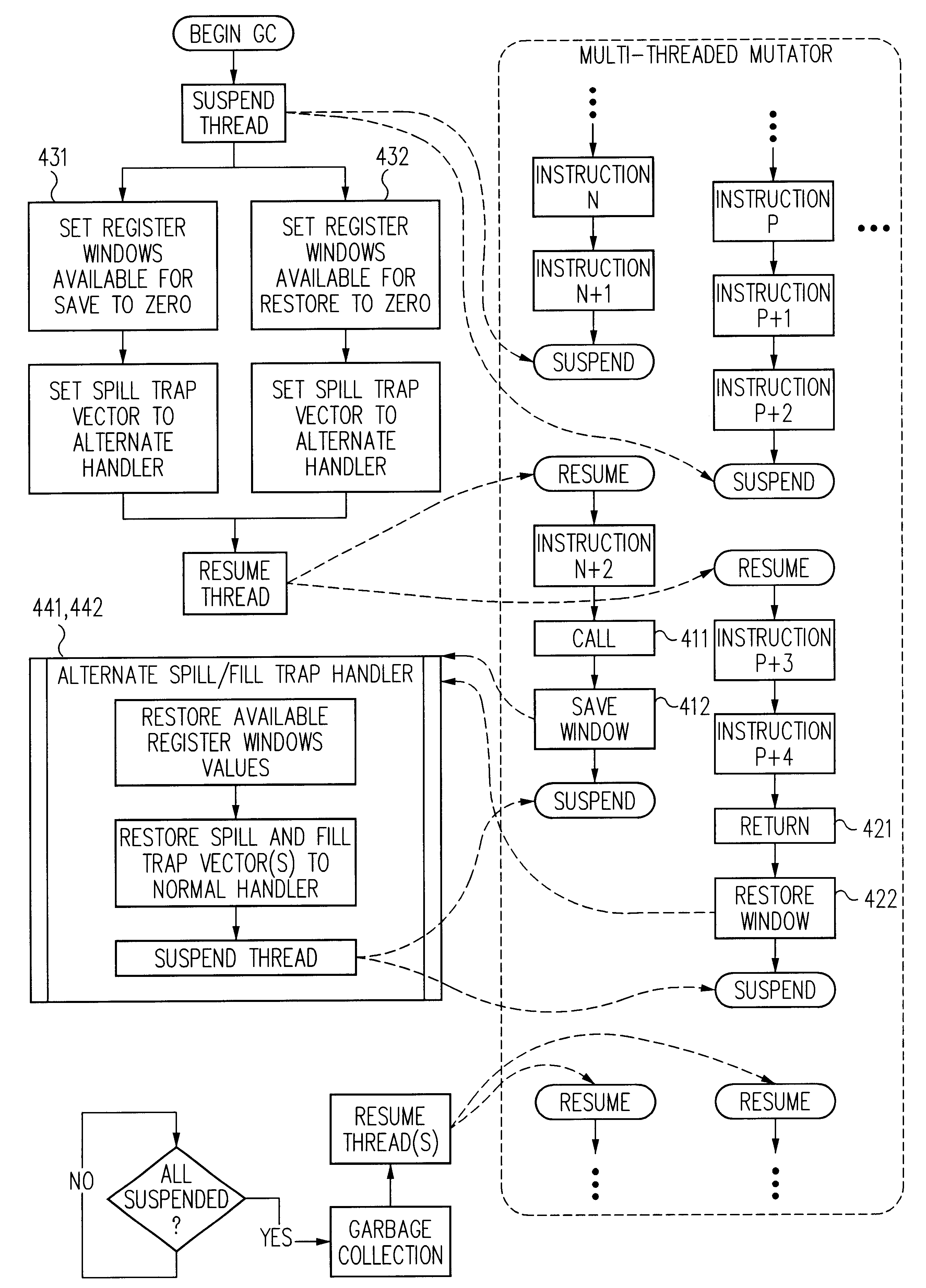

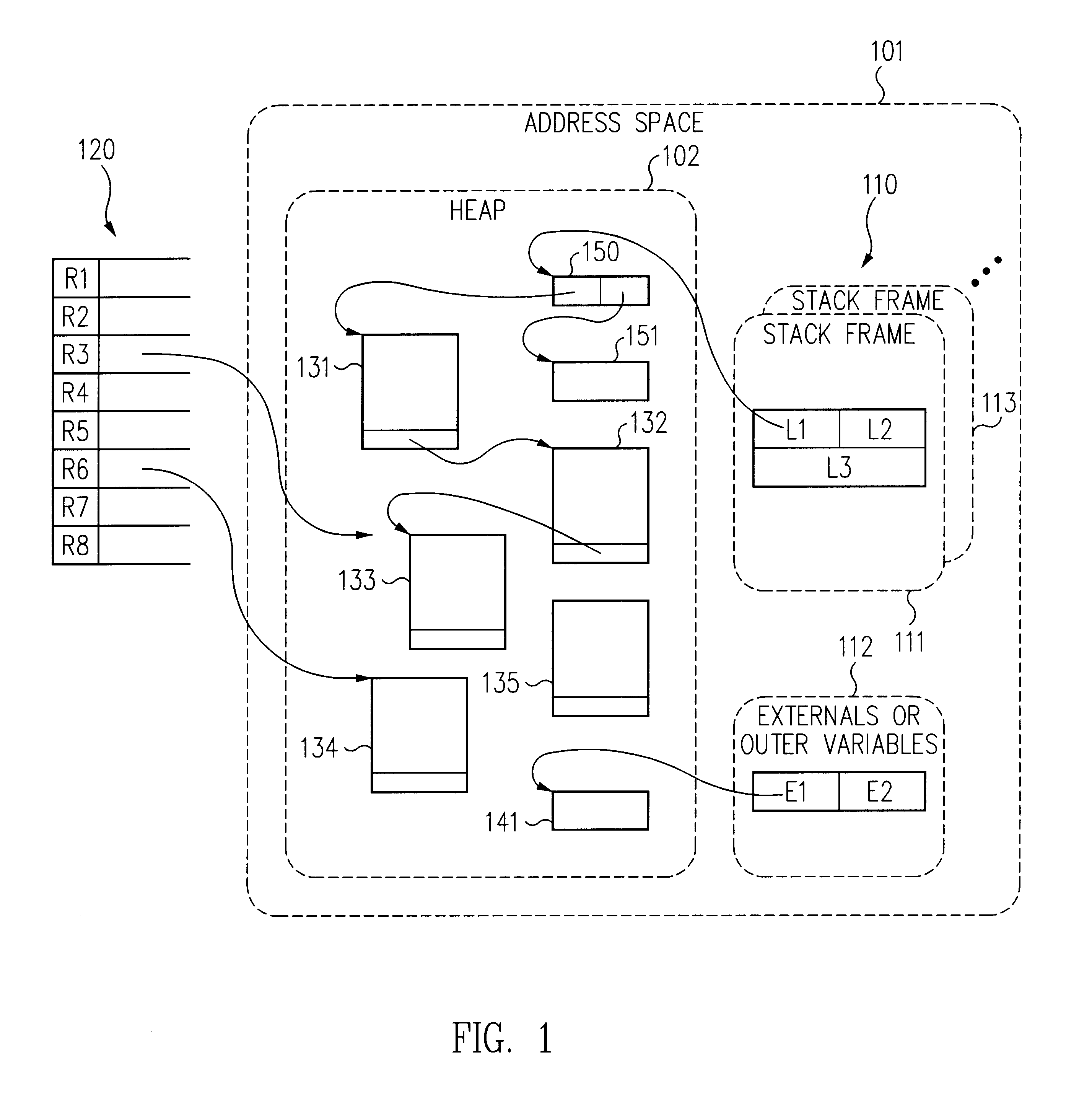

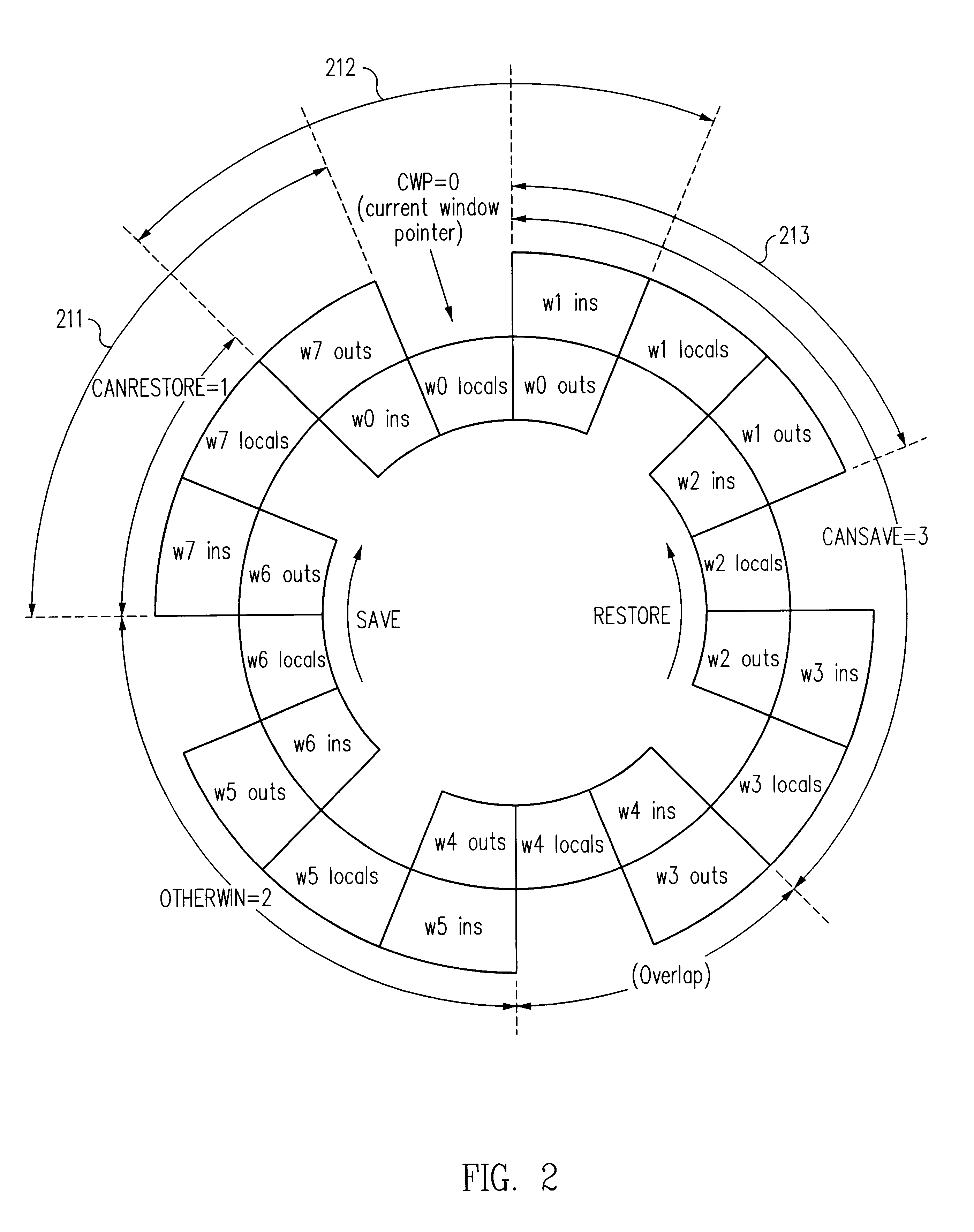

InactiveUS6842853B1Negligible overheadLower latencyMemory adressing/allocation/relocationDigital computer detailsRegister windowInstruction set

In processor architectures that support allocation of register windows to called procedures, functions or methods, register windowing mechanisms can be used to facilitate suspension of a mutator thread (or mutator threads) while imposing negligible overhead on the mutator computation during periods when thread suspension is not requested. Reduced Instruction Set Computer-(RISC)-oriented processor architectures often employ register windows (typically partially-overlapped register windows) and can therefore benefit from the technique. Variations can be employed even in processors (RISC or otherwise) that do not employ register windowing as long as the processor (by itself or in cooperation with software) provides facilities for allocating and reclaiming resources in correspondence with calls to, and returns from, procedures, functions or methods. Mechanisms are provided to spill values from the fixed set of resources to a secondary store and to fill values from the secondary store into the fixed set in correspondence with function call triggered overflows and function return triggered underflows. In some configurations, modified spill and / or fill mechanism(s) are used to suspend threads at safe points coinciding with call and / or return sites. Because the modified spill and / or fill mechanism(s) impose negligible overhead when not employed and can be engaged in response to an event (e.g., a start garbage collection event), safe points can be defined at call and / or return points throughout mutator code to reduce the latency between the event and suspension of threads.

Owner:ORACLE INT CORP

Compilation for a SIMD RISC processor

InactiveUS7840954B2Software engineeringGeneral purpose stored program computerData processing systemScalar Value

A computer implemented method, data processing system, and computer usable code are provided for generating code to perform scalar computations on a Single-Instruction Multiple-Data (SIMD) Reduced Instruction Set Computer (RISC) architecture. The illustrative embodiments generate code directed at loading at least one scalar value and generate code using at least one vector operation to generate a scalar result, wherein all scalar computation for integer and floating point data is performed in a SIMD vector execution unit.

Owner:INT BUSINESS MASCH CORP

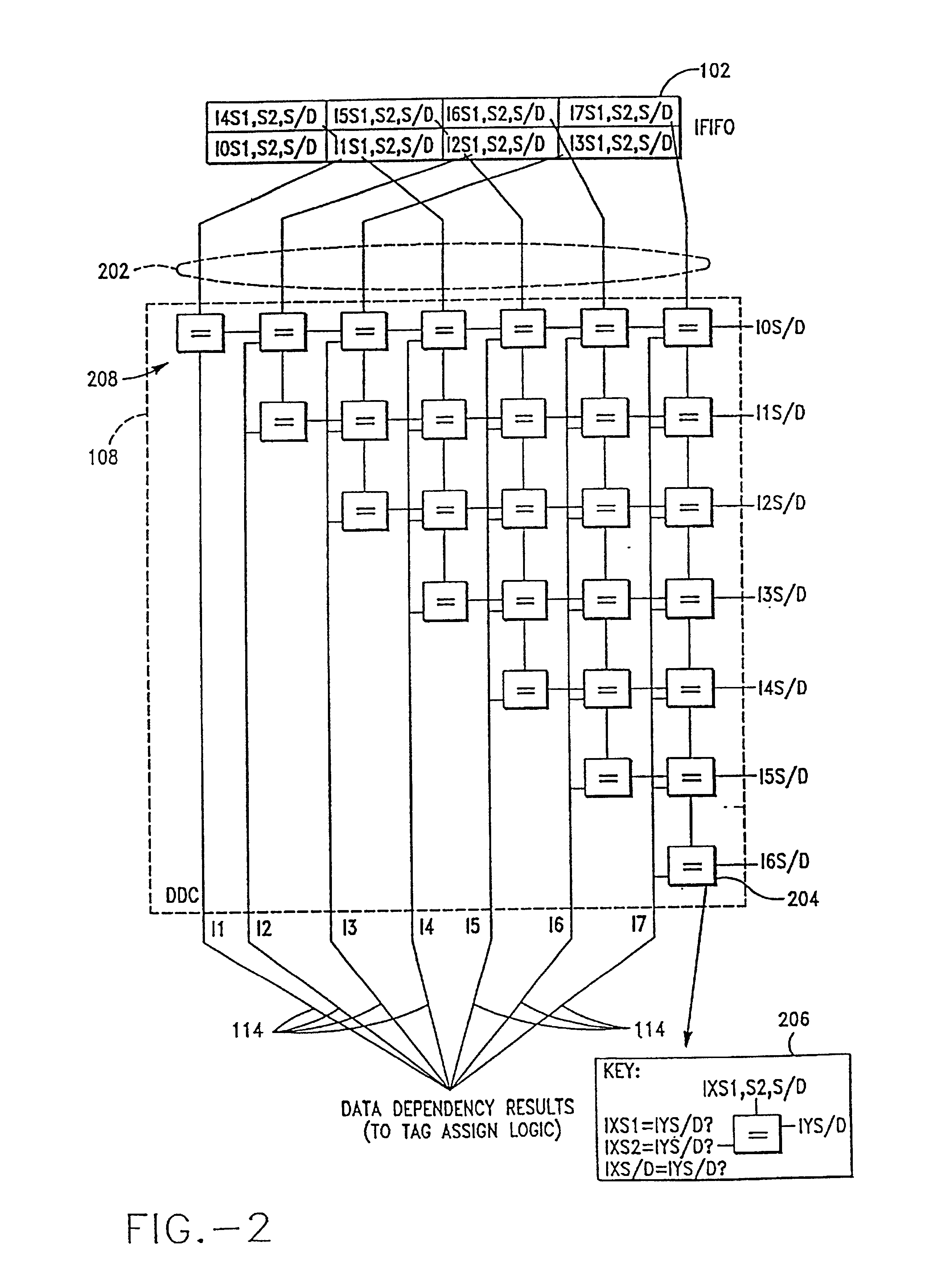

Superscalar RISC instruction scheduling

InactiveUS7051187B2Saving chip area/cost and execution speedRegister arrangementsGeneral purpose stored program computerScheduling instructionsMultiplexer

A register renaming system for out-of-order execution of a set of reduced instruction set computer instructions having addressable source and destination register fields, adapted for use in a computer having an instruction execution unit with a register file accessed by read address ports and for storing instruction operands. A data dependance check circuit is included for determining data dependencies between the instructions. A tag assignment circuit generates one or more tags to specify the location of operands, based on the data dependencies determined by the data dependance check circuit. A set of register file port multiplexers select the tags generated by the tag assignment circuit and pass the tags onto the read address ports of the register file for storing execution results.

Owner:HANGER SOLUTIONS LLC

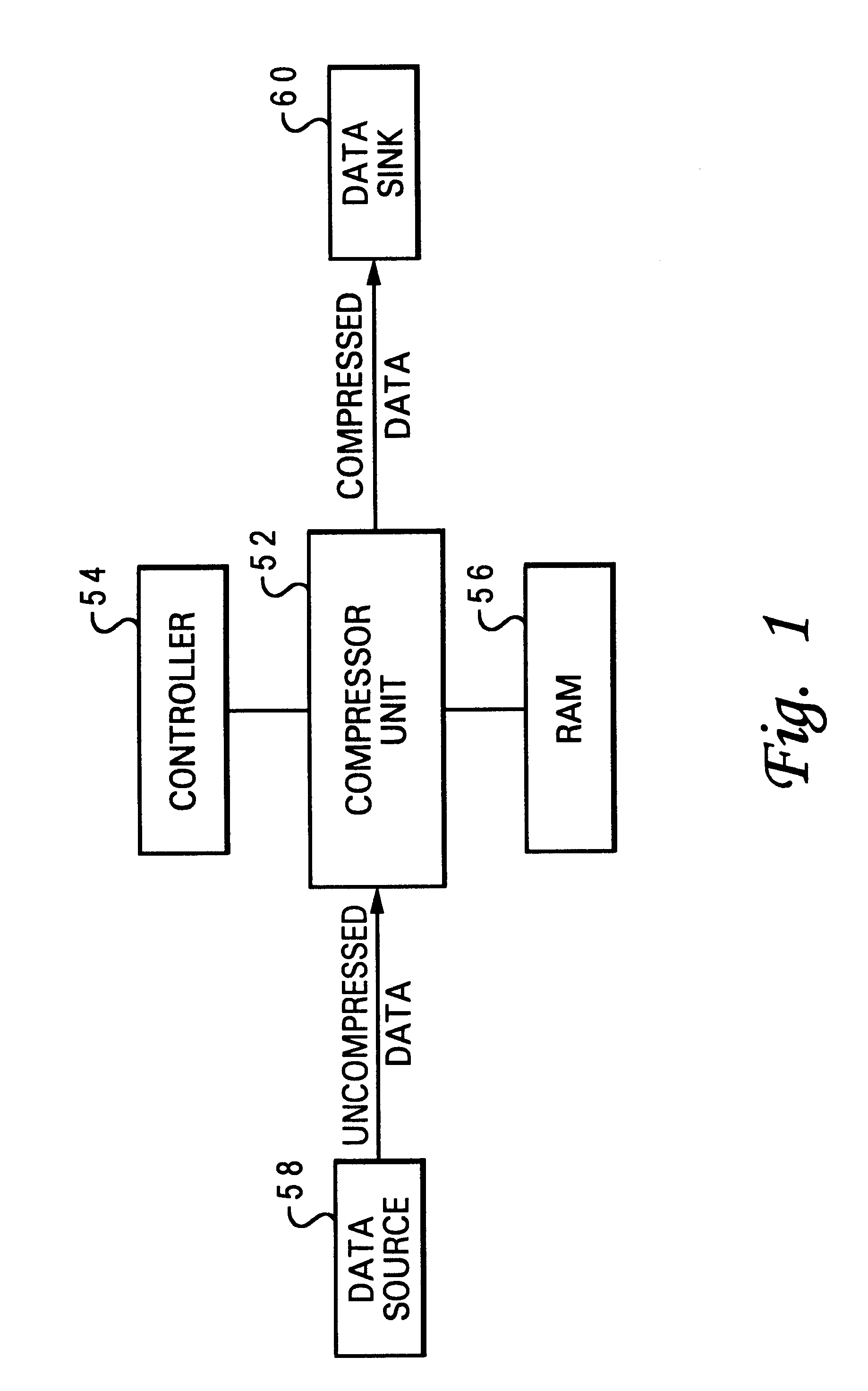

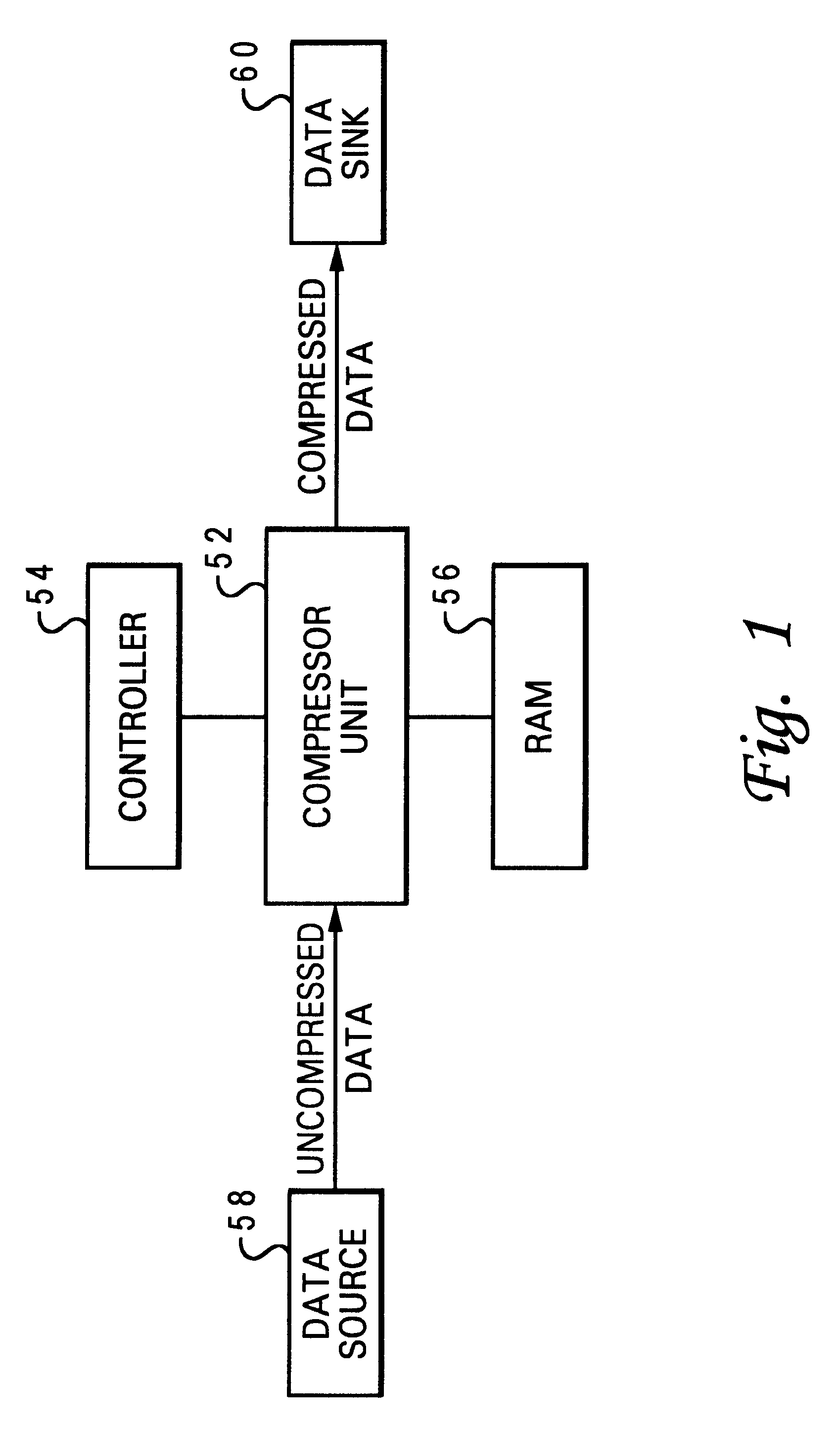

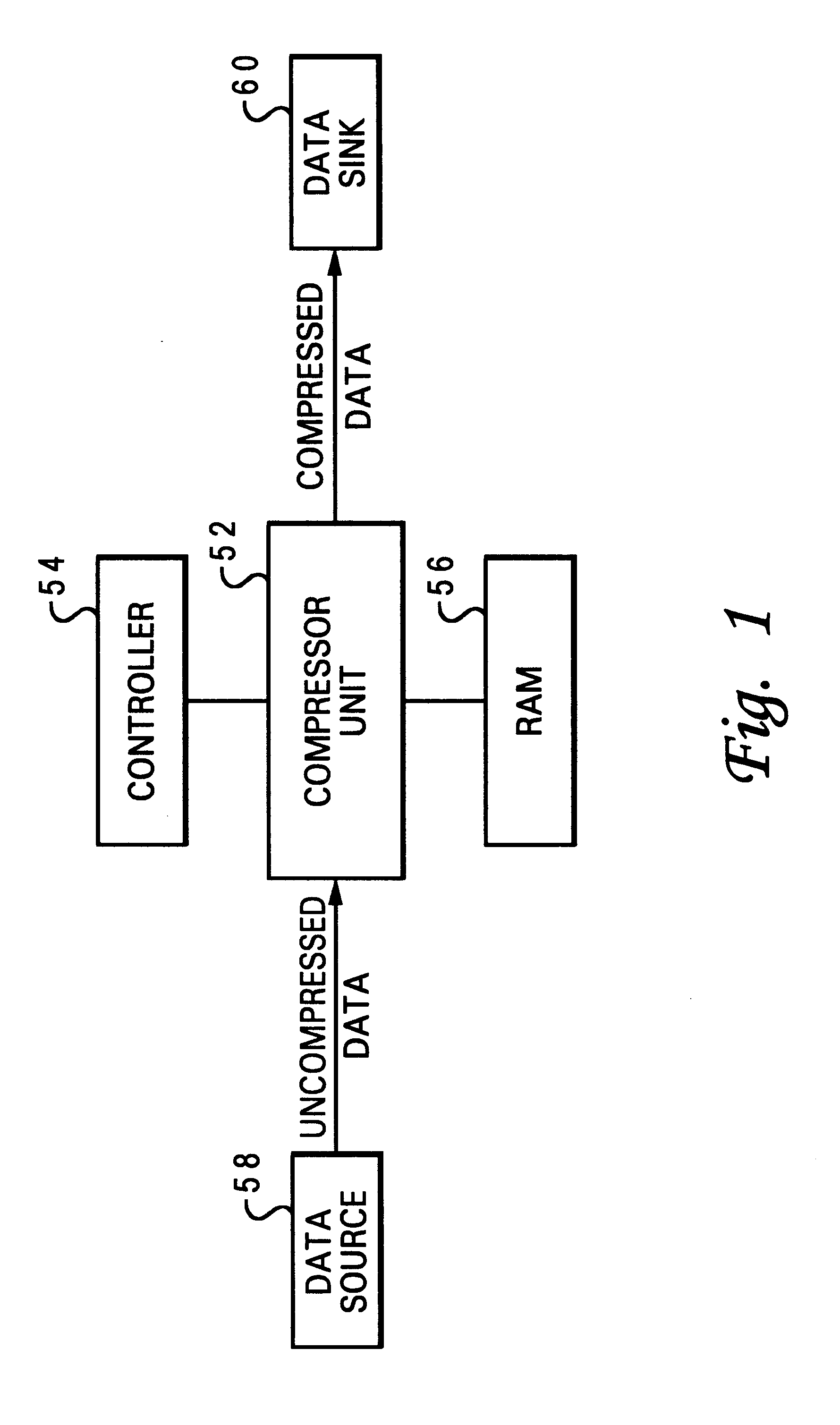

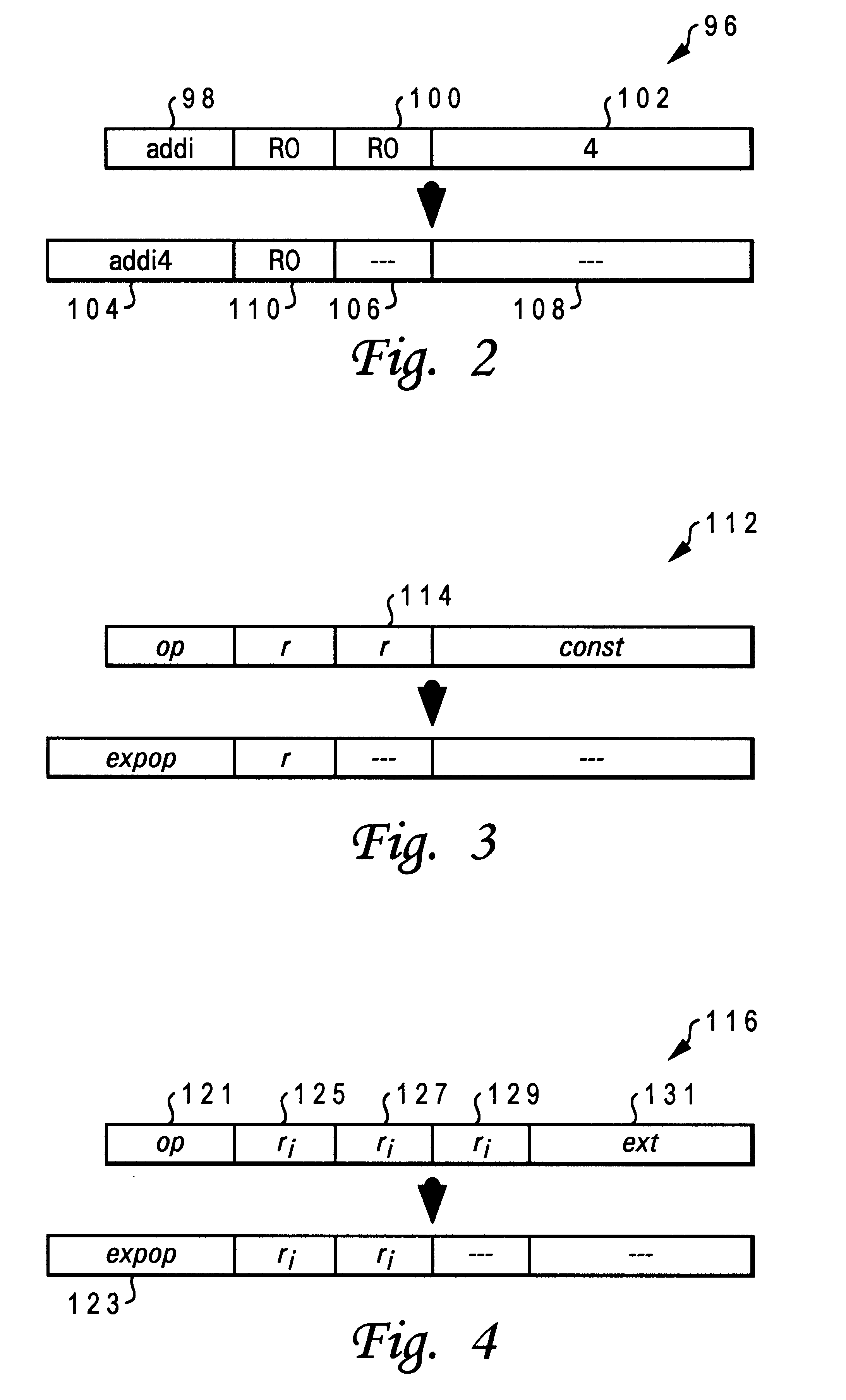

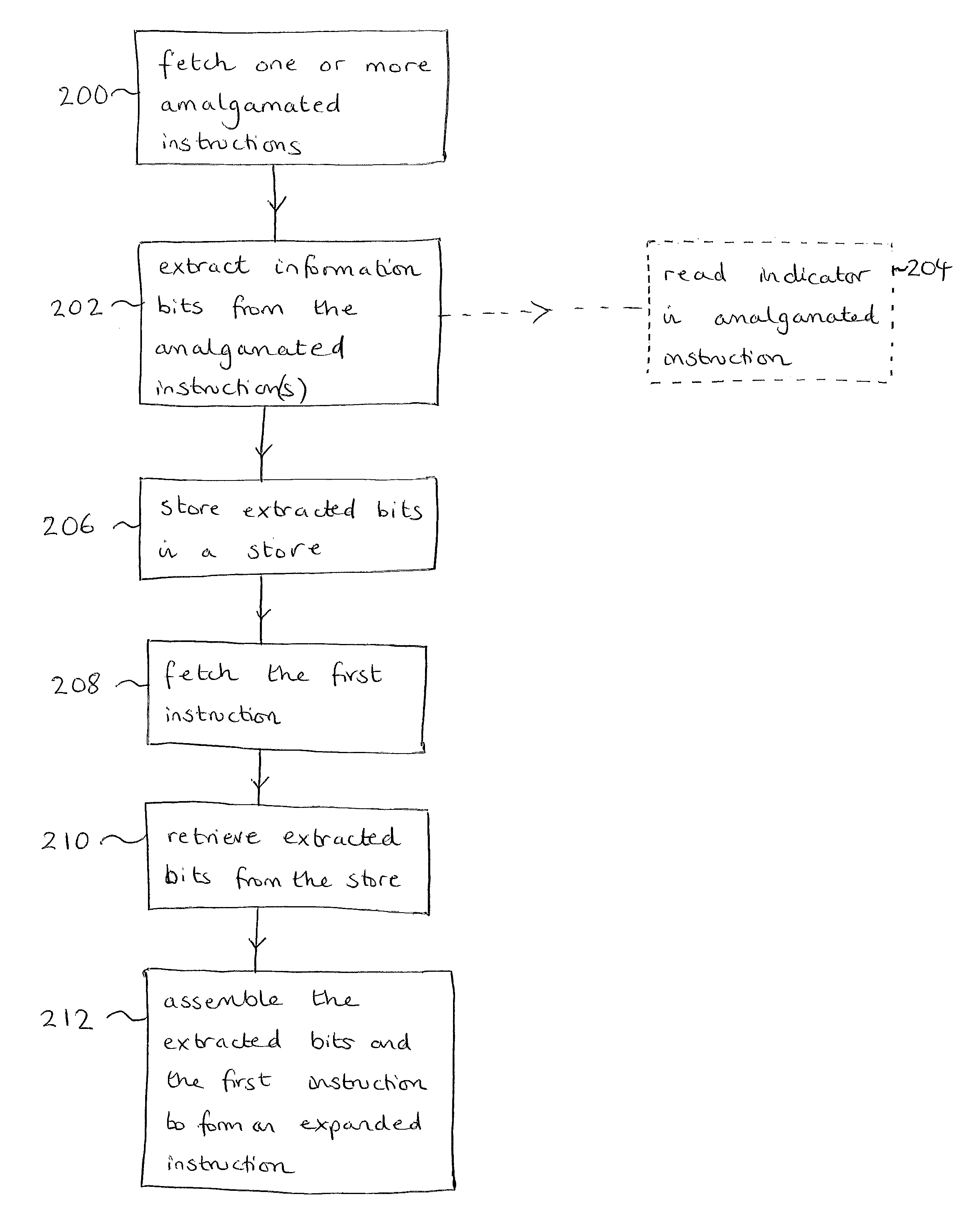

Method and system for compressing reduced instruction set computer (RISC) executable code

InactiveUS6442680B1Eliminate redundancySoftware engineeringDigital computer detailsPowerPCProcessor register

A method and system for a compression scheme used with program executables that run in a reduced instruction set computer (RISC) architecture such as the PowerPC is disclosed. Initially, a RISC instruction set is expanded to produce code that facilitates the removal of redundant fields. The program is then rewritten using this new expanded instruction set. Next, a filter is applied to remove redundant fields from the expanded instructions. The expanded instructions are then clustered into groups, such that instructions belonging to the same cluster show similar bit patterns. Within each cluster, the scopes are created such that register usage patterns within each scope are similar. Within each cluster, more scopes are created such that literals within each instruction scope are drawn from the same range of integers. A conventional compression technique such as Huffman encoding is then applied on each instruction scope within each cluster. Dynamic programming techniques are then used to produce the best combination of encoding among all scopes within all the different clusters. Where applicable, instruction scopes are combined that use the same encoding scheme to reduce the size of the resulting dictionary. Similarly instruction clusters are combined that use the same encoding scheme to reduce the size of the resulting dictionary.

Owner:IBM CORP

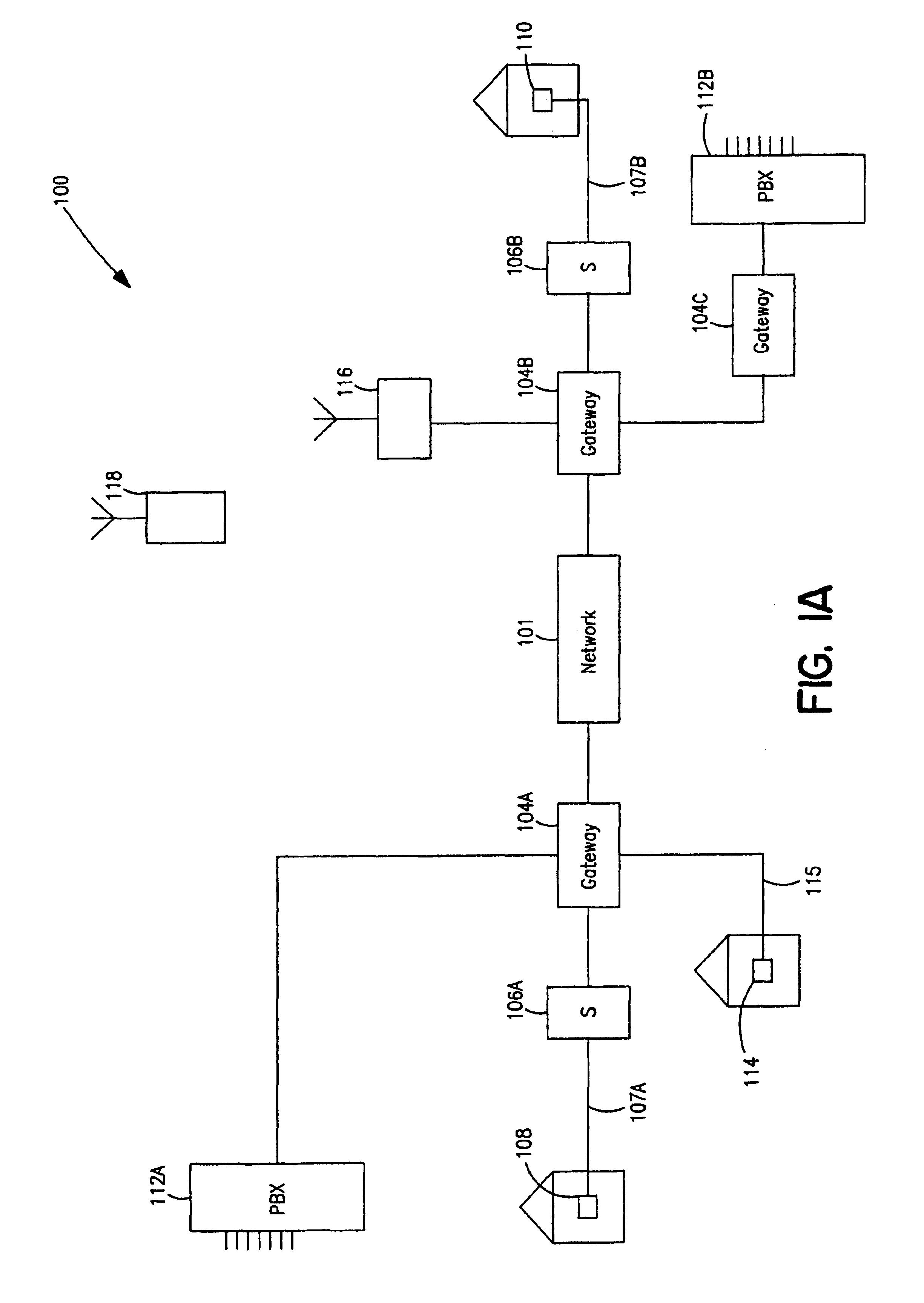

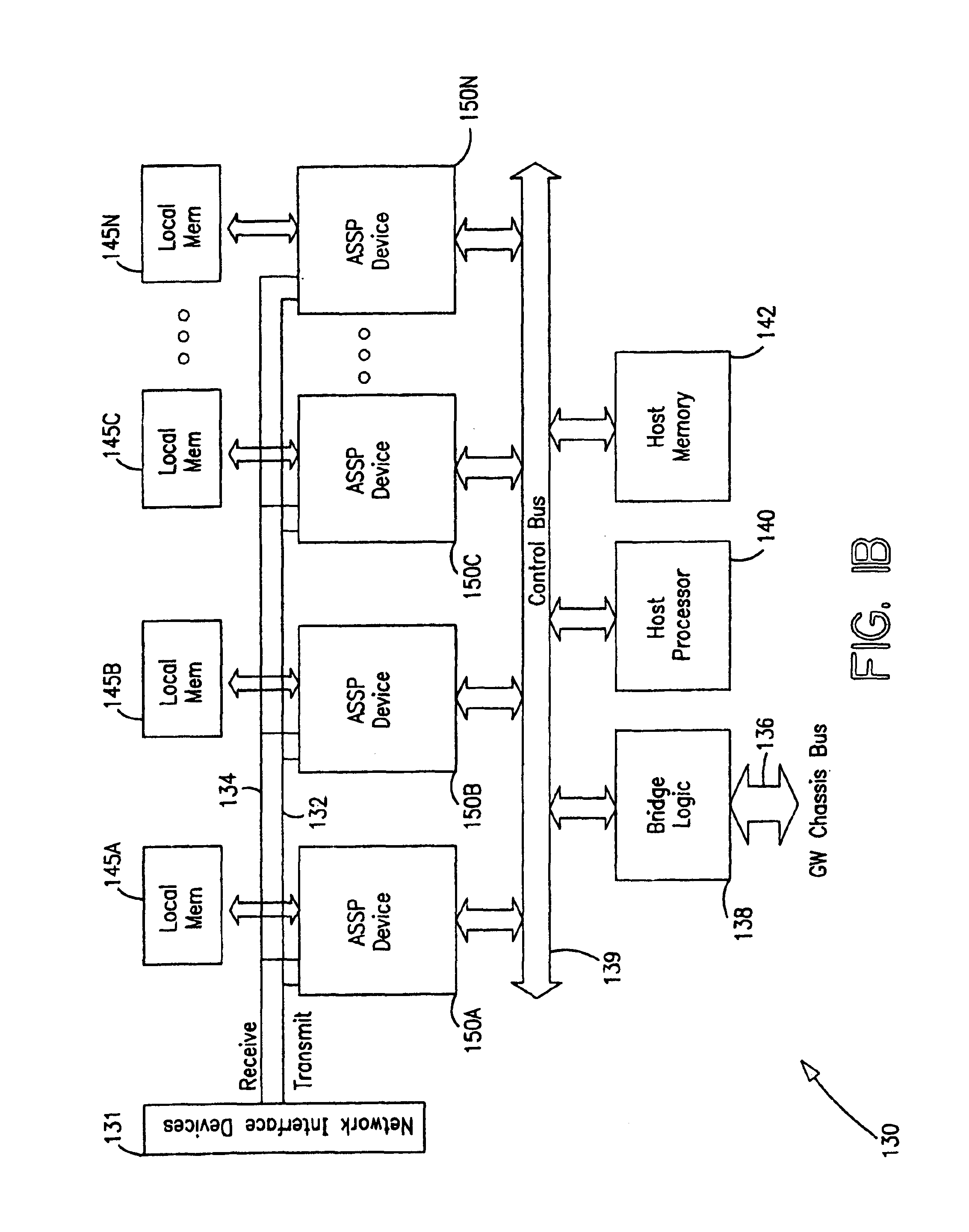

Methods and apparatuses for signal processing

InactiveUS6842845B2Reduce in quantityReduce delaysComputation using non-contact making devicesGeneral purpose stored program computerData compressionDigital signal processing

An application specific signal processor (ASSP) performs vectorized and nonvectorized operations. Nonvectorized operations may be performed using a saturated multiplication and accumulation operation. The ASSP includes a serial interface, a buffer memory, a core processor for performing digital signal processing which includes a reduced instruction set computer (RISC) processor and four signal processing units. The four signal processing units execute the digital signal processing algorithms in parallel including the execution of the saturated multiplication and accumulation operation. The ASSP is utilized in telecommunication interface devices such as a gateway. The ASSP is well suited to handling voice and data compression / decompression in telecommunication systems where a packetized network is used to transceive packetized data and voice.

Owner:INTEL CORP

Method and system for compressing reduced instruction set computer (RISC) executable code through instruction set expansion

A compression scheme is disclosed for program executables that run on Reduced Instruction Set Computer (RISC) processors, such as the PowerPC architecture. The RISC instruction set is expanded by adding opcodes to produce code that facilitates the removal of redundant fields. To compress a program, a compressor engine rewrites the executable using the new expanded instruction set. Next, a filter is applied to remove the redundant fields from the expanded instructions. A conventional compression technique such as Huffman encoding is then applied on the resulting code.

Owner:IBM CORP

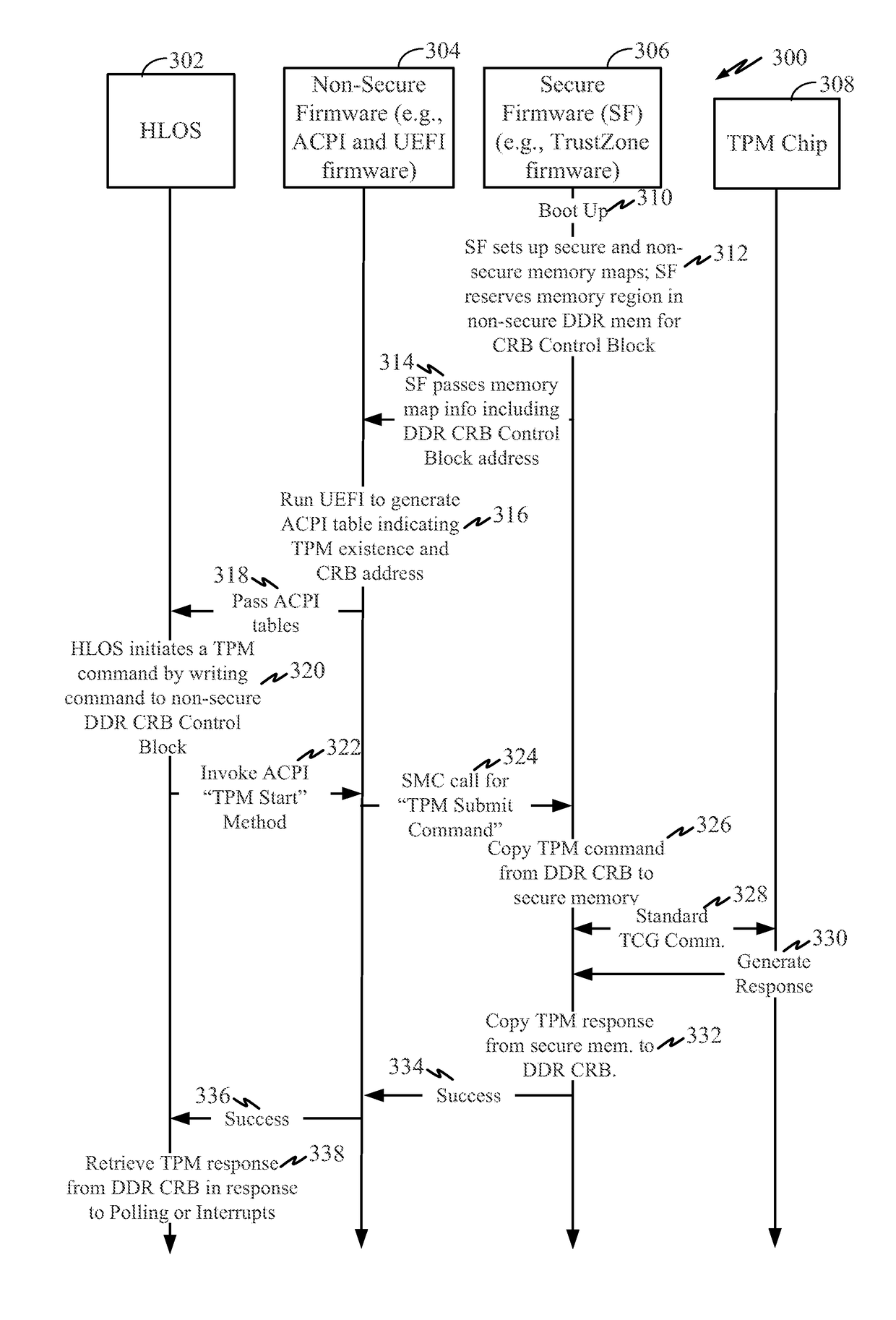

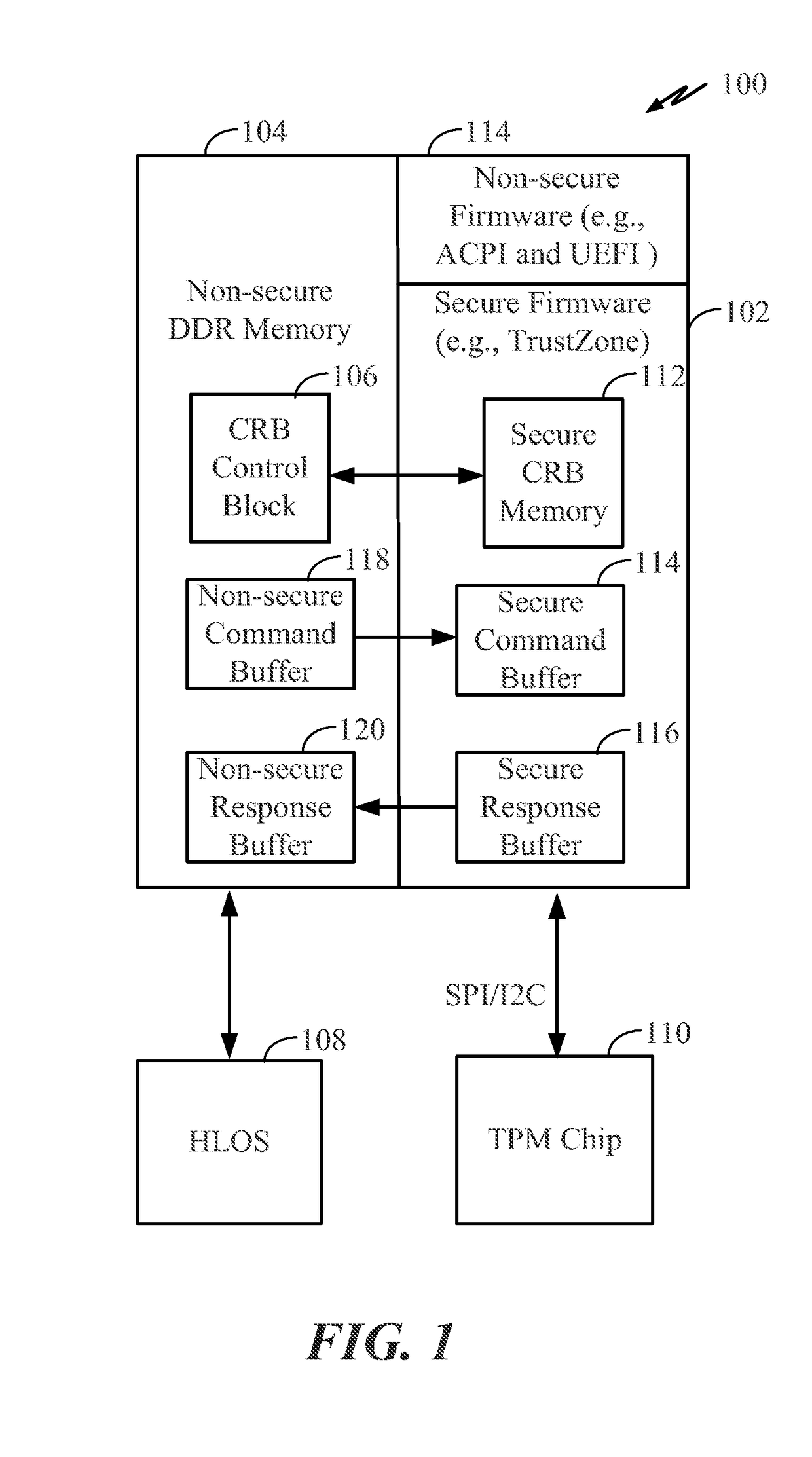

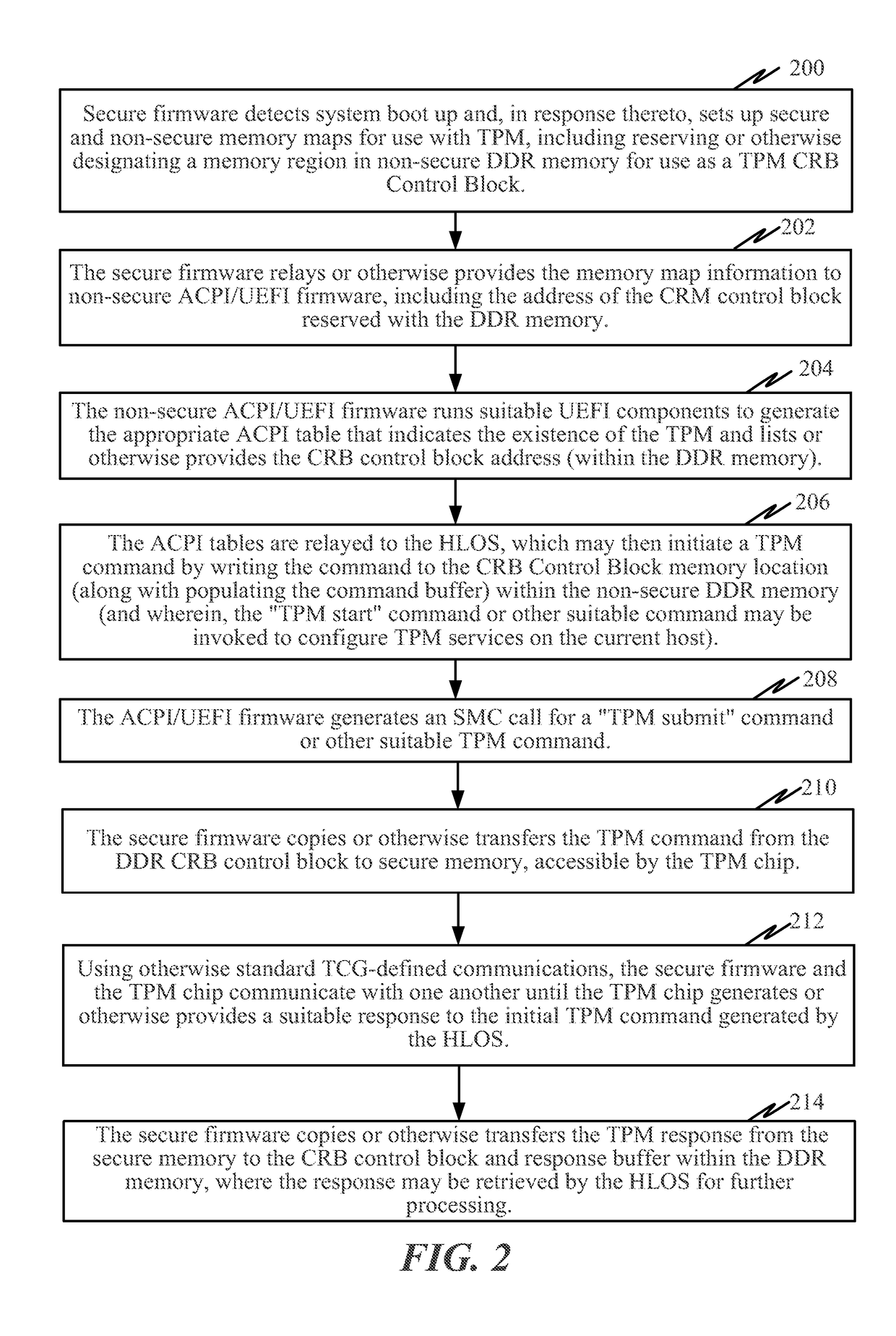

Trusted platform module support on reduced instruction set computing architectures

InactiveUS20180060077A1BootstrappingPlatform integrity maintainanceAdvanced Configuration and Power InterfaceTrusted Platform Module

Exemplary features pertain to providing trusted platform module (TPM) support for ARM®-based systems or other Reduced Instruction Set Computing (RISC) systems. In some examples, secure firmware (e.g., TrustZone firmware) operates as a shim between an unsecure high level operating system (HLOS) and a discrete TPM chip or other trusted execution environment component. The secure firmware reserves a portion of non-secure memory for use as a command response buffer (CRB) control block accessible by the HLOS. The secure firmware translates and relays TPM commands / responses between the HLOS and the TPM via the non-secure CRB memory. The system may also include various non-secure firmware components such as Advanced Configuration and Power Interface (ACPI) and Unified Extensible Firmware Interface (UEFI) components. Among other features, the exemplary system can expose the TPM to the HLOS via otherwise standard UEFI protocols and ACPI tables in a manner that is agnostic to the HLOS.

Owner:QUALCOMM INC

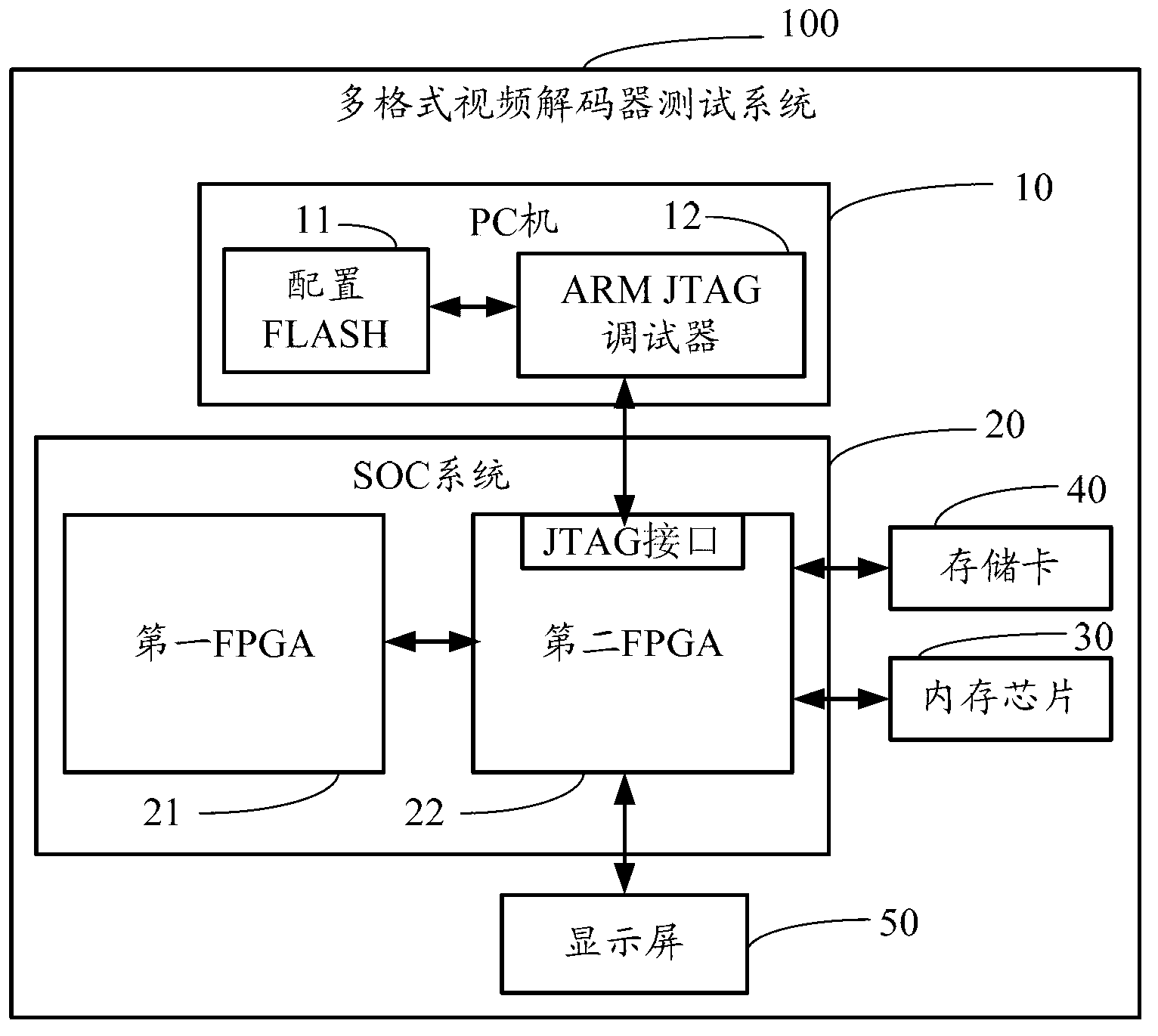

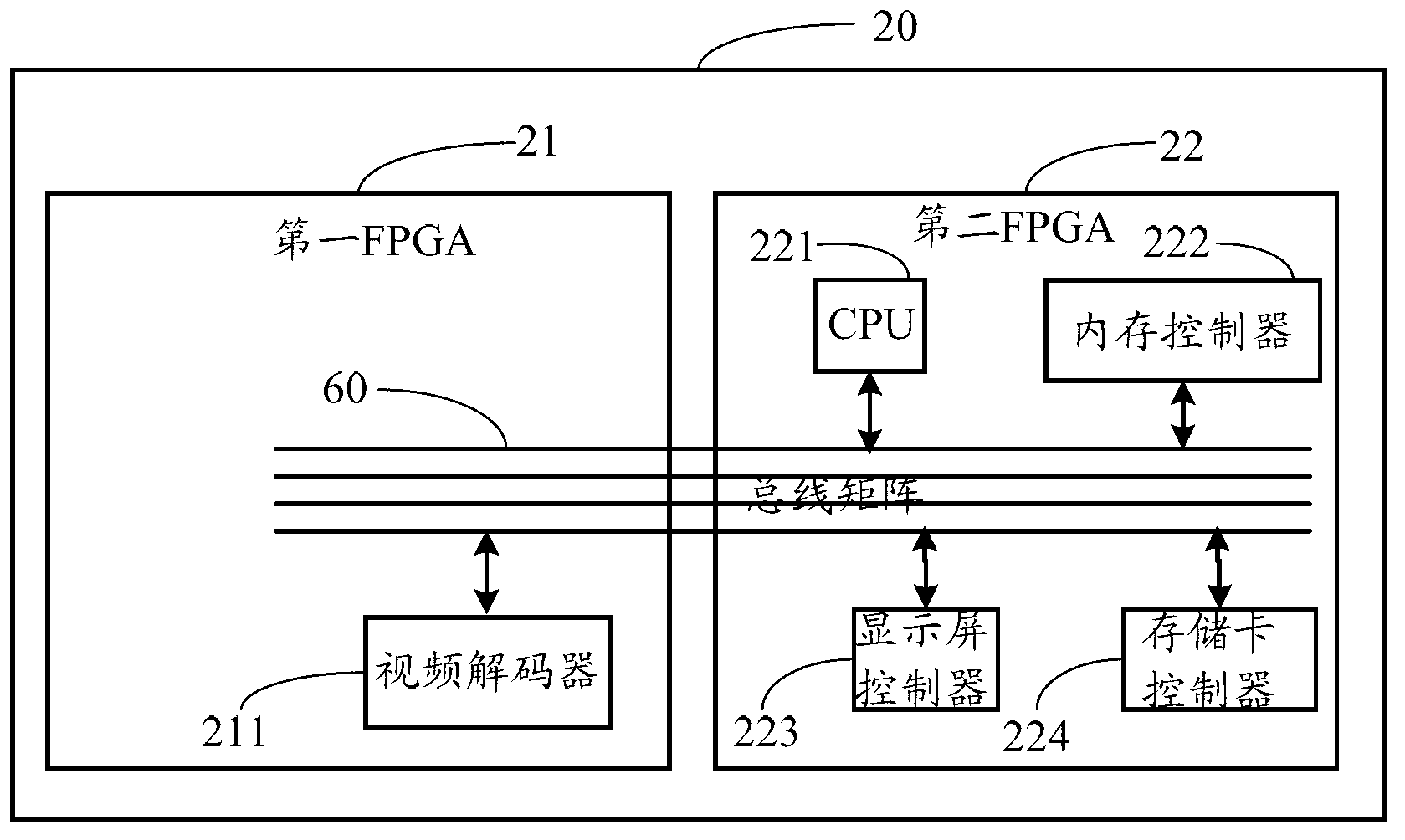

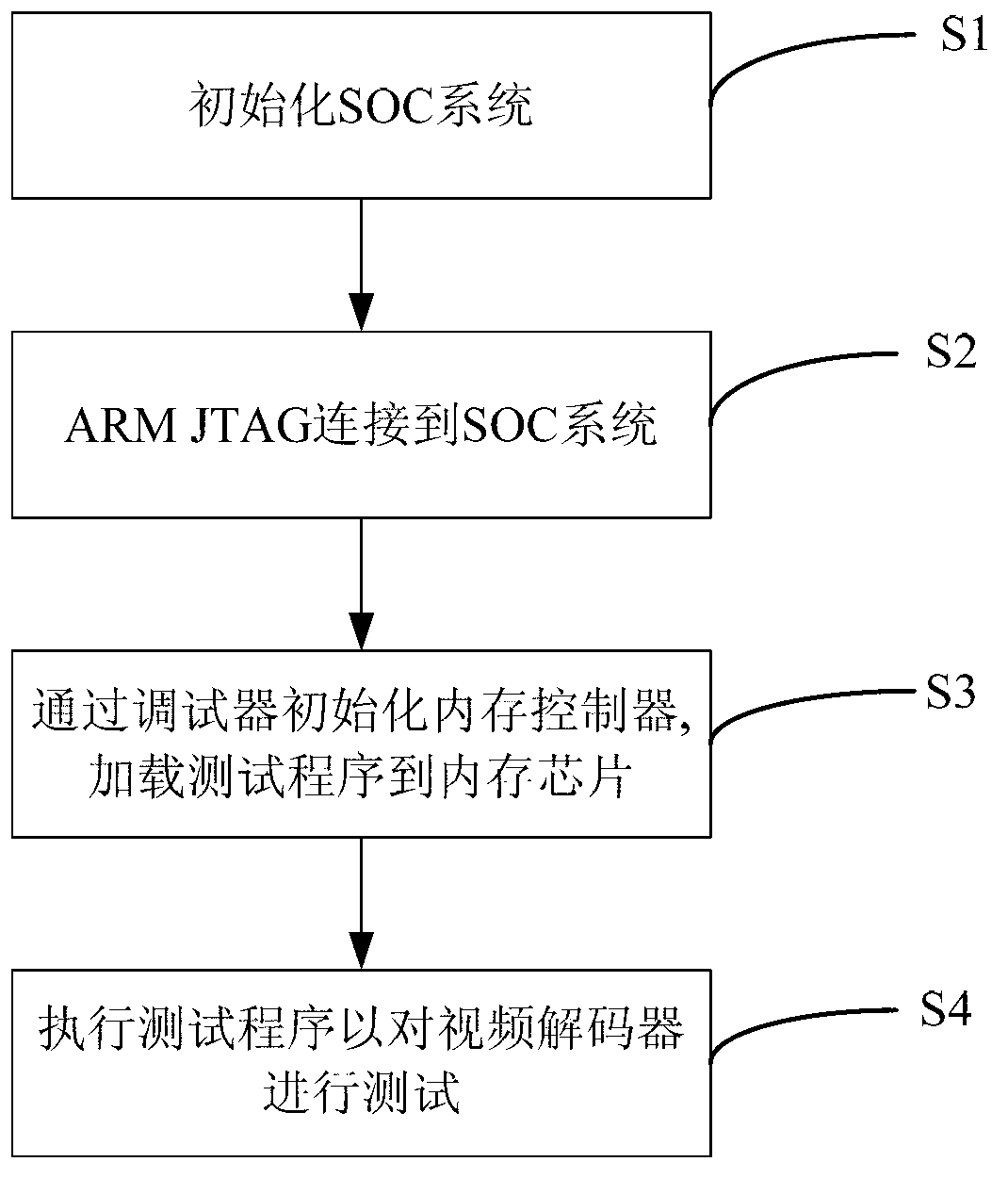

Testing system and testing method of multi-format video decoder

InactiveCN102917242AImplement automatic verificationFast and efficient test verificationTelevision systemsInternal memoryPersonal computer

The invention discloses a testing method of a multi-format video decoder. The testing method comprises the following steps of: reading programmable data from a configuration FLASH by a PFGA (field-programmable gate array), finishing initialization of an SOC (system on chip) system; connecting a PC (personal computer) machine to a JTAG (joint test action group) interface of the SOC system through an ARM (advanced reduced instruction set computing machines) JTGA debugger connection wire; initializing an internal memory controller, loading test program to an internal memory chip from the PC machine, and carrying out a test program to test the video decoder. A testing system of the multi-format video decoder is also disclosed by the invention.

Owner:FUZHOU ROCKCHIP SEMICON

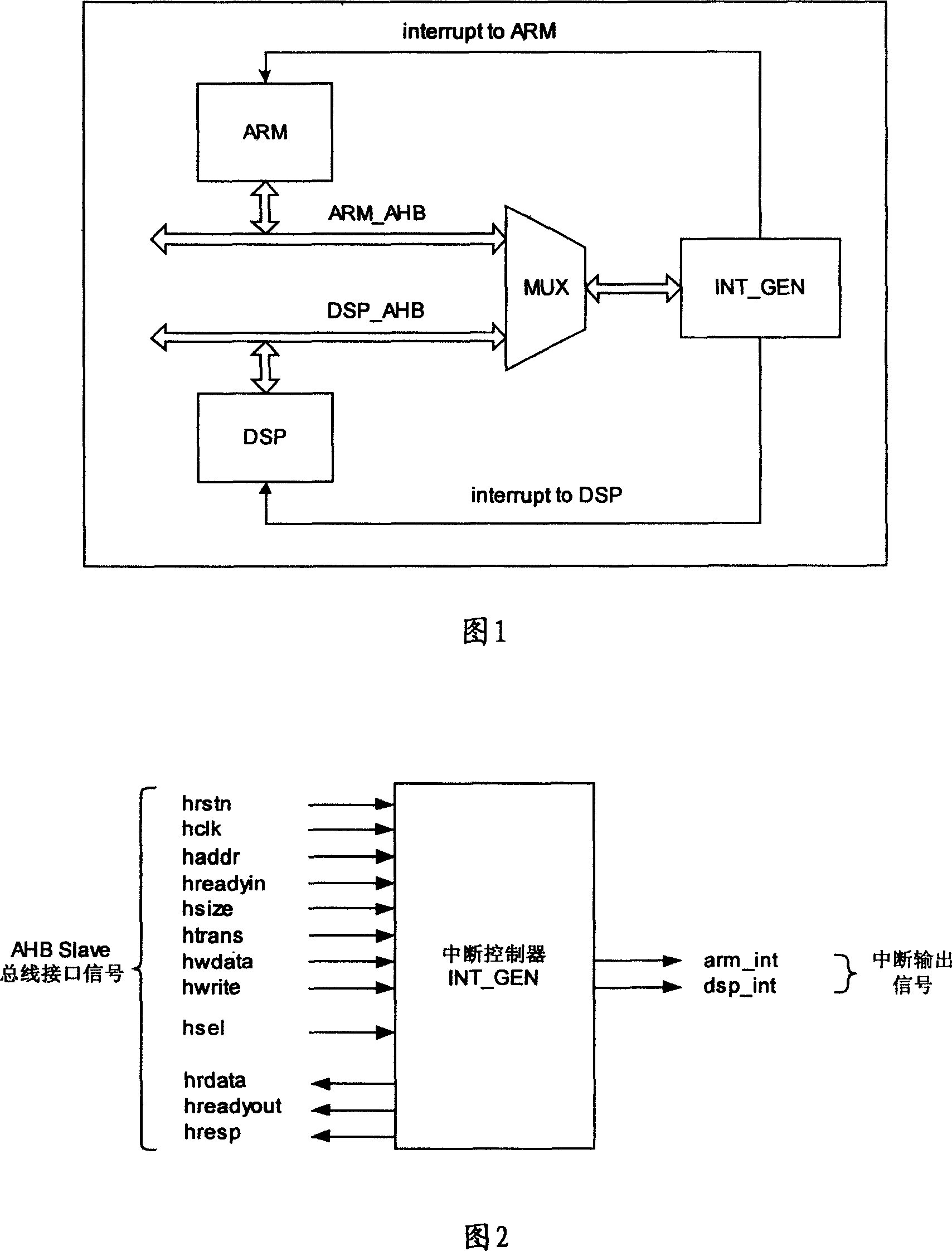

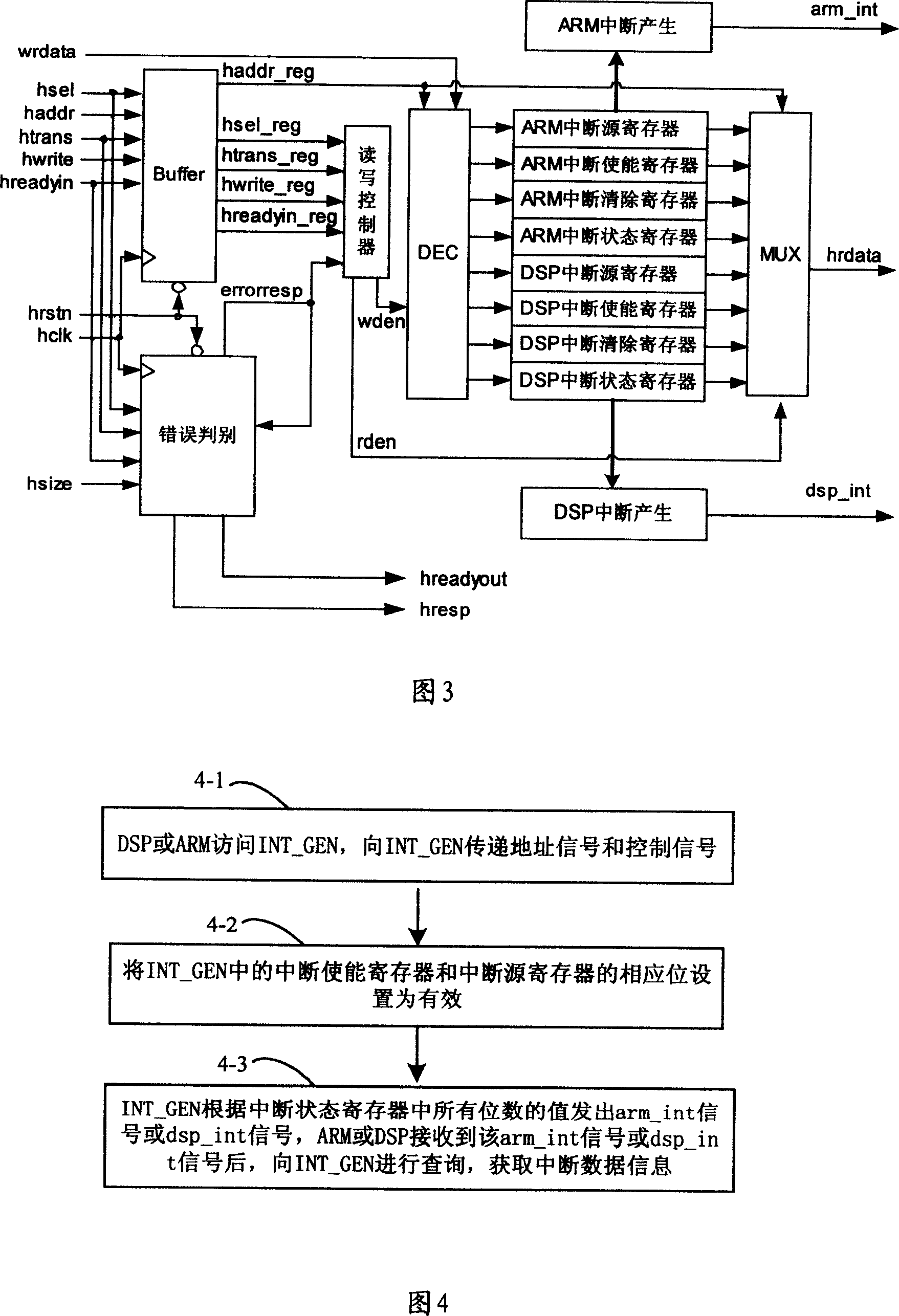

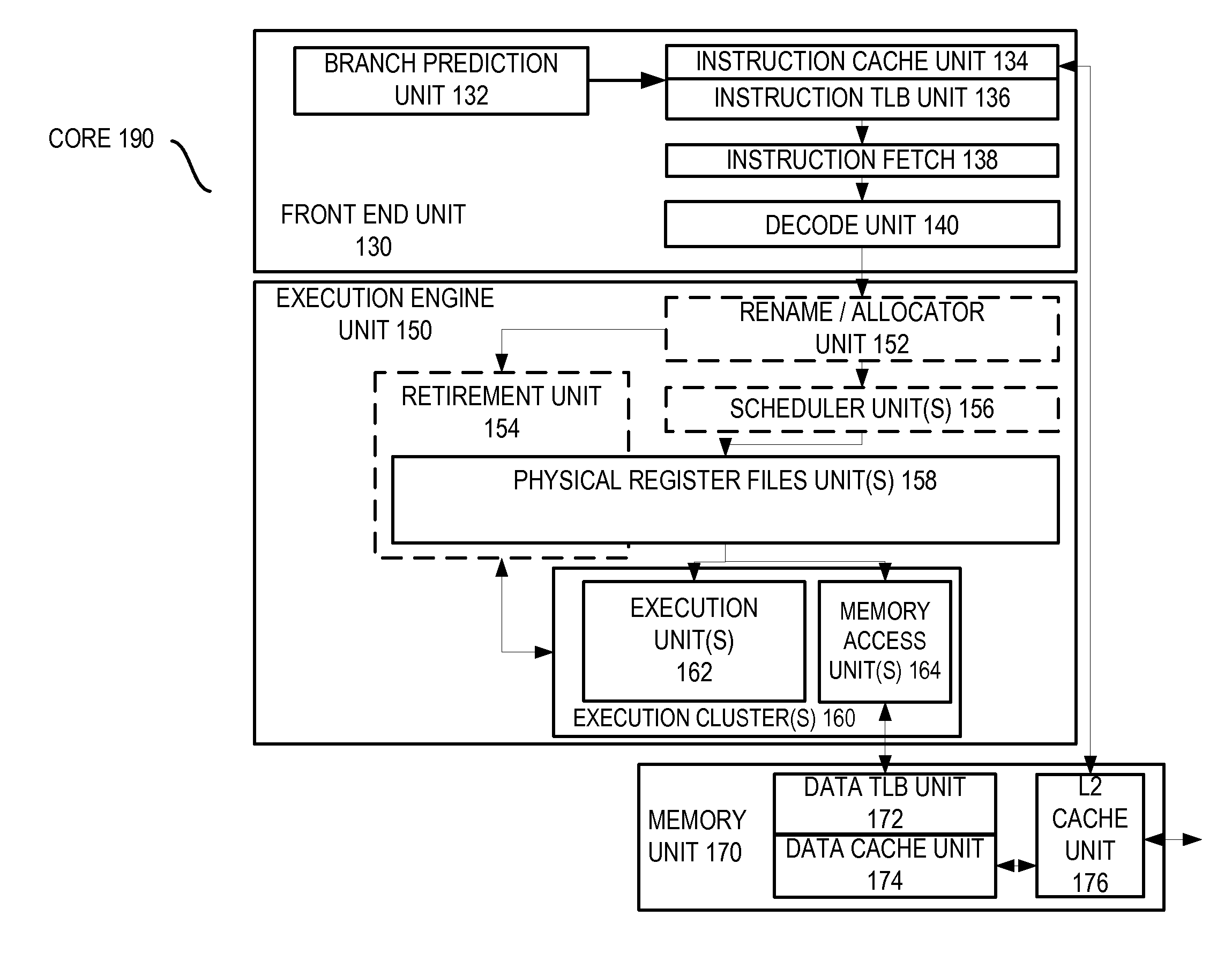

Device and method for implementing communication between processes

ActiveCN101000593AStrong real-timeImprove performanceElectric digital data processingCommunication unitMulti processor

A method for carrying out communication between processors includes setting multiprocessor communication unit in multiprocessor system, calling said multiprocessor communication unit by each processor through control bus in order to carry out communication between processors through said multiprocessor communication unit. The device used for realizing said method is also disclosed.

Owner:HUAWEI TECH CO LTD

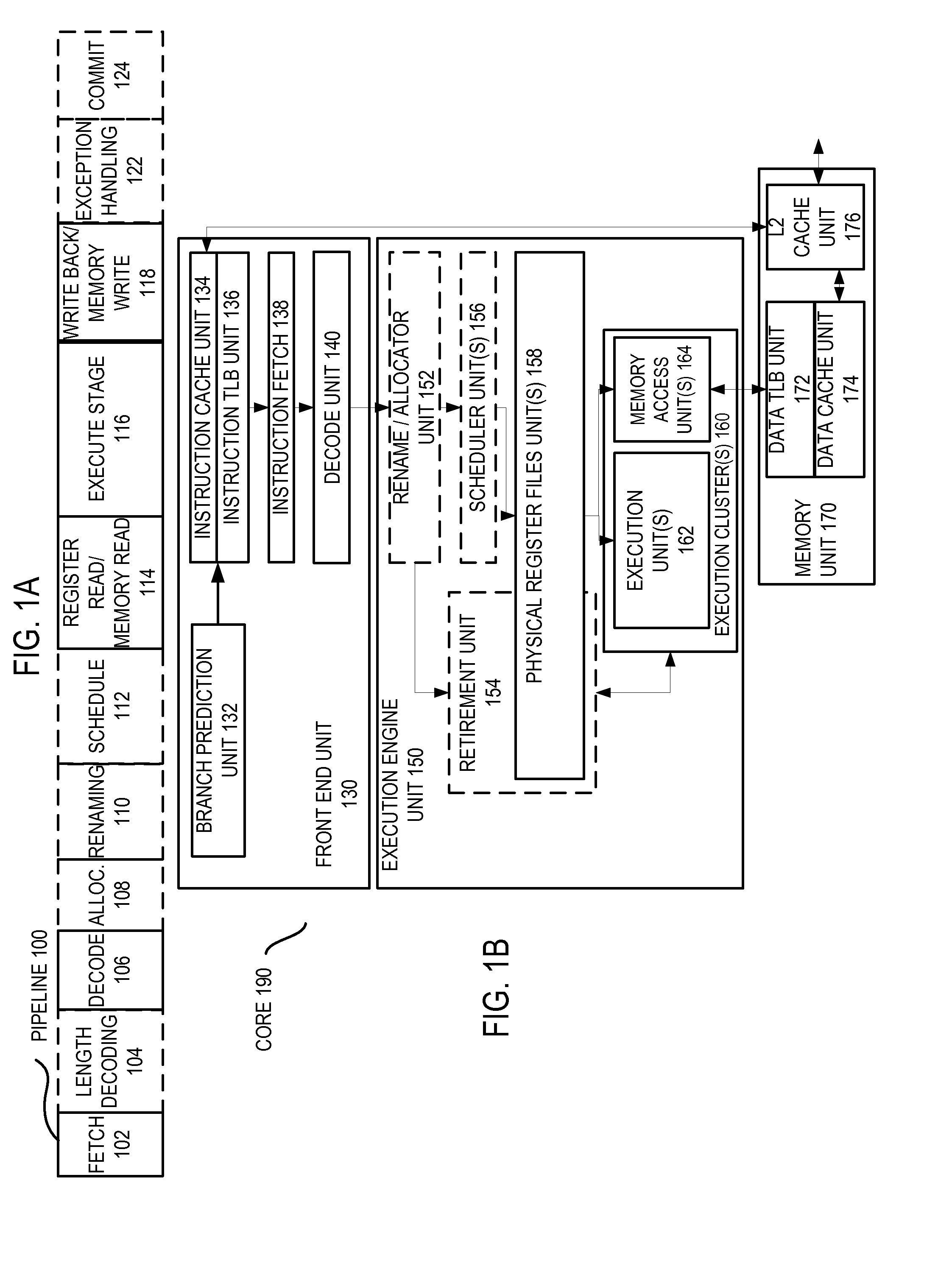

Method and apparatus for implementing a dynamic out-of-order processor pipeline

A hardware / software co-design for an optimized dynamic out-of-order Very Long Instruction Word (VLIW) pipeline. For example, one embodiment of an apparatus comprises: an instruction fetch unit to fetch Very Long Instruction Words (VLIWs) in their program order from memory, each of the VLIWs comprising a plurality of reduced instruction set computing (RISC) instruction syllables grouped into the VLIWs in an order which removes data-flow dependencies and false output dependencies between the syllables; a decode unit to decode the VLIWs in their program order and output the syllables of each decoded VLIW in parallel; and an out-of-order execution engine to execute the syllables preferably in parallel with other syllables, wherein at least some of the syllables are to be executed in a different order than the order in which they are received from the decode unit, the out-of-order execution engine having one or more processing stages which do not check for data-flow dependencies and false output dependencies between the syllables when performing operations.

Owner:INTEL CORP

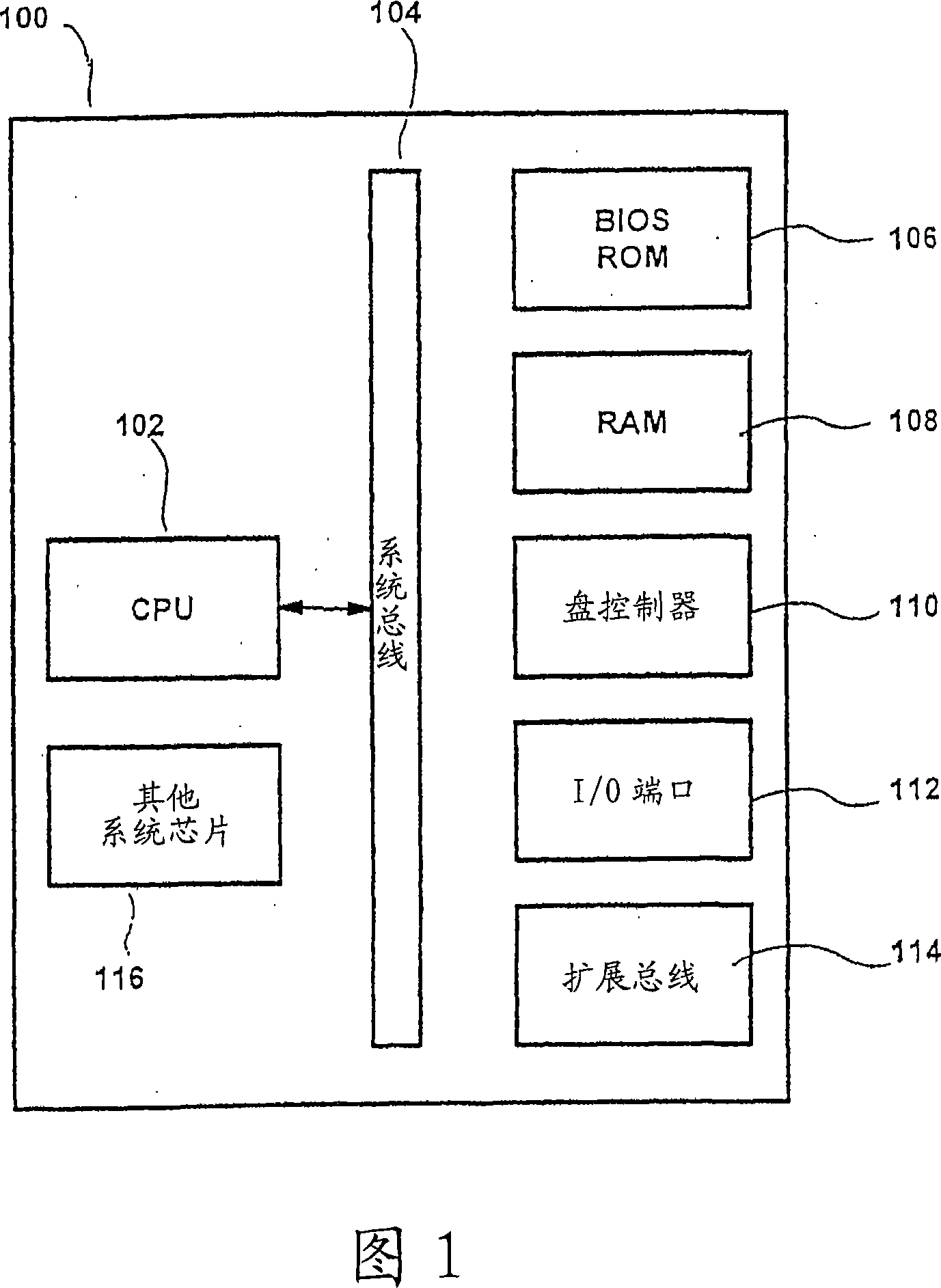

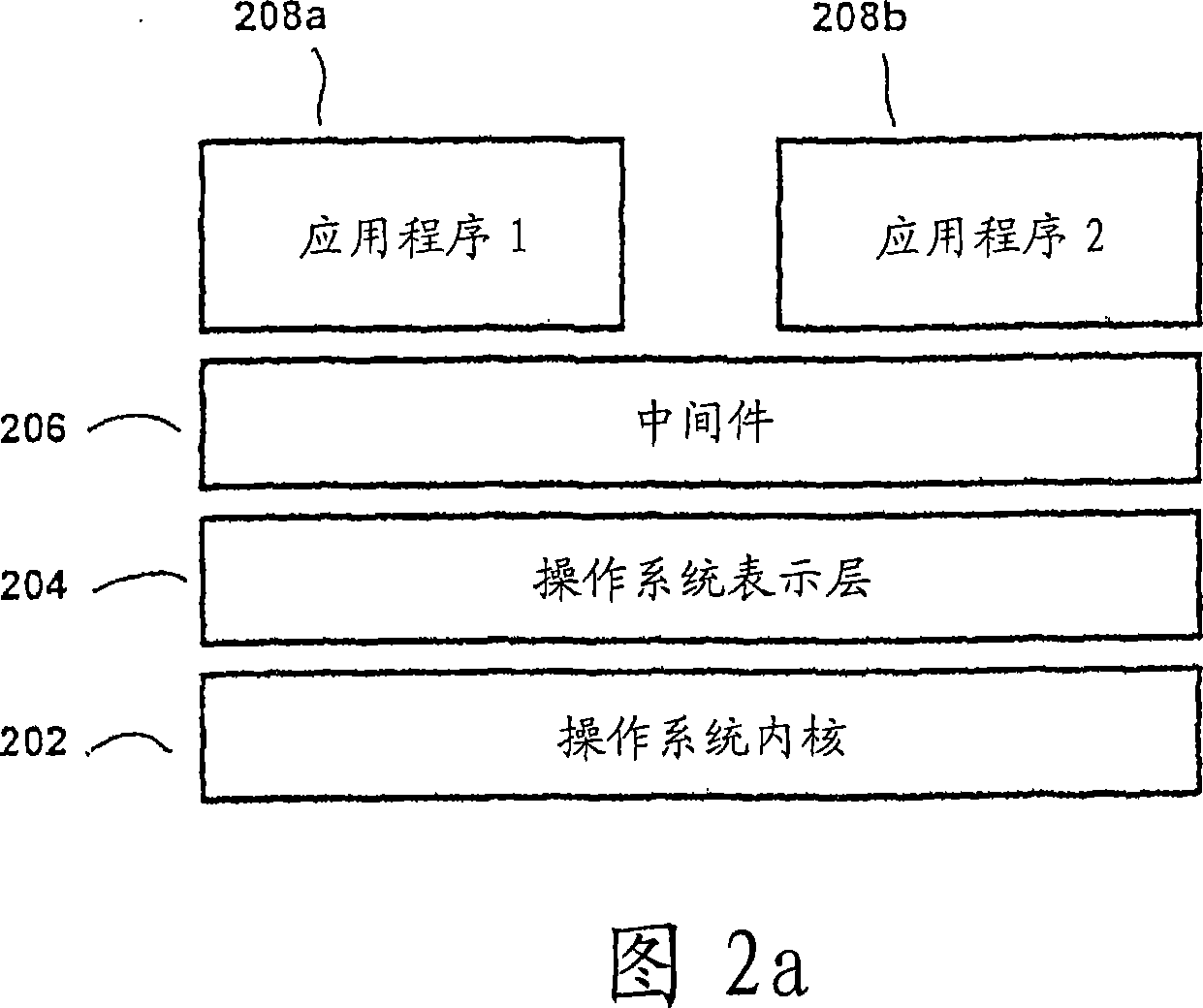

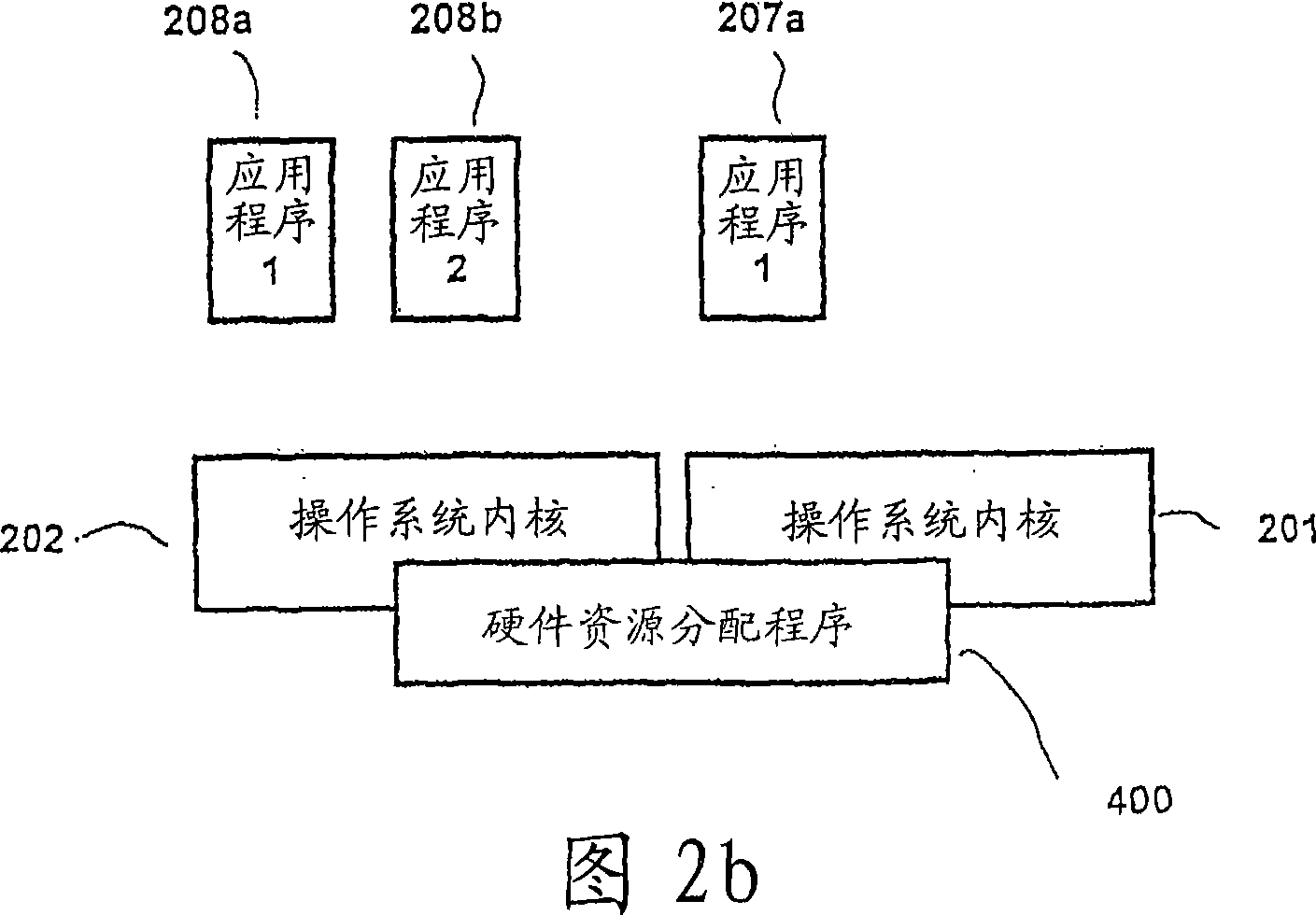

Operating systems

InactiveCN101052949AMemory architecture accessing/allocationProgram control using stored programsGeneral purposeOperational system

A method of enabling multiple different operating systems to run concurrently on the same RISC (e.g. ARM) computer, comprising selecting a first operating system to have a relatively high priority (the realtime operating system, such as C5); selecting at least one secondary operating system to have a relatively lower priority (the general purpose operating system, such as Linux); providing a common program (a hardware resource dispatcher similar to a nanokernel) arranged to switch between said operating systems under predetermined conditions; and providing modifications to said first and second operating systems to allow them to be controlled by said common program.

Owner:JALUNA

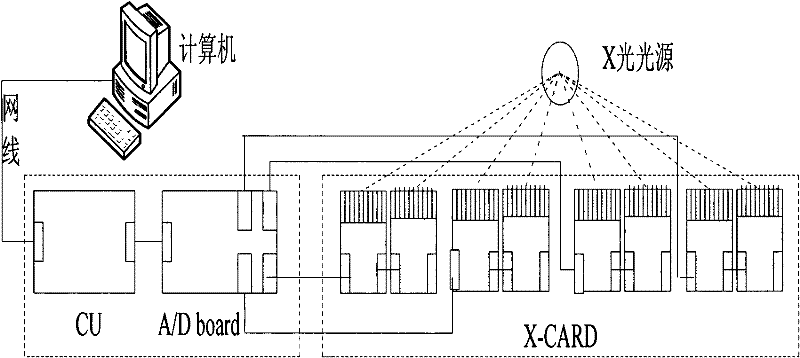

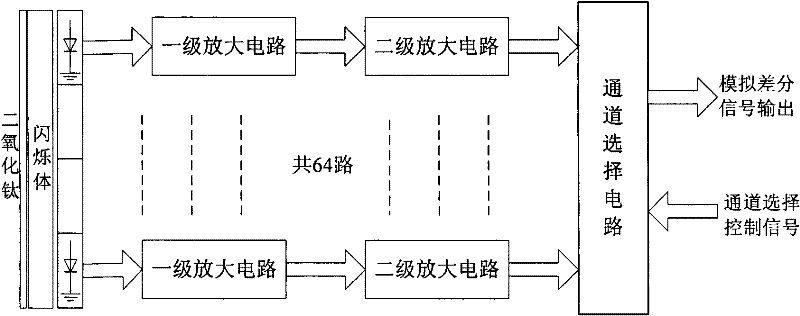

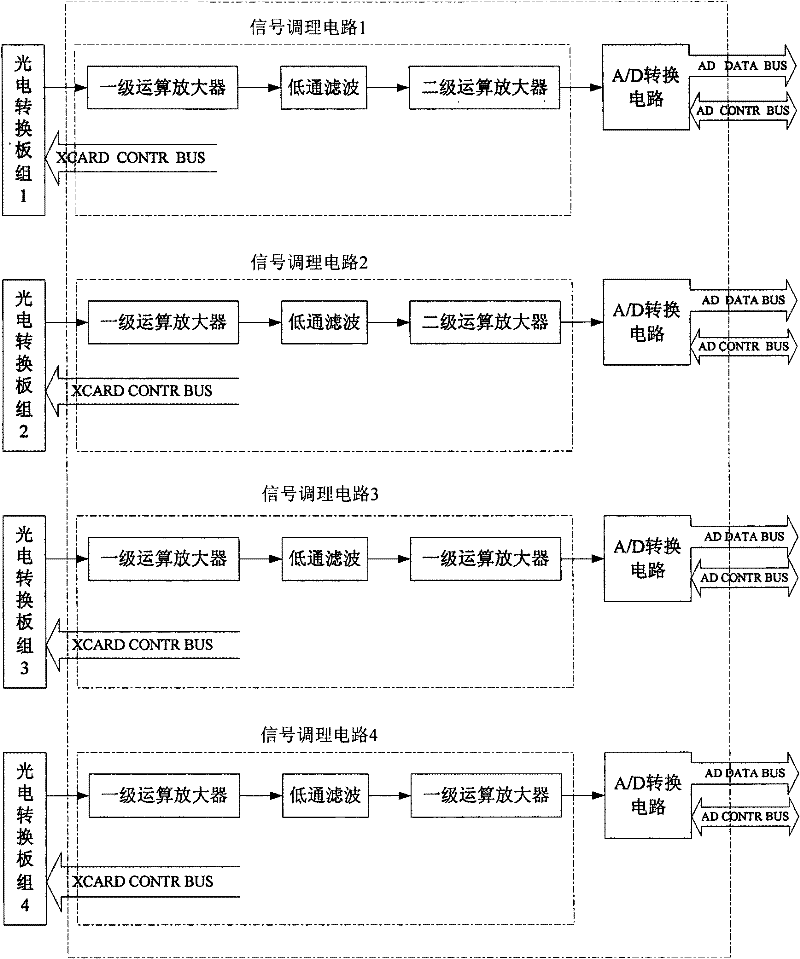

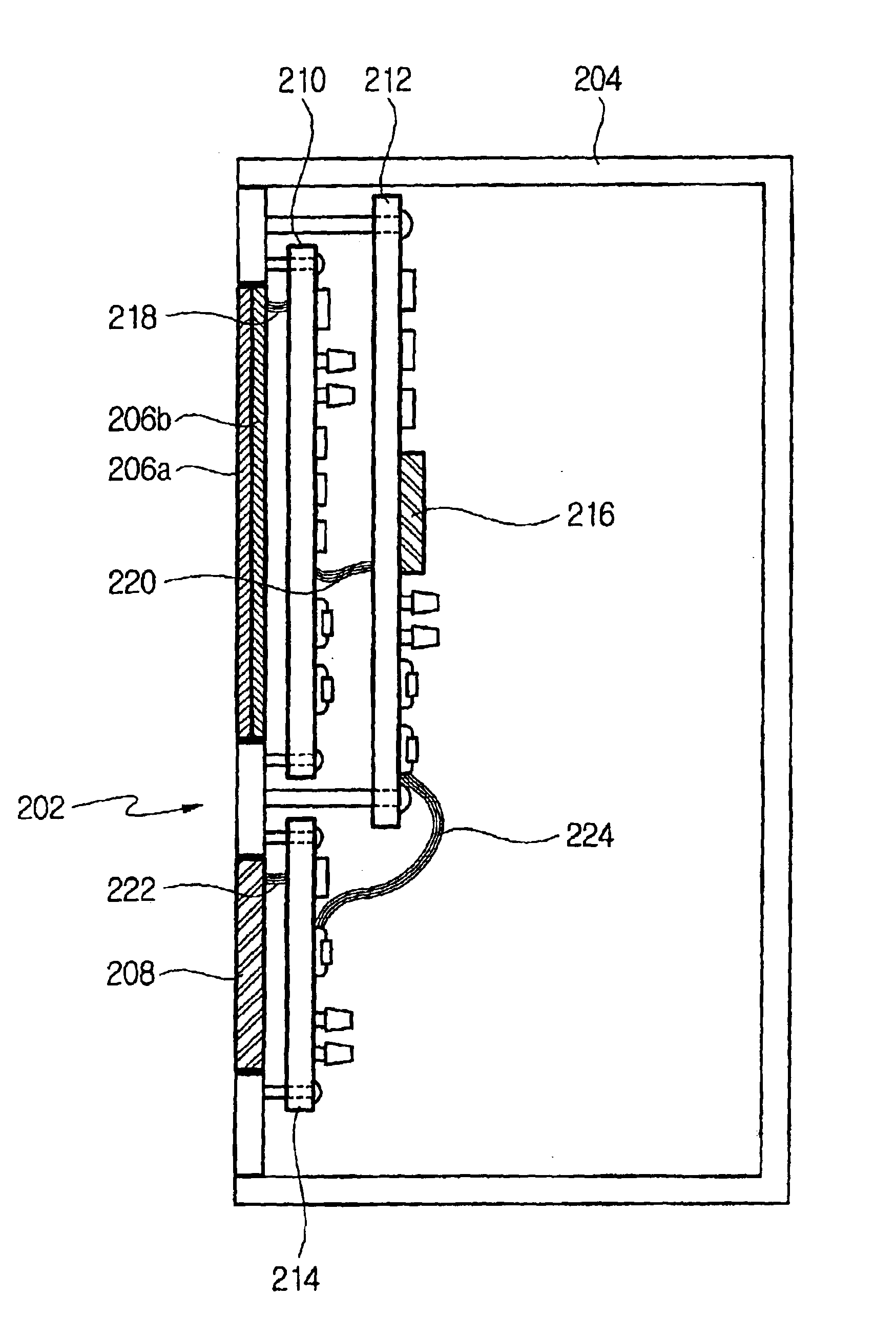

X-ray on-line detection probe of steel wire rope core conveyor belt and signal acquisition and processing method

InactiveCN102253063AImprove scalabilityHigh acquisition rateMaterial analysis by transmitting radiationCorrection algorithmX-ray

The invention relates to an X-ray on-line detection probe of a steel wire rope core conveyor belt and a signal acquisition and processing method. The X-ray on-line detection probe of the steel wire rope core conveyor belt belongs to the field of non-destructive X-ray on-line probing equipment. Hardware design of the X-ray on-line detection probe of the steel wire rope core conveyor belt is as follows: a photoelectric conversion module is used for realizing conversion from X-ray signals to electrical signals; four lines of A / D (analog / digital) modules are used for realizing sampling from analog signals to digital signals; and a signal acquisition and processing module in the structure of an ARM (advanced RICS (reduced instruction set computing) machine and an FPGA (field programmable gate array) is used for realizing the control of the A / D modules and the processing of image element data. The signal acquisition and processing method comprises the following steps: using the FPGA to adopt a state machine to realize the sampling control of the four lines of the A / D modules; adopting a three-point sectional image element non-homogenization correction algorithm based on a response model to realize homogenization processing of the image element data in the FPGA; and figuring out a coefficient of the correction algorithm through the ARM and performing median filtering processing on the image element data after completing the correction. By adopting the probe in the invention, the high-precision dynamic real-time detection of the conveyor belt can be realized, thereby facilitating diagnosis of elongation, rust, fracture and other situations of a joint of a steel rope core.

Owner:TIANJIN POLYTECHNIC UNIV +1

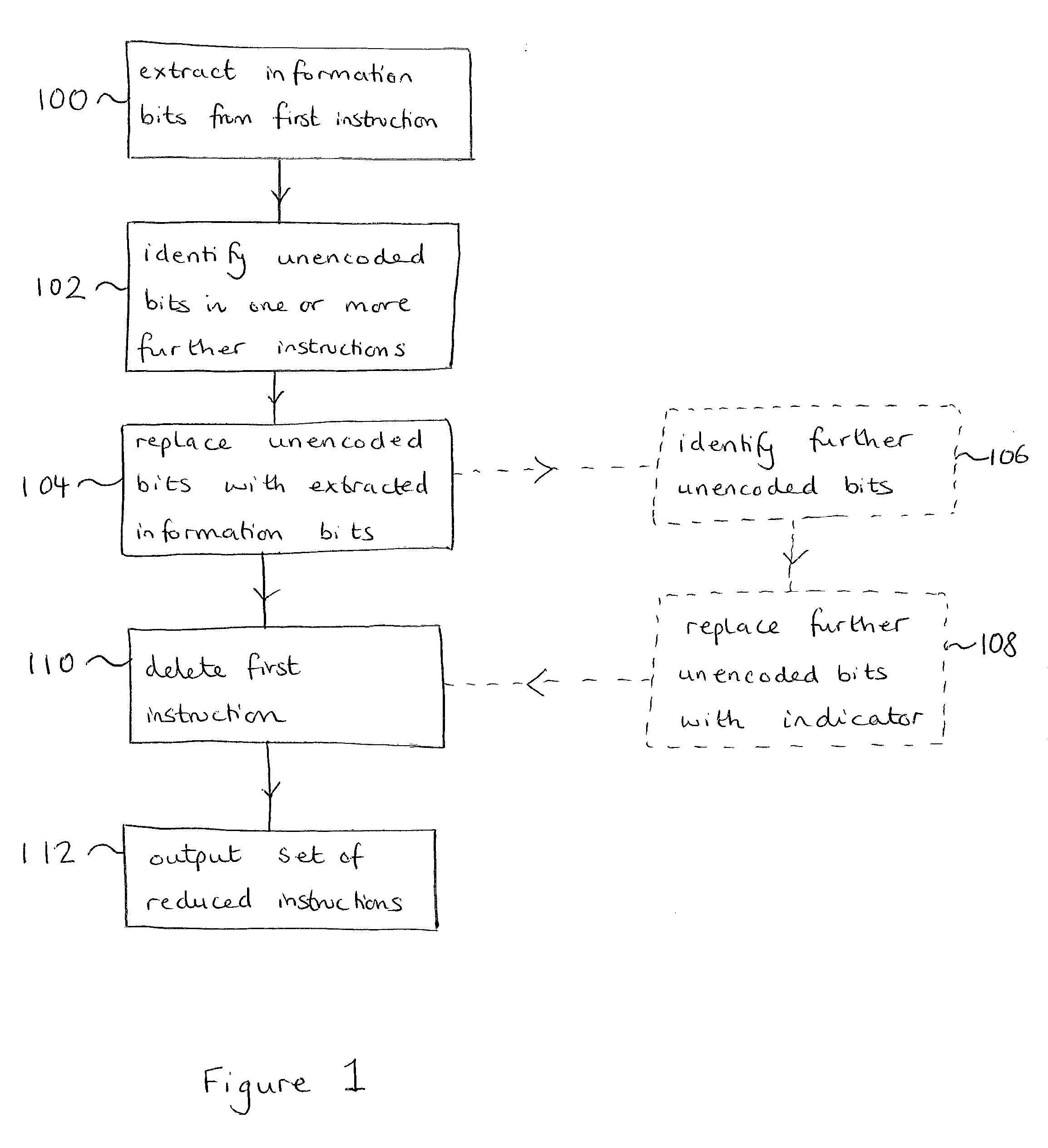

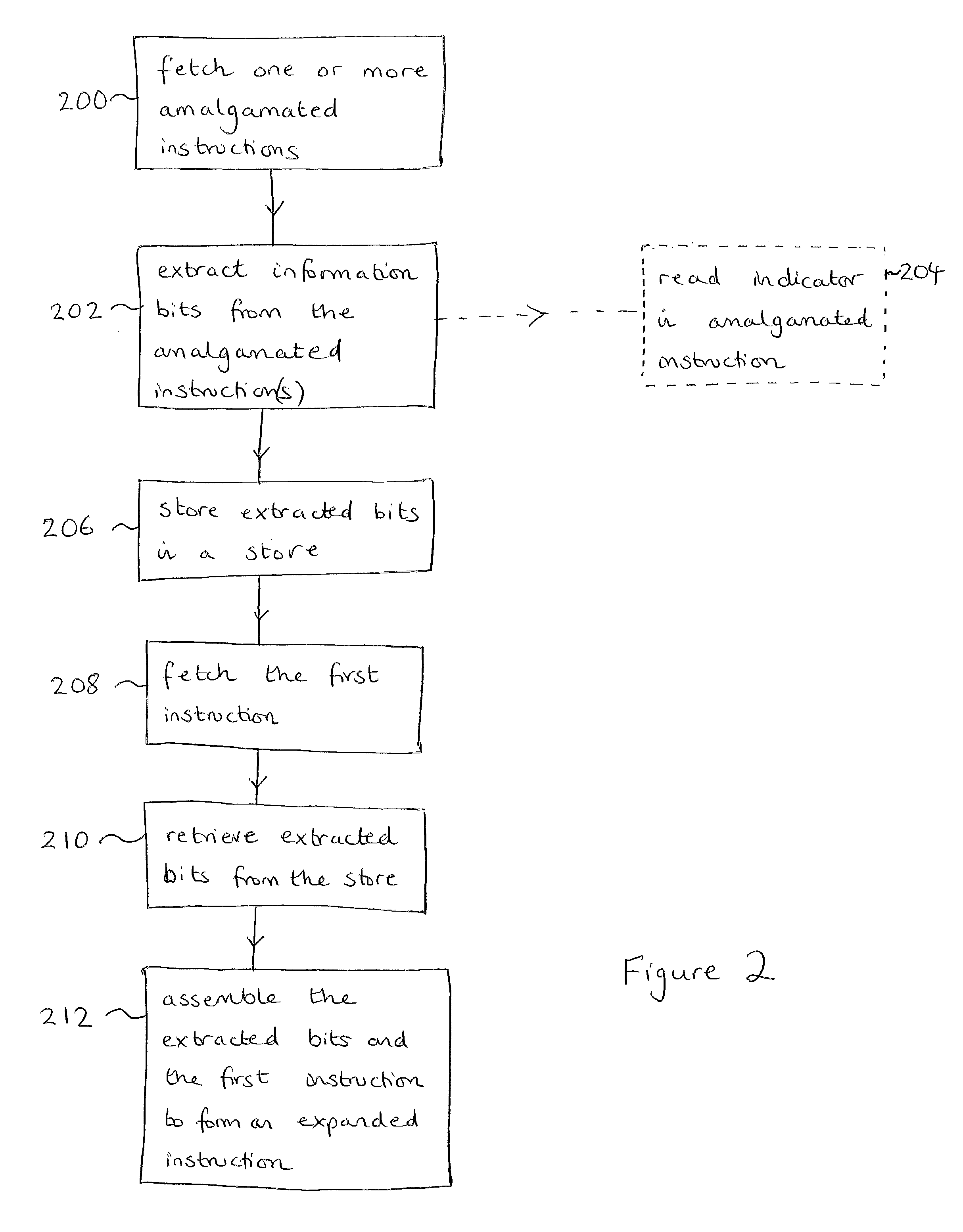

Reduced Instruction Set

InactiveUS20120331273A1Reduce settingsRuntime instruction translationDigital computer detailsInstruction setReduced instruction set computing

Owner:QUALCOMM TECH INT

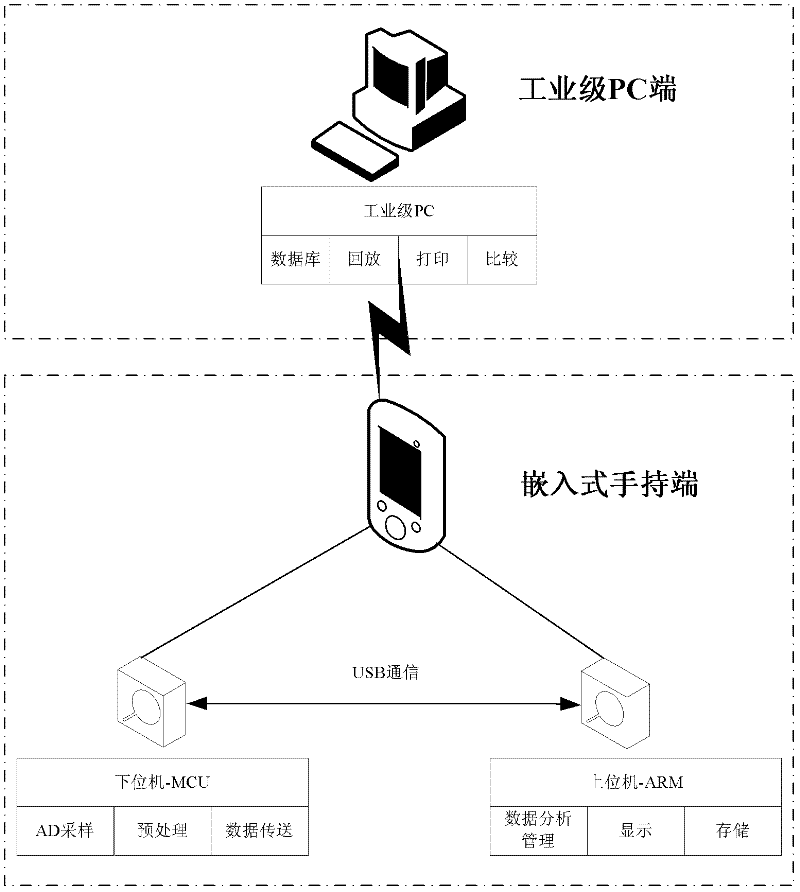

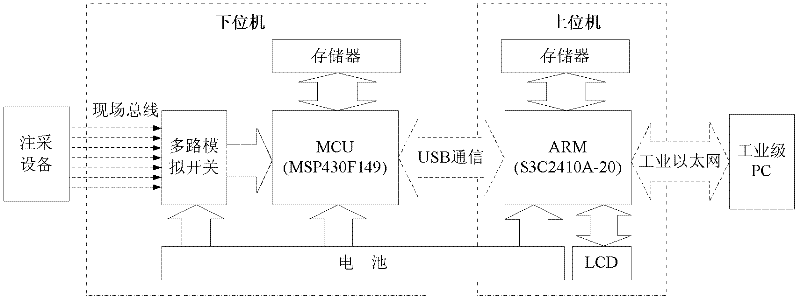

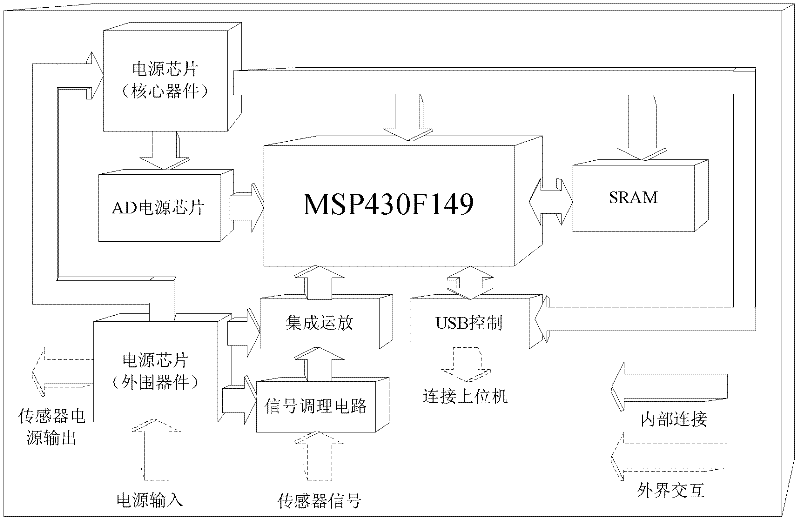

Handheld type condition monitoring and fault diagnosing system orienting to oil field injection-production equipment

InactiveCN102536203AReduce power consumptionReduce volumeConstructionsData analysis systemTrend prediction

The invention provides a handheld type condition monitoring and fault diagnosing system orienting to oil field injection-production equipment. The system comprises an embedded handheld end and an industrial-grade PC (Personal Computer) end, wherein the embedded handheld end is of a dual embedded processor structure of an upper computer and a lower computer and is composed of a lower computer real-time data acquisition system and an upper computer data processing analysis system, the lower computer real-time data acquisition system is a data acquisition card based on a mixed signal processing micro control unit, and the upper computer data processing analysis system is a condition monitoring card based on an advanced reduced instruction set computing machine; and the industrial-grade PC end is a depth data analysis system which is positioned in a control room of an oil field oil production plant, and is used for finishing off-line analysis tasks including related analysis, comparative analysis, trend prediction of equipment performance and generation and actuation of expert knowledge. The handheld type condition monitoring and fault diagnosing system orienting to the oil field injection-production equipment provided by the invention has the advantages of good flexibility, low requirement for working environment, wide application range, simple structure, simplicity and convenience in operation and lower cost.

Owner:ZHEJIANG UNIV OF TECH

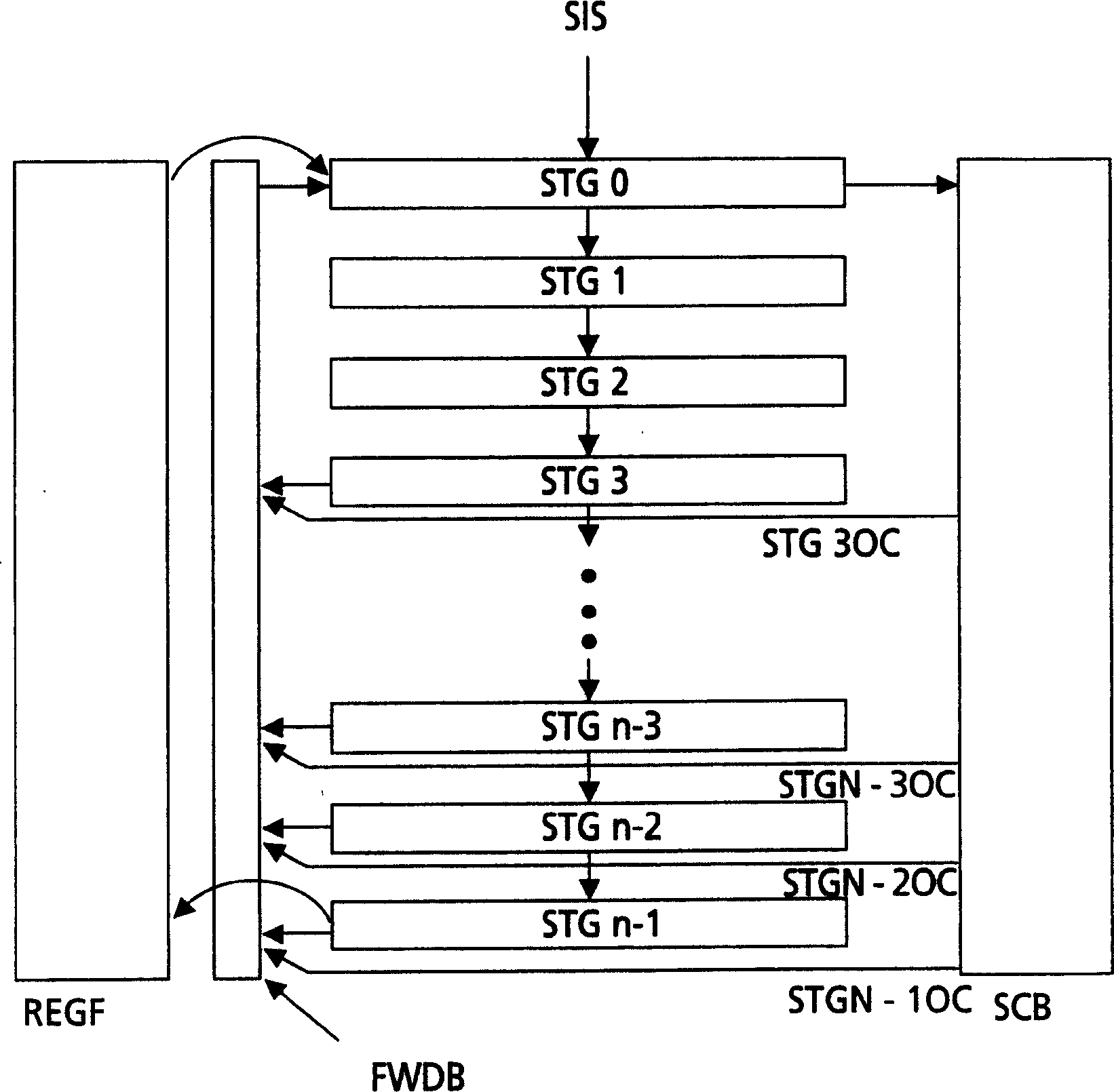

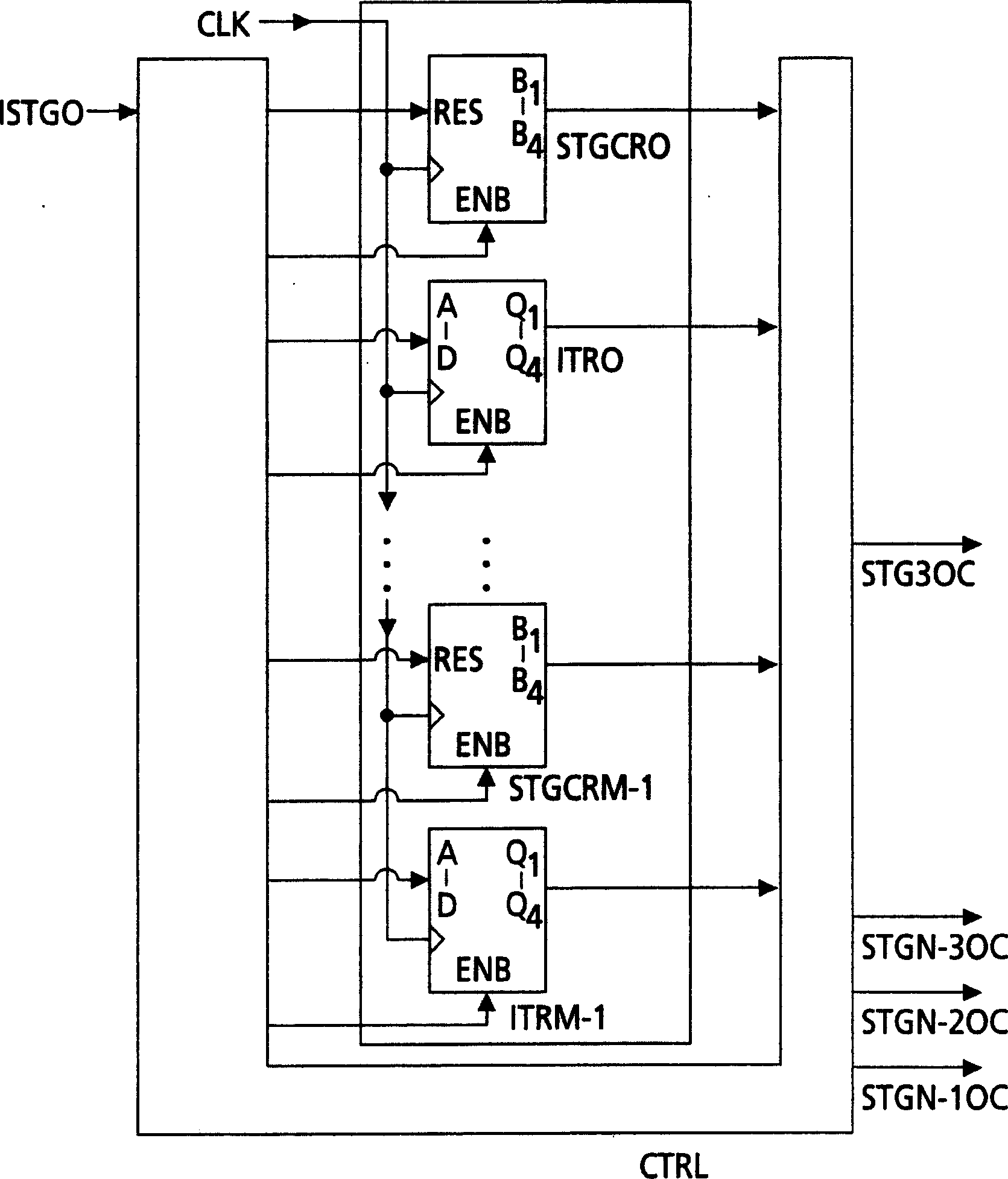

Method and equipment of pipeline treating series treatment command

InactiveCN1534462AProcessing speedImprove fault detection efficiencyConcurrent instruction executionMemory systemsSoftware engineeringOperand

Owner:THOMSON LICENSING SA

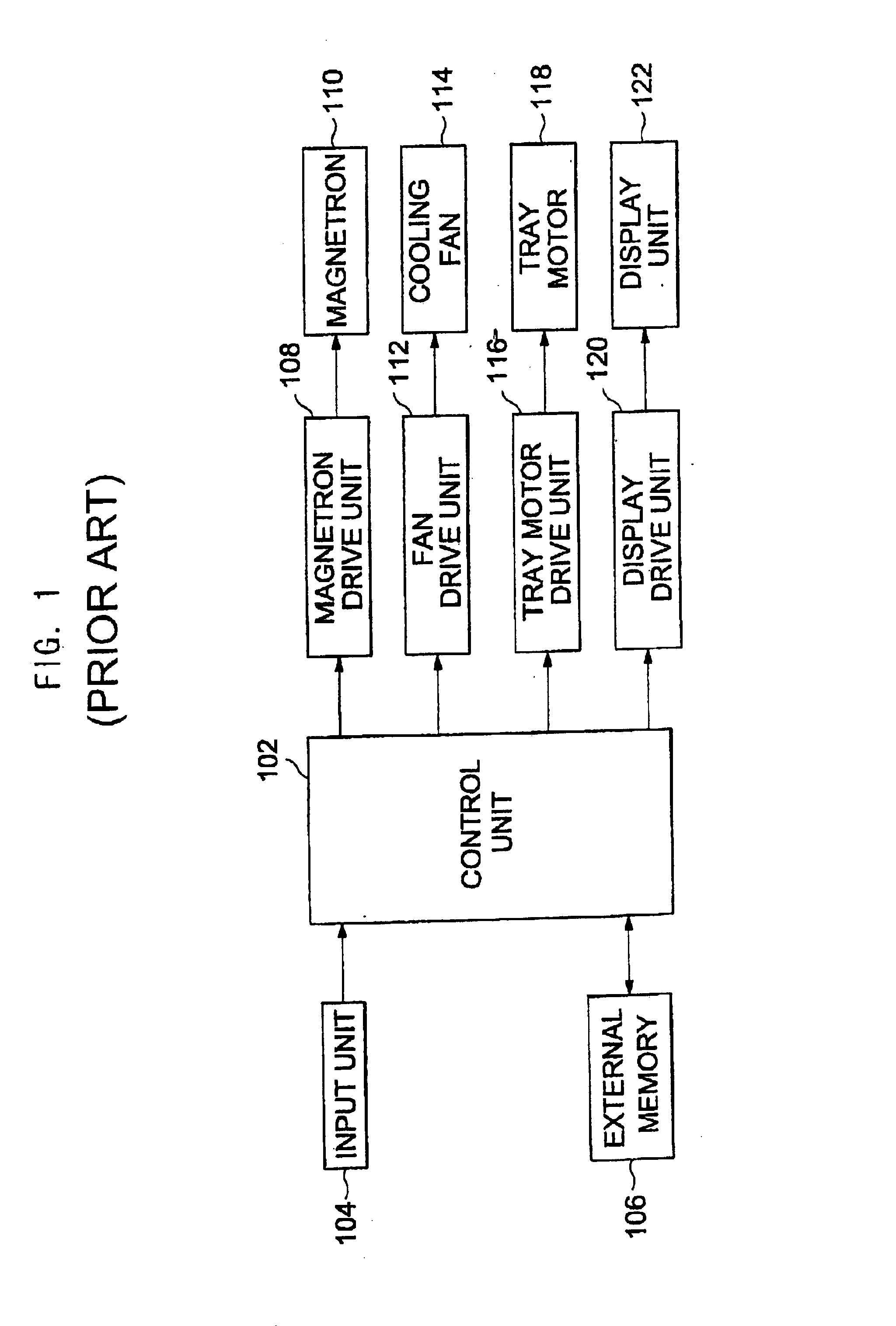

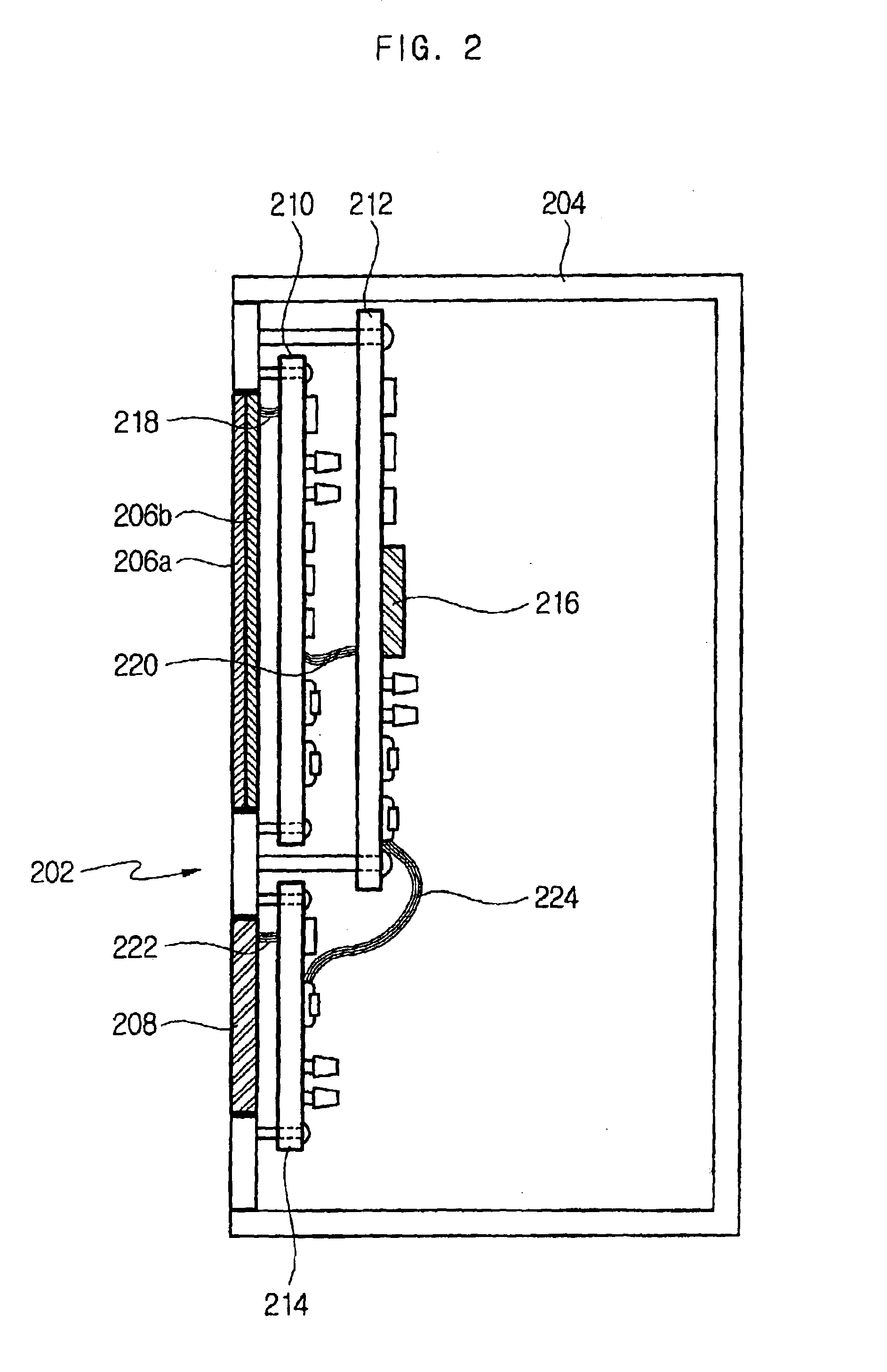

Microwave oven and control unit thereof

InactiveUS6900423B2Small sizeImprove developmentDomestic stoves or rangesLighting and heating apparatusMicrowave ovenMembrane switch

A microwave oven includes a widely applicable and extensible Reduced Instruction Set Computer (RISC) microprocessor, allowing a control panel to be easily included, and which controls various functions using a single microprocessor, reducing a size of the control panel. The microwave oven also includes a control panel in which soft touch switches using electrostatic capacity are substituted for membrane switches, allowing the control panel to be formed in various forms including a curved form.

Owner:SAMSUNG ELECTRONICS CO LTD

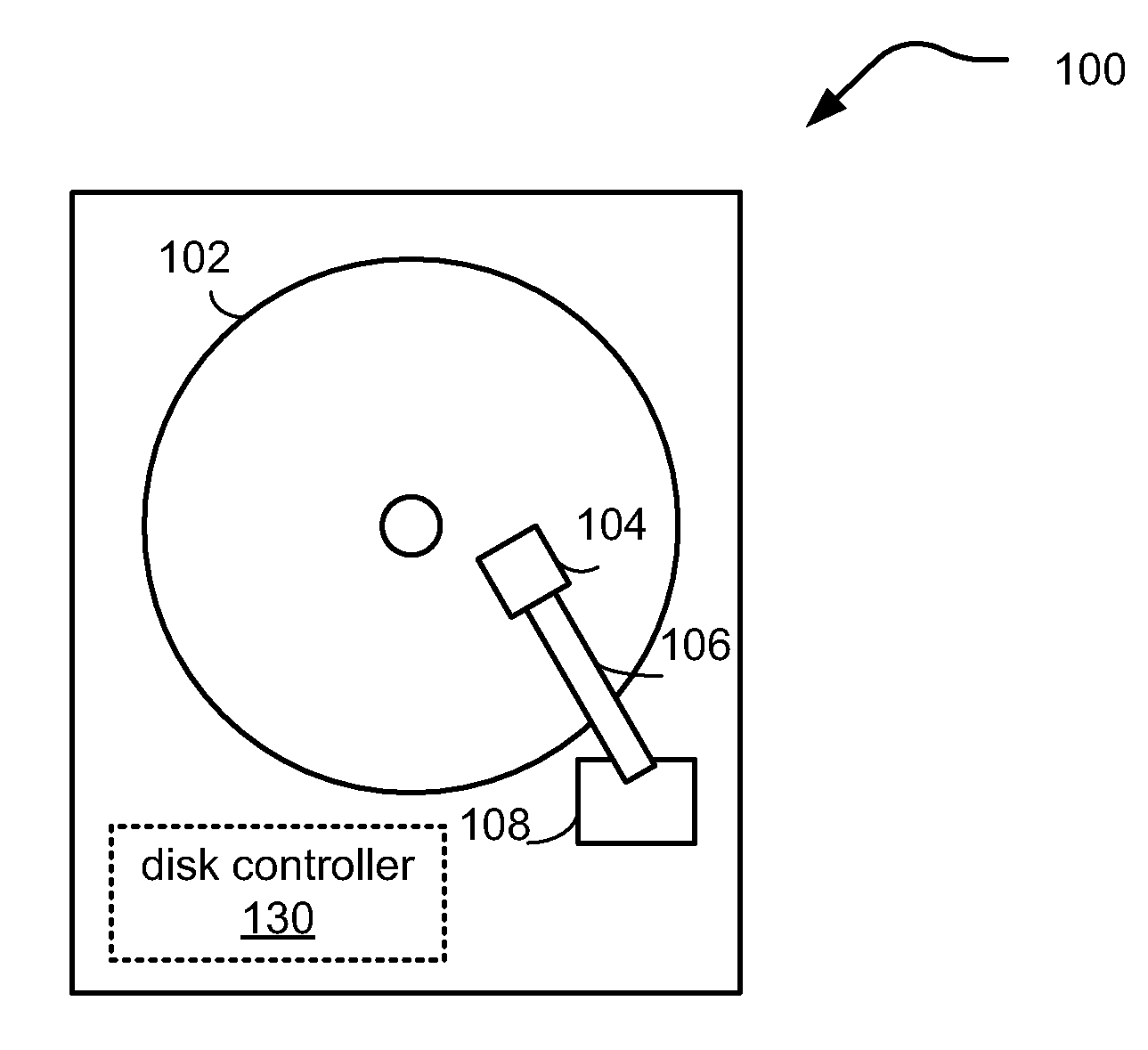

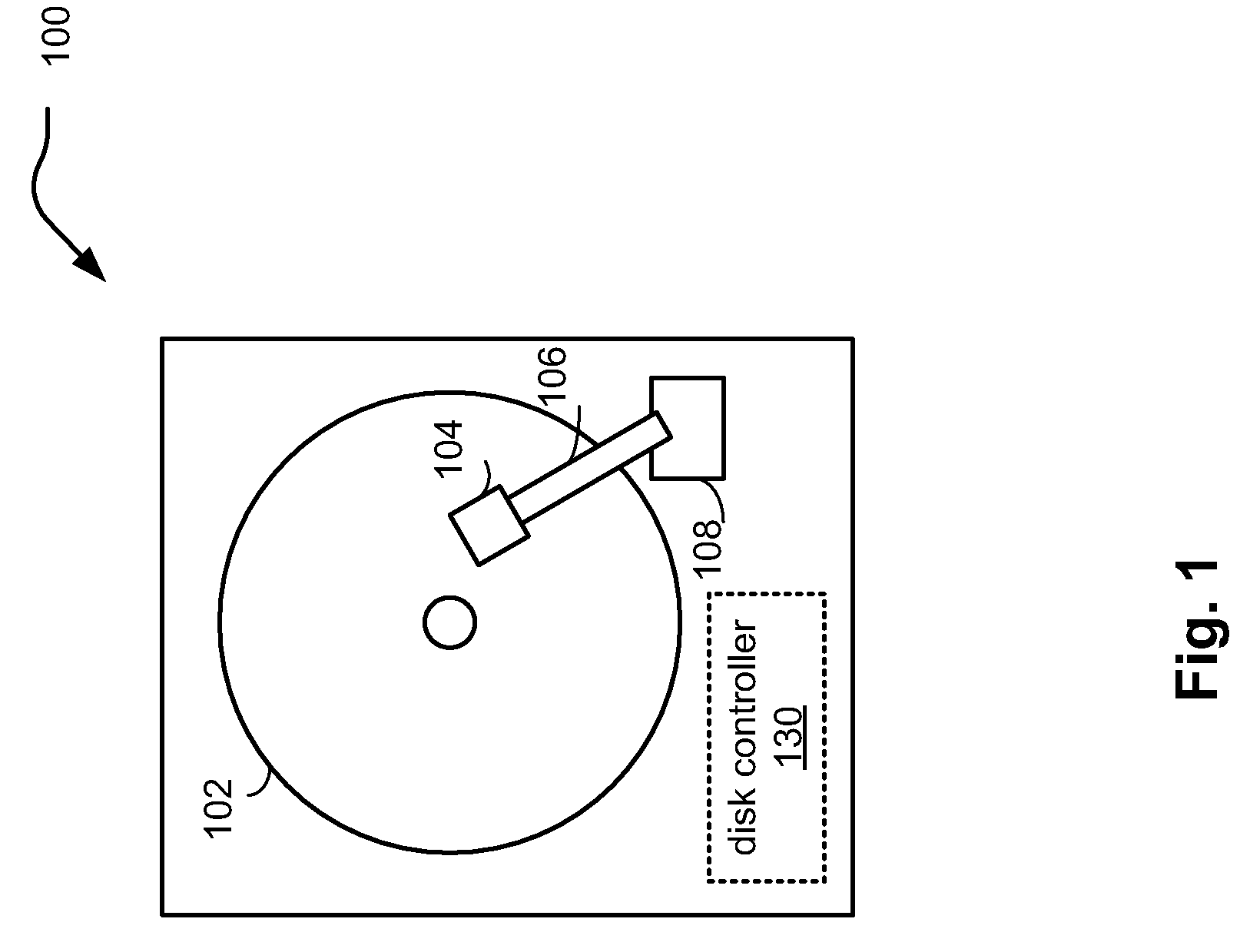

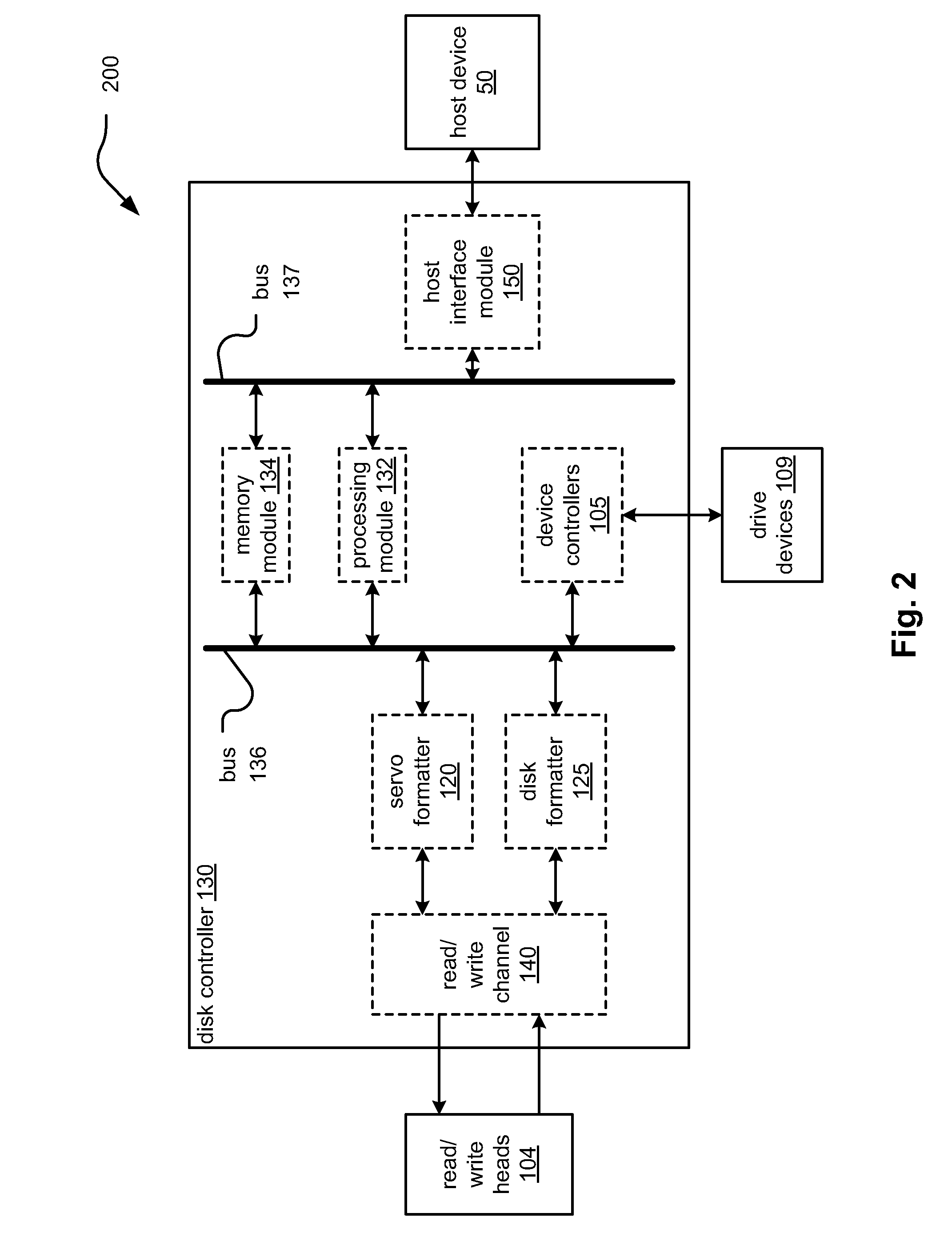

Formatting disk drive data using format field elements

Formatting disk drive data using format field elements (FFEs). A processing module (which can be a general purpose processor or a RISC (Reduced Instruction Set Computer) processor) is employed to generate FFEs that are employed to govern operation of the various data formatting modules within a formatting system within a HDD. The determination of when a data formatting module stops operating in accordance with a first FFE and begins operating in accordance with a second FFE can be a predetermined period of time, a number of operations being performed, the meeting of some condition, or some other means. Each FFE can be viewed as being a multi-dimensional instruction that not only includes a configuration for a data formatting module, but also includes the conditions by which the configuration is to be governed by a subsequent FFE, among other things.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Power circuit scanning test robot airplane and controlling system

InactiveCN1305194CNo casualtiesAvoid lostToy aircraftsCable installation apparatusEngineeringNavigation system

A robot airplane for tour inspection of power line in counterwise driving structure of coxial double propeller uses two engines to control flight stability, GPS and GIS to confirm flight path, computer processor to adjust flight attitute and battery to provide power for motor, transducer and data link system. Its control system consists of navigation system, autonomous planning system, data link system and on line detection system.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

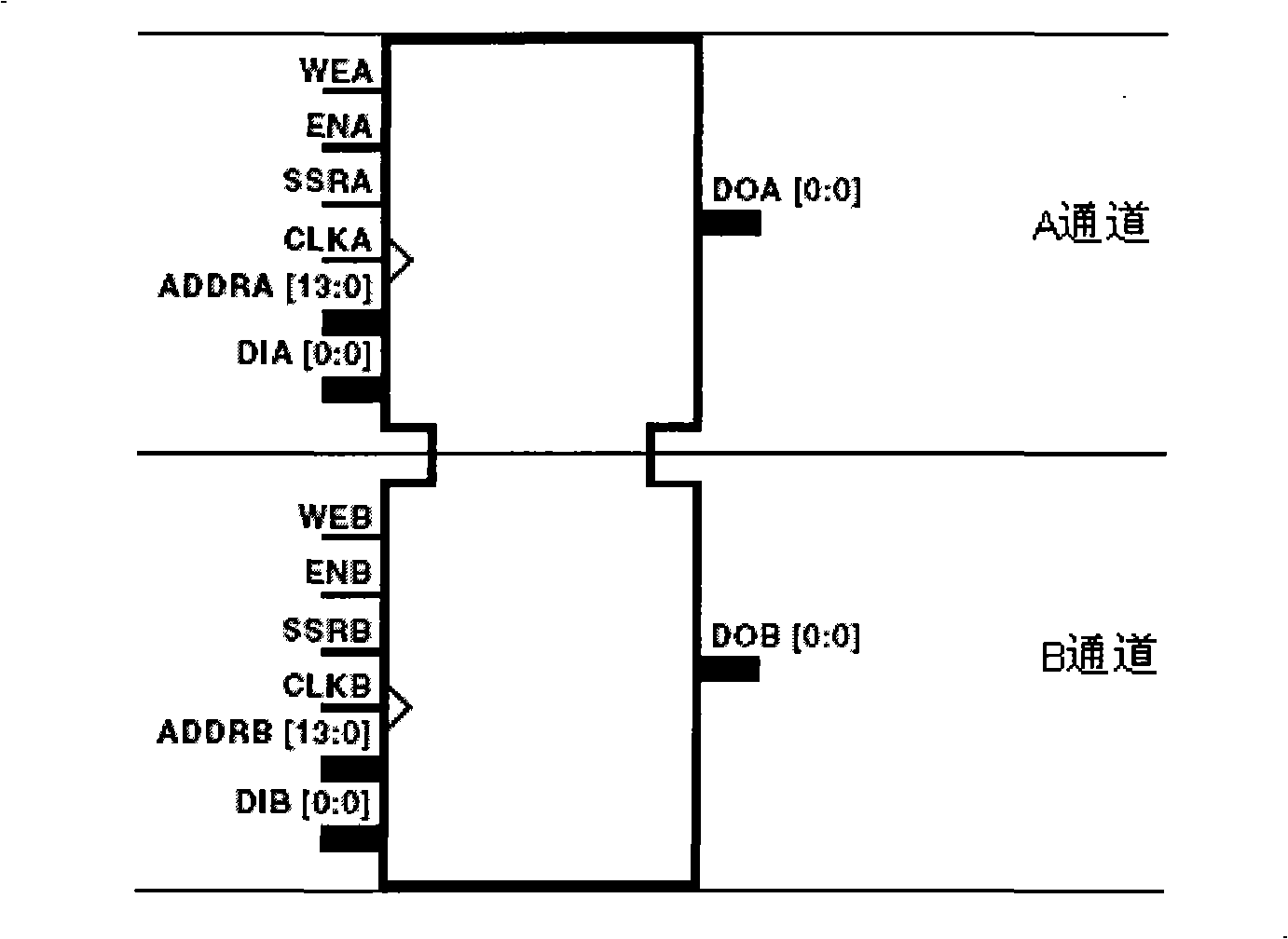

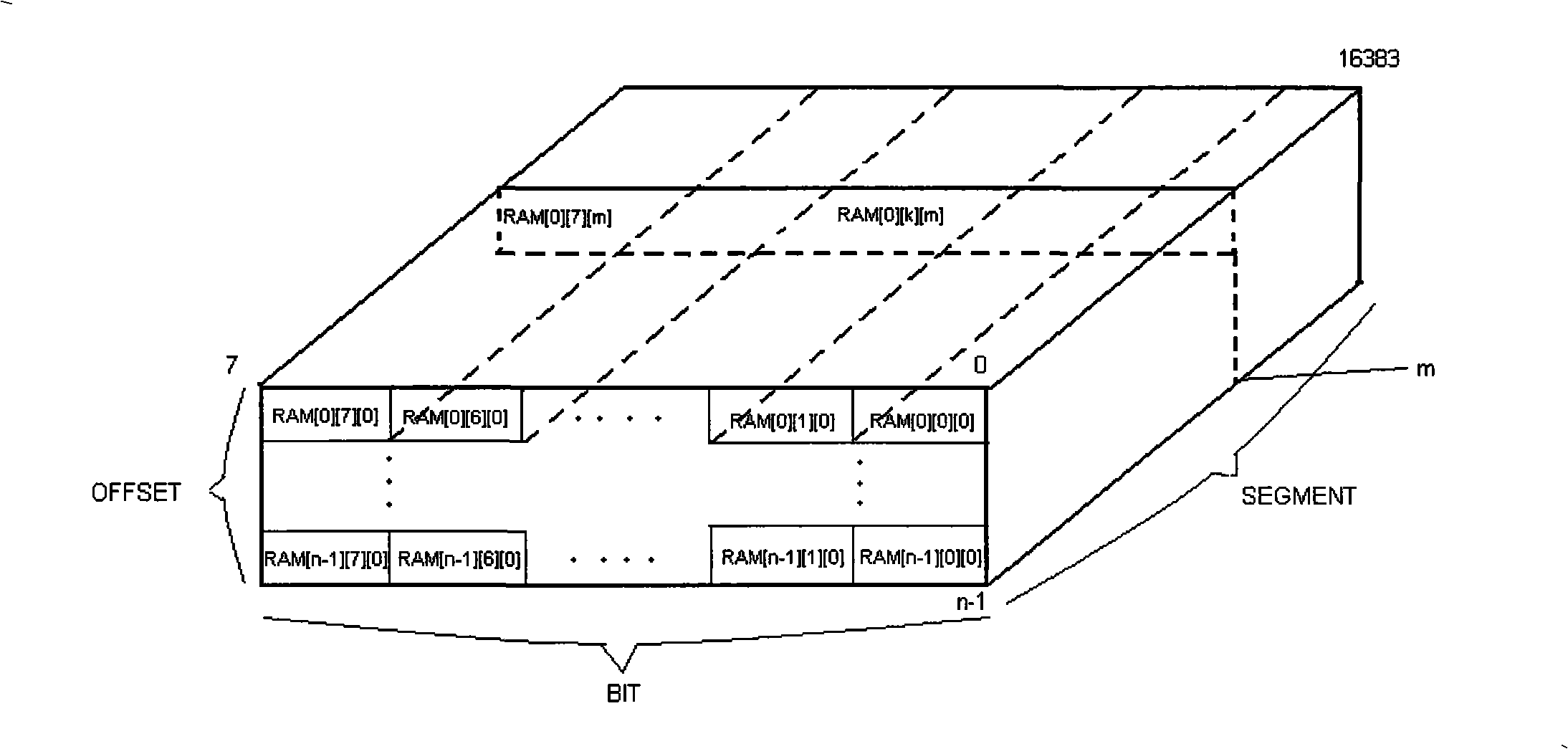

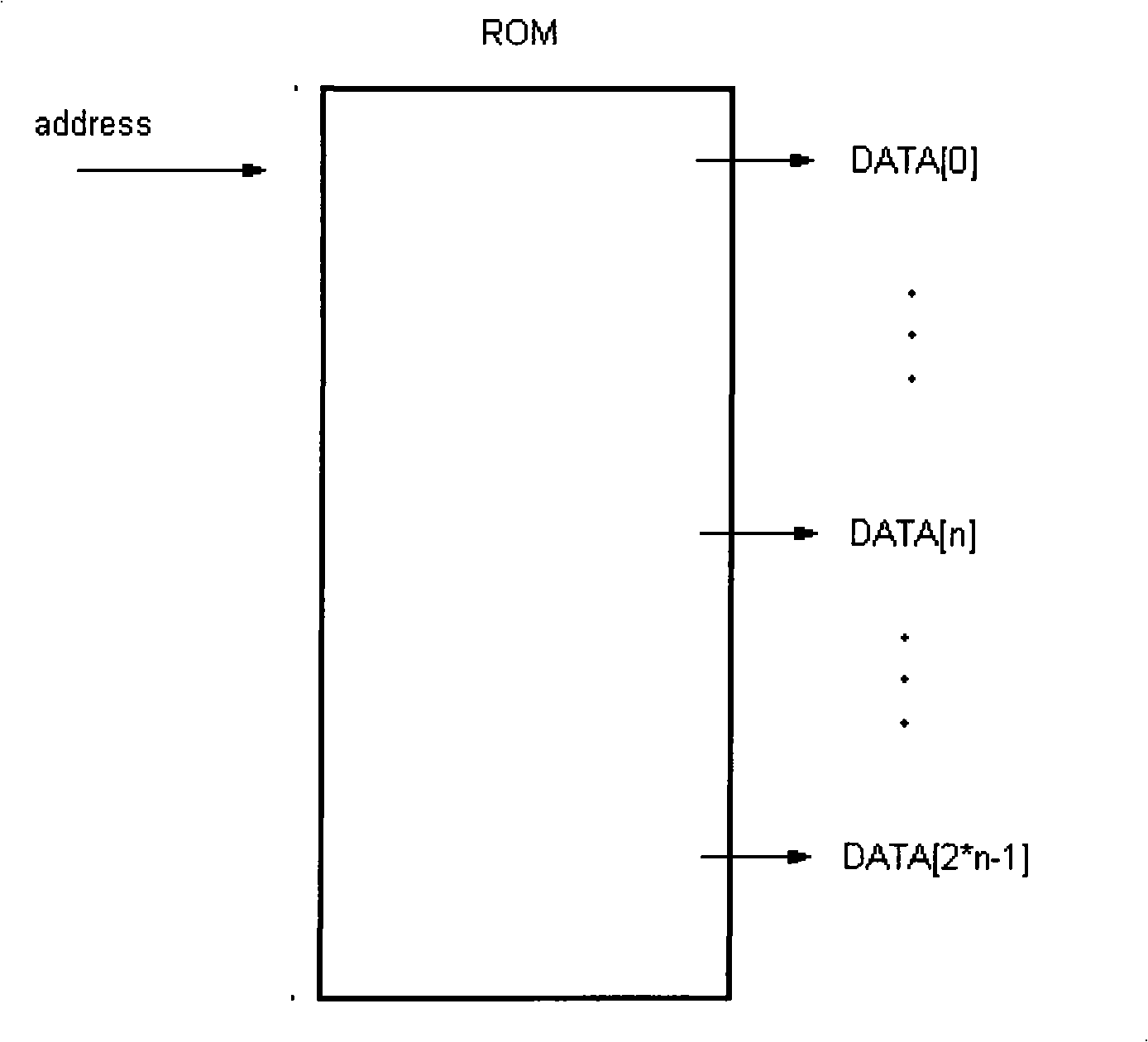

ROM structure and method for writing in INTEL HEX file

InactiveCN101324861ASave resourcesImprove work efficiencyMemory adressing/allocation/relocationIntel HEXData filling

The invention discloses an ROM structure and a method for writing an INTEL HEX file. The ROM is composed of n groups of RAMs, each group comprises eight dual-channel RAMs, each dual-channel RAM comprises an A channel and a B channel, and an identical address is respectively set for the address signals addrA and addrB of the A channel and the B channel of each RAM in each group; the address signals addrA and addrB input to the RAMs in each group are determined according to the address signals input to the ROM; the RAMs in each group respectively output data with two bytes; the n groups of the RAMs output data with 2*n bytes. The method for writing the INTEL HEX file by using the ROM structure is as follows: encoding and data padding are performed to the INTEL HEX file; and then data mapping is performed. By adopting the ROM structure and the method, a plurality of continuous data can be output after one address signal is input, and the ROM structure and the method are suitable for the single-chip microcomputer of the RISC architecture.

Owner:EAST CHINA NORMAL UNIV

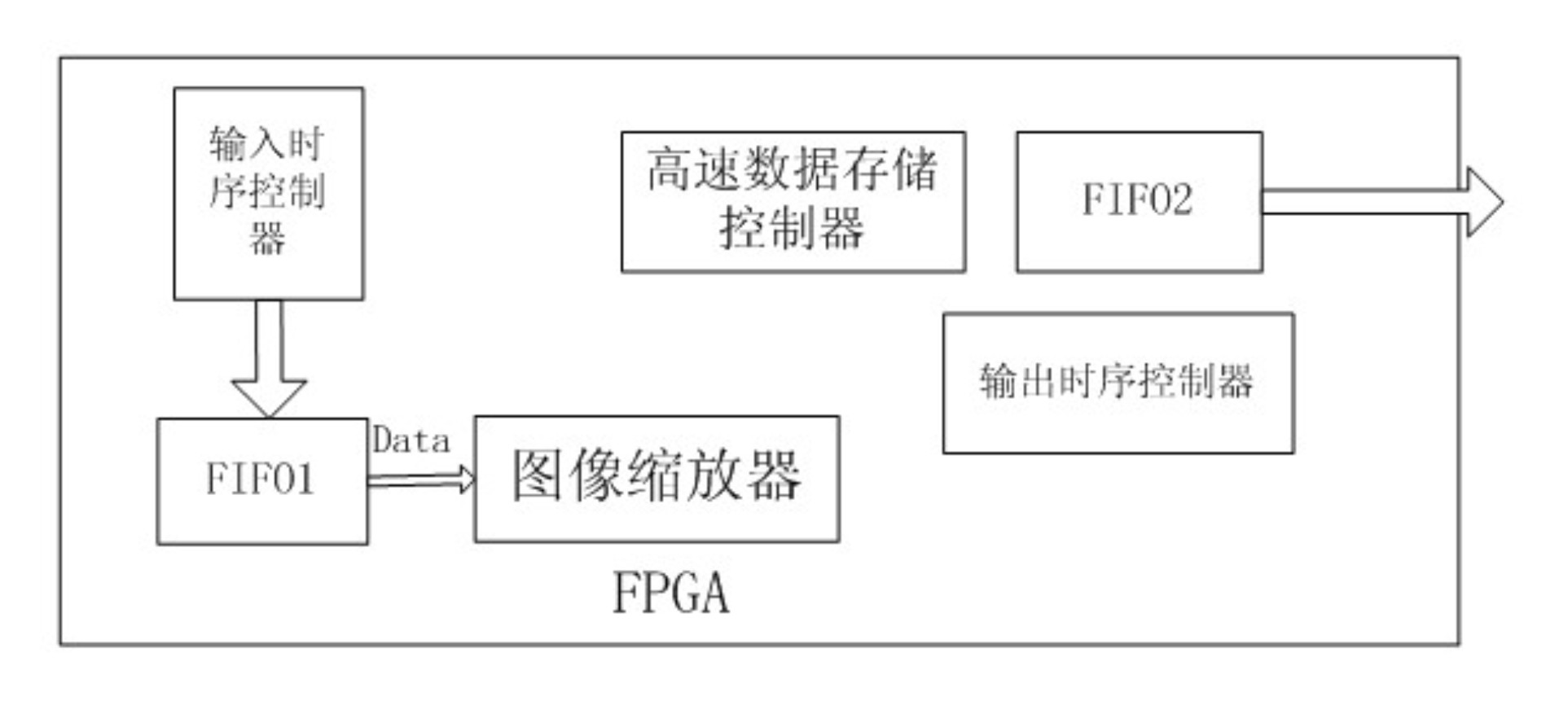

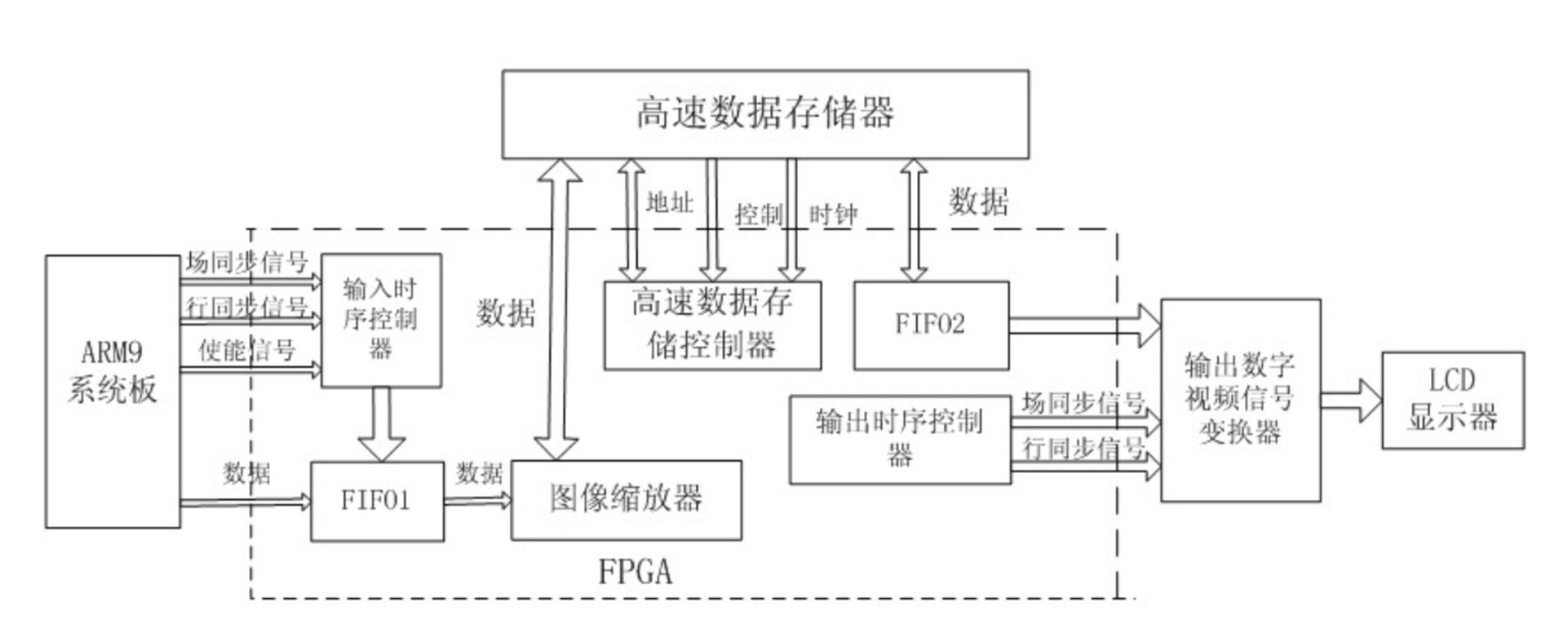

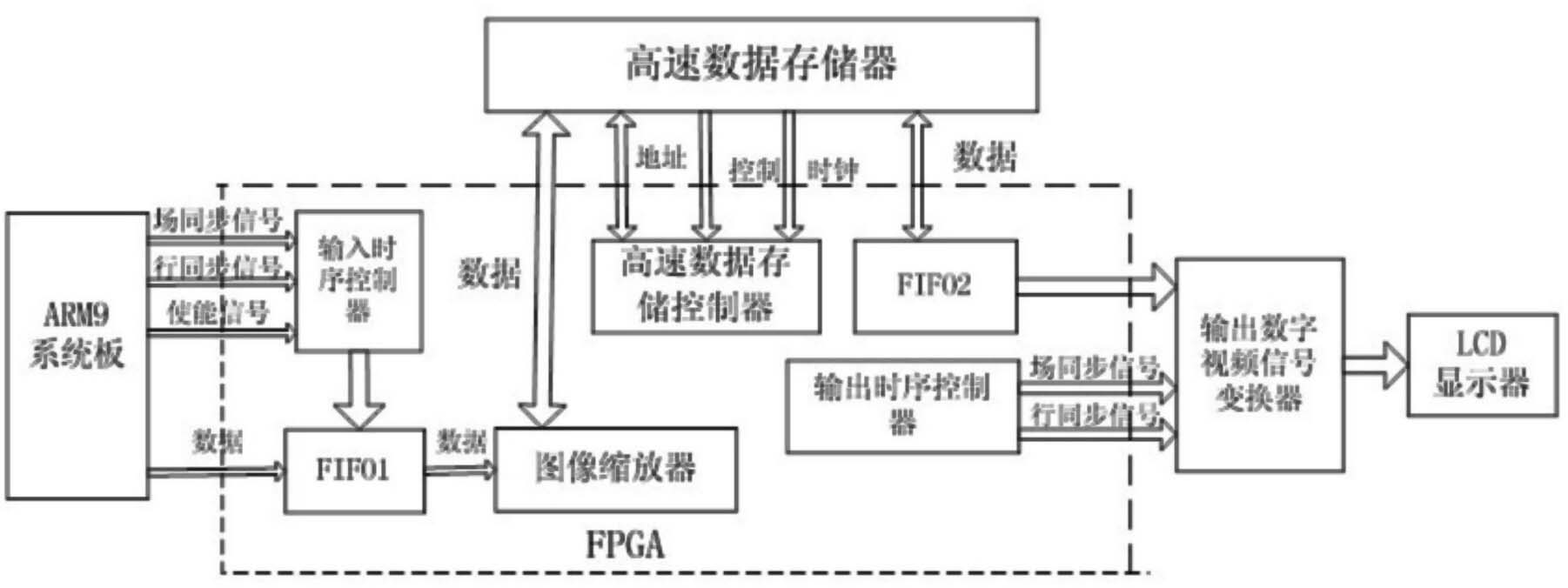

ARM (Advanced RISC (reduced instruction set computing) Machines) signal extension display device

InactiveCN102663984AImprove expressivenessEasy to observeStatic indicating devicesStandards conversionDigital videoGraphics

The invention discloses an ARM (Advanced RISC (reduced instruction set computing) Machines) signal extension display device, which comprises an ARM9 system circuit used for generating ARM image signals, a programmable device FPGA (Field Programmable Gate Array) used for controlling the zoom of graphics, a high-speed data memory used for storing input digital video data frames and output digital video data frames, an output digital video signal converter used for decoding the digital video signals to signals capable of being identified by an external display device, and an LCD (Light Crystal Display) screen used for converting the digital video signals into information capable of being directly sensed by the eyes of a human body. According to the ARM signal extension display device, the resolution of ARM signals is extended, thereby facilitating to observe the graphics and increasing the performance of the graphics.

Owner:EAST CHINA NORMAL UNIV

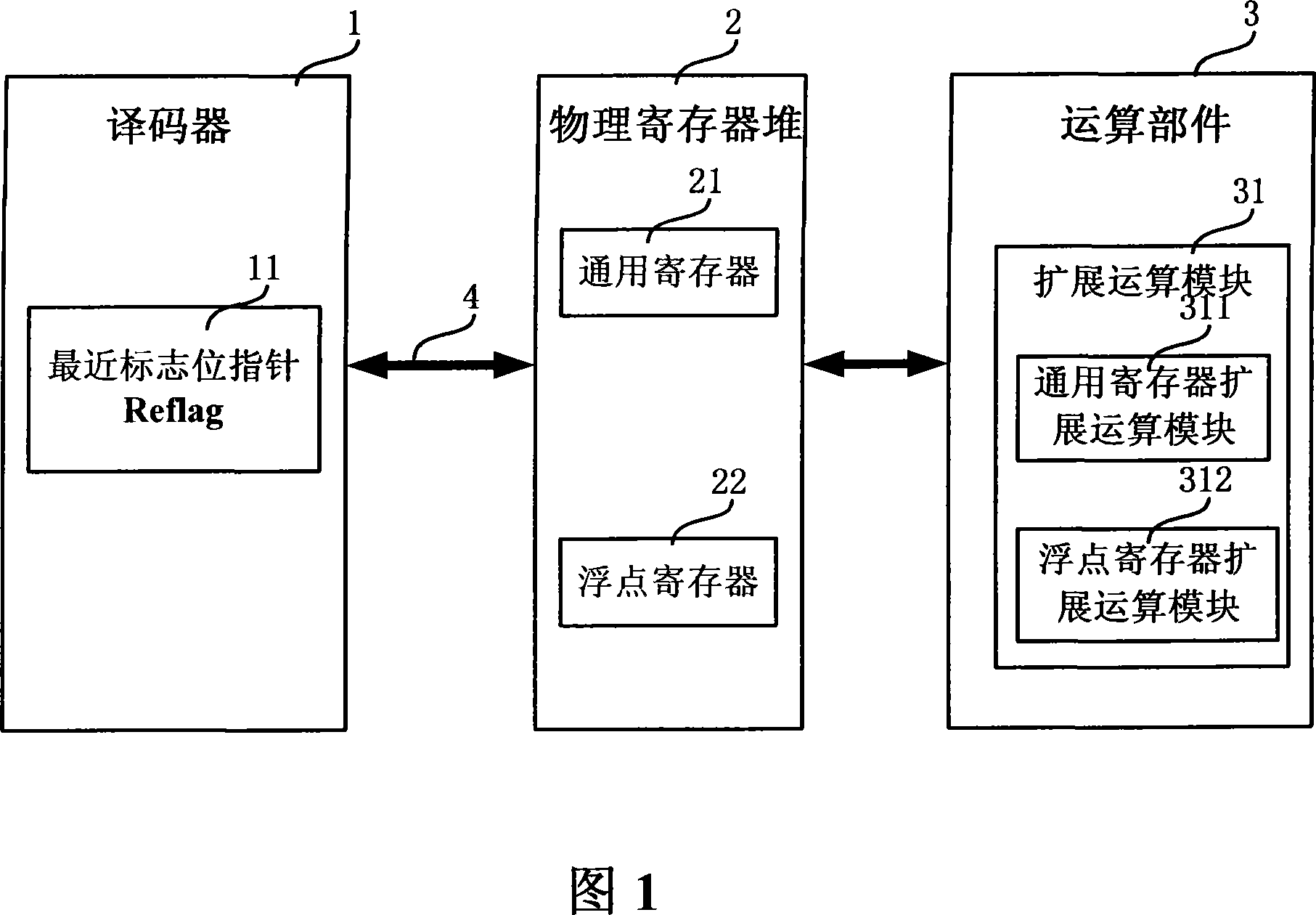

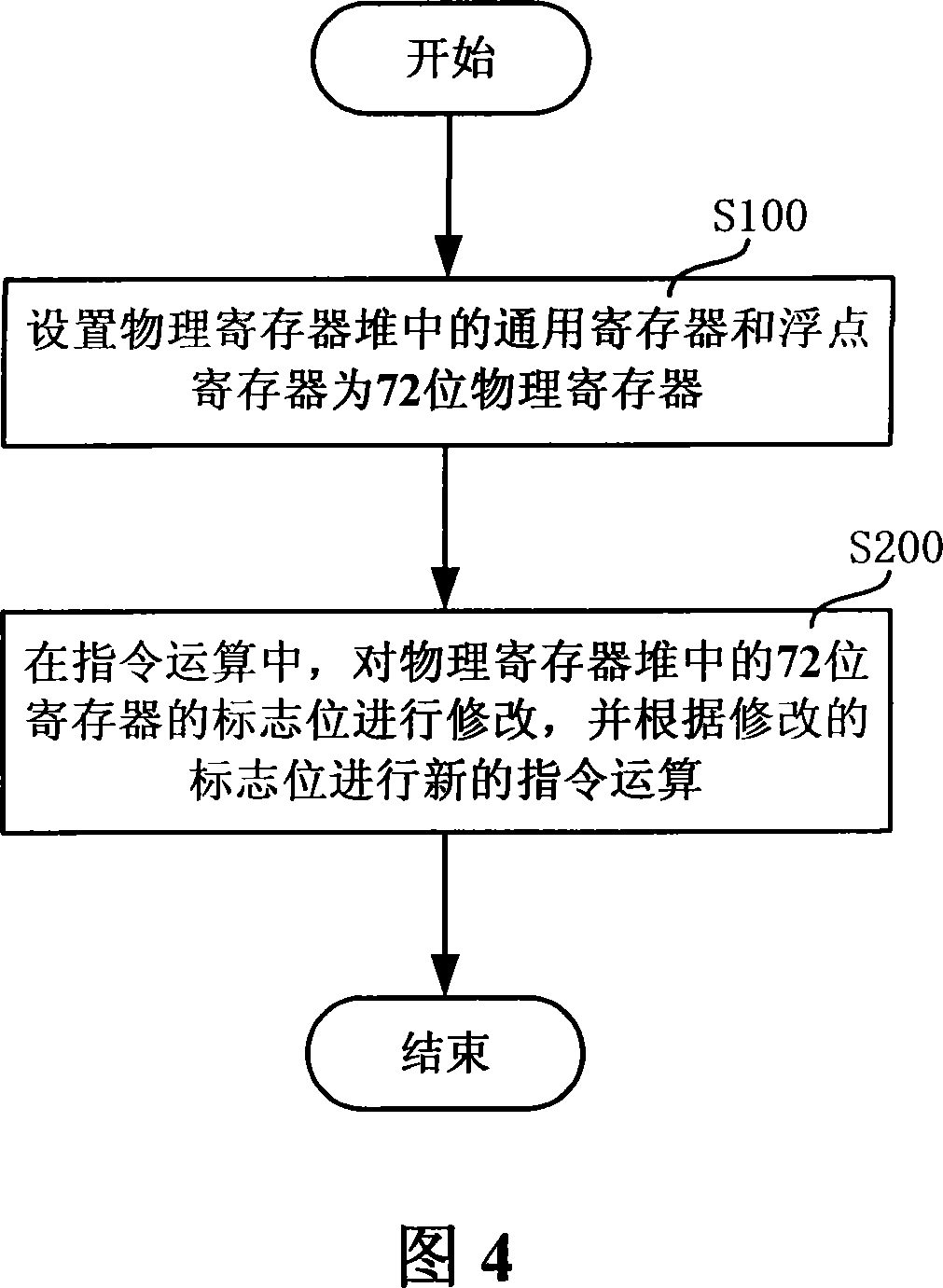

RISC processor device and data processing method thereof

ActiveCN101221496APrevent overflowLarge room for optimizationConcurrent instruction executionMemory systemsProcessor registerData path

The present invention discloses a reduced instruction set computer (RISC) processor device and the data processing method thereof. The device comprises a decoder, a physical register file and an operational unit, as well as a data path connected among the decoder, the physical register file and the operational unit, wherein, each physical register in the physical register file is extended to 72 bits, and the whole data path is uniformly expanded to 72 bits; the operational unit comprises an extended operational module which is used in instruction operation to modify the flag bit of the 72-bit register in the physical register file and to carry out new instruction operation according to the modified flag bit. The present invention expands the optimization space of virtual machines and achieves the objective of improving the performance of virtual machines.

Owner:LOONGSON TECH CORP

Method and apparatus for implementing a dynamic out-of-order processor pipeline

A hardware / software co-design for an optimized dynamic out-of-order Very Long Instruction Word (VLIW) pipeline. For example, one embodiment of an apparatus comprises: an instruction fetch unit to fetch Very Long Instruction Words (VLIWs) in their program order from memory, each of the VLIWs comprising a plurality of reduced instruction set computing (RISC) instruction syllables grouped into the VLIWs in an order which removes data-flow dependencies and false output dependencies between the syllables; a decode unit to decode the VLIWs in their program order and output the syllables of each decoded VLIW in parallel; and an out-of-order execution engine to execute the syllables preferably in parallel with other syllables, wherein at least some of the syllables are to be executed in a different order than the order in which they are received from the decode unit, the out-of-order execution engine having one or more processing stages which do not check for data-flow dependencies and false output dependencies between the syllables when performing operations.

Owner:INTEL CORP