Testing system and testing method of multi-format video decoder

A technology for video decoders and testing methods, which is applied in the field of multi-format video decoder test systems, can solve the problems of less FPGA verification and large logic resources of multi-format video decoders, and achieve the effect of real-time viewing of decoding effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

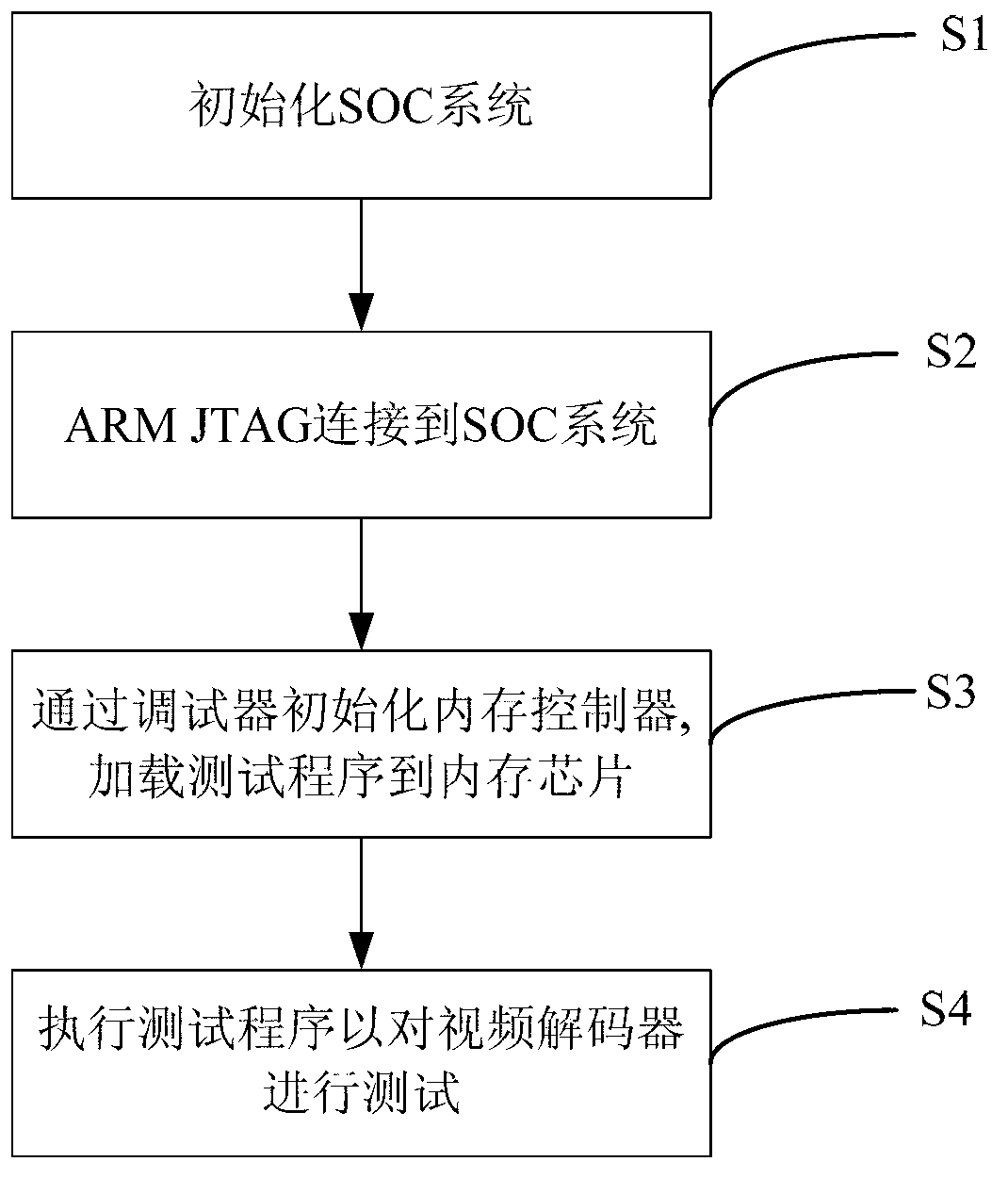

[0028] In order to describe the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

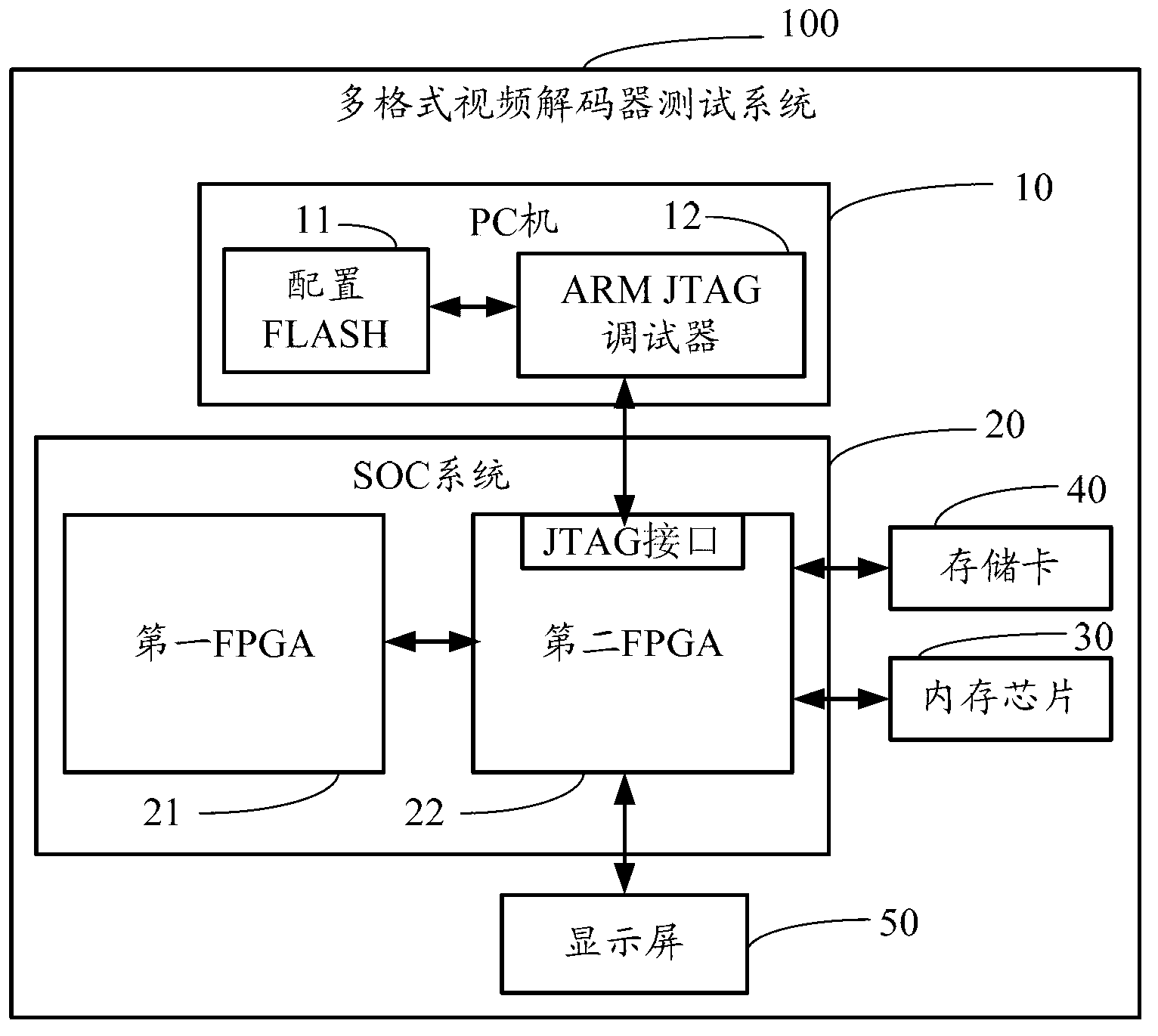

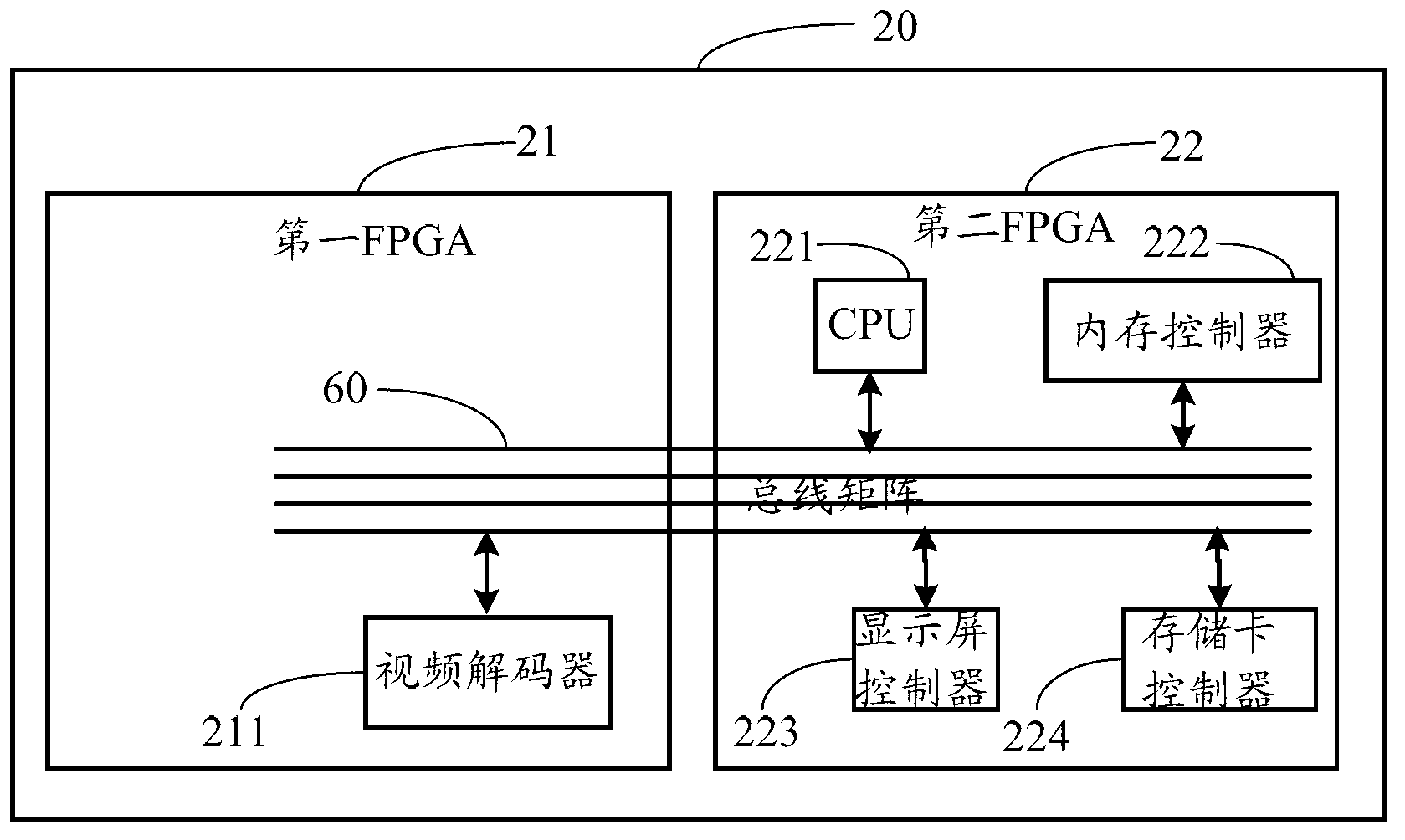

[0029] see figure 1 , is a structural block diagram of a test system for a multi-format video decoder in an embodiment of the present invention. The test system 100 of the multi-format video decoder includes a PC 10, an SOC system 20, a memory chip 30, a memory card 40, and a display screen 50, wherein the SOC system 20 includes a first FPGA 21 and a second FPGA 22, for For convenience of description, the first FPGA 21 and the second FPGA 22 are defined as dual FPGAs. Wherein, the second FPGA 22 is electrically connected to the PC 10 , the first FPGA 21 , the memory chip 30 , the memory card 40 and the display screen 50 respectively.

[0030]The PC 10 is used for compiling and debugging test programs, and the PC 10 includes an ARM JTAG d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More