Method and equipment of pipeline treating series treatment command

A technology for processing instructions and pipelines, applied in the direction of concurrent instruction execution, electrical digital data processing, memory systems, etc., can solve problems such as unavailability, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

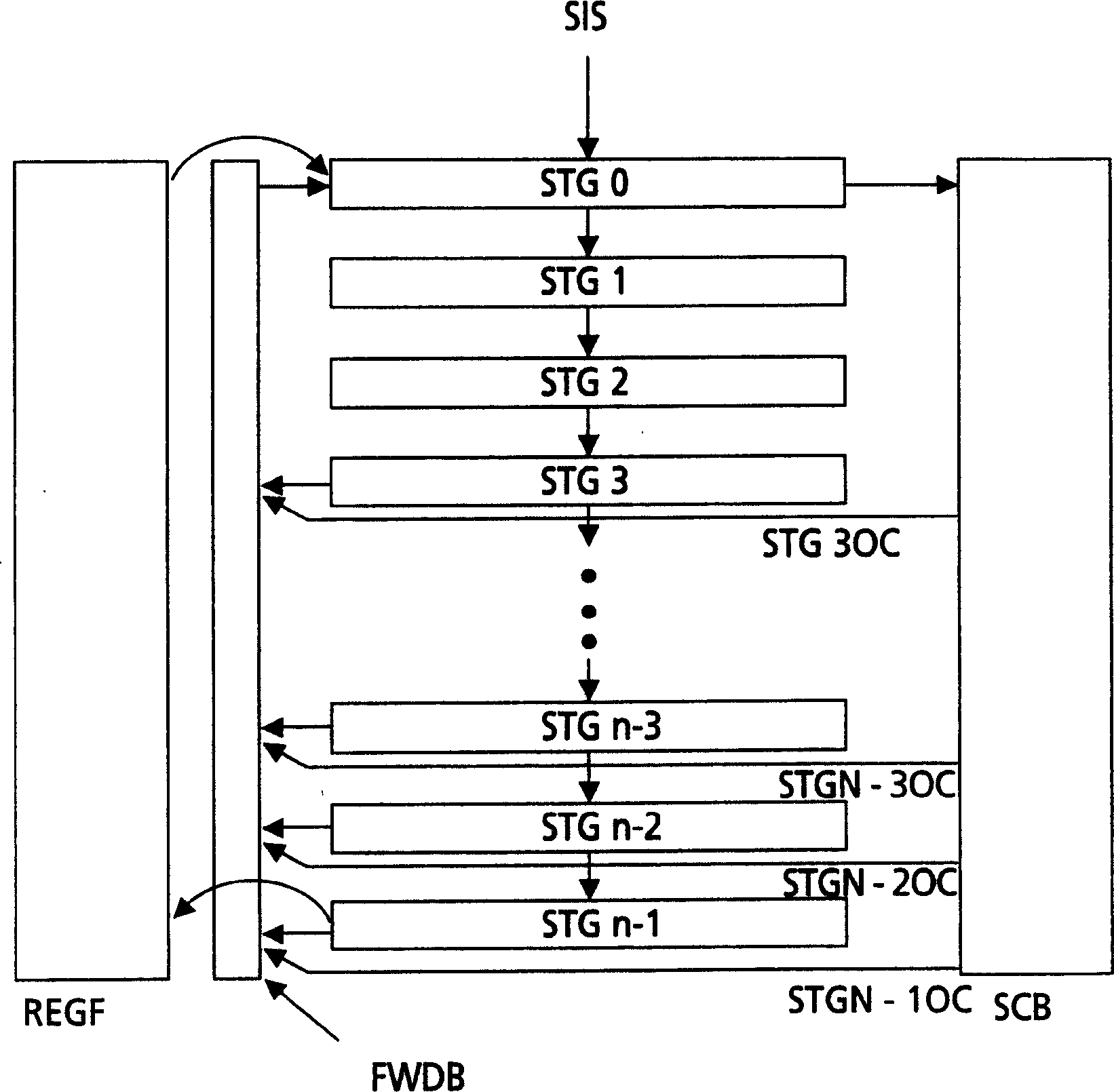

[0027] exist figure 1 , the (sequential) instruction stream enters the first stage STG0 of a series of n pipeline processing stages STG0 to STGN-1. Each of these stages includes, for example, a series of registers and appropriate processing means that perform typical calculations or operations performed in a CPU or microprocessor. For example, stages STG3 to STGn-2 can forward intermediate or partial results to the forwarding bus FWDB, or to a multiplexing bus. However, depending on the application, stages STG2 and / or STG1, or otherwise subsequent stages STG4, STG5, . . . , may also not forward intermediate or partial results to the FWDB bus. Stages STG0 to STGn-2 are capable of forwarding intermediate pipeline processing results to corresponding subsequent stages for further processing. The first stage STG0 is able to read intermediate or partial results from the bus FWDB and / or from the register file REGF. The final stage STGn-1 writes the final result into the register f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More