Silicon-on-insulator (SOI)/metal oxide semiconductor (MOS) device structure for connecting negative voltage on backgate through negative charge pump and manufacturing method

A technology of MOS devices and negative charge pumps, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, electrical components, etc., can solve problems affecting device performance, simplify process steps, improve back gate threshold voltage drift effect, eliminate effect of influence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

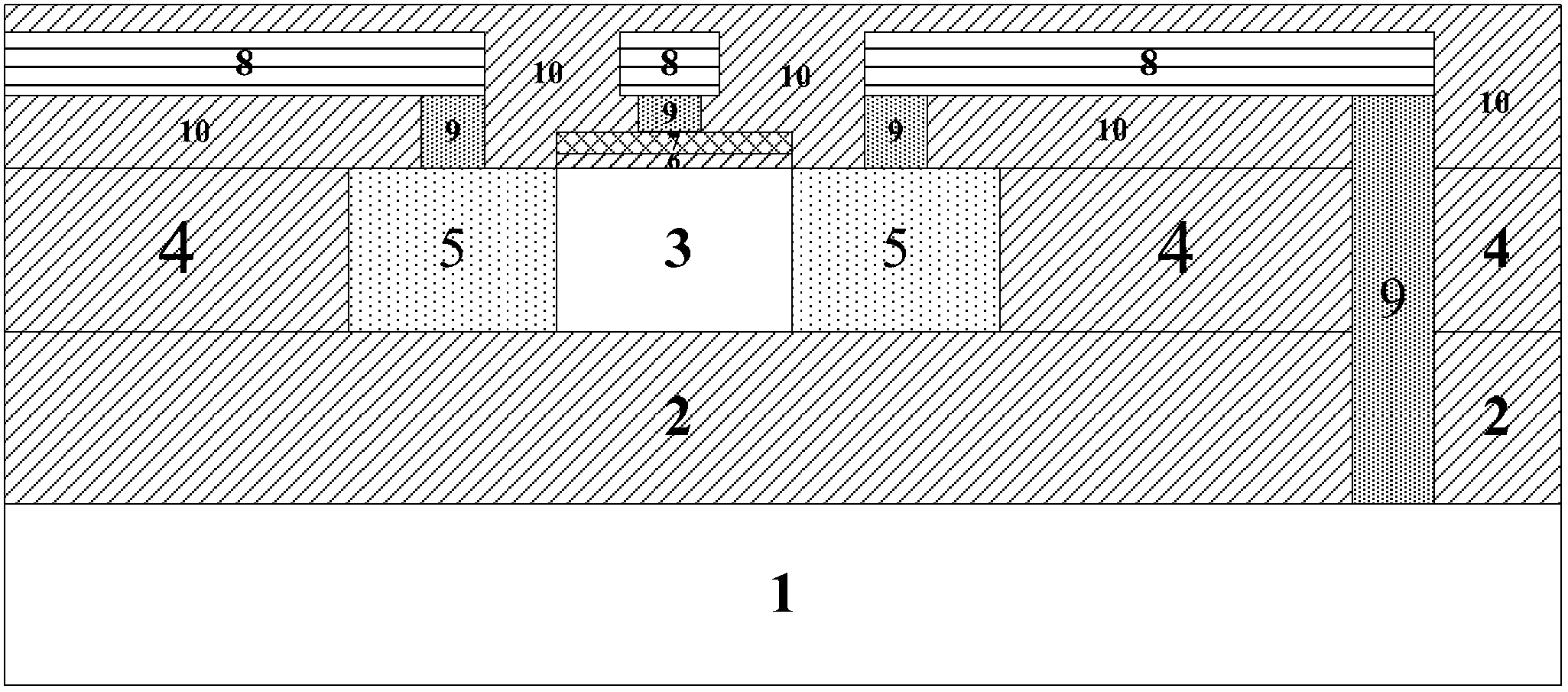

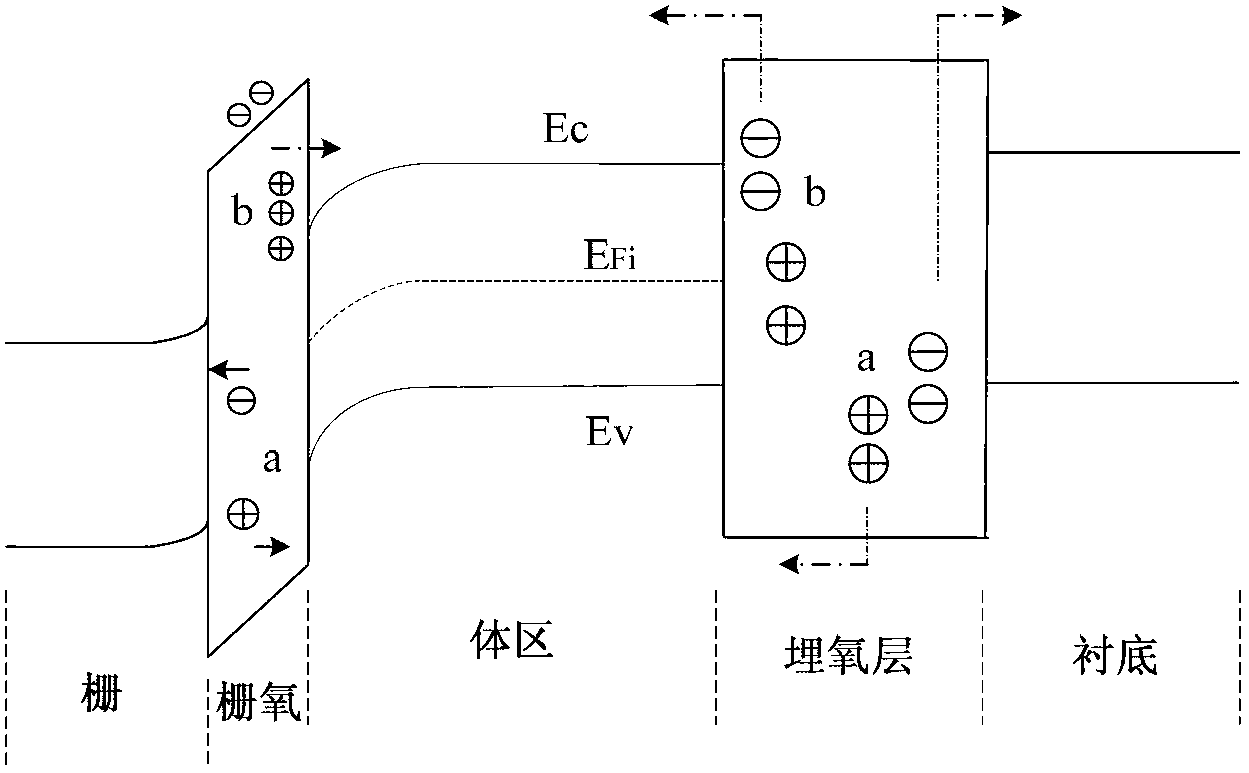

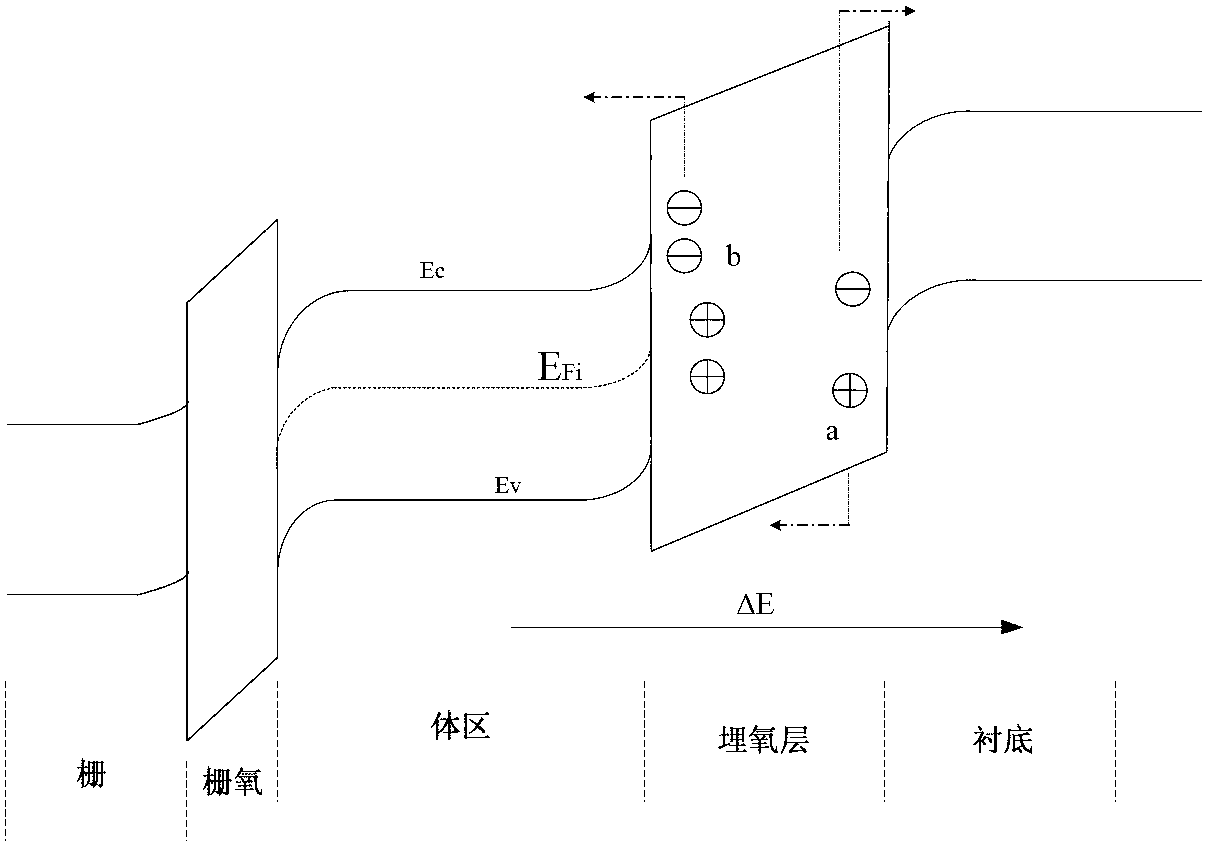

[0018] The present invention will be further described below in conjunction with drawings and embodiments. The invention relates to the SOI / MOS device structure and manufacturing method with negative voltage connected to the back gate. By opening holes from the front side of the silicon film of the SOI / MOS device, the contact hole passes through the buried oxide layer, and the substrate is connected to the surface of the SOI / MOS device. Negative charge pump to improve the back gate effect of partially depleted SOI / MOS devices under radiation conditions. The basic principle of this design is: use the back substrate to connect negative voltage to change the electric field distribution in the buried oxide layer of SOI / MOS devices, so as to affect the accumulation of positive charges at the back gate interface under radiation conditions, so as to eliminate the impact caused by the total radiation dose. The influence of back gate effect on device performance.

[0019] Such as fig...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap