Flash-sharing device for multiprocessors and firmware program loading and upgrading method

A FLASH memory and multi-processor technology, applied in the direction of program loading/starting, program control devices, etc., can solve problems affecting FPGA program loading and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The device for sharing FLASH among multiple processors and the method for loading and upgrading firmware programs of the present invention will be further described in detail below.

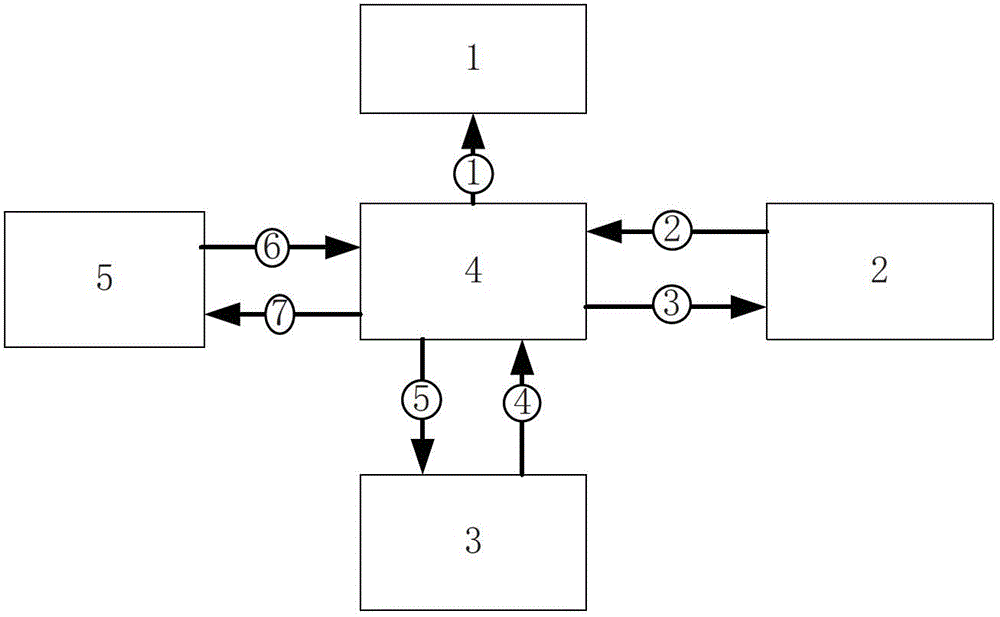

[0025] Such as figure 1 Shown, a kind of device that multiprocessor shares FLASH, comprises a DSP processor 2 and an FPGA processor 3, a FLASH memory 1, and a FLASH management device 4; Described FLASH management device 4 is processed with described DSP respectively device 2, the FPGA processor 3 bidirectionally controls the connection, and the FLASH management device 4 controls the connection to the FLASH memory 1. In order to realize that DSP and FPGA share a FLASH, on the distribution of address lines, the low-end address line of described FLASH memory 1 is connected with the address line of described DSP processor 2 by FLASH management device 4, and the address line of described FLASH memory The highest two address lines are connected with the address lines of the FLASH management dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More